Академический Документы

Профессиональный Документы

Культура Документы

Ec2203-Unit IV Memory Devices Digital Electronics

Загружено:

Karthikeyan_Go_9525Исходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Ec2203-Unit IV Memory Devices Digital Electronics

Загружено:

Karthikeyan_Go_9525Авторское право:

Доступные форматы

EC2203-DE|G.

Karthikeyan, AP|ECE, SKPEC

EC2203-DIGITAL ELECTRONICS

UNIT IV - MEMORY DEVICES PART-I

G.Karthikeyan M.E., AP | ECE, SKP Engineering College, Tiruvannamalai 606611, Tamilnadu, India

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

CONTENTS

Introduction Classification of Memory ROM PROM EPROM EEPROM ROM Origination RAM Static RAM Dynamic RAM RAM Organization DRAM organization Memory Cycles and Timing Waveforms Read Cycle Write Cycle Memory Decoding Coincident Decoding Memory Expansion Expanding Word Size Expanding memory Capacity

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

Introduction

Name Memory Meaning/Operation It is made up of registers

Memory Location Address

Capacity

Each register in the memory is one storage location. It is also called as memory location Used to identify the memory location

The total no. of bits that a memory can store is its capacity (Most of the types of capacity is specified in terms of bytes. 1 byte=8bits)

Registers

Consists of storage elements {Flip flop or Capacitors =Semiconductor memories Magnetic domain = Magnetic storage}

It is a storage element The process of storing a data in to a memory The process of retrieving the data from the memory

Cell Write Read

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

Read & Write operation

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

Block diagram of memory unit

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

How a communication is takes place between memory and its environment

1. 2.

Data lines

Provides the information stored in the memory

Address selection lines

Specify the particular word

3.

Control Lines

Direction of transfer

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

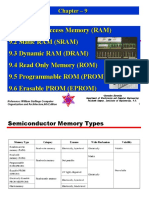

Classification of memory

CLASSIFICATION OF SEMICONDUCTOR MEMORIES NON VOLATILE

READ ONLY MEMORY (ROM) MaskProgrammable ROM Programmable ROM READ/WRITE MEMORY (NVRAM) EPROM

VOLATILE

READ/WRITE MEMORY (PWM)

RANDOM ACCESS SRAM DRAM

NON RANDOM ACCESS FIFO LIFO Shift Registers

EEPROM Flash

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

ROM (Read only Memory)

PROM 2. EPROM 3. EEPROM 4. ROM ORGANIZATION

1.

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

ROM CELL

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

10

PROM (Programmable Read Only Memory)

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

11

Four Byte PROM

Diode: Initially all 0

Proper current

pulse: to blow the fuse Fuse material: Nichrome & Polycrystalline Current range to blow fuse: 20 to 50mA Time: 5 to 20s Also called as burning of PROM

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

12

EPROM (Erasable Programmable Read Only Memory)

Uses MOS circuitry Store 1s & 0s

Programmed by

user Erasing the date: by using Ultraviolet light through its quartz window Time: 20minutes Erasing: Entire information lost

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

13

EEPROM (Electrically Erasable Programmable Read Only Memory)

Very Similar to EPROM The insulating layer: very thin (i.e) <200Ao Voltage: 20 to 25 V for programming or erasing Selective information can be erased Time: 10ms

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

14

ROM Organization

Simple Four Byte Diode ROM

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

15

ROM ORGANIZATION (CONTD)

Contents of ROM

Address in binary

00 01 10

Binary Data

D0 1 0 0 D1 0 1 1 D2 1 0 0 D3 0 1 0 D4 0 0 0 D5 1 0 1 D6 0 0 1 D7 1 1 0

Data in Hexa decimal

A5 51 46

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

16

ROM ORGANIZATION (CONTD)

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

17

RAM (Random Access Memory)

Static RAM (SRAM) Static RAM Cell

Read Operation Write operation

Bipolar RAM Cell

MOSFET RAM Cell

Dynamic RAM (DRAM) Dynamic RAM Cell COMPARISON BETWEEN SRAM AND DRAM

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

18

STATIC RAM CELL

Read Operation

Write Operation

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

19

BIPOLAR RAM CELL

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

20

MOSFET RAM CELL

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

21

Dynamic RAM (DRAM)

Dynamic Ram Cell

Storage Capacitor

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

22

COMPARISON BETWEEN SRAM AND DRAM

Sl.No

1

Static RAM

Dynamic RAM

Static RAM contains less memory Dynamic RAM contains more memory cells per area. cells as compared to static RAM per unit area It has less access time hence Its access time is greater than static faster memories RAMs Static RAM consists of flip-flops. Dynamic RAM stores the data as a Each flip-flop stores one bit charge on the capacitor. It consists of MOSFET and the capacitor for each cell. Refreshing required. circuitry is not Refreshing circuitry is required to maintain the charge on the capacitors after every few milliseconds. Extra hardware is required to control refreshing. This makes system design complicated. Cost is less

2 3

Cost is more

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

23

RAM Organization

RAM organization: in the

form of Array Each cell: capable of storing one bit information Memory chip: 8191 bit Line decoder

64 rows 128 columns i.e

13 address lines 6 for rows ( 0 to 5 ) 7 for columns ( 0 to 6 )

64x128=8192 memory cells

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

24

DRAM Organization

Two dimensional It is a 16 M-bit DRAM.

Configured as 2M x 8 Cells organized 4Kx4K array 4096 cells addressed by 12 address bits It can store 512x8, i.e 512 bytes 21 address lines

9 for column ( 0 to 8) 12 for row ( 9 to 20)

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

25

DRAM ORGANIZATION (CONTD)

Configured as 2Mx4 Row & Column

address lines multiplexed: To reduce number of pins So, less address pins than SRAM chip 11 address lines: to select one of 2048 lines for output 211=2048

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

26

Read Cycle

1. 2.

Memory Cycles and Timing Waveforms

tRC tAA tOH tLZ tACS tHZ tOE tDF tPU tPD

ADDRESS DATA CS OE SYPPLY CURRENT

3.

4. 5.

6.

7. 8. 9. 10.

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

27

Write Cycle

1. 2.

Memory Cycles and Timing Waveforms

tWC tAW tWR tAS tCW tWP tDW tDH

3.

4. 5.

6.

7. 8.

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

28

Decoder operation

Memory Decoding

16 words of 8 bits each

A memory with 16 words

needs 4 address lines So, 4 x16 decoder is used If memory enable = 0

If memory enable = 1

One of the 16 word is

No memory word is select

Read/write determines the

selected

operation Write operation:

Data transferred in to eight

memory cells If a memory cell is not selected, that is disabled and the previous value remain unchanged

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

29

Coincident Decoding

k input 2k output

2k and gates are needed

with k input to each gate So, 2 decoders used to reduce the no. of inputs So k/2 inputs to each decoder instead of k inputs Instead of 10 x 1024 we use 5 x 32 decoders

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

30

Illustrate The Concept of 16 X 8 Bit ROM Arrange With Diagram

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

31

Explain the Basic Structure of 256 X 4 Static RAM, with neat diagram

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

32

Memory Expansion

2 methods

1. Expanding word size 2. Expanding memory capacity

3. Limitations for memory expansion

4. Example Problems

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

33

Memory Expansion

Expanding Word Size By connecting 2 or

Design 1 K X 8 RAM using two 1 K X4 ICs

more ICs together Data bus: In Series Address bus: In parallel Chip select: common to Both memory ICs Word size is limited: by Data bus width

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

34

Memory Expansion

Expanding Memory

Capacity

Design 16 K X 8 RAM using four 4 K X 8 ICs

By connecting 2 or more

ICs in parallel i.e. The address & data bus connected in parallel Chip select: separate to each cell(generated by address decoder) Capacity is limited: by address bus width

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

35

Memory Expansion

Limitations for memory Expansion Memory devices: Processors accessed using Address,

data & Control bus But Each Processor has limited no. of address lines & data lines Eg:Suppose a processor has 24 address lines & 16 data lines, we can expand memory word size up to 16 Memory capacity up to 224 = 16Mbytes

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

36

How one can make 64x8 ROM using four 32x4 ROMs? Draw such a circuit and explain

64x8 ROM = Four 32x4 ROM Two pair ICs

Data bus: In series

Address bus: In parallel In two pair: The data, address

& control bus: In parallel To address 32 memory locations: 5 address lines(A0 to A4) needed The additional line: used to select the particular pair(A5)

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

37

Given the 32x8 ROM chip with enable input, show the external connection necessary to construct a 128x8 ROM with four chips and a decoder

EC2203-DE|G.Karthikeyan, AP|ECE, SKPEC

38

SUMMARY

Вам также может понравиться

- IC Applications Lab Manual Satish BabuДокумент74 страницыIC Applications Lab Manual Satish BabuRAVIHIMAJAОценок пока нет

- EC6302 Digital Electronics 2 Marks With AnswersДокумент18 страницEC6302 Digital Electronics 2 Marks With AnswersBasky40% (5)

- CNTLДокумент31 страницаCNTLAkanksha DixitОценок пока нет

- Embedded Systems: Technical PublicationsДокумент16 страницEmbedded Systems: Technical PublicationsPrince ScottОценок пока нет

- 8051 Microcontroller Lab Manual Lab 07Документ5 страниц8051 Microcontroller Lab Manual Lab 07sidiqbal100% (1)

- DC Motor ArduinoДокумент40 страницDC Motor ArduinoBodo De La BuernoОценок пока нет

- Optical Fiber Transmission Link ElementsДокумент15 страницOptical Fiber Transmission Link ElementsAchu0% (1)

- NTA UGC NET Electronic Science SyllabusДокумент3 страницыNTA UGC NET Electronic Science Syllabusgrk.elrОценок пока нет

- LICДокумент33 страницыLICRavi RathodОценок пока нет

- Design of Traffic Light Controller Using Timer CircuitДокумент3 страницыDesign of Traffic Light Controller Using Timer CircuitVinooja cОценок пока нет

- 355 - EC8451 Electromagnetic Fields - 2 Marks With Answers 1 PDFДокумент32 страницы355 - EC8451 Electromagnetic Fields - 2 Marks With Answers 1 PDFBala913100% (1)

- ECD Lab EEC 752Документ17 страницECD Lab EEC 752juhi99360% (5)

- A Presentation On Semiconductor Memories PDFДокумент112 страницA Presentation On Semiconductor Memories PDFSarthak RoyОценок пока нет

- Ec 3 Lab Viva QuestionsДокумент4 страницыEc 3 Lab Viva QuestionsDeepti Chandrasekharan0% (1)

- TM4C123G LaunchPad WorkshopДокумент336 страницTM4C123G LaunchPad Workshopmail87523Оценок пока нет

- Delay Time Estimation in Digital DesignДокумент12 страницDelay Time Estimation in Digital DesignSandeep PaulОценок пока нет

- Ec8261 Circuits and Devices LaboratoryДокумент1 страницаEc8261 Circuits and Devices LaboratoryJ.Gowri Shankar0% (1)

- LIC+COM Lab Manual - 17ECL48Документ58 страницLIC+COM Lab Manual - 17ECL48Surendra K V100% (4)

- Electronic Jewellery Security Alarm System Using 8085 MicroprocessorДокумент8 страницElectronic Jewellery Security Alarm System Using 8085 MicroprocessorAnand PrajapatiОценок пока нет

- BS Lab Manual R18 PDFДокумент113 страницBS Lab Manual R18 PDFKamarthi VanithaОценок пока нет

- 8051 MicrocontrollerДокумент32 страницы8051 MicrocontrollerRachit Sharma91% (11)

- RC OscillatorДокумент8 страницRC OscillatorRavi TejaОценок пока нет

- NotesДокумент43 страницыNotespriya dharshiniОценок пока нет

- EC6711 Embedded Lab Student Manual 19-20 Odd Sem PDFДокумент142 страницыEC6711 Embedded Lab Student Manual 19-20 Odd Sem PDFJayamani KrishnanОценок пока нет

- Ge8261 - Engineering Practices LabДокумент33 страницыGe8261 - Engineering Practices LabtkkarunyaОценок пока нет

- 17Документ9 страниц17Salni Kumari33% (3)

- Digital Storage OscilloscopeДокумент9 страницDigital Storage OscilloscopeamrithaОценок пока нет

- EI2353-Digital System DesignДокумент13 страницEI2353-Digital System DesignSanthosh KumarОценок пока нет

- Ec 2252 Communication Theory Lecture NotesДокумент120 страницEc 2252 Communication Theory Lecture NotesChoco BoxОценок пока нет

- Understanding electromagnetic compatibility through coupling mechanismsДокумент10 страницUnderstanding electromagnetic compatibility through coupling mechanismsPriya RaviОценок пока нет

- Vlsi PDFДокумент81 страницаVlsi PDFShruthiОценок пока нет

- 8051Документ141 страница8051sudhinnnОценок пока нет

- UMM AL-QURA UNIVERSITY Digital Electronics Lab ManualДокумент37 страницUMM AL-QURA UNIVERSITY Digital Electronics Lab ManualPECMURUGAN100% (1)

- Ece VI Digital Communication 10ec61 NotesДокумент252 страницыEce VI Digital Communication 10ec61 NotesNiharika Korukonda100% (1)

- EMBEDDED BASED Automatic AUDITORIUM CONTROLLER 0TH REVДокумент14 страницEMBEDDED BASED Automatic AUDITORIUM CONTROLLER 0TH REVspringsource100% (1)

- Antenna Synthesis and Continuous SourcesДокумент51 страницаAntenna Synthesis and Continuous Sourcesomnidirectional12367% (3)

- MOSFET-Internal Capacitances PDFДокумент11 страницMOSFET-Internal Capacitances PDFJayanth SrirangaОценок пока нет

- 555 Timer Final ReportДокумент36 страниц555 Timer Final ReportRavi Dubey100% (1)

- EC6711-Embedded Laboratory Uploaded by PRABHU.SДокумент66 страницEC6711-Embedded Laboratory Uploaded by PRABHU.Sprabhu s100% (2)

- GSM Interfacing With 8051 MicrocontrollerДокумент5 страницGSM Interfacing With 8051 MicrocontrollerJatin KumarОценок пока нет

- Microprocessor ProgramДокумент97 страницMicroprocessor ProgramPaulОценок пока нет

- VLSI DesignДокумент18 страницVLSI Designkishorereddy416Оценок пока нет

- Fpga ManualДокумент7 страницFpga ManualRahul SharmaОценок пока нет

- Measurements and InstrumentationДокумент54 страницыMeasurements and InstrumentationVikas PsОценок пока нет

- Program For Interfacing 8279: 1. 8085 Microprocessor Kit 2. 8279 Interfacing Module 3. Power SupplyДокумент21 страницаProgram For Interfacing 8279: 1. 8085 Microprocessor Kit 2. 8279 Interfacing Module 3. Power SupplySubhashini MurugesanОценок пока нет

- CCD Detectors LectureДокумент69 страницCCD Detectors Lecturebozadeda100% (1)

- Arduino Based Radar SystemДокумент22 страницыArduino Based Radar SystemMayank MrinalОценок пока нет

- JLTsДокумент67 страницJLTsJawar SinghОценок пока нет

- Radio PillДокумент4 страницыRadio PillsaranyaammuОценок пока нет

- Timers in 8051: How and Why to Use ThemДокумент5 страницTimers in 8051: How and Why to Use ThemKaran AroraОценок пока нет

- Measuring instruments: definitions and applicationsДокумент25 страницMeasuring instruments: definitions and applicationsShivaniОценок пока нет

- Microwave EnggДокумент4 страницыMicrowave EnggasiffarookiОценок пока нет

- VLSI Ch4 DelayДокумент27 страницVLSI Ch4 Delayជើងកាង ភូមិОценок пока нет

- VSWR Measurement, Microwave Engineering, Microwave Measurement, Power Meter, Measurement of Standing Wave PatternsДокумент16 страницVSWR Measurement, Microwave Engineering, Microwave Measurement, Power Meter, Measurement of Standing Wave PatternsvlsijpОценок пока нет

- Eca NotesДокумент220 страницEca NotesKiranmai KonduruОценок пока нет

- The Fundamentals of Signal Transmission: Optical Fibre, Waveguides and Free SpaceОт EverandThe Fundamentals of Signal Transmission: Optical Fibre, Waveguides and Free SpaceОценок пока нет

- Aptitude Tests Guide - Mental Ability, Problem Solving, Data InterpretationДокумент1 страницаAptitude Tests Guide - Mental Ability, Problem Solving, Data InterpretationKarthikeyan_Go_9525Оценок пока нет

- Tnpsc2a PDFДокумент26 страницTnpsc2a PDFArvind HarikrishnanОценок пока нет

- Tnpsc2a PDFДокумент26 страницTnpsc2a PDFArvind HarikrishnanОценок пока нет

- SyllabusДокумент118 страницSyllabusecessecОценок пока нет

- Ec 2253 Electromagnetic Fields L T P C 3 1 0 4Документ2 страницыEc 2253 Electromagnetic Fields L T P C 3 1 0 4Karthikeyan_Go_9525Оценок пока нет

- Transmission Lines and WaveguidesДокумент1 страницаTransmission Lines and WaveguidesKarthikeyan_Go_95250% (1)

- Ec 6011Документ8 страницEc 6011Karthikeyan_Go_9525Оценок пока нет

- Microprocessor and Microcontroller Lab Viva QuestionsДокумент2 страницыMicroprocessor and Microcontroller Lab Viva QuestionsKarthikeyan_Go_9525Оценок пока нет

- ECE II To VIIIДокумент119 страницECE II To VIIIEce ThirdyearОценок пока нет

- GATE SyllabusДокумент2 страницыGATE SyllabusVenkatesh KaulgudОценок пока нет

- De SyllabusДокумент2 страницыDe SyllabusKarthikeyan_Go_9525Оценок пока нет

- Aakash For Education Workshop Brochure PDFДокумент2 страницыAakash For Education Workshop Brochure PDFHaribhaskar GovindarajuluОценок пока нет

- COA-Virtual MemoryДокумент30 страницCOA-Virtual MemorySushrutОценок пока нет

- Fuelino Service Commands V1.1 20161027Документ16 страницFuelino Service Commands V1.1 20161027Muhamad IrfanОценок пока нет

- Chapter 2 COM101Документ5 страницChapter 2 COM101Christean Val Bayani ValezaОценок пока нет

- Design and Analysis of CMOS Based 6T SRAM Cell at Different TechnologyДокумент6 страницDesign and Analysis of CMOS Based 6T SRAM Cell at Different TechnologyRaj sambhavОценок пока нет

- OS Memory Management MCQs - Swapping Processes & Memory AllocationДокумент46 страницOS Memory Management MCQs - Swapping Processes & Memory AllocationMichael PeterОценок пока нет

- Dot Matrix 23 XXДокумент204 страницыDot Matrix 23 XXhatchett927Оценок пока нет

- Main Memory Databases: Faster Access with Volatility RiskДокумент12 страницMain Memory Databases: Faster Access with Volatility RiskShrutika ChawlaОценок пока нет

- Digital Electronics NotesДокумент29 страницDigital Electronics NotesHimanshu KhanduriОценок пока нет

- B-84175EN/03 Troubleshooting: Figure 3.7.1-1 LED On The Main BoardДокумент6 страницB-84175EN/03 Troubleshooting: Figure 3.7.1-1 LED On The Main Boardkaori quinteroОценок пока нет

- A Translation Lookaside BufferДокумент16 страницA Translation Lookaside Bufferarpana0709Оценок пока нет

- Flashattention: Fast and Memory-Efficient Exact Attention With Io-AwarenessДокумент34 страницыFlashattention: Fast and Memory-Efficient Exact Attention With Io-AwarenessMarcos CostaОценок пока нет

- CGS - 1100 Introduction To Computer ApplicationsДокумент23 страницыCGS - 1100 Introduction To Computer Applicationsalif perdanaОценок пока нет

- Booting Process (2) : Taku ShimosawaДокумент123 страницыBooting Process (2) : Taku ShimosawaSudharshan SОценок пока нет

- IBM 5170 Technical Reference 6280070 SEP85 Page109Документ503 страницыIBM 5170 Technical Reference 6280070 SEP85 Page109ChocoFruitОценок пока нет

- Question and AnswersДокумент57 страницQuestion and AnswersPate MtindyaОценок пока нет

- D 2 Uf 4 SPLДокумент56 страницD 2 Uf 4 SPLKurdo KurdОценок пока нет

- Micro - 51 Eb (User)Документ298 страницMicro - 51 Eb (User)maskply100% (1)

- SH79F085 SinowealthДокумент97 страницSH79F085 SinowealthMiguel RamirezОценок пока нет

- Qualified Vendors List (QVL) (Vermeer CPU)Документ13 страницQualified Vendors List (QVL) (Vermeer CPU)Олександр Вікторович РоманюкОценок пока нет

- Computer and Internet MCQs For All Competitive ExamsДокумент18 страницComputer and Internet MCQs For All Competitive ExamsSanam FatimaОценок пока нет

- 8085 ArchitectureДокумент17 страниц8085 ArchitectureSamaira Shahnoor ParvinОценок пока нет

- Hynix H5ANAG4 (8 6) NCJR (Rev1.4)Документ47 страницHynix H5ANAG4 (8 6) NCJR (Rev1.4)dong yiningОценок пока нет

- Chapter 9 MemoryДокумент28 страницChapter 9 MemoryBinod ManandharОценок пока нет

- Introduction of Direct Memory Access (DMA)Документ14 страницIntroduction of Direct Memory Access (DMA)ShivanjaliОценок пока нет

- Why I/O memory must be 512-byte aligned for O_DIRECT transfersДокумент2 страницыWhy I/O memory must be 512-byte aligned for O_DIRECT transferspreetamnОценок пока нет

- SEC - KMFN60012B-B214 221F 11.5x13 - 1.00.00 - FinalДокумент152 страницыSEC - KMFN60012B-B214 221F 11.5x13 - 1.00.00 - Finaldong yiningОценок пока нет

- Chapter 8: Main Memory: Silberschatz, Galvin and Gagne ©2013 Operating System Concepts - 9 EditionДокумент54 страницыChapter 8: Main Memory: Silberschatz, Galvin and Gagne ©2013 Operating System Concepts - 9 EditionnitishaОценок пока нет

- RAMДокумент9 страницRAMSourin SahaОценок пока нет

- 28f512 PDFДокумент35 страниц28f512 PDFHenryHutabaratОценок пока нет

- Computer Memory: TypesДокумент3 страницыComputer Memory: TypesRam Krishna AdhikariОценок пока нет