Академический Документы

Профессиональный Документы

Культура Документы

MEVD-102 CMOS VLSI Design DEC 2010

Загружено:

Prakash SinhaАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

MEVD-102 CMOS VLSI Design DEC 2010

Загружено:

Prakash SinhaАвторское право:

Доступные форматы

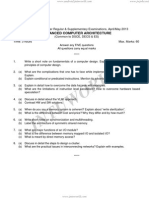

Rajiv Gandhi Proudyogiki Vishwavidyalaya, Bhopal MEVD-102 M.E./M.Tech.

(First Semester) EXAMINATION, Dec 2010

(Grading/Non-Grading)

CMOS VLSI DESIGN

Time: Three Hours Maximum Marks: GS:70 Note: Attempt any two parts from each question.

1. (a) Define abstraction level. Explain Gajeskis Y-chart. What is its significance in VLSI design? (b) Give the VLSI design flow and explain it. (c) What are frontend and backend tools? Explain with suitable examples. Why EDA tools are required for VLSI design? 2. (a) Discuss various types of power dissipation in CMOS circuits. Suggest some methods to minimize power dissipation. (b) Describe parasitic effect in integrated circuits with suitable example. (c) Explain CMOS logic structures and clocking strategies. 3. (a) Explain wafer preparation and its cleaning polishing for VLSI devices. (b) What is CMOS latch problem and how it is avoided? What is birds beak enchrochment? (c) Explain layout design rules and technology related CAD issues. 4. (a) Explain the working of CMOS inverter. Illustrate VTC and explain each region of operation. (b) Describe subsystem design process and design of full adder. (c) Discuss design of ALU subsystem and dynamic shift register. 5. (a) Describe evolution of programmable logic devices with example. (b) Explain computer aided design flow for FPDs. (c) Discuss about the following: i. ii. SPLDs CPLDs and FPGAs

1

Prakash Sinha

Вам также может понравиться

- Engineering Principles of Combat Modeling and Distributed SimulationОт EverandEngineering Principles of Combat Modeling and Distributed SimulationОценок пока нет

- Modeling and Simulation Support for System of Systems Engineering ApplicationsОт EverandModeling and Simulation Support for System of Systems Engineering ApplicationsLarry B. RaineyОценок пока нет

- MEVD-203 VLSI Test and Test Ability June-2012Документ1 страницаMEVD-203 VLSI Test and Test Ability June-2012Prakash SinhaОценок пока нет

- Vidyarthiplus Question Papers: Anna University, ChennaiДокумент3 страницыVidyarthiplus Question Papers: Anna University, ChennaisrgperumalОценок пока нет

- Testing of Vlsi CircuitsДокумент1 страницаTesting of Vlsi CircuitsmittazjОценок пока нет

- 9D06101 Digital System Design-2Документ1 страница9D06101 Digital System Design-2jayaram_le402Оценок пока нет

- MEVD-203 VLSI Test and Testability Dec-2012Документ1 страницаMEVD-203 VLSI Test and Testability Dec-2012Prakash SinhaОценок пока нет

- Answer Any FIVE Questions. All Questions Carry EQUAL MarksДокумент1 страницаAnswer Any FIVE Questions. All Questions Carry EQUAL MarksUday KumarОценок пока нет

- VLSIDesignДокумент5 страницVLSIDesignVenkatesh KolatiОценок пока нет

- MSC IT QuestionsДокумент7 страницMSC IT QuestionsthangaprakashОценок пока нет

- EC 04 801 Microelectronic Technology JUNE 2009Документ2 страницыEC 04 801 Microelectronic Technology JUNE 2009Maryann JacobОценок пока нет

- OoadДокумент3 страницыOoadBala ChanderОценок пока нет

- VLSI DESIGN Question Bank: Unit 1Документ12 страницVLSI DESIGN Question Bank: Unit 1Babu GundlapallyОценок пока нет

- Advanced Computer Architecture Question PaperДокумент1 страницаAdvanced Computer Architecture Question PaperPrasad KalyanОценок пока нет

- IA 2 VlsidtДокумент2 страницыIA 2 VlsidtAnonymous JnvCyu85Оценок пока нет

- 9D06106c Low Power VLSI DesignДокумент1 страница9D06106c Low Power VLSI Designraju.kprr8862Оценок пока нет

- Jntu MДокумент3 страницыJntu MVijay SagarОценок пока нет

- Testing of Vlsi Circuits: Answer All Questions Each Question Carries 25 MarksДокумент2 страницыTesting of Vlsi Circuits: Answer All Questions Each Question Carries 25 MarksAnonymous gwdxvOcoqОценок пока нет

- WWW - Manaresults.Co - In: (Electronics and Communication Engineering)Документ8 страницWWW - Manaresults.Co - In: (Electronics and Communication Engineering)Adhvay KrishnaОценок пока нет

- 2nd Sessional VLSI DesignДокумент1 страница2nd Sessional VLSI DesignMr. Manoj Kr. Sharma EceОценок пока нет

- 9D06106c Low Power VLSI Design PDFДокумент1 страница9D06106c Low Power VLSI Design PDFVijay Kshatriya HRОценок пока нет

- Embedded Systems Model Question PaperДокумент6 страницEmbedded Systems Model Question PaperSubramanyaAIyerОценок пока нет

- Software EngineeringДокумент32 страницыSoftware EngineeringSanjib DeraОценок пока нет

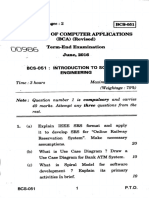

- BCS 051 PDFДокумент24 страницыBCS 051 PDFbnvhjОценок пока нет

- MCS-034 2 MCA (Revised) Term-End Examination December, 2011 Mcs-034: Software EngineeringДокумент2 страницыMCS-034 2 MCA (Revised) Term-End Examination December, 2011 Mcs-034: Software Engineeringriten mitraОценок пока нет

- r7411001 Vlsi DesignДокумент4 страницыr7411001 Vlsi DesignsivabharathamurthyОценок пока нет

- M&SE Dec 2011Документ4 страницыM&SE Dec 2011simalaraviОценок пока нет

- M.tech Algorithms For Vlsi Design AutomationДокумент1 страницаM.tech Algorithms For Vlsi Design AutomationsrinivasОценок пока нет

- 9D06106c Lower Power VLSI DesignДокумент1 страница9D06106c Lower Power VLSI Designjbsng123Оценок пока нет

- Previous Question PapersДокумент4 страницыPrevious Question Papersshaker423Оценок пока нет

- Vlsi Vlsi Design Dec 2020Документ2 страницыVlsi Vlsi Design Dec 2020Margoob TanweerОценок пока нет

- FPGA Based System DesignДокумент2 страницыFPGA Based System Designammayi9845_930467904Оценок пока нет

- Ques SetДокумент3 страницыQues SetTECH IS FUNОценок пока нет

- Time: 3 Hours Maximum Marks: 100 (Weightage: 75%) Note: Question No. 1 Is Compulsory. Attempt Any Three Questions From The RestДокумент2 страницыTime: 3 Hours Maximum Marks: 100 (Weightage: 75%) Note: Question No. 1 Is Compulsory. Attempt Any Three Questions From The Restriten mitraОценок пока нет

- EC2354 - VLSI DesignДокумент2 страницыEC2354 - VLSI DesignSriramОценок пока нет

- Mtech. Precision EngineeringДокумент5 страницMtech. Precision Engineeringsimalaravi100% (1)

- 16ec5507 TT Q BankДокумент5 страниц16ec5507 TT Q BankRAJESH SAMAОценок пока нет

- Algorithms For Vlsi Design Automation - b0609Документ1 страницаAlgorithms For Vlsi Design Automation - b0609Amy OliverОценок пока нет

- Summer 2021 AMIIW Question PapersДокумент32 страницыSummer 2021 AMIIW Question PapersRiyaz AhmedОценок пока нет

- EM506 VLSI ArchitectureДокумент5 страницEM506 VLSI ArchitecturePrakash Velayudham VОценок пока нет

- Ajay Kumar Garg Engineering College, Ghaziabad: Department of ITДокумент2 страницыAjay Kumar Garg Engineering College, Ghaziabad: Department of ITkhushibansal211Оценок пока нет

- MCS-034 MCA (Revised) ON Term-End Examination June, 2014 0 Mcs-034: Software EngineeringДокумент2 страницыMCS-034 MCA (Revised) ON Term-End Examination June, 2014 0 Mcs-034: Software Engineeringriten mitraОценок пока нет

- BCS 051Документ2 страницыBCS 051Rakesh KohliОценок пока нет

- MCS-014 June2022 - June2023Документ8 страницMCS-014 June2022 - June2023giyori6960Оценок пока нет

- Se Prev PapersДокумент16 страницSe Prev PapersAbd 17Оценок пока нет

- 54105-Mt-Vlsi Technology and DesignДокумент2 страницы54105-Mt-Vlsi Technology and DesignSrinivasa Rao GОценок пока нет

- Roll No.: B. TechДокумент3 страницыRoll No.: B. TechShivani VarshneyОценок пока нет

- Nr-Vlsi Technology and DesignДокумент2 страницыNr-Vlsi Technology and DesignSudhakar SpartanОценок пока нет

- Set No: 1: Code No: V3219/R07Документ4 страницыSet No: 1: Code No: V3219/R07Gopi Pavan JonnadulaОценок пока нет

- Bit2201 Bbit308 Simulation and ModelingДокумент3 страницыBit2201 Bbit308 Simulation and ModelingMark Joe AburОценок пока нет

- 09-Algorithms For Vlsi Design AutomationДокумент1 страница09-Algorithms For Vlsi Design AutomationroobetОценок пока нет

- Apollo Group of Colleges: Cs 2354 - Advanced Computer ArchitectureДокумент2 страницыApollo Group of Colleges: Cs 2354 - Advanced Computer ArchitectureJagan NathanОценок пока нет

- BCS 051Документ2 страницыBCS 051AnkitSinghОценок пока нет

- Previous PapersДокумент12 страницPrevious PapersKaran SanaОценок пока нет

- IV-i Question Bank (r15)Документ82 страницыIV-i Question Bank (r15)kd17209Оценок пока нет

- Systems Engineering Principles and PracticeОт EverandSystems Engineering Principles and PracticeРейтинг: 3.5 из 5 звезд3.5/5 (4)

- Mathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsОт EverandMathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsRoderick MelnikОценок пока нет

- Medc-301 (A) Information Theory and Coding Feb 2009 PDFДокумент2 страницыMedc-301 (A) Information Theory and Coding Feb 2009 PDFPrakash SinhaОценок пока нет

- Medc-301 (A) Information Theory and Coding Feb 2010 PDFДокумент2 страницыMedc-301 (A) Information Theory and Coding Feb 2010 PDFPrakash SinhaОценок пока нет

- MTech VLSI Design 3rd Sem SyllabusДокумент4 страницыMTech VLSI Design 3rd Sem SyllabusPrakash SinhaОценок пока нет

- MTech VLSI Design 1st Sem SyllabusДокумент5 страницMTech VLSI Design 1st Sem SyllabusPrakash Sinha100% (1)

- ME Digital Communication 2nd Sem SyllabusДокумент5 страницME Digital Communication 2nd Sem SyllabusPrakash SinhaОценок пока нет

- MEVD-205 Embedded Computing System Design June-2012Документ1 страницаMEVD-205 Embedded Computing System Design June-2012Prakash SinhaОценок пока нет

- TMH EmbeddedДокумент49 страницTMH EmbeddedSRINIVASANОценок пока нет

- Mevd/medc-101 Advanced Mathematics Dec-2010Документ2 страницыMevd/medc-101 Advanced Mathematics Dec-2010Prakash SinhaОценок пока нет

- MEDC-104 Vlsi Design Dec-2010Документ2 страницыMEDC-104 Vlsi Design Dec-2010Prakash SinhaОценок пока нет

- MEVD-104 DIGITAL SIGNAL PROCESSING RGPV Dec-2011Документ2 страницыMEVD-104 DIGITAL SIGNAL PROCESSING RGPV Dec-2011Prakash SinhaОценок пока нет

- MEVD-201 (2nd Sem) VLSI TECHNOLOGY June-2012Документ1 страницаMEVD-201 (2nd Sem) VLSI TECHNOLOGY June-2012Prakash SinhaОценок пока нет

- MEVD-103 ADVANCED LOGIC DESIGN Dec-2011Документ2 страницыMEVD-103 ADVANCED LOGIC DESIGN Dec-2011Prakash SinhaОценок пока нет