Академический Документы

Профессиональный Документы

Культура Документы

FSM 1

Загружено:

Ali AhmadОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

FSM 1

Загружено:

Ali AhmadАвторское право:

Доступные форматы

1

VeriIog HDL (EE 499/599 CS 499/599) 2004 AMIS

Section 14

ShiIt Registers

Einite State Machines (ESM)

2

VeriIog HDL (EE 499/599 CS 499/599) 2004 AMIS

ShiIt Registers

ShiIt Registers are a

useIuI part oI digitaI

design in:

SeriaI to ParaIIeI

Conversion.

Pattern Detection

EIement Extraction

Etc.

3

VeriIog HDL (EE 499/599 CS 499/599) 2004 AMIS

ShiIt Registers SeriaI to ParaIIeI

The data input stream is

scaIar (1-bit) the data

output stream is an 8-bit

vector.

The data output cIock

wiII be 1/8

th

the speed oI

the input cIock.

moduIe sertopar (DOUT.DIN.INCLK.OUTCLK.RESET);

input DIN. INCLK. OUTCLK. RESET;

output |7:0] DOUT;

reg |7:0] DOUT. shItreg;

aIways (posedge INCLK or posedge RESET) begin

iI (RESET) shItreg 0;

eIse begin

shItreg|7] shItreg|6];

shItreg|6] shItreg|5];

shItreg|5] shItreg|4];

shItreg|4] shItreg|3];

shItreg|3] shItreg|2];

shItreg|2] shItreg|1];

shItreg|1] shItreg|0];

shItreg|0] DIN;

end

end

aIways (posedge OUTCLK or posedge RESET) begin

iI (RESET) DOUT 0;

eIse DOUT shItreg;

end

endmoduIe

4

VeriIog HDL (EE 499/599 CS 499/599) 2004 AMIS

ShiIt Registers SeriaI to ParaIIeI

AIternate Eorm Ior ShiIt

Register.

Move bIocks when

shiIting rather than bits.

moduIe sertopar (DOUT.DIN.INCLK.OUTCLK.RESET);

input DIN. INCLK. OUTCLK. RESET;

output |7:0] DOUT;

reg |7:0] DOUT. shItreg;

aIways (posedge INCLK or posedge RESET) begin

iI (RESET) shItreg 0;

eIse begin

shItreg|7:1] shItreg|6:0];

shItreg|0] DIN;

end

end

aIways (posedge OUTCLK or posedge RESET) begin

iI (RESET) DOUT 0;

eIse DOUT shItreg;

end

endmoduIe

5

VeriIog HDL (EE 499/599 CS 499/599) 2004 AMIS

ShiIt Register - SeriaI to ParaIIeI

Testbench

Why is OUTCLK

deIayed by 1ms?

`timescaIe 1ms/10us

moduIe tb;

reg DIN. INCLK. OUTCLK. RESET;

integer i;

wire |7:0] DOUT;

sertopar u1 (DOUT.DIN.INCLK.OUTCLK.RESET);

aIways #10 INCLK INCLK;

initiaI begin

#1;

Iorever #80 OUTCLK OUTCLK;

end

initiaI begin

DIN. INCLK. OUTCLK. RESET} 0;

#1 RESET 1;

#2 RESET 0;

Ior (i 0; i 2048; i i 1) begin

(negedge INCLK) DIN $random;

end

#100 $Iinish;

end

endmoduIe

6

VeriIog HDL (EE 499/599 CS 499/599) 2004 AMIS

ShiIt Registers Pattern Detection

PATTERNMATCH wiII

go high whenever the

vaIue oI the shiIt register

matches the PATTERN

parameter.

Use conditionaI

constructs to Iind patterns

in Data.

moduIe pattern (PATTERNMATCH.DIN.CLK.RESET);

input DIN. CLK. RESET;

output PATTERNMATCH;

parameter PATTERN 8'b11001100;

reg |7:0] shItreg;

assign PATTERNMATCH (PATTERN shItreg) ? 1 : 0;

aIways (posedge CLK or posedge RESET) begin

iI (RESET) begin

shItreg 0;

end

eIse begin

shItreg|7:1] shItreg|6:0];

shItreg|0] DIN;

end

end

endmoduIe

7

VeriIog HDL (EE 499/599 CS 499/599) 2004 AMIS

ShiIt Registers Pattern Detection

Testbench

`timescaIe 1ms/10us

moduIe tb;

reg DIN. CLK. RESET;

integer i;

pattern u1 (PATTERNMATCH.DIN.CLK.RESET);

aIways #10 CLK CLK;

initiaI begin

DIN. CLK. RESET} 0;

#1 RESET 1;

#2 RESET 0;

repeat (2) begin

Ior (i 0; i 64; i i 1) begin

(negedge CLK) DIN $random;

end

#100;

(negedge CLK) DIN 1;

(negedge CLK);

(negedge CLK) DIN 0;

(negedge CLK);

(negedge CLK) DIN 1;

(negedge CLK);

(negedge CLK) DIN 0;

(negedge CLK);

end

#100 $Iinish;

end

endmoduIe

8

VeriIog HDL (EE 499/599 CS 499/599) 2004 AMIS

ShiIt Registers EIement Extraction

Data can be embedded in

synchronization code.

Eor ExampIe 8 bit data

embedded in 5 sync bits

oI Ieading data. and 4

sync bits oI traiIing data.

Data stream :

10110011110101001

moduIe eIementextract (DOUT.DIN.CLK.RESET);

input DIN. CLK. RESET;

output |7:0] DOUT;

reg |16:0] shItreg;

reg |7:0] DOUT;

parameter Ieadingsync 5'b10110;

parameter traiIingsync 4'b1001;

aIways (posedge CLK or posedge RESET) begin

iI (RESET) begin

DOUT 0;

shItreg 0;

end

eIse begin

shItreg|16:1] shItreg |15:0];

shItreg|0] DIN;

iI ((shItreg|16:12] Ieadingsync) & (shItreg|3:0] traiIingsync))

DOUT shItreg|11:4];

eIse

DOUT 'bz;

end

end

endmoduIe

Leading

Sync Data

Data

TraiIing

Sync Data

9

VeriIog HDL (EE 499/599 CS 499/599) 2004 AMIS

ShiIt Registers EIement Extraction

Testbench

`timescaIe 1ms/10us

moduIe tb;

reg CLK. RESET. DIN;

integer i;

wire |7:0] DOUT;

// Ieadingsync 5'b10110; traiIingsync 4'b1001;

eIementextract u1 (DOUT.DIN.CLK.RESET);

aIways #10 CLK CLK;

initiaI begin

RESET.CLK} 0;

#2 RESET 1;

#1 RESET 0;

repeat (40) (negedge CLK) DIN $random;

repeat (10) begin

(negedge CLK) DIN 1;

(negedge CLK) DIN 0;

(negedge CLK) DIN 1;

(negedge CLK);

(negedge CLK) DIN 0;

repeat (8) (negedge CLK) DIN $random;

(negedge CLK) DIN 1;

(negedge CLK) DIN 0;

(negedge CLK);

(negedge CLK) DIN 1;

end // repeat (10)

#100 $stop;

end

endmoduIe

10

VeriIog HDL (EE 499/599 CS 499/599) 2004 AMIS

Einite State Machines

Einite State Machine

EIements:

A state register is deIined

States deIined as

Parameters.

Not necessary. but much

easier to read and program.

State changes handIed in

case statements.

State 0 State 1

N == 1

N == 0

moduIe expIicitIsm (OUT. CLK. IN. RESET);

input CLK. IN. RESET

output OUT;

reg STATE. OUT;

parameter state0 0;

parameter state1 1;

aIways (posedge CLK or posedge RESET)

iI (RESET)

STATE.OUT} 2`b00;

eIse

case (STATE)

state0: begin

OUT 0;

iI (IN) STATE 0;

eIse STATE 1;

end

state1: begin

OUT IN;

STATE 0;

end

deIauIt: STATE.OUT} 2`b00;

endcase

endmoduIe

11

VeriIog HDL (EE 499/599 CS 499/599) 2004 AMIS

Einite State Machines ExampIe 1

State Diagram

dle

(0)

State 1

State 2

OUT2 = 0

if N1 == 1 or N2 == 1: OUT1 = 1

otherwise: OUT1 = 0

N

1

=

=

1

N

2

=

=

1

N1 != 1

OUT2 = 0

OUT1 = 0

N

2

!=

1

OUT2 = 1

OUT1 = 0

12

VeriIog HDL (EE 499/599 CS 499/599) 2004 AMIS

Einite State Machines ExampIe 1

RTL Code

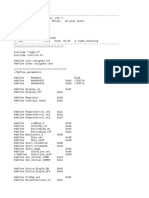

module fsm (OUT1,OUT2,CLK,IN1,IN2,RESET);

input CLK, RESET, IN1, IN2;

output OUT1,OUT2;

reg OUT1, OUT2;

reg [1:0| current_state, next_state;

parameter idle = 0;

parameter state1 = 1;

parameter state2 = 2;

always @ (posedge CLK or posedge RESET)

if (RESET)

current_state <= idle;

else

current_state <= next_state;

always @ (current_state or IN1 or IN2)begin

case(current_state)

idle : begin

OUT2 = 0;

if (IN1 ]] IN2) OUT1 = 1;

else OUT1 = 0;

if(IN1 == 1) next_state = state1;

else next_state = idle;

end

state1 : begin

OUT2 = 1; OUT1 = 0;

if(IN2 == 1) next_state = state2;

else next_state = idle;

end

state2 : begin

OUT2 = 0; OUT1 = 0;

next_state = idle;

end

default : begin

OUT1 = 1'b1; OUT2 = 1'b1;

next_state = idle;

end

endcase

end

endmodule

Some designers wiII expIicitIy encode their state variabIes to avoid gIitches (i.e. Gray code or One-Hot). Others

wiII add synthesis constraints to Iorce encoding. such as:

#Synopsys Design CompiIer ESM Encoding Constraint

setIsmencodingstyIe onehot

At synthesis. this wouId change the state encoding to:

idIe 3`b001;

state1 3`b010;

state2 3`b100;

13

VeriIog HDL (EE 499/599 CS 499/599) 2004 AMIS

Einite State Machine ExampIe 2

TraIIic Light ControIIer

SimpIe intersection Iight

with East-West and

North-South controI.

14

VeriIog HDL (EE 499/599 CS 499/599) 2004 AMIS

Einite State Machine ExampIe 2

DeIauIt (NSGEWR) is

North-South Iight green.

East-West Iight red.

Light wiII change Irom

green to yeIIow aIter 30

seconds.

Light wiII remain yeIIow

Ior 5 seconds.

Both Iights wiII be red

Ior two seconds.

ExternaI timers wiII be

controIIed by the State

Machine.

RESET

EWYNSR

EWGNSR

NSREWR

NSYEWR

NSGEWR

EWRNSR

TMER30 = 1

TMER5 = 1

TMER2 = 1

TMER30 = 1

NSGREEN = 1

NSYELLOW = 0

NSRED = 0

EWGREEN = 0

EWYELLOW = 0

EWRED = 1

TMER30START = 1

TMER5START =0

TMER2START = 0

NSGREEN = 0

NSYELLOW = 1

NSRED = 0

EWGREEN = 0

EWYELLOW = 0

EWRED = 1

TMER30START = 0

TMER5START = 1

TMER2START = 0

NSGREEN = 0

NSYELLOW = 0

NSRED = 1

EWGREEN = 0

EWYELLOW = 0

EWRED = 1

TMER30START = 0

TMER5START = 0

TMER2START = 1

NSGREEN = 0

NSYELLOW = 0

NSRED = 1

EWGREEN = 1

EWYELLOW = 0

EWRED = 0

TMER30START = 1

TMER5START = 0

TMER2START = 0

NSGREEN = 0

NSYELLOW = 0

NSRED = 1

EWGREEN = 0

EWYELLOW = 1

EWRED = 0

TMER30START = 0

TMER5START = 1

TMER2START = 0

TMER5 = 1

NSGREEN = 0

NSYELLOW = 0

NSRED = 1

EWGREEN = 0

EWYELLOW =

EWRED = 1

TMER30START = 0

TMER5START = 0

TMER2START = 1

TMER2 = 1

15

VeriIog HDL (EE 499/599 CS 499/599) 2004 AMIS

Einite State Machine ExampIe 2

moduIe traIIicIight (NSGREEN. NSYELLOW. NSRED. EWGREEN.

EWYELLOW. EWRED. TIMER30START.

TIMER5START. TIMER2START. CLK. RESET.

TIMER30. TIMER5. TIMER2);

input CLK. RESET. TIMER30. TIMER5. TIMER2;

output NSGREEN. NSYELLOW. NSRED. EWGREEN. EWYELLOW.

EWRED. TIMER30START. TIMER5START. TIMER2START;

reg NSGREEN. NSYELLOW. NSRED. EWGREEN. EWYELLOW.

EWRED. TIMER30START. TIMER5START. TIMER2START;

reg |2:0] STATE. NEXTSTATE;

parameter NSGEWR 0;

parameter NSYEWR 1;

parameter NSREWR 2;

parameter EWGNSR 3;

parameter EWYNSR 4;

parameter EWRNSR 5;

aIways (posedge CLK or posedge RESET) begin

iI (RESET) STATE state0;

eIse STATE NEXTSTATE;

end

aIways (TIMER30. TIMER5. TIMER2. STATE) begin

case (STATE)

NSGEWR : begin

NSGREEN 1;

NSYELLOW 0;

NSRED 0;

EWGREEN 0;

EWYELLOW 0;

EWRED 1;

TIMER30START 1;

TIMER5START 0;

TIMER2START 0;

iI (TIMER30 1) NEXTSTATE NSYEWR;

eIse NEXTSTATE STATE;

end

NSYEWR : begin

NSGREEN 0;

NSYELLOW 1;

NSRED 0;

EWGREEN 0;

EWYELLOW 0;

EWRED 1;

TIMER30START 0;

TIMER5START 1;

TIMER2START 0;

iI (TIMER5 1) NEXTSTATE NSREWR;

eIse NEXTSTATE STATE;

end

NSREWR : begin .

16

VeriIog HDL (EE 499/599 CS 499/599) 2004 AMIS

Einite State Machine ExampIe 2

NSREWR : begin

NSGREEN 0;

NSYELLOW 0;

NSRED 1;

EWGREEN 0;

EWYELLOW 0;

EWRED 1;

TIMER30START 0;

TIMER5START 0;

TIMER2START 1;

iI (TIMER2 1) NEXTSTATE EWGNSR;

eIse NEXTSTATE STATE; end

EWGNSR : begin

NSGREEN 0;

NSYELLOW 0;

NSRED 1;

EWGREEN 1;

EWYELLOW 0;

EWRED 0;

TIMER30START 1;

TIMER5START 0;

TIMER2START 0;

iI (TIMER30 1) NEXTSTATE EWYNSR;

eIse NEXTSTATE STATE; end

EWYNSR : begin

NSGREEN 0;

NSYELLOW 0;

NSRED 1;

EWGREEN 0;

EWYELLOW 1;

EWRED 0;

TIMER30START 0;

TIMER5START 1;

TIMER2START 0;

iI (TIMER5 1) NEXTSTATE EWRNSR;

eIse NEXTSTATE STATE; end

EWRNSR : begin

NSGREEN 0;

NSYELLOW 0;

NSRED 1;

EWGREEN 0;

NWYELLOW 0;

EWRED 1;

TIMER30START 0;

TIMER5START 0;

TIMER2START 1;

iI (TIMER2 1) NEXTSTATE NSGEWR;

eIse NEXTSTATE STATE; end

deIauIt : begin

NSGREEN 1;

NSYELLOW 0;

NSRED 0;

EWGREEN 0;

EWYELLOW 0;

EWRED 1;

TIMER30START 1;

TIMER5START 0;

TIMER2START 0;

NEXTSTATE NSGEWR;

end

endcase

end

endmoduIe

17

VeriIog HDL (EE 499/599 CS 499/599) 2004 AMIS

Einite State Machine ExampIe 2

Synthesis tooI shouId

recognize the state

machine.

=======================================

* HDL Synthesis *

=======================================

Synthesizing Unit <trafficlight>.

Related source file is trafficlight.v.

Found finite state machine <FSM_0>

for signal <STATE>.

--------------------------------------

| States | 6

|

| Transitions | 12

|

| Inputs | 3

|

| Outputs | 9

|

| Reset type | asynchronous

|

| Encoding | automatic

|

| State register | d flip-flops

|

--------------------------------------

Summary:

inferred 1 Finite State Machine(s).

Unit <trafficlight> synthesized.

======================================

18

VeriIog HDL (EE 499/599 CS 499/599) 2004 AMIS

Review

What uses to ShiIt Registers have?

How do you shiIt data through a ShiIt Register?

Are ESMs synthesizabIe?

What is the recommended was to decIare your

state variabIes?

Вам также может понравиться

- KORG N264 N364 Service ManualДокумент14 страницKORG N264 N364 Service Manualjfinnegan87Оценок пока нет

- Verilog Modules For Common Digital FunctionsДокумент30 страницVerilog Modules For Common Digital Functionselle868Оценок пока нет

- Digital Design and Synthesis: Fall 09Документ35 страницDigital Design and Synthesis: Fall 09Lua Dinh ThiОценок пока нет

- Sequential Circuits and Seven Segment Display: Lab Assignment 10Документ7 страницSequential Circuits and Seven Segment Display: Lab Assignment 10Ahmed UzairОценок пока нет

- VerilogДокумент22 страницыVerilogSyurga FathonahОценок пока нет

- EDM18B010 - Expt4-Embedded System Design PracticeДокумент9 страницEDM18B010 - Expt4-Embedded System Design PracticeCHIRAG C M CHIRAG C MОценок пока нет

- CED19I032Документ13 страницCED19I032Pranavram VОценок пока нет

- ERC16064-1 DemoCode 4 Wire SPIДокумент19 страницERC16064-1 DemoCode 4 Wire SPIDVTОценок пока нет

- OrgcmdДокумент13 страницOrgcmdMuhammad Jalal AldeenОценок пока нет

- DSD PPT Usr and CN and Odd DividerДокумент22 страницыDSD PPT Usr and CN and Odd Dividerece19637ec003Оценок пока нет

- Three-Phase Motor Control With STM32F401RET6U: B L D CДокумент34 страницыThree-Phase Motor Control With STM32F401RET6U: B L D Cbokic88Оценок пока нет

- 19" 1U Rack Mounting Auto Gain Multi Port Video Receiver HubДокумент4 страницы19" 1U Rack Mounting Auto Gain Multi Port Video Receiver HubLuis NascimentoОценок пока нет

- Presentation 1Документ7 страницPresentation 1ece19637ec003Оценок пока нет

- CED19I032Документ12 страницCED19I032Pranavram VОценок пока нет

- New Text DocumentДокумент8 страницNew Text DocumentMuneeb AhmadОценок пока нет

- 1769 HSC Program ReferenceДокумент6 страниц1769 HSC Program ReferenceMario HenriqueОценок пока нет

- Isplsi 1024/883: In-System Programmable High Density PLDДокумент13 страницIsplsi 1024/883: In-System Programmable High Density PLDCristiano BruschiniОценок пока нет

- MainДокумент14 страницMainRené Isaac Martínez OlivaОценок пока нет

- Electronics Design Lab Manual - VLSI Prog-V3Документ14 страницElectronics Design Lab Manual - VLSI Prog-V3shanmugasundatamОценок пока нет

- Experiment 4 Stepper Motor Control With Systick Timer: 1 ObjectivesДокумент5 страницExperiment 4 Stepper Motor Control With Systick Timer: 1 ObjectivesEVD18I001 A BALAVIGNESHОценок пока нет

- GSM Based Home AutomationДокумент80 страницGSM Based Home AutomationShashi Kant SainiОценок пока нет

- Verilog HDLДокумент14 страницVerilog HDLAshokkumar GanesanОценок пока нет

- Vlsi Lab ProgramsДокумент14 страницVlsi Lab ProgramsThirumalai TrendchaserОценок пока нет

- TP4-Información AdjuntaДокумент11 страницTP4-Información AdjuntaRasiel Daniel SalinasОценок пока нет

- Interface Verilog CodeДокумент21 страницаInterface Verilog CodeVishwanath B RajashekarОценок пока нет

- uPF1 Monitor Program Listing (Original Scan)Документ59 страницuPF1 Monitor Program Listing (Original Scan)Jose Luis Abasolo MayorОценок пока нет

- Omair Akhtar 120526 Bemts (6A) Assignment 5Документ6 страницOmair Akhtar 120526 Bemts (6A) Assignment 5HammadMehmoodОценок пока нет

- Evl 104 Vlsi Design Lab-I: Ex - No:1 Modeling of Sequential Digital Systems Using VHDLДокумент34 страницыEvl 104 Vlsi Design Lab-I: Ex - No:1 Modeling of Sequential Digital Systems Using VHDLvijithacvijayanОценок пока нет

- DSD Lab 9 HandoutДокумент5 страницDSD Lab 9 HandoutMuhammad AnasОценок пока нет

- Dataflow Modelling: 1) Logic GatesДокумент39 страницDataflow Modelling: 1) Logic Gateslilly jamesОценок пока нет

- Experiment No: 11 Design of 10 Bit Shift Register AIMДокумент8 страницExperiment No: 11 Design of 10 Bit Shift Register AIMPraveen KumarОценок пока нет

- MotorencodersДокумент9 страницMotorencodersapi-398062839100% (1)

- Clock System: Appendix DДокумент21 страницаClock System: Appendix Dmostafa HusseinОценок пока нет

- Main Code Lab 7Документ4 страницыMain Code Lab 7William HuangОценок пока нет

- Assignment3 2021HT80531Документ14 страницAssignment3 2021HT80531crypto.investnmentОценок пока нет

- Test Verification GuideДокумент7 страницTest Verification GuideArchana KoreОценок пока нет

- roject mẫu AVR2Документ58 страницroject mẫu AVR2luuvuduc81Оценок пока нет

- Lab 3 ReportДокумент33 страницыLab 3 ReportdasdasdОценок пока нет

- Fpga Lab Reports 1-8 2Документ17 страницFpga Lab Reports 1-8 2Sohail AfridiОценок пока нет

- STM32F3 TimersДокумент75 страницSTM32F3 TimersVport Port100% (1)

- Systick and Watchdog TimerДокумент31 страницаSystick and Watchdog Timerxa yОценок пока нет

- Main4 CДокумент5 страницMain4 CestonuncahaocurridoОценок пока нет

- Fa20-Bee-150 MP Lab Report - 10Документ6 страницFa20-Bee-150 MP Lab Report - 10Saadat KhanОценок пока нет

- Acer Extensa 4220 4620 - Wistron Biwa - Rev - 2secДокумент42 страницыAcer Extensa 4220 4620 - Wistron Biwa - Rev - 2secMayank Mani SinghОценок пока нет

- For Ideal Relay Case, Compare E K KДокумент6 страницFor Ideal Relay Case, Compare E K KrnellyОценок пока нет

- Homework #9 SolutionДокумент4 страницыHomework #9 Solutionsanjeewa29Оценок пока нет

- Toro Cpu ProjectДокумент10 страницToro Cpu Projectapi-302919798Оценок пока нет

- DC-Motor Speed ControllerДокумент3 страницыDC-Motor Speed ControllerchakralabsОценок пока нет

- Embedded Systems Assignment 2Документ6 страницEmbedded Systems Assignment 2ramrevolt55Оценок пока нет

- Lecture 7Документ48 страницLecture 7tecleador1Оценок пока нет

- Electrical ProjectДокумент8 страницElectrical ProjectUtkarsh DubeyОценок пока нет

- INVDRT035 MoveVelocityRPM FreeДокумент4 страницыINVDRT035 MoveVelocityRPM FreeJosephОценок пока нет

- ST-680 - Installation Manual - EngДокумент28 страницST-680 - Installation Manual - EngTam Ka100% (1)

- Fully Controlled RectifierДокумент18 страницFully Controlled RectifierVipin_amОценок пока нет

- (User-Set Allocation) Deceleration Stop: - INVDRT063 - Stop - FreeДокумент3 страницы(User-Set Allocation) Deceleration Stop: - INVDRT063 - Stop - FreeJosephОценок пока нет

- Evd19i018-Esdp Lab 9Документ18 страницEvd19i018-Esdp Lab 9Jampani sarath chandraОценок пока нет

- Aurduino 12345Документ4 страницыAurduino 12345adershОценок пока нет

- PH Alkalinity ExplainedДокумент4 страницыPH Alkalinity ExplainedDean DsouzaОценок пока нет

- Lectrue # 12 and 13 - 30-04-08Документ26 страницLectrue # 12 and 13 - 30-04-08Ali AhmadОценок пока нет

- AC MaintenanceДокумент21 страницаAC MaintenanceAli AhmadОценок пока нет

- Electrical Theory: Howard W Penrose, PH.D., CMRP InstructorДокумент79 страницElectrical Theory: Howard W Penrose, PH.D., CMRP InstructorSandun LakminaОценок пока нет

- The Purpose of Business Activity: LECTURE # 01 & 02Документ9 страницThe Purpose of Business Activity: LECTURE # 01 & 02Ali AhmadОценок пока нет

- Jan 2008 Course Outline FinanceДокумент5 страницJan 2008 Course Outline FinanceAli AhmadОценок пока нет

- Lecture 2 - 30-01-08Документ17 страницLecture 2 - 30-01-08Ali AhmadОценок пока нет

- The Purpose of Business Activity: LECTURE # 01 & 02Документ9 страницThe Purpose of Business Activity: LECTURE # 01 & 02Ali AhmadОценок пока нет

- Printing The Model:: SimulinkДокумент8 страницPrinting The Model:: SimulinkAli AhmadОценок пока нет

- Matlab Training Session Vii Basic Signal Processing: Frequency Domain AnalysisДокумент8 страницMatlab Training Session Vii Basic Signal Processing: Frequency Domain AnalysisAli AhmadОценок пока нет

- Matlab Training - Basic Control TheoryДокумент10 страницMatlab Training - Basic Control TheoryhamedОценок пока нет

- Matlab Training - SIMULINKДокумент8 страницMatlab Training - SIMULINKAtta RehmanОценок пока нет

- Matlab Training Session Iv Simulating Dynamic Systems: Sampling The Solution EquationДокумент9 страницMatlab Training Session Iv Simulating Dynamic Systems: Sampling The Solution EquationAli AhmadОценок пока нет

- Matlab Training - SIMULINKДокумент8 страницMatlab Training - SIMULINKAtta RehmanОценок пока нет

- Lecture 2Документ26 страницLecture 2Ali AhmadОценок пока нет

- Acknowledgement - 2Документ11 страницAcknowledgement - 2Ali AhmadОценок пока нет

- Matlab Training - Writing M-Files - Scripts and FunctionsДокумент6 страницMatlab Training - Writing M-Files - Scripts and Functionsederdiego2709Оценок пока нет

- Matlab Training Session Iii Numerical Methods: Solutions To Systems of Linear EquationsДокумент14 страницMatlab Training Session Iii Numerical Methods: Solutions To Systems of Linear EquationsAli AhmadОценок пока нет

- Matlab Training Session Ii Data Presentation: 2-D PlotsДокумент8 страницMatlab Training Session Ii Data Presentation: 2-D PlotsAli AhmadОценок пока нет

- Introduction To: Artificial IntelligenceДокумент31 страницаIntroduction To: Artificial IntelligenceAli AhmadОценок пока нет

- Example 5.1: Multiplexer #1 Using OperatorsДокумент10 страницExample 5.1: Multiplexer #1 Using OperatorsAli AhmadОценок пока нет

- Introduction To VHDL: AIR University AU, E-9, IslamabadДокумент29 страницIntroduction To VHDL: AIR University AU, E-9, IslamabadAli AhmadОценок пока нет

- Operators: Introduction To ASIC DesignДокумент6 страницOperators: Introduction To ASIC DesignAli AhmadОценок пока нет

- System On Chips Soc'S & Multiprocessor System On Chips MpsocsДокумент42 страницыSystem On Chips Soc'S & Multiprocessor System On Chips MpsocsAli AhmadОценок пока нет

- Multiply and Accumulate Circuits LabДокумент5 страницMultiply and Accumulate Circuits LabAli AhmadОценок пока нет

- 2-Level Logic ( 0', 1') .: Introduction To ASIC DesignДокумент8 страниц2-Level Logic ( 0', 1') .: Introduction To ASIC DesignAli AhmadОценок пока нет

- Sequential Code in VHDLДокумент42 страницыSequential Code in VHDLAli Ahmad0% (1)

- Small Neural Nets LabДокумент6 страницSmall Neural Nets LabAli AhmadОценок пока нет

- Introduction To ASIC Design: Lab Report InstructionsДокумент1 страницаIntroduction To ASIC Design: Lab Report InstructionsAli AhmadОценок пока нет

- Introduction To ASIC Design: Lab Report StandardsДокумент1 страницаIntroduction To ASIC Design: Lab Report StandardsAli AhmadОценок пока нет

- V1 - Multistage Amplifier N Current MirrorДокумент18 страницV1 - Multistage Amplifier N Current MirrorAshiqur Rahman ASОценок пока нет

- ELTE2.3 Wireless Access Device EA660 Configuration GuideV1.0 (20140414)Документ23 страницыELTE2.3 Wireless Access Device EA660 Configuration GuideV1.0 (20140414)Sebastian StopyraОценок пока нет

- Gesture RobotДокумент11 страницGesture RobotAnonymous jQFCoNОценок пока нет

- Digital Logic Design: Decoder & EncoderДокумент20 страницDigital Logic Design: Decoder & EncoderMd AshiqОценок пока нет

- Design Examples Using The ToolboxДокумент23 страницыDesign Examples Using The Toolboxrajeevjain09Оценок пока нет

- Tablet PCДокумент22 страницыTablet PCbtaleraОценок пока нет

- 04 Introduction To The Cisco IOS PDFДокумент67 страниц04 Introduction To The Cisco IOS PDFamitsinghОценок пока нет

- DriveRack VENU360 Manual 5058681-C OriginalДокумент127 страницDriveRack VENU360 Manual 5058681-C OriginalLuis Bernardo Choque SallamaОценок пока нет

- MODEL PC-252 - Transformer Temperature IndicatorДокумент6 страницMODEL PC-252 - Transformer Temperature IndicatorMKОценок пока нет

- VR-3000 - VR3000-S - Error - Codes SW 2.54Документ2 страницыVR-3000 - VR3000-S - Error - Codes SW 2.54gОценок пока нет

- N-Split 85MHz - RBU Network Tech Presentation V10aДокумент28 страницN-Split 85MHz - RBU Network Tech Presentation V10aAntonio RondinelliОценок пока нет

- Data Communication LabДокумент16 страницData Communication LabdicijОценок пока нет

- LED Codes and Error Codes in P SeriesДокумент15 страницLED Codes and Error Codes in P Seriesamits2034Оценок пока нет

- SYSTRON DONNER 5000A Operation ManualДокумент42 страницыSYSTRON DONNER 5000A Operation ManualRon CarlsonОценок пока нет

- Introduction To Computer SystemsДокумент92 страницыIntroduction To Computer SystemsAmit SahaОценок пока нет

- DVSR v1-5 EN-0906Документ114 страницDVSR v1-5 EN-0906Prana RajОценок пока нет

- UCPДокумент0 страницUCPcontact_egypt2Оценок пока нет

- WP DP Series Brochure 20210115Документ4 страницыWP DP Series Brochure 20210115baraiyahetal26Оценок пока нет

- BIOS and DOS Interrupts: Basic Input /outpu System Disk Operating SystemДокумент17 страницBIOS and DOS Interrupts: Basic Input /outpu System Disk Operating SystemTeddy112Оценок пока нет

- Encoder OutputsДокумент5 страницEncoder OutputsfarmarahОценок пока нет

- Datasheet Diodos 1W y 2WДокумент2 страницыDatasheet Diodos 1W y 2WAnonymous BQOxf8XX58Оценок пока нет

- Foxess 10,5K G10500 220VДокумент2 страницыFoxess 10,5K G10500 220Valex reisОценок пока нет

- M24C64-W M24C64-R M24C64-F M24C64-Df: 64-Kbit Serial I C Bus EepromsДокумент50 страницM24C64-W M24C64-R M24C64-F M24C64-Df: 64-Kbit Serial I C Bus EepromsMax SDKОценок пока нет

- Control Industrial PDFДокумент2 страницыControl Industrial PDFJose David Alava CedeñoОценок пока нет

- Ex 2200 PDFДокумент2 страницыEx 2200 PDFLindaОценок пока нет

- Odi 065R16NB17JJJ GДокумент1 страницаOdi 065R16NB17JJJ GMARCO ROALCABAОценок пока нет

- VAMP 140. Overcurrent - and Earthfault Relay. Technical Data SheetДокумент20 страницVAMP 140. Overcurrent - and Earthfault Relay. Technical Data SheetIbrar Hussain100% (1)

- B. Write T On The Blank If The Statement Is True and F If The Statement Is FalseДокумент1 страницаB. Write T On The Blank If The Statement Is True and F If The Statement Is FalsePatricia Ann Dulce AmbataОценок пока нет

- Electrical Curriculum (List of 1-5 Year Courses) - 1Документ7 страницElectrical Curriculum (List of 1-5 Year Courses) - 1migadОценок пока нет