Академический Документы

Профессиональный Документы

Культура Документы

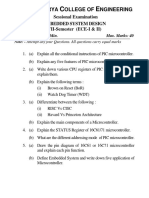

UNIT-V Realization of State Machines

Загружено:

Narasimha Murthy YayavaramАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

UNIT-V Realization of State Machines

Загружено:

Narasimha Murthy YayavaramАвторское право:

Доступные форматы

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.

com

UNIT-V : REALIZATION OF STATE MACHINE INTRODUCTION: A sequential circuit is also known as an Algorithmic State Machine

(ASM) or simply a State Machine. These names are often used when the sequential circuit is used to control a digital system that carries out a step-by-step procedure or algorithm. The state graphs are used to define state machines for controlling digitial circuits like adders, multipliers, and dividers. As an alternative to using state graphs, a special type of flowchart, called a State Machine flowchart or SM Chart, is also widely used to describe the behavior of a state machine. Flowcharts are useful in software design, similarly SM Charts are useful in the state machine

hardware design of digital systems. This is a also special type of a flow chart

flowchart, or SM chart for short. SM charts are also called ASM (algorithmic state machine) charts. These SM Charts have many advantages. It is often easier to understand the operation of a digital system by inspection of the SM chart instead of the equivalent state graph. A given SM chart can be converted into several equivalent forms, and each form leads directly to a hardware realization. SM Charts : A State Machine chart which is similar to a flow-chart is used to describe the behavior of a digital system or state machine.Stae Machine charts are also known as Algorithmic State Machine(ASM) Chart. The ASM chart has many advantages over state graphs. It is also easy to understand the operation of a digital system by the inspection of the SM Chart rather than the state graph. The basic difference between an ordinary flow chart and SM chart is that ,certain specific rules must be followed to constructing the SM chart ,but no such specific rules are to be followed in the case of flow-chart. A State Machine Chart can be constructed from the State Graph of a Digital system. There are three important components in an SM Chart. They are (i)State Box (ii) Decision Box and (iii) Conditional output Box .

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

State Box : The state box contains a state name followed by a slash(/) and an optional output list. After the state assignment ,a state code must be placed outside the box at the top. Decision Box: A decision box is represented by the diamond shape symbol with true and False branches. The condition placed in the box is a Boolean expression that is evaluated to determine which branch is true.

(a).State box

(b).Decision box

(c).Conditional Output box

Conditional output Box: The conditional output box , which has curved ends contains a conditional output list. The conditional outputs depend on both the state of the system and inputs. Specific Rules for constructing SM Chart: Certain rules must be followed while constructing an SM block. For every valid combination of input variables ,there must be exactly one exit path defined .This is necessary because ,each allowable input combination must lead to a single next state. The second rule is no internal feedback within an SM block is allowed. This is shown in the diagram below.

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

Wrong feedback Conversion of State graph into Equivalent SM Chart:

Correct feedback

Let us consider a state graph with three states S0, S1 and S2 as shown below. Here Za,Zb and Zc are the Moore outputs. And Z1 ,Z2 are the Mealy outputs which change after a state change or input change.

The Moore outputs change only after a state change. The equivalent state chart is shown below.

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

Derivation of SM Charts: To derive the SM chart for any digital system ,first its block diagram must be drawn.Next ,the required input,output signals must be defined .Then the SM Chart must be constructed ,that tests the input signals and generates the proper sequence of the output signals. Let us consider the case of a binary Multiplier .In the binary Multiplier ,there will be a add shift controller which generates required sequence of add and shift signals.The counter counts the number of shifts and outputs K=1 ,just before the last shift occurs. The SM Chart for Binary Multiplier is shown below.

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

In the SM chart ,in the state S0,where the start signal St is 1 ,the registers are loaded.In S1,the Multiplier bit M is tested. If M=1, an add signal is generated and the shift signal is generated and K is tested. If K=1 ,this will be the last shift and the next state is S3.

In S2, a shift signal is generated ,since a shift must always follow and add . If K=1 ,the network goes to S3 at the time of the last shift, otherwise ,the next state is S1. In S3 ,the Done signal is turned ON. Dice Game: Let us derive the SM chart for the electronic dice game. Figure below shows the block diagram for the dice game. Here two counters are used to simulate the roll of the dice. Each counter

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

counts in the sequence 1, 2, 3, 4, 5, 6, 1, 2, . . . . Thus, after the roll of the dice, the sum of the values in the two counters will be in the range 2 through 12.

The two important rules of the game are as follows: 1. After the first roll of the dice, the player wins if the sum is 7 or 11. He loses if the sum is 2, 3, or 12. Otherwise, the sum which he obtained on the first roll is referred to as his point, and he must roll the dice again. 2. On the second or subsequent roll of the dice, he wins if the sum equals his point, and he loses if the sum is 7. Otherwise, he must roll again until he finally wins or loses. The inputs to the dice game come from two push buttons, Rb (roll button) and Reset. Reset is used to initiate a new game. When the roll button is pushed, the dice counters count at a high speed, so the values cannot be read on the display. When the roll button is released, the values in the two counters are displayed and the game can proceed. Because the button is released at a random time, this simulates a random roll of the dice. If the Win light or Lose light is not on, the player must push the roll button again. The components for the dice game shown in the block diagram include an adder which adds the two counter outputs, a register to store the point, test logic to determine conditions for win or lose, and a control circuit. The input signals to the control circuit are defined as follows:

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

D7 = 1 if the sum of the dice is 7 D711 = 1 if the sum of the dice is 7 or 11 The SM Chart for Dice game is shown below.

D2312 = 1 if the sum of the dice is 2, 3, or 12 Eq = 1 if the sum of the dice equals the number stored in the point register Rb = 1 when the roll button is pressed Reset = 1 when the reset button is pressed The outputs from the control circuit are defined as follows: Roll = 1 enables the dice counters Sp = 1 causes the sum to be stored in the point register

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

Win = 1 turns on the win light Lose = 1 turns on the lose light In the SM Chart control circuit waits in state S0 until the roll button is pressed (Rb = 1). Then, it goes to state S1, and the roll counters are enabled as long as Rb = 1. As soon as the roll button is released (Rb = 0), D711 is tested. If the sum is 7 or 11, the circuit goes to state S2 and turns on the Win light; otherwise, D2312 is tested. If the sum is 2, 3, or 12, it goes to state S3 and turns on the Lose light; otherwise, the signal Sp becomes 1, and the sum is stored in the point register. It then enters S4 and waits for the player to roll the dice again. In S5, after the roll button is released, if Eq = 1, the sum equals the point and state S2is entered to indicate a win. If D7 = 1, the sum is 7 and S3 is entered to indicate a loss. Otherwise, the control returns to S4 so that the player can roll again. When in S2 or S3, the game is reset to S0 when the Reset button is pressed Realization of SM Charts : The realization of SM charts is done using similar methods used to to realize state graphs. The realization consists of a combinational sub network ,together with flip-flops for storing the states of the network. Sometimes it is possible to identify equivalent states in an SM chart and eliminate redundant states. However, in an SM chart all inputs are not tested in every state, as it makes makes the reduction procedure more difficult. Even if the number of states in an SM chart can be reduced, it is not always desirable to do so because combining states may make the SM chart more difficult to interpret. Before deriving next-state and output equations from an SM chart, a state assignment must be made. The best way of making the assignment depends on how the SM chart is realized. If gates and flip-flops (or the equivalent PLD realization) are used, the guideline method of state assignment is more useful.

As an example let us consider the realization of a binary counter using one PLA and two D-Flipflops.The SM chart of the Multiplier is shown below.

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

Next, the multiplier whose SM chart is shown above is implemented using a PLA and two D flip-flops connected, as shown in figure below. The PLA has five inputs and six outputs. Here binary assignment is made for states.(S0 = 00, S1 = 01,etc.). Each row in the PLA table corresponds to one of the link paths in the SM chart. Because S0 has two exit paths, the table has two rows for present state S0. Because only St is tested in S0, M and K are dont-cares as indicated by dashes.

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

The first row corresponds to the St = 0 exit path, so the next state is 00 and all outputs are 0. In the second row, St = 1, so the next state is 01 and the other PLA outputs are 1000. Because St is not tested in states S1, S2, and S3, St is a dont-care in the corresponding rows. The outputs for each row can be filled in by tracing the corresponding link paths on the SM chart. For example, the link path from S1 to S2 passes through conditional output Ad when M = 1, so Ad = 1 in this row. Because S2 has a Moore output Sh, Sh = 1 in both of the rows for which AB = 10.

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

Implementation of Dice Game: The SM chart for the dice game controller can be implemented using a PLA and three D flipflops, as shown below in Figure . The PLA has nine inputs and seven outputs.

In state ABC = 000, the next state is A+B+C+ = 000 or 001, depending on the value of Rb. Because state 001 has four exit paths, the PLA table has four corresponding rows. When Rb is 1, Roll is 1 and there is no state change. When Rb = 0 and D711 is 1, the next state is 010.When Rb = 0 and D2312 = 1, the next state is 011. For the link path from state 001to 100, Rb, D711, and D2312 are all 0, and Sp is a conditional output. This path corresponds to row 4 of the PLA table, which has Sp = 1 and A+B+C+ = 100. In state 010, the Win signal is always on, and the next state is 010 or 000, depending on the

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

value of Reset. Similarly, Lose is always on in state 011. In state 101, A+B+C+ = 010 if Eq = 1; otherwise, A+B+C+ = 011 or 100, depending on the value of D7. States110 and 111 are unused, so all inputs and outputs are dont-cares in these states. Alternative Realizations Using Microprogramming: The realization of SM charts for logic circuits using PLAs or PALs or ROMs ,if the number of inputs to the control network is large ,the number of inputs to PLAs or PALs will also become large.This makes the problem more complicated. In such situations certain alternate methods are used where the use of MUX s is considered. In such methods ,the inputs to the PLA are taken from the state register .The control network inputs are given to a MUX instead of directly to PLA. The PLA output has four fields.TEST, NSF ,NST and OUTPUT. The TEST field controls the input MUX ,which selects one of the inputs to be tested.

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

The diagram shows the control network using an input MUX to select the next state.In each state. If this input is zero (False), then second MUX selects the NSF field as the next state. If the input is 1 i.e True , it selects the NST field as the next state. The out-put field is the same as for standard realization. But this SM chart has only Moore outputs.,because the outputs can be function of only of the state of the machine. The PLA table is derived using binary state assignment. The variables Rb,D711,D2312,Eq ,D7 and Reset must be tested. To test these variables an 8 to 1 MUX is used as shown below.

For example when TEST=001 ,Rb is selected. In state S13 the next state is always 0111,so NSF=NST=0111 and the TEST field is dont care. Each row in PLA table corresponds to a link path on the SM chart.

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

For example ,in S2,the test field 110 selects Reset.If Reset =0 ,NSF =0100 is selected and if Reset =1, NST=0000 is selected. In S2 ,the output Win =1 and other outputs are 0. The MUX is used to implement the block diagram shown above.The same block diagram can be modified by replacing the state register with a counter as shown below .

The NSF field is eliminated from the PLA output.The TEST field selects one of the inputs to be tested in each state.If the selected input is true ( 1) the NST field is loaded into the counter.If the selected input is 0 ,the counter is incremented. For each condition box ,for the false branch, the next state is assigned in sequence if possible.If this not possible extra states (called X-states) must be added. This method of implementing SM charts is called Microprogramming. The counter used here is similar to the program counter in a computer ,which provides the address of the next instruction to be executed. The PLA or PAL or ROM output is a micro-instruction ,which is executed by the remaining hardware. Each micro-instruction is like a conditional branch instruction that tests an input and branches to a different address if the test is true, otherwise the next instruction in a sequence is executed.The output field in the micro-instruction is has bits that control the operation of the hardware . LINKED STATE MACHINES: Design of a large & complex sequential machine is always difficult and time consuming. So, a large sequential machine is divided into several smaller machines which are linked together.

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

This makes the problem more simple and easy because it is easy to design and implement smaller machines. One of the submachines is called by the main machine at different points of time.For example ,let us consider two machines A and B where the main machine A executes certain sequence of states until it is ready to call the submachine B. When state SA is reached ,the output signal ZA activates machine B. Then machine B starts executing certain sequence of other states. When it is finished, it outputs ZB before returning to the idle state.

When machine A reaches ZB , it continues to execute other states. This activity is similar to a sub routine calling in software programs. Linked SM Chart for DICE Game: Let us consider the example of Dice Game as a Linked SM Chart. The graph below shows the SM chart for Dice game .In the SM chart Rb is used to control the roll of Dice in states S0 ,S1 and also in S4 and S5.As this function is repeatedly used ,a separate machine for Roll control can be used .So,the SM chart for Dice game is divided in to two linked charts (a) and (b) as shown in the figure (2).The first one (a) is the main control and the (b) is the Roll control.

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

The main control generates an En-roll (Enable rolling) signal in T0 and then waits for a Dn-roll (Done rolling) signal before continuing .A similar action occurs in T1.

Figure (1) The roll control machine waits in state S0 until it gets an En-roll signal from the main dice game control.Then on pressing the roll button (Rb=1) the machine goes to S1 and generates a roll signal .

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

It remains in S1 until Rb=0, in which case the Dn-roll signal is generated and the machine goes back to state S0. When SM Charts are realized using PLAs,the PLA size can be reduced by transforming the SM chart into a form in which only one input is tested in each state. But this has a drawback of increased number of states and reduced speed of operation of the state machine. ONE-HOT DESIGN METHOD : Designing a FSM is the most challenging task for any digital logic designer. One of the key factors for optimizing a FSM design is the choice of state coding, which influences the complexity of the logic functions, the hardware costs of the circuits, timing issues, power usage,

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

etc. There are several methods like Binary encoding, Gray encoding, One-hot encoding etc. The choice of the designer depends on the factors like technology, design specifications, etc. In one-hot encoding only one bit of the state vector is asserted for any given state. All other state bits are zero i.e only one bit is Hot(one) and all other bits are zero. Thus if there are n states then n state flip-flops are required to implement it. As only one bit remains logic high and rest are logic low, it is called as One-hot encoding. Example: If there is a FSM, which has 4 states. Then 4 flip-flops are required to implement the FSM using one-hot encoding. The states will have the following values: S0 - 1000 S1 - 0100 S2 - 0010 S3 - 0001 For the efficient design of a State Machine, it should have minimum number of state variables i.e minimum number of Flip-Flops. In such cases ,functions must be often mapped and

minimized before the design process is completed. Also for such designs ,no direct relations exists between the states of the FSM and NS(Next State) and output functions. So,the best alternative method that greatly reduces the design effort and provides a direct relationship between states of the FSM and the NS and output logic is the One-Hot method. The major advantage of this One-Hot method is that the NS and output functions are generated directly from either the state diagram ,state table or from an ASM chart.No specific state assignment code is needed. Advantages (i)State decoding is simplified, since the state bits themselves can be used directly to check whether the FSM is in a particular state or not. Hence additional logic is not required for decoding, this is extremely advantageous when implementing a big FSM. (ii).Low switching activity, hence resulting low power consumption, and less prone to glitches.

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

(iii).Modifying a design is easier. Adding or deleting a state and changing state transition equations (combinational logic present in FSM) can be done without affecting the rest of the design. (iv).Faster than other encoding techniques. Speed is independent of number of states, and depends only on the number of transitions into a particular state. (v).Finding the critical path of the design is easier (static timing analysis). (vi).One-hot encoding is particularly advantageous for FPGA implementations. If a big FSM design is implemented using FPGA, regular encoding like binary, gray, etc will use fewer flops for the state vector than one-hot encoding, but additional logic blocks will be required to encode and decode the state. But in FPGA each logic block contains one or more flip-flops .So due to presence of encoding and decoding more logics block will be used by regular encoding FSM than one-hot encoding FSM. Disadvantages The only disadvantage of using one-hot encoding is that it required more flip-flops than the other techniques like binary, gray, etc. The number of flip-flops required grows linearly with number of states. For example: If there is a FSM with 38 states. One-hot encoding requires 38 flip-flops where as other require 6 flip-flops only. Using a One-Hot State Assignment : In designing with CPLDs and FPGAs , it is considered that each logic cell contains one or more flip-flops. These flip-flops are there whether we use them or not. This means that it may not be important to minimize the number of flip-flops used in the design. Instead, we should try to reduce the total number of logic cells used and try to reduce the interconnections between cells. When several cells are cascaded to realize a function the propagation delay is increased and the logic runs slower. In order to design faster logic, we should try to reduce the number of cells required to realize each equation. The one-hot state assignment help to solve this. The one-hot assignment uses one flip-flop for each state, so a state machine with N states requires N flip-flops. Exactly one of the flip-flops is set to one (Hot) in each state and all others are rest.

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

Foe example let us consider the implementation of an LUT in FPGA device . The output of the LUT can be written as F= abcd + abcd + abcd + abcd + abcd +----------------------+ abcd Here each one of the term requires one function generator. If we use one-Hot assignment , the system with four states a,b,c,d (S0, S1, S2, and S3) could use four flip-flops (Q0, Q1, Q2, and Q3) with the following state assignment . S0 : Q0 Q1 Q2 Q3 = 1000 , S1: Q0 Q1 Q2 Q3 = 0100 , S2 : Q0 Q1 Q2 Q3 = 0010 and , the remaining 12 combinations are not considered. S3 : Q0 Q1 Q2 Q3 = 0001

The next-state and output equations are written by inspecting the state graph. Consider the partial state graph given in Figure below. In the graph all the four arcs lead into S3, so,there are four conditions under which the next state is S3. These conditions are Present state (PS) = S0 and X1 = 1, PS = S1 and X2 = 1, PS = S2 and X3 = 1, PS = S3 and X4 = 1. The next state of flip-flop Q3 is 1 under these four conditions (and 0 otherwise). Therefore, the next-state equation for Q3 can be written as

Q+3 = X1 (Q0 Q1 Q2 Q3 ) + X2 (Q0 Q1 Q2 Q3) +X3 (Q0 Q1 Q2 Q3 ) + X4 (Q0 Q1 Q2 Q3 )

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

Here as Q0 = 1 means Q1 = Q2 = Q3 = 0, and the Q1 Q2 Q3 term is redundant and so it can be eliminated. Similarly, all of the primed state variables can be eliminated from the other terms, so the next-state equation reduces to Q+3 = X1Q0 + X2Q1 + X3Q2 + X4Q3

In general, when a one-hot state assignment is used, each term in the next-state equation for each flip-flop contains exactly one state variable, and the reduced equation can be written by inspecting the state graph. Similarly, each term in each reduced output equation contains exactly one state variable. Because Z1 = 1 when PS = S0 and X1 = 1, and also when PS = S2 and X3 = 1, we can write that By inspecting the state graph, we can also write that Z2 = X2Q1 + X4Q3 Z1 = X1Q0 + X3Q2.

When a one-hot assignment is used, resetting the system requires that one flip flop be set to 1 instead of resetting all flip-flops to 0. If the flip-flops used do not have a preset input, then we can modify the one-hot assignment by replacing Q0 with Q0 throughout.

The assignments for this are

S0 : Q0 Q1 Q2 Q3 = 0000, S1 : Q0 Q1 Q2 Q3 = 1100, S2: Q0 Q1 Q2 Q3 = 1010, S3: Q0 Q1 Q2 Q3 = 1001

And the modified equations are Q3+ = X1Q0 + X2Q1 + X3Q2 + X4Q3 Z1 = X1Q0 + X3Q2, Z2 = X2Q1 + X4Q3 While designing with CPLDs or FPGAs, one should try both an assignment with a minimum number of state variables and a one-hot assignment to check which one leads to a design with the smallest number of logic cells. Alternatively, if the speed of operation is important, the design which leads to the fastest logic should be chosen. When a one-hot assignment is used, more next-state equations are required, but for some state graphs both the next-state and output

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

equations may contain fewer variables. An equation with fewer variables may require fewer logic cells to realize. The more cells which are cascaded, the longer the propagation delay, and the slower the operation. PETRI NETS : Introduction: Normally in any Finite State Machine or Sequential Machines only one state is active at any time.This type of machine cannot be used to control parallel processes. So, a machine which can have several states active simultaneously is needed.This type of sequential machine which has many states active at an instant of time is called Petri Net . Petri Nets were invented by Carl Adam Petri in the year 1962 .Petri nets have been used in a variety of fields including computer science, chemistry, and biology. Petri nets are a graphical for representing a system in which there are multiple independent activities in progress at the same time. In a finite state machine there is always a single current state that determines which action can next occur. In Petri nets there may be several states, any one of which may evolve by changing the state of the Petri net. Alternatively, some, of even all, of these states may evolve in parallel causing several independent changes to the Petri net to occur at once. Basic Structure of Petri Nets : A Petri net consists of four elements : Places, Transitions, Edges, and Tokens. Graphically, places are represented by circles, transitions by rectangles, edges by directed arrows, and tokens by small solid (filled) circles. There are a wide variety of extensions to Petri nets. These extensions add features to model probabilistic behavior, allow weighted edges, or have tokens of various colors among others. A basic Petri net is shown in figure below. This Petri net has five places, P0,P1,P2 and P3 through P4, and three transitions, labeled T0 ,T1,T2. Notice that places P0 and P2 each have a single token represented by the black dot inside each place. Edges, represented as directed arcs, connect places to transitions and transitions to places. In a properly formed Petri net, places cannot be directly connected to other places and transitions cannot be directly connected to other transitions. Also notice that the Petri net may contain cycles. The Petri net in figure below contains two cycles. One cycle contains P0, T0, P1, T1, P3, and

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

T3. The other cycle contains T1, P4, T2, and P2. Cycles are common in Petri nets which represent activities that happen repeatedly.

A Petri net changes from one state to the next state when a transition fires. The firing of a transition involves the transitions input places and output places. The firing rules for a transition are : A transition is able to fire when there is at least one token on each of the transitions input places, and When a transition fires it removes one token from each of its input places and produces a single token on each of its output places. Basic Concepts : A Petrinet is a directed graph which consists of two types of nodes. Places & Transitions. And directed arcs which connect places to transitions and transitions to places.The places are commonly denoted by circles and transitions by bars. A place can contain tokens ,which is represented by a black Dot.A marking of a Petrinet is a mapping of set of tokens to places in the net.The behaviour of the system represented by the Petri net is defined by the movement of tokens. A simple Petrinet is shown diagramatically below.

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

The arcs are generally marked by the integer numbers ,to describe the number of tokens carried through a particular arc when tokens move around the net.Petri nets having arcs that are able to carry only one token at a time are called Ordinay petri nets. Tokens can proceed through a Petri net based on certain rule called a Transition firing rule. The input places of a transition are the places that are connected to the transition by arcs leading from those places to the transition. Similarly ,the output places of a transition are the places connected to the transition by arcs leading from the transition to those places.A transition is enabled if each of its input places contains at least one token.If a transition is enabled ,it may fire.A firing of a transition removes a token from each of its input places and adds a token to each of its output places.Figure below shows a Petri net before (a) and after the firing (b) of transition T2.

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

All enabled transitions fire asynchronously , on completion of the rule with the restriction that the tokens are indivisible. In figure (b) above both transitions T4 and T5 are enabled,but only one of them can fire since they share an input place holding a token.Whenever a conflict arises in a net ,the choice of which transition to fire is purely arbitrary.If a syaytem that is represented by a Petri net is to be deterministic ,all conflicts must be removed from the net. BASIC PROPERTIES : A Petri Net representation of a system can be used as an input for analyzing behavioural properties of the system.Two properties are necessary to confirm that the system described by Petri Net is to work correctly.The two properties are Liveness and Boundedness or safeness.Both boundedness and liveness are strictly connected not only with a structure of a net but also with an initial marking .A petri net with a marking is called a marked petri net.

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

A Petri net is said to be live if for any marking reached from the initial marking it is possible to fire any transition of the net by progressing through a fire sequence.If a Petri net representation of a system is live ,it means that there is no deadlock in the system. The Petri nets shown in above figures (a) and (b) are live and the Petri net shown in figure below is non-live Petri net. This petri net is non-live because when P1 and P4 have tokens and T2 fires no further firing is possible .The net would be live if it could be guaranteed that whenever the marking is P1, P4 only T1 could fire. A marking M is said to be reachable in a Petri set (N) with the initial marking M0 ,if there exists a firing sequence that transform M0 to M.A Petri net is said to be bounded if the number of tokens in each place does not exceed a finite number for any reachable marking.Safeness is a special case of boundedness.A Petri net is said to be safe if the numbeer of tokens in each place never exceeds one.

Figure :Non-Live Petri net

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

Extended Petri Net Models : The basic Petri Net models have a limited expressive power. So, the Timed Petri Nets with the following features Transitions have associated times (time intervals) Tokens are carrying time stamps. With timed Petri nets we can model the timing aspects are considered as extended Petri Nets. Another type of extended Petri nets are Colored Petri Nets .The important features are Tokens have associated values Transitions have associated functions Colored Petri Nets are similar to dataflow models (but also capture non determinism!).

So, the Extended Petri Nets have a larger expressive power then classical Petri Nets. But the analysis is more complex; the formal analysis of properties can take unacceptably large amounts of time (memory). Extended Petri nets for Parallel Controllers: A device which supports the multiple control flow is known as a parallel controller.It is not possible optimally to realize the parallel controller using Finite State Machine techniques .Because the FSM technique does not support any explicit representation of multiple process system.So, a more suitable and efficient approach is to use Petri nets to specify the design.Behavioral analysis of the controller specification can be performed using well defined techniques from Petri net theeory.Once the Petri net specification of a controller is tested ,it can be transformed automatically into logic-level description. When a Petri net is used to model a parallel controller ,each of its places represent a local state of the controller.Every marked place represents an active local state and so the marking of the net represents the entire state of the controller .The movement of the tokens defines the control behavior and can be represented using a reachability graph.

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

Transitions map on to the combinational logic block.Resetting the controller returns the Petri net to its initial marking.This model is extended in three ways. Firstly a controller receives signals (inputs) coming from a data path and some times from another control unit.Using this information ,the controller produces control signals (outputs) which determine the behavior of the system.Explicit specificationof these signals has been

Dr.Y.Narasimha Murthy. Ph.D yayavaram@yahoo.com

incorporated into the interpretation of the Petri nets.Input signals affect changes in the state of the system and are strictly bound to events and consequently to transitions. Several signals may form a logic function describing a condition for an event to take place.Such a function is called a transition predicate.A Transition predicate is a restriction imposed on the transition firing rule.This rule is defined as ,a transition is enabled and may fire when all its input places are marked and a predicate associated with it is asserted. In addition to this the controller should be able to assert output signals both when the system stays in a particular state and when a stated event takes place.This means that outputs should be associated with with both places and transitions.Outputs which are associated with places are Moore-type outputs.They only depend on the local states of the system and are asserted whenever the the asscioted places have tokens.Outputs associted with transition depend not only on the state of the system ,but also on the inputs used in the transition predicate.They are Mealy type outputs of the controller and they are asserted whenever the associated transitions are enabled. Secondly ,to model systems which are synchronized by a blobal clock a new transition firing rule is to be introduced.All transitions are synchronized by a global clock ,and so all enabled transitions fire simultaneously ,and the marking is updated only once per clock cycle.Such a Petri net is said to be a synchronous Petri net. Finally the ability to describe priorityor synchronization between quasi independent sub-

processes running concurrently in the system is useful and realized by inhibitor and enabling arcs.An inhibitor arc allows the absebce of token in a place to be tested,while an enabling arc is used to test for the presence of token in a place. References : 1.Fundamentals of Logic Design Charles Roth Jr 2.Field Programmable Gate Arrays Oldfield. 3.Highlevel Synthesis of Synchronous Parallel Controller Erick.L.Dagles --------------XXXX-----

Вам также может понравиться

- Unit Iii: CPLD & Fpga Architecture & ApplicationsДокумент30 страницUnit Iii: CPLD & Fpga Architecture & ApplicationsNarasimha Murthy Yayavaram100% (7)

- Low Power Vlsi Question PaperДокумент2 страницыLow Power Vlsi Question Paperustadkrishna100% (3)

- UNIT-3 Gate Level Design NotesДокумент22 страницыUNIT-3 Gate Level Design NotesPallavi Ch100% (2)

- Verilog HDL Lab QuizДокумент69 страницVerilog HDL Lab Quizsrilakshmi0850% (2)

- EI2403 - VLSI Design 2 Marks With AnswersДокумент23 страницыEI2403 - VLSI Design 2 Marks With AnswersAnand GvphОценок пока нет

- EC8661 VLSI Design LaboratoryДокумент53 страницыEC8661 VLSI Design LaboratorySriram100% (4)

- ARM - PPT 8Документ74 страницыARM - PPT 8roysalways4u100% (1)

- 15ecl48-VTU-raghudathesh-BJT MIXER PDFДокумент2 страницы15ecl48-VTU-raghudathesh-BJT MIXER PDFraghudatheshgp100% (1)

- VLSI & ASIC Digital Design Interview QuestionsДокумент6 страницVLSI & ASIC Digital Design Interview QuestionsRupesh Kumar DuttaОценок пока нет

- CAD For VLSI Lecture Notes - Aravinda KoithyarДокумент116 страницCAD For VLSI Lecture Notes - Aravinda KoithyarAravinda Koithyar100% (3)

- VLSI Signal ProcessingДокумент19 страницVLSI Signal ProcessingSuriya SkariahОценок пока нет

- Verilog Lab ManualДокумент72 страницыVerilog Lab ManualAditya NarayanОценок пока нет

- Digital Electronics Interview Questions: 1) What Is The Difference Between Latch and Flip-Flop?Документ11 страницDigital Electronics Interview Questions: 1) What Is The Difference Between Latch and Flip-Flop?yashuОценок пока нет

- Mobile Computing Model Exam Question PapersДокумент3 страницыMobile Computing Model Exam Question PapersSamy KmОценок пока нет

- Dec Lab QuestionsДокумент25 страницDec Lab QuestionsPrathiksha Harish Medical Electronics EngineeringОценок пока нет

- Verilog Code For Code ConvertersДокумент5 страницVerilog Code For Code Convertersseeksudhanshu1100% (1)

- 15A04802-Low Power VLSI Circuits & Systems - Two Marks Q&A-5 UnitsДокумент31 страница15A04802-Low Power VLSI Circuits & Systems - Two Marks Q&A-5 UnitsPallavi Ch71% (7)

- Multiplier in Vlsi PDFДокумент23 страницыMultiplier in Vlsi PDFvmspraneeth100% (1)

- VLSI Module-1Документ119 страницVLSI Module-1Phanindra Reddy100% (2)

- UNIT - I CPLD & FPGA ArchitecturesДокумент22 страницыUNIT - I CPLD & FPGA Architecturesyayavaram100% (2)

- DSP Important Viva QuestionsДокумент3 страницыDSP Important Viva QuestionsDeepak Sahu100% (2)

- Low Voltage Low Power MemoriesДокумент21 страницаLow Voltage Low Power Memoriesanusha100% (1)

- Digital Electronics Lab Viva QuestionsДокумент2 страницыDigital Electronics Lab Viva Questionspramodrp200750% (8)

- Digital Design Lab Manual: Introduction To VerilogДокумент48 страницDigital Design Lab Manual: Introduction To VerilogKeith FernandesОценок пока нет

- VLSI Lab Manual PART-B, VTU 7th Sem KIT-TipturДокумент64 страницыVLSI Lab Manual PART-B, VTU 7th Sem KIT-Tipturpramodkumar_sОценок пока нет

- Low-Voltage Low-Power Adders: Unit-IvДокумент24 страницыLow-Voltage Low-Power Adders: Unit-Ivrakesh100% (3)

- Mes Question-BankДокумент4 страницыMes Question-BankGanaraj KaruvajeОценок пока нет

- VerilogДокумент5 страницVerilogChandru Ramaswamy100% (2)

- Unit 1 - ARM7, ARM9, ARM11 ProcessorsДокумент88 страницUnit 1 - ARM7, ARM9, ARM11 ProcessorsKunal Khandelwal50% (2)

- MIxed Signal Simulation Lab Manual I M.tech II SemДокумент150 страницMIxed Signal Simulation Lab Manual I M.tech II SemrppvchОценок пока нет

- Unit 7 Interfacing Memory and Parallel IO PeripheralsДокумент23 страницыUnit 7 Interfacing Memory and Parallel IO PeripheralsPreetham Saigal0% (1)

- Physics of Power Dissipation in CMOSДокумент24 страницыPhysics of Power Dissipation in CMOSMahendra Babu100% (1)

- 8086 Microprocessor MASM ProgramsДокумент9 страниц8086 Microprocessor MASM ProgramsSasi Bhushan100% (2)

- Cs9251 Mobile Computing Question BankДокумент16 страницCs9251 Mobile Computing Question BankNivithaОценок пока нет

- Questions and AnswersДокумент199 страницQuestions and AnswersRamesh100% (4)

- PIC QuestionsДокумент4 страницыPIC Questionsgopikrishnarao100% (1)

- This Set of VLSI Multiple Choice QuestionsДокумент20 страницThis Set of VLSI Multiple Choice QuestionsSujith Mrinal100% (3)

- AVR Microcontroller Question BankДокумент2 страницыAVR Microcontroller Question BankmadhurithkОценок пока нет

- EC1401 VLSI - Question Bank (N.shanmuga Sundaram)Документ35 страницEC1401 VLSI - Question Bank (N.shanmuga Sundaram)Dr. N.Shanmugasundaram50% (2)

- VLSI LAB MANUAL (18ECL77) - Analog dt14-01-2022Документ148 страницVLSI LAB MANUAL (18ECL77) - Analog dt14-01-2022Aamish PriyamОценок пока нет

- DSDV Lab Manual PDFДокумент15 страницDSDV Lab Manual PDFÅᴅᴀʀsʜ Rᴀᴍ100% (3)

- Project Report On Electronic Voting Machine Using Fpga VerilogДокумент23 страницыProject Report On Electronic Voting Machine Using Fpga Verilogteja72452Оценок пока нет

- Microprocessor and Microcontroller Anna University Question PapersДокумент3 страницыMicroprocessor and Microcontroller Anna University Question PapersthennishaОценок пока нет

- 18ecl66 - Embedded Systems LaboratoryДокумент33 страницы18ecl66 - Embedded Systems Laboratorytefflon trolegdy100% (1)

- Introduction To Tanner ToolДокумент8 страницIntroduction To Tanner Toolshantanudeka72% (18)

- LPC2148 DacДокумент14 страницLPC2148 DacSmruti Pore100% (1)

- Carry Select AdderДокумент72 страницыCarry Select Adderharshithakr100% (1)

- Question Bank Solutions (Module-2-IAT 1) - IOT - 15CS81Документ12 страницQuestion Bank Solutions (Module-2-IAT 1) - IOT - 15CS81Shobhit Kushwaha100% (1)

- Unit Ii: CPLD & Fpga Architecture & ApplicationsДокумент20 страницUnit Ii: CPLD & Fpga Architecture & ApplicationsNarasimha Murthy Yayavaram100% (1)

- Dr.Y.Narasimha Murthy. PH.DДокумент28 страницDr.Y.Narasimha Murthy. PH.DGoutham Devisetty100% (1)

- UNIT-I Digital System DesignДокумент28 страницUNIT-I Digital System DesignNarasimha Murthy YayavaramОценок пока нет

- Dice GameДокумент17 страницDice GameDuy Le100% (1)

- FSM ExamplesДокумент12 страницFSM ExamplesRanjith M KumarОценок пока нет

- 2 Chapter 12 Algorithmic State MachineДокумент16 страниц2 Chapter 12 Algorithmic State MachinekaosadОценок пока нет

- Lecture 9: Finite State Representation of Digital Circuits: DOC112: Computer Hardware Lecture 9 1Документ4 страницыLecture 9: Finite State Representation of Digital Circuits: DOC112: Computer Hardware Lecture 9 1Debashish PalОценок пока нет

- DLD Term ProjectДокумент10 страницDLD Term ProjectH052 Rajesh Komaravalli ECEОценок пока нет

- 2-Lecture Notes Lesson4 4Документ10 страниц2-Lecture Notes Lesson4 4kstu1112Оценок пока нет

- Algorithmic State Machine (ASM) : UnitДокумент10 страницAlgorithmic State Machine (ASM) : Unitateeq mughalОценок пока нет

- Deffects Textures LCДокумент480 страницDeffects Textures LCNarasimha Murthy YayavaramОценок пока нет

- UNIT II-Digital DesignДокумент14 страницUNIT II-Digital DesignNarasimha Murthy YayavaramОценок пока нет

- UNIT III-Digital System DesignДокумент13 страницUNIT III-Digital System DesignNarasimha Murthy YayavaramОценок пока нет

- UNIT-I Digital System DesignДокумент28 страницUNIT-I Digital System DesignNarasimha Murthy YayavaramОценок пока нет

- Mixed Signal Embedded ProgrammingДокумент268 страницMixed Signal Embedded ProgrammingPavan Kumar100% (14)

- Applications - Embedded SystemsДокумент25 страницApplications - Embedded SystemsNarasimha Murthy YayavaramОценок пока нет

- Data Communications - NotesДокумент26 страницData Communications - NotesNarasimha Murthy YayavaramОценок пока нет

- Unit Ii: CPLD & Fpga Architecture & ApplicationsДокумент20 страницUnit Ii: CPLD & Fpga Architecture & ApplicationsNarasimha Murthy Yayavaram100% (1)

- MOS and BiCMOS Circuit Design ProcessДокумент17 страницMOS and BiCMOS Circuit Design ProcessNarasimha Murthy YayavaramОценок пока нет

- Semi Custom Integrated Circuit DesignДокумент18 страницSemi Custom Integrated Circuit DesignNarasimha Murthy YayavaramОценок пока нет

- Introduction To MSP430 MicrocontrollersДокумент70 страницIntroduction To MSP430 MicrocontrollersNarasimha Murthy YayavaramОценок пока нет

- Unit-I: CPLD & Fpga Architectures & ApplicationsДокумент22 страницыUnit-I: CPLD & Fpga Architectures & ApplicationsNarasimha Murthy Yayavaram100% (5)

- Introduction To VLSI TechnologyДокумент32 страницыIntroduction To VLSI TechnologyNarasimha Murthy YayavaramОценок пока нет

- Arm 7 ArchitectureДокумент22 страницыArm 7 ArchitectureNarasimha Murthy YayavaramОценок пока нет

- Fiber Optic CommunicationsДокумент23 страницыFiber Optic CommunicationsNarasimha Murthy YayavaramОценок пока нет

- Sensors Interfacing TechniquesДокумент16 страницSensors Interfacing TechniquesRaja VenkateshОценок пока нет

- Pic Microcontroller - Class NotesДокумент26 страницPic Microcontroller - Class NotesNarasimha Murthy Yayavaram80% (25)

- Introduction To VHDL ProgrammingДокумент68 страницIntroduction To VHDL ProgrammingNarasimha Murthy YayavaramОценок пока нет

- Basics of Peripheral Devices and WorkingДокумент33 страницыBasics of Peripheral Devices and WorkingNarasimha Murthy Yayavaram100% (1)

- Recent Advances in ElectronicsДокумент73 страницыRecent Advances in ElectronicsNarasimha Murthy YayavaramОценок пока нет

- Power Supplies & RegulatorsДокумент15 страницPower Supplies & RegulatorsNarasimha Murthy YayavaramОценок пока нет

- Introduction To MasmДокумент13 страницIntroduction To MasmNarasimha Murthy Yayavaram100% (2)

- Control Systems - NotesДокумент61 страницаControl Systems - NotesNarasimha Murthy YayavaramОценок пока нет

- Introduction To ASICsДокумент53 страницыIntroduction To ASICsNarasimha Murthy YayavaramОценок пока нет

- Embedded Systems-UnitIДокумент33 страницыEmbedded Systems-UnitINarasimha Murthy YayavaramОценок пока нет

- Introduction To 68HC11 MICROCONTROLLERДокумент72 страницыIntroduction To 68HC11 MICROCONTROLLERNarasimha Murthy Yayavaram100% (3)

- 8096 Microcontrollers NotesДокумент9 страниц8096 Microcontrollers NotesNarasimha Murthy YayavaramОценок пока нет

- 8096 MicrocontrollerДокумент51 страница8096 MicrocontrollerNarasimha Murthy Yayavaram67% (3)

- Relay Selection Guide A1 enДокумент26 страницRelay Selection Guide A1 enAdamian InakeaОценок пока нет

- Features: TL494 Pulse-Width-Modulation Control CircuitsДокумент19 страницFeatures: TL494 Pulse-Width-Modulation Control CircuitsEdgarAlonsoОценок пока нет

- Published by DB 0 946 Service Audio Printed in The Netherlands Subject To ModificationДокумент34 страницыPublished by DB 0 946 Service Audio Printed in The Netherlands Subject To ModificationCarmine Del PreteОценок пока нет

- Chapter 6 LogicДокумент49 страницChapter 6 LogicProspect Teaches MathematicsОценок пока нет

- Rom TELE-audiovision 1309Документ260 страницRom TELE-audiovision 1309Alexander WieseОценок пока нет

- Smallest Radio Circuit Using Two Transistors - Engineering Projects12Документ4 страницыSmallest Radio Circuit Using Two Transistors - Engineering Projects12max_orwellОценок пока нет

- Antenna Group OE-254/GRC (NSN 5985-01-063-1574) : Operator'S, Organizational, and Direct Support Maintenance ManualДокумент80 страницAntenna Group OE-254/GRC (NSN 5985-01-063-1574) : Operator'S, Organizational, and Direct Support Maintenance ManualesubalewОценок пока нет

- Experiment 6 Implementation of LP Fir Filter For A Given SequenceДокумент25 страницExperiment 6 Implementation of LP Fir Filter For A Given SequenceSrinivas SamalОценок пока нет

- Sound System EqualizationДокумент17 страницSound System EqualizationEspartaco ValdezОценок пока нет

- Ilox Epu-1500 ManualДокумент1 страницаIlox Epu-1500 ManualMar Val Ionita100% (1)

- Ada 6.1 & Ampx4: Ada 6.1 Surround Processor & 4 Channel Power Amplifier Operations & Installation ManualДокумент19 страницAda 6.1 & Ampx4: Ada 6.1 Surround Processor & 4 Channel Power Amplifier Operations & Installation ManualCesar Eddy Diaz HernandezОценок пока нет

- Local Control Unit - DCSДокумент44 страницыLocal Control Unit - DCSAmit Kumar Shukla80% (5)

- FINAL-GROUP-5 Transistors BJT Oct 14asdsdasdДокумент27 страницFINAL-GROUP-5 Transistors BJT Oct 14asdsdasdFrancis Valdez LopezОценок пока нет

- Ec6503 Transmission Lines and Waveguides QBW (R2013)Документ22 страницыEc6503 Transmission Lines and Waveguides QBW (R2013)Beti GechОценок пока нет

- Villa Smart 2 Solar Power Back Up SystemДокумент4 страницыVilla Smart 2 Solar Power Back Up SystemCamaОценок пока нет

- 2.2. Inductor Volt-Second Balance, Capacitor Charge Balance, and The Small Ripple ApproximationДокумент11 страниц2.2. Inductor Volt-Second Balance, Capacitor Charge Balance, and The Small Ripple ApproximationGian Carlos Perea DiazОценок пока нет

- Prefix Pro BlendДокумент12 страницPrefix Pro BlendoconejerОценок пока нет

- 2 SD 424Документ2 страницы2 SD 424Ruben David Ibañez RetamalОценок пока нет

- Digsi 5Документ7 страницDigsi 5MilosОценок пока нет

- Digital Clock SystemДокумент39 страницDigital Clock SystemBipul Das100% (2)

- Catálogo KLIP XTREME y FORZA Enero 2014Документ126 страницCatálogo KLIP XTREME y FORZA Enero 2014Alfonso Alfaro CortezОценок пока нет

- Control Theory Quiz 1Документ5 страницControl Theory Quiz 1Sundas Khalid100% (1)

- Magnat Ultra 4000Документ13 страницMagnat Ultra 4000irfz44Оценок пока нет

- PL-2303HXD PL-2303HXD: Application For RS-232 TransceiverДокумент1 страницаPL-2303HXD PL-2303HXD: Application For RS-232 TransceiverMHZAОценок пока нет

- Basic Arduino NotesДокумент11 страницBasic Arduino NotesdanielОценок пока нет

- Organização Dos OBs de Um CLP Vipa Speed 7Документ30 страницOrganização Dos OBs de Um CLP Vipa Speed 7luizsnОценок пока нет

- Modified 0-30V - 0-3A Variable Power Supply - Rev.2Документ2 страницыModified 0-30V - 0-3A Variable Power Supply - Rev.2Manuel Cereijo NeiraОценок пока нет

- Simatic S7-300: The Universal, Small Control System Supplemented by New, Compact CpusДокумент18 страницSimatic S7-300: The Universal, Small Control System Supplemented by New, Compact Cpuslucian07Оценок пока нет

- 2 42Документ2 страницы2 42Eric KialОценок пока нет

- Keen 600: The Power To ControlДокумент2 страницыKeen 600: The Power To ControlSky o skyОценок пока нет