Академический Документы

Профессиональный Документы

Культура Документы

Ese570 Mos Theory p206

Загружено:

premkumar8719Исходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Ese570 Mos Theory p206

Загружено:

premkumar8719Авторское право:

Доступные форматы

1

EE 560

MOS TRANSISTOR THEORY

EE 560

MOS TRANSISTOR THEORY

Kenneth R. Laker, University of Pennsylvania

PART 2

1

GCA (gradual channel approximaton) MOS Tranistor Model

Strong Inversion Operation

Kenneth R. Laker, University of Pennsylvania

2

V

S

= 0

V

DS

=V

D

= V

DSAT

channel

V

DS

=V

D

= small

nMOS TRANSISTOR IN LINEAR REGION

nMOS TRANSISTOR AT EDGE OF SATURATION REGION

pinch-off point

SiO

2

depletion region

substrate

or bulk B p

V

S

= 0

channel

I

D

substrate

or bulk B

p

depletion region

SiO

2

C

GC

C

BC

C

GC

C

BC

V

GS

= V

G

> V

T0

V

GS

= V

G

> V

T0

Kenneth R. Laker, University of Pennsylvania

3

nMOS TRANSISTOR IN SATURATION REGION

V

S

= 0

pinch-off point

channel

depletion region

substrate

or bulk B p

SIO

2

C

GC

C

BC

V

DS

- V

DSAT

V

CS

(y) = V

DSAT

x

y = 0

y

V

GD

= V

G

- V

D

< V

T0

V

DS

= V

D

> V

DSAT

V

GS

= V

G

> V

T0

I

D

substrate

or bulk B

p

V

S

= V

B

= 0

V

DS

y = L

y

x

y = 0

dy

Source

side

Drain

side

y = L

y = 0

y

Channel length = L

inversion layer (channel)

Channel

width = W

Kenneth R. Laker, University of Pennsylvania

4

MOSFET CURRENT - VOLTAGE CHARACTERISTICS

C

GC

C

BC

V

GS

= V

G

> V

T0

5

MOSFET CURRENT - VOLTAGE CHARACTERISTICS

Kenneth R. Laker, University of Pennsylvania

Mobile charge in channel:

n

= electron mobility

= cm

2

/Vsec

[ > U0 in SPICE]

dR

dy

W

1

n

Q

I

(y)

_

,

Q

I

(y) C

ox

[V

GS

V

CS

(y) V

T0

]

C

C/s

Incremental R for differential channel segment

V

G

> V

T0

I

D

substrate

or bulk B

p

V

S

= V

B

= 0

V

DS

y = L

y

x

y = 0

V

CS

(y)

C

GC

C

BC

V

GS

= V

G

> V

T0

Assumptions:

V

T0

(y) = V

T0

V

GS

> V

T0

V

GD

= V

GS

- V

DS

> V

T0

E

y

>> E

x

Boundary conditions:

V

CS

(y = 0) = V

S

= 0

V

CS

(y = L) = V

DS

(C/cm

2

)

6

MOSFET CURRENT - VOLTAGE CHARACTERISTICS

Kenneth R. Laker, University of Pennsylvania

dV

CS

I

D

dR

I

D

W

n

Q

I

(y)

dy

dR

dy

W

1

n

Q

I

(y)

_

,

Q

I

(y) C

ox

[V

GS

V

CS

(y) V

T0

]

I

D

dy W

n

0

L

Q

I

(y)

0

V

DS

dV

CS

i.e.

W

n

C

ox

[(V

GS

V

T0

) V

DS

V

DS

2

/ 2]

I

D

n

C

ox

2

W

L

[2(V

GS

V

T0

) V

DS

V

DS

2

]

Integrating along the channel 0 < y < L and 0 < V

CS

< V

DS

:

Voltage drop across

incremental segment dy

Boundary conditions:

V

CS

(y = 0) = V

S

= 0

V

CS

(y = L) = V

DS

I

D

n

C

ox

2

W

L

[2(V

GS

V

T0

) V

DS

V

DS

2

]

Kenneth R. Laker, University of Pennsylvania

7

MOSFET CURRENT - VOLTAGE CHARACTERISTICS

k'

2

W

L

[2(V

GS

V

T0

) V

DS

V

DS

2

]

k

2

[2(V

GS

V

T0

) V

DS

V

DS

2

]

k'

n

C

ox

[k' -> KP in SPICE]

k k'

W

L

Kenneth R. Laker, University of Pennsylvania

8

MOSFET CURRENT - VOLTAGE CHARACTERISTICS

EXAMPLE 3.4

For an n-MOS transistor with

n

= 600 cm

2

/Vsec, C

ox

= 7 x 10

-8

F/cm

2

,

W = 20 m, L = 2 m, V

T0

= 1.0 V, plot the relationship between I

D

and V

DS

, V

GS

.

k

n

C

ox

W

L

(600cm

2

/Vsec)(7x10

8

F/cm

2

)

20m

2m

0.42 mA/V

2

I

D

k

2

[2(V

GS

V

T0

) V

DS

V

DS

2

] where k

n

C

ox

W

L

F = C/V

I

D

0.21mA/V

2

[2(V

GS

1. 0) V

DS

V

DS

2

]

I

D

(mA)

V

DS

(V) 0

2.0

4.0

1.0 3.0 5.0

V

GS

= 5V

V

GS

= 4V

V

GS

= 3V

V

DS

= V

GS

- V

T0

V

DS

V

GS

V

T0

Assumptions:

V

GS

> V

T0

V

GD

= V

GS

V

DS

> V

T0

LINEAR OR TRIODE REGION

9

MOSFET CURRENT - VOLTAGE CHARACTERISTICS

Kenneth R. Laker, University of Pennsylvania

V

DS

V

GS

- V

T0

= V

DSAT

SATURATION REGION

I

D

n

C

ox

2

W

L

[2(V

GS

V

T0

) V

DS

V

DS

2

]

@V

DS

= V

DSAT

= V

GS

- V

T0

n

C

ox

2

W

L

[2(V

GS

V

T0

)(V

GS

V

T0

) (V

GS

V

T0

)

2

]

I

D

(sat)

n

C

ox

2

W

L

(V

GS

V

T0

)

2

I

D

(mA)

V

DS

(V)

0

2.0

4.0

1.0 3.0 5.0

V

GS

= 5V

V

GS

= 4V

V

GS

= 3V

V

DS

= V

GS

- V

T0

LINEAR

SAT

I

D

(sat)

V

GS

V

T0

10

MOSFET CURRENT - VOLTAGE CHARACTERISTICS

Kenneth R. Laker, University of Pennsylvania

CHANNEL LENGTH MODULATION

Boundary conditions:

V

CS

(y = 0) = V

S

= 0

V

CS

(y = L) = V

DS

Q

I

(y) C

ox

[V

GS

V

CS

(y) V

T0

]

Q

I

(y 0) C

ox

[V

GS

V

T0

]

= 0 @ V

DS

= V

DSAT

L' = L L

effective channel length

V

CS

(y = L') = V

DSAT

V

S

= 0

substrate

or bulk B p

L

L'

L

Q

1

(y L) C

ox

[V

GS

V

DS

V

T0

]

C

GC

C

BC

V

GS

=V

G

> V

T0

V

DS

=V

D

> V

DSAT

Kenneth R. Laker, University of Pennsylvania

11

MOSFET CURRENT - VOLTAGE CHARACTERISTICS

I

D

(sat)

n

C

ox

2

W

L'

(V

GS

V

T0

)

2

n

C

ox

2

W

L(1

L

L

)

(V

GS

V

T0

)

2

L V

DS

V

DSAT

where

1

1

L

L

1 + V

DS emperical relation:

= channel length modulation coefficent (V

-1

)

[ -> LAMBDA in SPICE]

V

S

= 0

substrate

or bulk B p

L

L'

L

C

GC

C

BC

V

GS

=V

G

> V

T0

V

DS

=V

D

> V

DSAT

I

D

(sat)

n

C

ox

2

W

L'

(V

GS

V

T0

)

2

n

C

ox

2

W

L(1

L

L

)

(V

GS

V

T0

)

2

12

MOSFET CURRENT - VOLTAGE CHARACTERISTICS

Kenneth R. Laker, University of Pennsylvania

1

1

L

L

1 + V

DS

I

D

(mA)

V

DS

(V)

0

2.0

4.0

1.0 3.0 5.0

V

GS

= 5V

V

GS

= 4V

V

GS

= 3V

V

DS

= V

GS

- V

T0

0

0

0

assume V

DS

<< 1

I

D

(sat)

n

C

ox

2

W

L

(V

GS

V

T0

)

2

(1+ V

DS

)

LEVEL 1

Model

13

MOSFET CURRENT - VOLTAGE CHARACTERISTICS

Kenneth R. Laker, University of Pennsylvania

SUBSTRATE BIAS EFFECT

I

D

= f(V

GS

, V

DS

, V

SB

)

(sat)

LEVEL 1

Model

14

MOSFET CURRENT - VOLTAGE CHARACTERISTICS

Kenneth R. Laker, University of Pennsylvania

I

D

D

G

B

S

+

+

+ -

V

GS

V

DS

V

SB I

D

D

G

B

S

+

+

+ -

V

GS

V

DS

V

SB

n-MOS

p-MOS

n-MOS

for

V

GS

>

V

T,

V

DS

<

V

GS

-

V

T

p-MOS

V

GS

<

V

T,

V

DS

>

V

GS

-

V

T

I

D

0 V

GS

V

T

for I

D

0 V

GS

V

T

V

GS

<

V

T,

V

DS

<

V

GS

-

V

T

V

GS

>

V

T,

V

DS

>

V

GS

-

V

T

-

-

-

-

15

MOSFET CURRENT - VOLTAGE CHARACTERISTICS

Kenneth R. Laker, University of Pennsylvania

k

n

n

C

ox

W

L

k

p

p

C

ox

W

L

MEASUREMENT OF PARAMETERS (V

T0

, , , k

n

, k

p

)

I

D

(sat)

k

n

2

(V

GS

V

T0

)

2

I

D

(sat)

k

n

2

(V

GS

V

T0

)

I

D

D

G

B

S

+

+

V

GS

V

DS

= V

GS

V

SB

V

T1

I

D

V

GS

V

T0

V

SB

= 0

V

SB

> 0

Gamma

16

MOSFET CURRENT - VOLTAGE CHARACTERISTICS

Kenneth R. Laker, University of Pennsylvania

I

D

D

G

B

S

+

V

GS

= V

T0

+ 1 V

V

DS

> V

GS

- V

T0

V

BS

= 0

+

Lambda

V

DS

I

D

I

D1

I

D2

V

DS1

V

DS2

V

GS

= V

T0

+ 1

I

D

(sat) k

n

(V

GS

V

T0

)

2

(1+ V

DS

)

V

GS

= V

T0

+ 1 V

I

D2

I

D1

1+ V

DS 2

1 + V

DS1

DC current meter

Kenneth R. Laker, University of Pennsylvania

17

EFFECTIVE CHANNEL LENGTH AND WIDTH

L

eff

= L

M

- 2LD - DL

SPICE Parameters

LD -> under diffusion

DL -> error in photolith and etch

W

eff

= W

M

- DW

SPICE Parameters

DW -> error in photolith and etch

n

+

p

G

D

S

n

+

C

GC

C

BC

n

+

n

+

LD

L

eff

L

M

LD

B

substrate

or bulk B p

L

EFFECTIVE CHANNEL LENGTH AND WIDTH

C

GC

C

BC

18

MOSFET - SCALING

SCALING -> refers to ordered reduction in dimensions of the

MOSFET and other VLSI features

Reduce Size of VLSI chips.

Change operational charateristics of MOSFETs and parasitics.

Phyiscal limits restrict degree of scaling that can be achieved.

First-order "constant field" MOS scaling theory:

The electric field E is kept constant, and the scaled device is obtained

by applying a dimensionless scale-factor to reduce dimensions by

(1/) and maintain E unchanged:

a. All dimensions, including those vertical to the surface (1/)

b. device voltages (1/)

c. the concentration densities ().

Kenneth R. Laker, University of Pennsylvania

SCALING FACTOR = > 1 --> S

(1/) = 1 (1/)/(1/) = 1

<=>

Constant Voltage Scaling, i.e. V

DD

is kept constant, while the process

dimensions are scaled by (1/).

a. All dimensions, including those vertical to the surface (1/)

b. device voltages (1)

c. the concentration densities (

2

) to preserve charge-field relations.

Lateral Scaling: only the gate length is scaled L = 1/ (gate-shrink).

Alternative Scaling Rules:

19

MOSFET - SCALING

Kenneth R. Laker, University of Pennsylvania

Feature Size(m)

Year 1991 1993

1997 1999 2001 2003 2005

1.00

0.80 0.60 0.35 0.25 0.18

0.13 0.09

Historical reduction in min feature size for typical CMOS Process

2

(1/) = 1/(1/) =

<=>

1995

Kenneth R. Laker, University of Pennsylvania

20

Influence of Scaling on MOS Device Performance

PARAMETER SCALING MODEL

Constant Field Constant Voltage Lateral

Length (L) 1/ 1/ 1/

Width (W) 1/ 1/ 1

Supply Voltage (V) 1/ 1 1

Gate Oxide thickness (t

ox

) 1/ 1/ 1

Junction depth (X

j

) 1/ 1/ 1

Substrate Doping (N

A

)

2

1

Current (I) - (W/L) (1/t

ox

)V

2

1/

Power Dissipation (P) - IV 1/

2

Power Density (P/Area) 1 **(

3

)**

2

Electric Field Across Gate Oxide - V/t

ox

1 1

Load Capacitance (C) - WL (1/t

ox

) 1/ 1/ 1/

Gate Delay (T) - VC/I 1/ 1/

2

1/

2

Kenneth R. Laker, University of Pennsylvania

21

MOSFET CAPACITANCES

n

+

p

G

D

S

n

+

C

GC

C

BC

n

+

n

+

LD

L

eff

L

M

LD

B

p

n

+

n

+

L

D

L

D

Y

C

GC

C

BC

p

substrate

or bulk B

substrate

or bulk B

22

MOSFET CAPACITANCES

Kenneth R. Laker, University of Pennsylvania

S

MOSFET

(DC MODEL)

D

B

G

C

gd

C

gs

C

gb

C

db

C

sb

C

gd

, C

gs

, C

gb

-> Oxide Capacitances

C

db

, C

sb

-> Junction Capacitances

23

MOSFET CAPACITANCES

OXIDE Capacitances

a. Overlap Caps

C

ox

ox

t

ox

b. Gate - Channel

MOSFET - Cut-off Region

C

gb

= C

ox

W L

eff

C

gs

= C

gd

= 0

Kenneth R. Laker, University of Pennsylvania

p

C

GS0

(overlap) = C

ox

W L

D

C

GD0

(overlap) = C

ox

W L

D

ALL MOSFET

OPERATION

REGIONS

C

GB0

(overlap) = C

ox

W

ov

L

eff

SPICE: C

ox

L

D

= CGS0; C

ox

L

D

= CGD0; C

ox

W

ov

= CGB0

L

D

= LD in SPICE

C

gb

, C

gb

and C

gb

(no conducting

channel in cut-off)

Kenneth R. Laker, University of Pennsylvania

24

MOSFET CAPACITANCES

b. Gate - Channel

C

gb

= 0

C

gs

= (1/2) C

ox

W L

eff

MOSFET - Linear Region

C

gd

= (1/2) C

ox

W L

eff

C

gb

= 0

C

gs

= (2/3) C

ox

W L

eff

C

gd

= 0

p

p

Kenneth R. Laker, University of Pennsylvania

25

Capacitance

Cut-off Linear Saturation

C

gb

(total)

C

gd

(total)

C

gs

(total)

C

ox

WL

eff

+ C

GB0

0 + C

GB0

0.5C

ox

WL

eff

+

C

GD0

(2/3)C

ox

WL

eff

+ C

GS0

(C/C

ox

WL)

V

GS

Saturation

Cut-off Linear

V

T

V

T

+ V

DS

1

2/3

1/2

C

gb

C

gs

C

gd

0 + C

GD0

0 +C

GS0

0.5C

ox

WL

eff

+

C

GS0

Gate -to Channel/Bulk Cap Contribution

0 + C

GB0

0 + C

GD0

C

GS0

C

GD0

=

C

GB0

Kenneth R. Laker, University of Pennsylvania

26

JUNCTION Capacitances -> C

db

, C

sb

p

x

d

x

j

Channel

n

+

n

+

W

x

j

Y

1

2

3

4

5

Drain Source

Channel

n

+

n

+

W

x

j

Y

1

2

3

4

5

Drain Source

Kenneth R. Laker, University of Pennsylvania

27

JUNCTION Capacitances -> C

db

, C

sb

Junction Area Type

1

2

3

4

5

W x

j

Y x

j

W x

j

Y x

j

WY

n

+

/p

n

+

/p

n

+

/p

+

n

+

/p

+

n

+

/p

+

p - Substrate -> N

A

p

+

- Channel-stop -> 10N

A

[x

j

-> XJ in SPICE]

28

Kenneth R. Laker, University of Pennsylvania

kT

q

ln

N

A

N

D

n

i

2

_

,

built-in junction

potential

x

d

2

Si

q

1

N

A

+

1

N

D

_

,

(

0

V)

V = Ext bias --> V

BD

, V

BS

Q

j

Aq

N

A

N

D

N

A

+ N

D

_

,

x

d

A 2

Si

q

N

A

N

D

N

A

+ N

D

_

,

(

0

V)

Depletion-region charge

p

x

d

x

j

N

A

N

D

JUNCTION Capacitances -> C

db

, C

sb

n

+

, p junctions

A = junction

area

[AS, AD ->

Source, Drain

Areas in

SPICE]

[

0

-> PB in SPICE]

29

Kenneth R. Laker, University of Pennsylvania

C

j

(V) = C

j0

when V = 0

m = grading coefficent

m = 1/2 for abrupt junction

[m = MJ in SPICE]

EQUIVALENT LARGE SIGNAL CAPACTIANCE

(F/cm

2

)

(F)

C

j0

Si

q

2

N

A

N

D

N

A

+ N

D

_

,

1

0

0 < K

eq

< 1 --> Voltage Equiv Factor

[C

j0

-> CJ in SPICE]

[

0

-> PB in SPICE]

n

+

, p

+

junctions

30

Kenneth R. Laker, University of Pennsylvania

(Sidewalls)

C

j 0 s w

Si

q

2

N

A

(sw) N

D

N

A

(sw) + N

D

_

,

1

0 s w

(F/cm

2

)

Since all sidewalls have depth = x

j

:

(F/cm)

m(sw) = 1/2

EQUIVALENT LARGE SIGNAL CAPACTIANCE

P = sidewall perimeter

[m(sw) -> MJSW in SPICE]

[C

jsw

-> CJSW in SPICE]

[x

j

-> XJ in SPICE]

[PS, PD -> Source, Drain Perimeters in SPICE]

C

jsw

= C

j0sw

x

j

K

eq

(sw)

2

0 s w

(V

2

V

1

)

1

V

2

0 s w

_

,

1 /2

1

V

1

0 s w

_

,

1 /2

1

]

1

1

31

Kenneth R. Laker, University of Pennsylvania

EXAMPLE 3-8

Determine the total junction capacitance at the drain, i.e. C

db

, for

the n-channel enhancement MOSFET in Fig. 1. The process

parameters are

Substrate doping N

A

= 2 x 10

15

cm

-3

Source/drain (n+) doping N

D

= 10

20

cm

-3

Sidewall (p+) doping N

A

(sw) = 4 x 10

16

cm

-3

Gate oxide thickness t

ox

= 45 nm

Junction depth x

j

= 1.0 m

10 m

5 m

2 m

n

+

n

+

G

D

S

Figure 1

Source, Drain are surrounded by p

+

channel-stop. The substrate

is biased at 0V. Assume the drain voltage range is 0.5 V to 5.0 V.

C

j 0 s w

Si

q

2

N

A

(sw) N

D

N

A

(sw) + N

D

_

,

1

0 s w

C

j0

Si

q

2

N

A

N

D

N

A

+ N

D

_

,

1

0

where

32

kT

q

ln

N

A

N

D

n

i

2

_

,

0.026Vln

(2x10

15

)10

20

2.1x10

20

_

,

0.896V

10 m

5 m

2 m

n

+

n

+

G

D

S

Figure 1

N

A

= 2 x 10

15

cm

-3

N

D

= 10

20

cm

-3

N

A

(sw) = 4 x 10

16

cm

-3

t

ox

= 45 nm

x

j

= 1.0 m

0

,

0sw

0 s w

kT

q

ln

N

A

(sw)N

D

n

i

2

_

,

0.026Vln

(4 x10

16

)10

20

2.1x10

20

_

,

0.975V

C

j0

Si

q

2

N

A

N

D

N

A

+ N

D

_

,

1

(1.04x10

12

F/cm)(1.6x10

19

C)

2

(2x10

15

)10

20

2x10

15

+10

20

_

,

1

0.896V

1.35x10

8

F/cm

2

33

Kenneth R. Laker, University of Pennsylvania

C

j0

, C

j0sw

F = C/V

34

Kenneth R. Laker, University of Pennsylvania

C

j0 sw

Si

q

2

N

A

(sw) N

D

N

A

(sw) + N

D

_

,

1

0sw

(1.04x10

12

F/cm)(1.6x10

19

C)

2

(4 x10

16

)10

20

4x10

16

+10

20

_

,

1

0.975V

5.83x10

8

F/cm

2

C

jsw

C

jsw

= C

j0sw

x

j

(5.83x10

8

F/cm

2

)(10

4

cm) 5.83pF/cm

K

eq

, K

eq

(sw)

V

BD2

= V

B

- V

D2

= 0 - 5V = -5V

V

BD1

= V

B

- V

D1

= 0 - 0.5V = -0.5V

and x

j

= 1.0 m = 10

-4

cm

Kenneth R. Laker, University of Pennsylvania

Area, Perimeter

10 m

5 m

2 m

n

+

n

+

G

D

S

Figure 1

A

D

: n

+

/p junctions:

A

D

= (5 x 1) m

2

+ (10 x 5) m

2

= 55 m

2

P

D

: n

+

/p

+

junctions:

P

D

= 2Y + W = 20 m + 5 m = 25 m

Channel

n

+

n

+

W = 5 m

x

j

= 1m

Y=10m

1

2

3

4

5

Drain Source

P

D

35

Short Channel Effects - L

eff

--> x

j

Narrow Channel Effects - W --> x

dm

Kenneth R. Laker, University of Pennsylvania

36

Subthreshold Current - V

GS

< V

T0

Important 2nd Order Effects

VELOSITY SATURATION

Mobility Degradation due to Lateral Electric Field:

(very small channel lengths + high supply voltages)

velosity(v

D

)

E

v

Dsat

slope =

0

slope

s

E

crit

0

= v

sat

/E

crit

Note

s

<

0

[SPICE Parameters: U0 ->

0

, UCRIT -> E

crit

, VMAX -> v

sat

]

I

D

(sat) = W v

DSAT

C

ox

(V

GS

- V

T

)

Kenneth R. Laker, University of Pennsylvania

36

Note: I

D

(sat) = linear f(V

GS

- V

T

), independent of L

E

y

Mobility Degradation due to Normal Electric Field:

(due to gate voltage across very thin oxide-depletion layer)

[SPICE Parameter: THETA -> ]

E

x

imperical mobility modulation factor

37

Short Channel Effect - L

eff

--> x

j

(source, drain diffusion depth)

Kenneth R. Laker, University of Pennsylvania

V

T0

(short channel) = V

T0

- V

T0

L

S

, L

D

= lateral extensions at source, drain of depletion

region due to reverse biased sourse, drain junctions with

substrate

Narrow Channel Effect - W --> x

dm

(depletion region depth)

[SPICE Parameter: DELTA -> imperical channel width factor]

V

T0

(narrow channel) = V

T0

+ V

T0

Subthreshold Current - V

GS

< V

T0

(Spice Model)

I

on

= I

D

in strong inversion and V

GS

= V

on

is the boundary weak and strong inversion

Kenneth R. Laker, University of Pennsylvania

38

SPICE SIMUATION - MODELS

Level 1 (MOS1) - analylitical mode, I

D

(sat) is described by square

law - strong inversion (with Channel Length Modulation). Based

on GCA (gradual channel approximaton) equations in Ch3.

Level 2 (MOS2) - anaylitical model, more detailed than MOS1.

Includes second order effects, e.g. mobility degradation, small

channel effects and sub-threshold currents. Relaxes some

simplifying GCA assumptions.

Level 3 (MOS3) - semi-emperical model. Uses simpler

expressions than MOS2 plus emperical equations to fit

experimental data. Improves accuracy and reduces simulation

time.

BSIM3 (Berkeley Short-Channel IGFET Model) - includes

sub-micron MOSFET characteristics. Analytically simple, makes

full use of parameters extracted from experimental data.

M1 4 3 5 0 NFET W=4U L=1U AS=15P AD=15P PS=11.5U PD=11.5U

.

.

.

.MODEL NFET NMOS

+ TOX=200E-10

+ CGBO=200P CGSO=300P CGDO=300P

+ CJ=200U CJSW=400P MJ=0.5 MJSW=0.3 PB=0.7

M1 4 3 5 0 NFET W=4U L=1U AS=15P AD=15P PS=11.5U PD=11.5U

D G S B

SPICE MODELING OF MOS CAPACITANCES

C

gb

= W L C

ox

= (4E-6 m) (1E-6 m) (17E-3 F/m

2

) = 6.8 fF

U = 10

-6

P = 10

-12

m

m

F/m

F/m

F/m

2

m

2 m

V

Kenneth R. Laker, University of Pennsylvania

39

M1 4 3 5 0 NFET W=4U L=1U AS=15P AD=15P PS=11.5U PD=11.5U

.

.MODEL NFET NMOS

+ TOX=200E-8

+ CGBO=200P CGSO=300P CGDO=300P

+ CJ=200U CJSW=400P MJ=0.5 MJSW=0.3 PB=0.7

CJ = zero-bias junction capacitance per junction area

(200 10

-6

F/m

2

= 2 10

-4

pF/m

2

)

CJSW = zero-bias junction capacitance per junction periphery

(400 10

-12

F/m = 4 10

-10

pF/m)

MJ = grading coefficient of junction bottom (0.5)

MJSW = grading coefficient of junction side-wall (0.3)

VJ = the junction potential (V

sb

, V

db

for n-channel, V

bs

, V

bd

for p-channel)

PB = the built-in voltage (+0.7 V)

Area = AS or AD, the area of source or drain (15 10

-12

m

2

= 15 m

2

)

Periphery = PS or PD, the periphery of source or drain

(11.5 10

-6

m = 11.5 m) Kenneth R. Laker, University of Pennsylvania

40

Вам также может понравиться

- MOS Integrated Circuit DesignОт EverandMOS Integrated Circuit DesignE. WolfendaleОценок пока нет

- EKV v2.6 Parameter Extraction Tutorial Wladyslaw Grabinski: Geneva Modeling Center MotorolaДокумент15 страницEKV v2.6 Parameter Extraction Tutorial Wladyslaw Grabinski: Geneva Modeling Center MotorolaMohammad Ayatullah MaktoomОценок пока нет

- Device Parameter Extraction of 14Nm, 10nmand 7Nm FinfetДокумент43 страницыDevice Parameter Extraction of 14Nm, 10nmand 7Nm FinfetKrisumraj PurkaitОценок пока нет

- Lecture 2 - CMOS FabricationДокумент39 страницLecture 2 - CMOS Fabricationsadia santaОценок пока нет

- High Speed Vlsi DesignДокумент93 страницыHigh Speed Vlsi DesignDr Narayana Swamy RamaiahОценок пока нет

- Design and Simulation of LNA: (Cadence Spectre RF)Документ19 страницDesign and Simulation of LNA: (Cadence Spectre RF)Kushal GajavellyОценок пока нет

- Signal Integrity in The Real WorldДокумент52 страницыSignal Integrity in The Real WorldpatarinwОценок пока нет

- Two Stage Op-AmpДокумент4 страницыTwo Stage Op-AmpShreerama Samartha G BhattaОценок пока нет

- Vlsi Test Structures For Process CharacterizationДокумент76 страницVlsi Test Structures For Process CharacterizationSumeet SauravОценок пока нет

- Lecture21 dr1Документ31 страницаLecture21 dr1api-3834272Оценок пока нет

- Lecture 5Документ47 страницLecture 5Ershad ShaikОценок пока нет

- Spice Parameter CalculatorДокумент14 страницSpice Parameter Calculatorhamid_kh_56Оценок пока нет

- BGRДокумент30 страницBGRMohammad Ayatullah MaktoomОценок пока нет

- Cmos Electronic PDFДокумент356 страницCmos Electronic PDFJustin WilliamsОценок пока нет

- Lecture8 Floorplan2Документ34 страницыLecture8 Floorplan2api-3834272Оценок пока нет

- ISSCC 2021 Tutorials T11: Ultra-Low Power Wireless Receiver DesignДокумент74 страницыISSCC 2021 Tutorials T11: Ultra-Low Power Wireless Receiver DesigndxzhangОценок пока нет

- A Review of Recent MOSFET VTH Extraction MethodsДокумент14 страницA Review of Recent MOSFET VTH Extraction Methodshpnx9420Оценок пока нет

- Modeling of Passive Elements With ASITICДокумент20 страницModeling of Passive Elements With ASITICKyusang ParkОценок пока нет

- Spectral PLL Built-In Self-Test For Integrated Cellular TransmittersДокумент231 страницаSpectral PLL Built-In Self-Test For Integrated Cellular TransmittersChipmuenkОценок пока нет

- Comparative Analysis of Different Architectures of CMOS ComparatorДокумент4 страницыComparative Analysis of Different Architectures of CMOS Comparatorj4everОценок пока нет

- PROJECT1 S 2013 v2 PDFДокумент4 страницыPROJECT1 S 2013 v2 PDFHarshal SinghОценок пока нет

- A CMOS Bandgap Reference Circuit With Sub-1V OperationДокумент5 страницA CMOS Bandgap Reference Circuit With Sub-1V Operationbooky_mookyОценок пока нет

- Lab-2 (Tutorial) Simulation of Lna (Cadence Spectrerf) : Prepared by Rashad.M.Ramzan Rashad@Isy - Liu.SeДокумент18 страницLab-2 (Tutorial) Simulation of Lna (Cadence Spectrerf) : Prepared by Rashad.M.Ramzan Rashad@Isy - Liu.Seblue-smart1355100% (1)

- An Overview of Design Techniques For CMOS Phase DetectorsДокумент4 страницыAn Overview of Design Techniques For CMOS Phase DetectorsfypcommОценок пока нет

- Zipper Cmos Logic CircuitДокумент15 страницZipper Cmos Logic CircuitShreerama Samartha G BhattaОценок пока нет

- 14 NMДокумент23 страницы14 NMNikhilAKothariОценок пока нет

- Inductor WorkshopДокумент35 страницInductor WorkshoppatarinwОценок пока нет

- Lecture18 GRДокумент36 страницLecture18 GRapi-3834272Оценок пока нет

- Basic Design Approaches To Accelerating Deep Neural NetworksДокумент93 страницыBasic Design Approaches To Accelerating Deep Neural NetworksdxzhangОценок пока нет

- Two-Stage CMOS Op-Amp Circuit Design - Jianfeng SunДокумент17 страницTwo-Stage CMOS Op-Amp Circuit Design - Jianfeng Sunjianfeng sun100% (2)

- Rail To Rail Amplifier ProjectДокумент19 страницRail To Rail Amplifier Projectneva91Оценок пока нет

- Parameters Extraction of Semiconductor DevicesДокумент75 страницParameters Extraction of Semiconductor DevicesCarlos RodriguezОценок пока нет

- 665report - Design of CMOS Ring VCO and Quadrature LC VCO For 8 Phases GenerationДокумент17 страниц665report - Design of CMOS Ring VCO and Quadrature LC VCO For 8 Phases GenerationapplebeeОценок пока нет

- 3DICДокумент148 страниц3DICnoorevОценок пока нет

- Calibration Techniques in Adcs: Ahmed M. A. Ali Analog Devices, IncДокумент74 страницыCalibration Techniques in Adcs: Ahmed M. A. Ali Analog Devices, IncdxzhangОценок пока нет

- Tutorial On Layout of Mixed-Signal CircuitsДокумент29 страницTutorial On Layout of Mixed-Signal CircuitsPetru NistorОценок пока нет

- Low Voltage CMOS SAR ADC DesignДокумент68 страницLow Voltage CMOS SAR ADC DesignAyush SukaniОценок пока нет

- MMIC Design, Part 2 - ProcessingДокумент23 страницыMMIC Design, Part 2 - ProcessingVishal IyerОценок пока нет

- Chapter 08 PDFДокумент46 страницChapter 08 PDFAnonymous CNAdojОценок пока нет

- Charge Redistribution AdcДокумент74 страницыCharge Redistribution AdcAnonymous eWMnRr70qОценок пока нет

- FM - PM Demodulation - The Phase Lock LoopДокумент5 страницFM - PM Demodulation - The Phase Lock LoopSunit Kumar Sharma100% (1)

- An Adaptive Biased Single-Stage CMOS Operational Amplifier With A Novel Rail-To-Rail Constant-Gm Input StageДокумент8 страницAn Adaptive Biased Single-Stage CMOS Operational Amplifier With A Novel Rail-To-Rail Constant-Gm Input Stagekhausar1785Оценок пока нет

- Phase Noise and Jitter in CMOS Ring OscillatorsДокумент14 страницPhase Noise and Jitter in CMOS Ring Oscillatorsnucleur_13Оценок пока нет

- Lecture12 Placement 3Документ51 страницаLecture12 Placement 3api-3834272Оценок пока нет

- Cmos Analog Ic Design Problems and SolutionsДокумент206 страницCmos Analog Ic Design Problems and SolutionsEdsel Silva100% (1)

- Fully Differential CMOS Voltage AmplifierДокумент16 страницFully Differential CMOS Voltage AmplifierAjit Narwal0% (1)

- EEE 357 Lecture 10 Mux, DemuxДокумент15 страницEEE 357 Lecture 10 Mux, DemuxShuvodip Das100% (1)

- Stmicroelectronics Deep Sub-Micron Processes: 0.18Μ, 0.12Μ, 90Nm CmosДокумент36 страницStmicroelectronics Deep Sub-Micron Processes: 0.18Μ, 0.12Μ, 90Nm CmosAbhiОценок пока нет

- Lecture 12 SRAMДокумент37 страницLecture 12 SRAMSachin MalikОценок пока нет

- Design and Test of An L-Band GNSS Low No PDFДокумент70 страницDesign and Test of An L-Band GNSS Low No PDFyyryОценок пока нет

- Eecs 2011 31Документ106 страницEecs 2011 31woshisimoxОценок пока нет

- Lecture 7 - CMOS DC - Transient ResponseДокумент40 страницLecture 7 - CMOS DC - Transient Responsesadia santaОценок пока нет

- Thesis ChandraДокумент60 страницThesis Chandraprabhu kiranОценок пока нет

- Sar Adc 65nm PHD PDFДокумент87 страницSar Adc 65nm PHD PDFLex LutherОценок пока нет

- Low Power Optimization of Full Adder Circuit Based On Gdi Logic For Biomedical ApplicationsДокумент11 страницLow Power Optimization of Full Adder Circuit Based On Gdi Logic For Biomedical ApplicationsIJAR JOURNALОценок пока нет

- Lecture5 PartitionspectralДокумент14 страницLecture5 Partitionspectralapi-3834272Оценок пока нет

- Lecture1 IntroДокумент35 страницLecture1 Introapi-3834272Оценок пока нет

- Chapter 17Документ66 страницChapter 17helenarajОценок пока нет

- Fundamentals of Fully-Integrated Voltage Regulators: Yan Lu University of Macau, Macao, ChinaДокумент81 страницаFundamentals of Fully-Integrated Voltage Regulators: Yan Lu University of Macau, Macao, ChinadxzhangОценок пока нет

- Optimum Array Processing: Part IV of Detection, Estimation, and Modulation TheoryОт EverandOptimum Array Processing: Part IV of Detection, Estimation, and Modulation TheoryОценок пока нет

- BBB 4M1 Summative Article ExpectationsДокумент3 страницыBBB 4M1 Summative Article ExpectationsMuhammad SherazОценок пока нет

- ProbabilityДокумент29 страницProbabilitymaryroseОценок пока нет

- Transparency IIДокумент25 страницTransparency IIKatyanne ToppingОценок пока нет

- Afritalent Agency Seeks To Bridge Talent of The Global Diaspora With Hollywood Casting Directors and ProducersДокумент3 страницыAfritalent Agency Seeks To Bridge Talent of The Global Diaspora With Hollywood Casting Directors and ProducersPR.comОценок пока нет

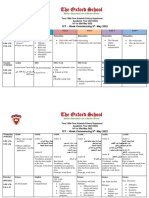

- Term 3 Mid-Term Assessment ScheduleДокумент9 страницTerm 3 Mid-Term Assessment ScheduleRabia MoeedОценок пока нет

- The Criticism of African Fiction: Its Nature and Function: EUSTACE PALMER, University of Sierra LeoneДокумент8 страницThe Criticism of African Fiction: Its Nature and Function: EUSTACE PALMER, University of Sierra LeoneBenjamín AlíasОценок пока нет

- Mergers and Acquisitions of Hindalco and NovelisДокумент35 страницMergers and Acquisitions of Hindalco and Novelisashukejriwal007Оценок пока нет

- Strucni TekstДокумент6 страницStrucni TekstDusanОценок пока нет

- Minipro Anemia Kelompok 1Документ62 страницыMinipro Anemia Kelompok 1Vicia GloriaОценок пока нет

- Process Audit Manual 030404Документ48 страницProcess Audit Manual 030404azadsingh1Оценок пока нет

- Home DepotДокумент13 страницHome DepotTyfanie PetersenОценок пока нет

- Seven Years WarДокумент55 страницSeven Years WarKismat Dhaliwal100% (1)

- Cargill Web Application Scanning ReportДокумент27 страницCargill Web Application Scanning ReportHari KingОценок пока нет

- Itm University, Raipur (Chhattisgarh) IndiaДокумент5 страницItm University, Raipur (Chhattisgarh) Indiajassi7nishadОценок пока нет

- The World of The GerДокумент302 страницыThe World of The GerMystic Master0% (1)

- Test 04 AnswerДокумент16 страницTest 04 AnswerCửu KhoaОценок пока нет

- Silk Road ActivityДокумент18 страницSilk Road Activityapi-332313139Оценок пока нет

- Gripped by The Mystery: Franziska Carolina Rehbein SspsДокумент70 страницGripped by The Mystery: Franziska Carolina Rehbein SspsdonteldontelОценок пока нет

- Sampling TechДокумент5 страницSampling TechJAMZ VIBESОценок пока нет

- 99 Attributes of Allah Al Khaliq (The Creator) Al Bari (The Inventor) Al Musawwir (The Fashioner)Документ7 страниц99 Attributes of Allah Al Khaliq (The Creator) Al Bari (The Inventor) Al Musawwir (The Fashioner)Abdourahamane GarbaОценок пока нет

- Introduction To Qualitative ResearchДокумент19 страницIntroduction To Qualitative ResearchAnonymous LToOBqDОценок пока нет

- CatalysisДокумент50 страницCatalysisnagendra_rdОценок пока нет

- Best Trusts and Estates OutlineДокумент84 страницыBest Trusts and Estates OutlineJavi Luis100% (4)

- Ieee - 2030 Smart GridДокумент26 страницIeee - 2030 Smart GridarturoelectricaОценок пока нет

- Chap 005Документ13 страницChap 005Mohammad ElabedОценок пока нет

- Ayurveda Secrets of Healing Maya Tiwari.07172 2seasonal CleansingДокумент5 страницAyurveda Secrets of Healing Maya Tiwari.07172 2seasonal CleansingkidiyoorОценок пока нет

- Progress Test 1 Units 1-6: Exercise 1 Personal InformationДокумент3 страницыProgress Test 1 Units 1-6: Exercise 1 Personal InformationLuis Villaverde VerasteguiОценок пока нет

- Abra State Institute of Sciences and TechnologyДокумент9 страницAbra State Institute of Sciences and TechnologyTintin Bejarin100% (3)

- 5 - Data Room Procedure TemplatesДокумент8 страниц5 - Data Room Procedure TemplatesnajahОценок пока нет

- Headache PAINДокумент1 страницаHeadache PAINOmarОценок пока нет