Академический Документы

Профессиональный Документы

Культура Документы

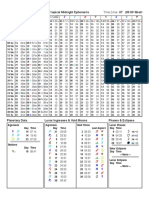

MMC SD Memory Card Driver Schematics

Загружено:

engrmunirОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

MMC SD Memory Card Driver Schematics

Загружено:

engrmunirАвторское право:

Доступные форматы

1

+3V3

R1

10K

+3V3

A

R4

10K

100nF

VSS

VSS

RE0/RD/AN5

RE1/WR/AN6

RE2/CS/AN7

MCLR/Vpp/RE3

OSC1/CLKI/RA7

OSC2/CLKO/RA6

19

20

21

22

23

24

MMC/SD CS

SPI MOSI

SPI SCK

SPI MISO

LED1 +3V3

R5

LED-A

470R

8

9

10

11

14

15

16

17

Red

Switch

LED2

LED-A

LED-B

470R

COM

CD

WP

MMC/SD CD

MMC/SD WP

R6

LED-B

1

2

5

7

8

9

Green

MMC/SD(SPI)/SD

CS/CS/D3

SI/DI/CMD

SCK/SCK/CLK

SO/DO/D0

NC/IRQ/D1

NC/NC/D2

COM

CD

WP

MMC/SD Card Socket

J1

GND

GND

VDD

VDD

RD0/PSP0

RD1/PSP1

PD2/PSP2

RD3/PSP3

RD4/PSP4

RD5/PSP5/P1B

RD6/PSP6/P1C

RD7/PSP7/P1D

GND

Prog PGC

Prog PGD

GND

32

35

36

37

42

43

44

1

MMC/SD CD

MMC/SD CS

MMC/SD WP

SPI SCK

SPI MISO

SPI MOSI

+3V3

VPP

38

39

40

41

2

3

4

5

B

1

2

3

4

5

6

Prog PGD

Prog PGC

J2

CONN RJ12 6/6

GND

'Programming Port'

7

28

GND

RC0/T1OSO/T13CKI

RC1/T1OSI/CCP2

RC2/CCP1/P1A

RC3/SCK/SCL

RC4/SDI/SDA

RC5/SDO

RC6/TX/CK

RC7/RX/DT

6

29

R3

10K

VDD

R2

10K

Switch

U1

RB0/INT0/FLT0/AN12

RB1/INT1/AN10

RB2/INT2/AN8

RB3/AN9/CCP2

RB4/KBI0/AN11

RB5/KBI1/PGM

RB6/KBI2/PGC

RB7/KBI3/PGD

+3V3

SW1

GND

RA0/AN0

RA1/AN1

RA2/AN2/Vref-/CVref

RA3/AN3/Vref+

RA4/T0CKI/C1OUT

RA5/AN4/SS/HLVDIN/C2OUT

+3V3

C1

C3

22nF

6

3

C2

22nF

+3V3

25

26

27

R7

10K

VPP

18

30

31

VPP

C4

XTAL1

PIC18LF4620-TQFP

6MHz

R8

470R

C5

100nF

15pF

C6

GND

15pF

GND

GND

6MHz with x4 PLL = 24MHz

(Max possible speed for this device powered at

3.3V)

1.03

1.02

1.01

1.00

Rev.

Project:

MMC / SD Memory Card Driver

CENTRE

OUTSIDE

OUTSIDE LINK

D1

Pwr In

Vin

GF1B

C9

100uF 25V

MINI PWR 2.5MM

Title:

U2

3V3 Voltage Regulator

PIC18, PIC 24 & NXP LPC23xx Sample Project Circuits

Drawing Number:

GND

'+9V - +12V PSU'

+3V3

J3

Vout

C7

100nF

Added LPC2365 circuit.

Changed PIC 18 to PIC18LF4620 and added PIC24HJ64GP206

circuit.

Moved 'MMC/SD CD' from PIC pin RC0 to RC2 to match code.

Original release

Notes

3563-005

C8

100nF

C10

22uF

C11

22uF

Rev:

1.03

IMPORTANT: THIS DESIGN IS COPYRIGHT OF EMBEDDED-CODE.COM

AND IS SUBJECT TO A LICENCE AGREEMENT. ALL RIGHTS

RESERVED. UNAUTHORISED USE, REPRODUCTION OR

DISTRIBUTION OF THIS DESIGN MAY LEAD TO PROSECUTION.

ENQUIRIES TO INFO@EMBEDDED-CODE.COM

GND

Sheet:

1 of 3

+3V3

A

+3V3

R9

10K

C13

22nF

RG0

RG1

SCL1/RG2

SDA1/RG3

SCK2/CN8/RG6

SDI2/CN9/RG7

SDO2/CN10/RG8

SS2/CN11/RG9

RG12

RG13

RG14

RG15

16

15

14

13

12

11

17

18

21

22

23

24

27

28

29

30

MMC/SD CS

SPI MOSI

SPI SCK

SPI MISO

LED3 +3V3

R13

LED-A

470R

PGC

PGD

R12

10K

100nF

1

2

5

7

8

9

Red

LED4

MMC/SD CD

MMC/SD WP

R14

LED-B

470R

Green

COM

CD

WP

MMC/SD(SPI)/SD

CS/CS/D3

SI/DI/CMD

SCK/SCK/CLK

SO/DO/D0

NC/IRQ/D1

NC/NC/D2

COM

CD

WP

J4

MMC/SD Card Socket

GND

2

3

47

48

46

49

50

51

52

53

54

55

42

43

44

45

Switch

58

59

34

33

31

32

35

MMC/SD CS

61

60

37

36

4

5

6

8

63

64

62

1

MMC/SD CD

MMC/SD WP

7

39

40

VPP

LED-A

LED-B

SPI MISO

SPI MOSI

+3V3

R15

2K2

SPI SCK

VPP

1

2

3

4

5

6

Prog PGD

Prog PGC

GND

J5

CONN RJ12 6/6

C19

XTAL2

AVss

MCLR

OSC1/CLKIN/RC12

OSC2/CLKO/RC15

20

R11

10K

R10

10K

Switch

GND

GND

RF0

RF1

U1RX/SDI1/RF2

U1TX/SDO1/RF3

U2RX/SDA2/CN17/RF4

U2TX/SCL2/CN18/RF5

U1RTS/SCK1/INT0/RF6

Vss

Vss

Vss

+3V3

C18

GND

OC1/RD0

OC2/RD1

OC3/RD2

OC4/RD3

OC5/IC5/CN13/RD4

OC6/IC6/CN14/RD5

OC7/CN15/RD6

OC8/CN16/RD7

IC1/INT1/RD8

IC2/U1CTS/INT2/RD9

IC3/INT3/RD10

IC4/INT4/RD11

9

25

41

+3V3

VDD

U3

PGD3/EMUD3/AN0/Vref+/CN2/RB0

PGC3/EMUC3/AN1/Vref-/CN3/RB1

AN2/SS1/CN4/RB2

AN3/CN5/RB3

AN4/IC7/CN6/RB4

AN5/IC8/CN7/RB5

PGC1/EMUC1/AN6/OCFA/RB6

PGD1/EMUD1/AN7/RB7

U2CTS/AN8/RB8

AN9/RB9

TMS/AN10/RB10

TDO/AN11/RB11

TCK/AN12/RB12

TDI/AN13/RB13

U2RTS/AN14/RB14

AN15/OCFB/CN12/RB15

C16

22nF

SW2

AN16/T2CK/T7CK/RC1

AN17/T3CK/T6CK/RC2

PGD2/EMUD2/SOSCI/T4CK/CN1/RC13

PGC2/EMUC2/SOSCO/T1CK/CN0/RC14

C15

22nF

GND

GND

19

10

26

38

57

C14

22nF

AVdd

Vddcore

22nF

GND

Vdd

Vdd

Vdd

Vdd

56

10uF 10V

C17

6

3

C12

'Programming Port'

10MHz

PIC24HJ64GP206

15pF

C20

Project:

15pF

MMC / SD Memory Card Driver

Title:

GND

PIC18, PIC 24 & NXP LPC23xx Sample Project Circuits

GND

Drawing Number:

3563-005

Rev:

1.03

Sheet:

2 of 3

IMPORTANT: THIS DESIGN IS COPYRIGHT OF EMBEDDED-CODE.COM

AND IS SUBJECT TO A LICENCE AGREEMENT. ALL RIGHTS

RESERVED. UNAUTHORISED USE, REPRODUCTION OR

DISTRIBUTION OF THIS DESIGN MAY LEAD TO PROSECUTION.

ENQUIRIES TO INFO@EMBEDDED-CODE.COM

+3V3

L1

C27

100nF

C28

100nF

C29

100nF

1

2

3

4

5

100

14

17

Reset

TDO

TDI

TMS

TRST

TCK

RTCK

RSTOUT

RESET

C32

22

23

18pF

C33

XTAL3

12MHz

XTAL1

XTAL2

18pF

GND

C34

16

18

22pF

C35

XTAL4

32.768kHz

RTCX1

RTCX2

19

Vdda

Vref

750R

C30

100nF

GND

U4

P0[15]/TXD1/SCK0/SCK

P0[16]/RXD1/SSEL0/SSEL

P0[17]/CTS1/MISO0/MISO

P0[18]/DCD1/MOSI0/MOSI

P0[19]/DSR1/MCICLK/SDA1

P0[20]/DTR1/MCICMD/SCL1

P0[21]/RI1/MCIPWR/RD1

P0[22]/RTS1/MCIDAT0/TD1

P0[23]/AD0[0]/I2SRX_CLK/CAP3[0]

P0[24]/AD0[1]/I2SRX_WS/CAP3[1]

P0[25]/AD0[2]/I2SRX_SDA/TXD3

P0[26]/AD0[3]/AOUT/RXD3

P0[27]/SDA0

P0[28]/SCL0

P0[29]

P0[30]

P1[0]/ENET_TXD0

P1[1]/ENET_TXD1

P1[4]/ENET_TX_EN

22pF

P1[8]/ENET_CRS

P1[9]/ENET_RXD0

P1[10]/ENET_RXD1

P1[14]/ENET_RX_ER

P1[15]/ENET_REF_CLK

P1[16]/ENET_MDC

P1[17]/ENET_MDIO

P1[18]/PWM1[1]/CAP1[0]

P1[19]/CAP1[1]

P1[20]/PWM1[2]/SCK0

P1[21]/PWM1[3]/SSEL0

P1[22]/MAT1[0]

P1[23]/PWM1[4]/MISO0

P1[24]/PWM1[5]/MOSI0

P1[25]/MAT1[1]

P1[26]/PWM1[6]/CAP0[0]

P1[27]/CAP0[1]

P1[28]/PCAP1[0]/MAT0[0]

P1[29]/PCAP1[1]/MAT0[1]

P1[30]/AD0[4]

P1[31]/SCK1/AD0[5]

P2[0]/PWM1[1]/TXD1/TRACECLK

P2[1]/PWM1[2]/RXD1/PIPESTAT0

P2[2]/PWM1[3]/CTS1/PIPESTAT1

P2[3]/PWM1[4]/DCD1/PIPESTAT2

P2[4]/PWM1[5]/DSR1/TRACESYNC

P2[5]/PWM1[6]/DTR1/TRACEPKT0

P2[6]/PCAP1[0]/RI1/TRACEPKT1

P2[7]/RD2/RTS1/TRACEPKT2

P2[8]/TD2/TXD2/TRACEPKT3

P2[9]/RXD2/EXTIN0

P2[10]/EINT0

P2[11]/EINT1/MCIDAT1/I2STX_CLK

P2[12]/EINT2/MCIDAT2/I2STX_WS

P2[13]/EINT3/MCIDAT3/I2STX_SDA

P3[25]/MAT0[0]/PWM1[2]

P3[26]/MAT0[1]/PWM1[3]

GND

1

Vssa

11

15

31

41

55

72

83

97

Vss

Vss

Vss

Vss

Vss

Vss[AN]

Vss

P4[28]/MAT2[0]/TXD3

P4[29]/MAT2[1]/RXD3

+3V3

BAT1

3V CR2032

R17

10K

+3V3

+3V3

C31

SW3

46

47

98

99

81

80

79

78

77

76

48

49

62

63

61

60

59

58

57

56

9

8

7

6

25

24

29

30

R18

10K

Switch

GND

P0[0]/RD1/TXD3/SDA1

P0[1]/TD1/RXD3/SCL1

P0[2]/TXD0

P0[3]/RXD0

P0[4]/I2SRX_CLK/RD2/CAP2[0]

P0[5]/I2SRX_WS/TD2/CAP2[1]

P0[6]/I2SRX_SDA/SSEL1/MAT2[0]

P0[7]/I2STX_CLK/SCK1/MAT2[1]

P0[8]/I2STX_WS/MISO1/MAT2[2]

P0[9]/I2STX_SDA/MOSI1/MAT2[3]

P0[10]/TXD2/SDA2/MAT3[0]

P0[11]/RXD2/SCL2/MAT3[1]

GND

D3

BAT54

Vbat

28

54

71

96

Vdd

Vdd

Vdd

Vdd[AN]

Vdd_DCDC

Vdd_DCDC

Vdd_DCDC[AN]

JTAG TDO

JTAG TDI

JTAG TMS

JTAG TRST

JTAG TCK

JTAG RTCK

10

12

GND

13

42

84

GND

R16

C25

100nF

GND

A

+3V3

BAT54

R19

10K

R20

10K

100nF

C26

100nF

D2

Ferrite

GND

GND

MMC/SD CS

SPI MOSI

SPI SCK

SPI MISO

Bootloader TX

Bootloader RX

LED5 +3V3

R21

LED-A

470R

Red

LED6

470R

SPI SCK

COM

CD

WP

MMC/SD CD

MMC/SD WP

R22

LED-B

1

2

5

7

8

9

Green

MMC/SD(SPI)/SD

CS/CS/D3

SI/DI/CMD

SCK/SCK/CLK

SO/DO/D0

NC/IRQ/D1

NC/NC/D2

COM

CD

WP

MMC/SD Card Socket

SPI MISO

SPI MOSI

MMC/SD CD

MMC/SD WP

J6

VDD

C24

10nF

GND

GND

C23

10nF

6

3

C22

10nF

GND

B

MMC/SD CS

95

94

93

92

91

90

89

88

87

86

32

33

34

35

36

37

38

39

40

43

44

45

21

20

75

74

73

70

69

68

67

66

65

64

53

52

51

50

J7

1

2

3

Bootloader TX

Bootloader RX

SIL3

GND

'Enable Bootloader'

Switch

Bootloader Enable

JP1

GND

+3V3

LED-A

LED-B

J8

Bootloader Enable

1

3

5

7

9

11

13

15

17

19

JTAG TRST

JTAG TDI

JTAG TMS

JTAG TCK

JTAG RTCK

JTAG TDO

Reset

27

26

R23

24K

82

85

+3V3

2

4

6

8

10

12

14

16

18

20

'JTAG Programmer'

C21

10nF

'Programming'

Project:

MMC / SD Memory Card Driver

Title:

PIC18, PIC 24 & NXP LPC23xx Sample Project Circuits

Drawing Number:

3563-005

R25

24K

1.03

GND

GND

LPC2365FBD100

L2

Ferrite

GND

3

Sheet:

3 of 3

IMPORTANT: THIS DESIGN IS COPYRIGHT OF EMBEDDED-CODE.COM

AND IS SUBJECT TO A LICENCE AGREEMENT. ALL RIGHTS

RESERVED. UNAUTHORISED USE, REPRODUCTION OR

DISTRIBUTION OF THIS DESIGN MAY LEAD TO PROSECUTION.

ENQUIRIES TO INFO@EMBEDDED-CODE.COM

10+10

R24

24K

Rev:

Вам также может понравиться

- Max 202Документ26 страницMax 202José AdelinoОценок пока нет

- Delta Ia-Plc Pid An en 20141222Документ26 страницDelta Ia-Plc Pid An en 20141222PrestoneKОценок пока нет

- Entry Test: Academic Session 2019-20Документ5 страницEntry Test: Academic Session 2019-20engrmunirОценок пока нет

- IG I EnglishДокумент6 страницIG I EnglishengrmunirОценок пока нет

- DELTA IA-PLC Mark AN EN 20151022 PDFДокумент32 страницыDELTA IA-PLC Mark AN EN 20151022 PDFengrmunirОценок пока нет

- 74LVCH162373AДокумент17 страниц74LVCH162373AengrmunirОценок пока нет

- MSDM Remote Monitoring SystemДокумент4 страницыMSDM Remote Monitoring SystemengrmunirОценок пока нет

- DELTA IA-PLC Interrupt AN EN 20150706 PDFДокумент29 страницDELTA IA-PLC Interrupt AN EN 20150706 PDFengrmunirОценок пока нет

- HGTG10N120BND PDFДокумент8 страницHGTG10N120BND PDFengrmunirОценок пока нет

- Data Sheet HGTG11N120CNDДокумент8 страницData Sheet HGTG11N120CNDTiaraОценок пока нет

- s7-1200 Opc Simatic-Net eДокумент28 страницs7-1200 Opc Simatic-Net ebsb1912Оценок пока нет

- Guide About Tcpip Connections Between Pcs and Siemens PlcsДокумент11 страницGuide About Tcpip Connections Between Pcs and Siemens Plcsnathan_allgrenОценок пока нет

- UC3843 DatasheetДокумент13 страницUC3843 DatasheetBigbrain99Оценок пока нет

- AP Power Factor Correction PFC Modules AP24c PDFДокумент7 страницAP Power Factor Correction PFC Modules AP24c PDFengrmunirОценок пока нет

- Oracle11g Dba1 (Brochure)Документ6 страницOracle11g Dba1 (Brochure)engrmunirОценок пока нет

- 802.11 Wireless LAN: Network Connectivity To The Legacy Wired LANДокумент12 страниц802.11 Wireless LAN: Network Connectivity To The Legacy Wired LANvizooooОценок пока нет

- Duplicate: 1 A1-R 1 Norm 40.00Документ1 страницаDuplicate: 1 A1-R 1 Norm 40.00engrmunirОценок пока нет

- Moduł PM Sma00000.49 D Rexroth Manual PDFДокумент187 страницModuł PM Sma00000.49 D Rexroth Manual PDFengrmunirОценок пока нет

- Ds Ah 0055514Документ8 страницDs Ah 0055514engrmunirОценок пока нет

- Oracle Developer11g (BROCHURE)Документ11 страницOracle Developer11g (BROCHURE)engrmunirОценок пока нет

- Wireless Local Area NetworksДокумент40 страницWireless Local Area NetworksengrmunirОценок пока нет

- SensemfinДокумент19 страницSensemfinengrmunirОценок пока нет

- 17 WirelessLANsДокумент64 страницы17 WirelessLANsapi-19500872Оценок пока нет

- Procedure For Preparing 840c HarddiskДокумент0 страницProcedure For Preparing 840c HarddiskengrmunirОценок пока нет

- Nas M ManualДокумент208 страницNas M ManualwilliampinhoОценок пока нет

- PLC Errors 840CДокумент19 страницPLC Errors 840CengrmunirОценок пока нет

- Asm 8086Документ19 страницAsm 8086Andres Ruiz CarrascoОценок пока нет

- Chap 2Документ18 страницChap 2engrmunirОценок пока нет

- Sihg20N50C: Vishay SiliconixДокумент8 страницSihg20N50C: Vishay SiliconixengrmunirОценок пока нет

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- Winning The Budapest Gambit: 82 Traps That Black Can Really Use.Документ20 страницWinning The Budapest Gambit: 82 Traps That Black Can Really Use.Bill Harvey100% (13)

- FIDE Surveys - PALATNIK - JUNE 2015 PDFДокумент4 страницыFIDE Surveys - PALATNIK - JUNE 2015 PDFRenukha PannalaОценок пока нет

- Chess Training For Budding ChampionsДокумент4 страницыChess Training For Budding Championsradovanb50% (2)

- Symphony X - FallenДокумент15 страницSymphony X - Fallensergio evaristo michlosОценок пока нет

- Hedgehog (Chess)Документ2 страницыHedgehog (Chess)Carlo Edoardo CapponiОценок пока нет

- BTC-006 Daily Yard Inspection ChecklistДокумент2 страницыBTC-006 Daily Yard Inspection ChecklistAlfred PabloОценок пока нет

- Grivas New Book PDFДокумент20 страницGrivas New Book PDFoofgame0% (1)

- Chess Openings: Philidor DefenseДокумент2 страницыChess Openings: Philidor DefenseBob100% (2)

- Bom Rev2Документ2 страницыBom Rev2gautamkr15Оценок пока нет

- Collins, S. - The King's Indian Defence PDFДокумент321 страницаCollins, S. - The King's Indian Defence PDFSuper PippoОценок пока нет

- Carlsen Anti SicilianДокумент2 страницыCarlsen Anti SicilianTantizmОценок пока нет

- Lolo September 16-30Документ1 страницаLolo September 16-30Denielle Casimiro RabanezОценок пока нет

- Teaching Endgames by Bill Wal1Документ18 страницTeaching Endgames by Bill Wal1Chessman100% (2)

- Consolidate Data From Multiple Worksheets Into A Summary Worksheet in ExcelДокумент10 страницConsolidate Data From Multiple Worksheets Into A Summary Worksheet in ExcelThomas WongОценок пока нет

- School of Future Champions 2 - Secrets of Opening Preparation (Dvoretsky and Yusupov 2007) PDFДокумент282 страницыSchool of Future Champions 2 - Secrets of Opening Preparation (Dvoretsky and Yusupov 2007) PDFAlpha Wolf100% (3)

- Wing GambitДокумент3 страницыWing GambitAdi SusantoОценок пока нет

- Italian Game (C50-59) Annotated Games 1850-1950Документ100 страницItalian Game (C50-59) Annotated Games 1850-1950dqtstock9555Оценок пока нет

- Agents of Edgewatch 2 - Sixty Feet Under - Interactive Maps PDFДокумент6 страницAgents of Edgewatch 2 - Sixty Feet Under - Interactive Maps PDFFrancisco Bravo FernándezОценок пока нет

- 【DSE中文範文】《論語.論仁、論孝、論君子》語譯及分析 - 尋補・BlogДокумент15 страниц【DSE中文範文】《論語.論仁、論孝、論君子》語譯及分析 - 尋補・BlogKatrina ChowОценок пока нет

- September 2019 - Io Midnight EphemerisДокумент1 страницаSeptember 2019 - Io Midnight Ephemerisfractal1Оценок пока нет

- Guitar Barre ChordsДокумент1 страницаGuitar Barre ChordsTaha ErdenОценок пока нет

- Endgame Corner: The Underestimated KnightДокумент7 страницEndgame Corner: The Underestimated KnightpiodasljkОценок пока нет

- Nokia E72 Rm-529, Rm-530 SchematicsДокумент29 страницNokia E72 Rm-529, Rm-530 SchematicsRuben De CampanaОценок пока нет

- Mastering The Chess Openings, Volume 3Документ353 страницыMastering The Chess Openings, Volume 3Justin Agluba100% (1)

- Karpovs Strategic Wins 2Документ7 страницKarpovs Strategic Wins 2Overmensch LogsОценок пока нет

- Chess Cryptosystem Alexandru Miron GATEJ: AbstractДокумент6 страницChess Cryptosystem Alexandru Miron GATEJ: AbstractJournal of Mobile, Embedded and Distributed Systems (JMEDS)Оценок пока нет

- AD9851 V100 SchematicsДокумент1 страницаAD9851 V100 SchematicsbaymanОценок пока нет

- Wilhelm Steinitz: Number of Games in Database: 890 Years Covered: 1859 To 1899 Overall Record: +453 - 191 154Документ2 страницыWilhelm Steinitz: Number of Games in Database: 890 Years Covered: 1859 To 1899 Overall Record: +453 - 191 154lyna_madaОценок пока нет

- 24tet-Quarter Tone Fingering Chart For SaxophoneДокумент4 страницы24tet-Quarter Tone Fingering Chart For SaxophoneGeorge Christian Vilela PereiraОценок пока нет

- Jacob Aagard - A Short Cut To ExperienceДокумент6 страницJacob Aagard - A Short Cut To ExperienceRenukha PannalaОценок пока нет