Академический Документы

Профессиональный Документы

Культура Документы

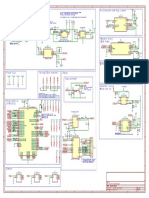

Piksi Schematics v2.3.1

Загружено:

Danut StanciuОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Piksi Schematics v2.3.1

Загружено:

Danut StanciuАвторское право:

Доступные форматы

0.47uF 0.

47uF

GND GND

GND

VCCIO

4.7uF 0.47uF 0.47uF 0.47uF 0.47uF

VCCIO

GND

VCCIO

GND

DNP

VCCIO

GND

GND

VCCIO

1

5

0

VCCIO

9

1

0

VCCIO

R

E

D

G

R

E

E

N

GND

GND

0.47uF

0.047uF 4.7uF

10K

U3

STM32-M-64-LQFP

VBAT

1

PC13-TAMPER-RTC

2

PC14-OSC32_IN

3

PC15-OSC32_OUT

4

PD0-OSC_IN-CANRX

5

PD1-OSC_OUT-CANTX

6

NRST

7

VSSA

12

VDDA

13

PA0-WKUP/USART2CTS/ADC0/TIM2CH1ETR

14

PA1-USART2RTS/ADC1/TIM2CH2

15

PA2-USART2TX/ADC2/TIM2CH3

16

PA3-USART2RX/ADC3/TIM2CH4

17

PA4-SPI1NSS/ADC4/USART2CK

20

PA5-SPI1SCK/ADC5

21

PA6-SPI1MISO/ADC6/TIM3CH1-TIM1BKIN

22

PA7-SPI1MOSI/ADC7/TIM3CH2-TIM1CH1N

23

PB0-ADC8/TIM3CH3-TIM1CH2N

26

PB1-ADC9/TIM3CH4-TIM1CH3N

27

PB2/BOOT1

28

PB10-I2C2SCL/USART3TX-TIM2CH3

29

PB11-I2C2SDA/USART3RX-TIM2CH4

30

VSS1

31

VDD1

32

PB12-SPI2NSS/I2C2SMBAI/USART3CK/TIM1BKIN

33

PB13-SPI2SCK/USART3CTS/TIM1CH1N

34

PB14-SPI2MISO/USART3RTS/TIM1CH2N

35

PB15-SPI2MOSI/TIM1CH3N

36

PA8-USART1CK/MCO/TIM1CH1

41

PA9-USART1TX/TIM1CH2

42

PA10-USART1RX/TIM1CH3

43

PA11-USART1CTS/CANRX/USBDM/TIM1CH4

44

PA12-USART1RTS/CANTX/USBDP/TIM1ETR

45

PA13/JTMS/SWDIO

46

VSS2

47

VDD2

48

PA14/JTCK/SWCLK

49

PA15/JTDI-TIM2CH1ETR/SPI1NSS

50

PB3/JTDO--TIM2CH2/TRACESWO/SPI1SCK

55

PB4/JNTRST--TIM3CH1/SPI1MISO

56

PB5-I2C1SMBAI-TIM3CH2/SPI1MOSI

57

PB6-I2C1SCL/TIM4CH1-USART1TX

58

PB7-I2C1SDA/TIM4CH2-USART1RX

59

BOOT0

60

PB8-TIM4CH3-I2C1SCL/CANRX

61

PB9-TIM4CH4-I2C1SDA/CANTX

62

VSS3

63

VDD3

64

PC0-ADC10

8

PC1-ADC11

9

PC2-ADC12

10

PC3-ADC13

11

PC4-ADC14

24

PC5-ADC15

25

PC6-TIM3CH1

37

PC7-TIM3CH2

38

PC8-TIM3CH3

39

PC9-TIM3CH4

40

PC10--USART3TX

51

PC11--USART3RX

52

PC12--USART3CK

53

PD2-TIM3ETR

54

VDD4

19

VSS4

18

C66 C82

C51 C52 C53 C54 C55

R34

R

2

8

R

3

0

L

E

D

1

L

E

D

2

P

$

1

P

$

2

B1 C32

C27 C33

R10

FPGA_PROGRAM_B

SPI2SCK

JTAG_TMS

JTAG_TCK

JTAG_TDO

JTAG_RST

UART1_TX

UART1_RX

MAX_PGM

MAX_NIDLE

MAX_NSHDN

SPI2NSS_MAX

MAX_ANT_FLAG

MAX_LD

FPGA_INIT_B

FPGA_DONE

SPI1NSS

SPI1SCK

SPI1MISO

SPI1MOSI

SPI2NSS_FLASH

SPI2MISO

SPI2MOSI

SPI2NSS_FPGA

UART3_TX

UART3_RX

TIM2CH3

TIM2CH4

TIM2CH2

TIM2CH1ETR

STM_CLK_IN

FTDI_NRST

UART6_TX/FTDI_ADBUS1

UART6_RX/FTDI_ADBUS0

V_USB

FPGA_TDO_STM_TDI

IO

IO

IO

IO

IO

IO IO

A

B

C

D

E

1 2 3 4 5 6 7 8

A

B

C

D

E

1 2 3 4 5 6 7 8

STM32F4 Microcontroller

Reset Button

STM has internal pull-up

STM32 Bypass

Piksi 2.3.1

Copyright (C) 2011-2013 Swift Navigation Inc.

License : CC BY-SA 3.0

Microcontroller

v2.3.1

6SLX9FTG256

6SLX9FTG256

6SLX9FTG256

6SLX9FTG256

6SLX9FTG256

GND

V

C

C

I

O

2K

V

C

C

I

O

V

C

C

I

O

V

C

C

I

O

0.47uF

GND

10K

GND

2K

VCCIO

330

V

C

C

I

O

2K

VCCIO

2K

GND

GND

V

C

C

I

O

V

C

C

I

O

V

C

C

I

O

V

C

C

I

O

V

C

C

I

O

GND

U1B0

VCCO_0

B13

VCCO_0

B4

VCCO_0

B9

VCCO_0

D10

VCCO_0

D7

IO_L1N_VREF_0

A4

IO_L1P_HSWAPEN_0

C4

IO_L2N_0

A5

IO_L2P_0

B5

IO_L3N_0

C5

IO_L3P_0

D5

IO_L4N_0

A6

IO_L4P_0

B6

IO_L5N_0

E6

IO_L5P_0

F7

IO_L6N_0

A7

IO_L6P_0

C7

IO_L7N_0

C6

IO_L7P_0

D6

IO_L33N_0

A8

IO_L33P_0

B8

IO_L34N_GCLK18_0

A9

IO_L34P_GCLK19_0

C9

IO_L35N_GCLK16_0

A10

IO_L35P_GCLK17_0

B10

IO_L36N_GCLK14_0

E8

IO_L36P_GCLK15_0

E7

IO_L37N_GCLK12_0

C10

IO_L37P_GCLK13_0

E10

IO_L38N_VREF_0

C8

IO_L38P_0

D8

IO_L39N_0

A11

IO_L39P_0

C11

IO_L40N_0

D9

IO_L40P_0

F9

IO_L62N_VREF_0

A12

IO_L62P_0

B12

IO_L63N_SCP6_0

A13

IO_L63P_SCP7_0

C13

IO_L64N_SCP4_0

E11

IO_L64P_SCP5_0

F10

IO_L65N_SCP2_0

A14

IO_L65P_SCP3_0

B14

IO_L66N_SCP0_0

D12

IO_L66P_SCP1_0

D11

U1B1

VCCO_1

D15

VCCO_1

G13

VCCO_1

J15

VCCO_1

K13

VCCO_1

N15

VCCO_1

R13

IO_L1N_A24_VREF_1

E12

IO_L1P_A25_1

E13

IO_L29N_A22_M1A14_1

B16

IO_L29P_A23_M1A13_1

B15

IO_L30N_A20_M1A11_1

G11

IO_L30P_A21_M1RESET_1

F12

IO_L31N_A18_M1A12_1

D16

IO_L31P_A19_M1CKE_1

D14

IO_L32N_A16_M1A9_1

F14

IO_L32P_A17_M1A8_1

F13

IO_L33N_A14_M1A4_1

C16

IO_L33P_A15_M1A10_1

C15

IO_L34N_A12_M1BA2_1

E16

IO_L34P_A13_M1WE_1

E15

IO_L35N_A10_M1A2_1

F16

IO_L35P_A11_M1A7_1

F15

IO_L36N_A8_M1BA1_1

G16

IO_L36P_A9_M1BA0_1

G14

IO_L37N_A6_M1A1_1

H16

IO_L37P_A7_M1A0_1

H15

IO_L38N_A4_M1CLKN_1

H11

IO_L38P_A5_M1CLK_1

G12

IO_L39N_M1ODT_1

H14

IO_L39P_M1A3_1

H13

IO_L40N_GCLK10_M1A6_1

J12

IO_L40P_GCLK11_M1A5_1

J11

IO_L41N_GCLK8_M1CASN_1

K14

IO_L41P_GCLK9_IRDY1_M1RASN_1

J13

IO_L42N_GCLK6_TRDY1_M1LDM_1

K11

IO_L42P_GCLK7_M1UDM_1

K12

IO_L43N_GCLK4_M1DQ5_1

J16

IO_L43P_GCLK5_M1DQ4_1

J14

IO_L44N_A2_M1DQ7_1

K16

IO_L44P_A3_M1DQ6_1

K15

IO_L45N_A0_M1LDQSN_1

N16

IO_L45P_A1_M1LDQS_1

N14

IO_L46N_FOE_B_M1DQ3_1

M16

IO_L46P_FCS_B_M1DQ2_1

M15

IO_L47N_LDC_M1DQ1_1

L16

IO_L47P_FWE_B_M1DQ0_1

L14

IO_L48N_M1DQ9_1

P16

IO_L48P_HDC_M1DQ8_1

P15

IO_L49N_M1DQ11_1

R16

IO_L49P_M1DQ10_1

R15

IO_L50N_M1UDQSN_1

T15

IO_L50P_M1UDQS_1

R14

IO_L51N_M1DQ13_1

T13

IO_L51P_M1DQ12_1

T14

IO_L52N_M1DQ15_1

T12

IO_L52P_M1DQ14_1

R12

IO_L53N_VREF_1

L13

IO_L53P_1

L12

IO_L74N_DOUT_BUSY_1

M14

IO_L74P_AWAKE_1

M13

U1B2

VCCO_2

N10

VCCO_2

N7

VCCO_2

R4

VCCO_2

R8

CMPCS_B_2

L11

DONE_2

P13

IO_L1N_M0_CMPMISO_2

T11

IO_L1P_CCLK_2

R11

IO_L2N_CMPMOSI_2

M11

IO_L2P_CMPCLK_2

M12

IO_L3N_MOSI_CSI_B_MISO0_2

T10

IO_L3P_D0_DIN_MISO_MISO1_2

P10

IO_L12N_D2_MISO3_2

P12

IO_L12P_D1_MISO2_2

N12

IO_L13N_D10_2

P11

IO_L13P_M1_2

N11

IO_L14N_D12_2

P9

IO_L14P_D11_2

N9

IO_L16N_VREF_2

M10

IO_L16P_2

L10

IO_L23N_2

T9

IO_L23P_2

R9

IO_L29N_GCLK2_2

N8

IO_L29P_GCLK3_2

M9

IO_L30N_GCLK0_USERCCLK_2

T8

IO_L30P_GCLK1_D13_2

P8

IO_L31N_GCLK30_D15_2

M7

IO_L31P_GCLK31_D14_2

P7

IO_L32N_GCLK28_2

T7

IO_L32P_GCLK29_2

R7

IO_L47N_2

T6

IO_L47P_2

P6

IO_L48N_RDWR_B_VREF_2

T5

IO_L48P_D7_2

R5

IO_L49N_D4_2

P5

IO_L49P_D3_2

N5

IO_L62N_D6_2

L7

IO_L62P_D5_2

L8

IO_L63N_2

T4

IO_L63P_2

P4

IO_L64N_D9_2

N6

IO_L64P_D8_2

M6

IO_L65N_CSO_B_2

T3

IO_L65P_INIT_B_2

R3

PROGRAM_B_2

T2

U1B3

VCCO_3

D2

VCCO_3

G4

VCCO_3

J2

VCCO_3

K4

VCCO_3

N2

IO_L1N_VREF_3

M3

IO_L1P_3

M4

IO_L2N_3

N4

IO_L2P_3

M5

IO_L32N_M3DQ15_3

R1

IO_L32P_M3DQ14_3

R2

IO_L33N_M3DQ13_3

P1

IO_L33P_M3DQ12_3

P2

IO_L34N_M3UDQSN_3

N1

IO_L34P_M3UDQS_3

N3

IO_L35N_M3DQ11_3

M1

IO_L35P_M3DQ10_3

M2

IO_L36N_M3DQ9_3

L1

IO_L36P_M3DQ8_3

L3

IO_L37N_M3DQ1_3

K1

IO_L37P_M3DQ0_3

K2

IO_L38N_M3DQ3_3

J1

IO_L38P_M3DQ2_3

J3

IO_L39N_M3LDQSN_3

H1

IO_L39P_M3LDQS_3

H2

IO_L40N_M3DQ7_3

G1

IO_L40P_M3DQ6_3

G3

IO_L41N_GCLK26_M3DQ5_3

F1

IO_L41P_GCLK27_M3DQ4_3

F2

IO_L42N_GCLK24_M3LDM_3

J4

IO_L42P_GCLK25_TRDY2_M3UDM_3

K3

IO_L43N_GCLK22_IRDY2_M3CASN_3

H5

IO_L43P_GCLK23_M3RASN_3

J6

IO_L44N_GCLK20_M3A6_3

H3

IO_L44P_GCLK21_M3A5_3

H4

IO_L45N_M3ODT_3

L5

IO_L45P_M3A3_3

L4

IO_L46N_M3CLKN_3

E1

IO_L46P_M3CLK_3

E2

IO_L47N_M3A1_3

K6

IO_L47P_M3A0_3

K5

IO_L48N_M3BA1_3

C2

IO_L48P_M3BA0_3

C3

IO_L49N_M3A2_3

D1

IO_L49P_M3A7_3

D3

IO_L50N_M3BA2_3

B1

IO_L50P_M3WE_3

C1

IO_L51N_M3A4_3

G5

IO_L51P_M3A10_3

G6

IO_L52N_M3A9_3

A2

IO_L52P_M3A8_3

B2

IO_L53N_M3A12_3

F3

IO_L53P_M3CKE_3

F4

IO_L54N_M3A11_3

E3

IO_L54P_M3RESET_3

E4

IO_L55N_M3A14_3

F5

IO_L55P_M3A13_3

F6

IO_L83N_VREF_3

A3

IO_L83P_3

B3

U1BNA

SUSPEND

P14

TCK

C14

TDI

C12

TDO

E14

TMS

A15

R13

C48

R14

NCS

1

DO

2

NWP

3

GND

4

DI

5

CLK

6

NHOLD

7

VCC

8

E

P

9

R15

R16

R17

R18

MAX_I1

MAX_I0

MAX_Q0

MAX_Q1

MAX_CLKOUT

SPI2MISO

SPI2MISO

JTAG_TCK

JTAG_TMS

FPGA_DONE

STM_CLK_IN

SPI2NSS_FLASH

SPI2NSS_FLASH

FPGA_INIT_B

FPGA_PROGRAM_B

SPI1SCK

SPI1NSS

SPI1MISO

SPI1MOSI

SPI2SCK

SPI2SCK

SPI2MOSI

SPI2MOSI

DEBUG6

DEBUG5

TIM2CH4

TIM2CH2

TIM2CH1ETR

TIM2CH3

FTDI_CLKOUT

FTDI_NTXE

FTDI_NWR

FTDI_ADBUS5

FTDI_ADBUS6

FTDI_ADBUS7

FPGA_TDO_STM_TDI

JTAG_TDI

FTDI_NRXF

FTDI_NRD

FTDI_NSIWU

FTDI_NOE

UART6_RX/FTDI_ADBUS0

UART6_TX/FTDI_ADBUS1

FTDI_ADBUS4

FTDI_ADBUS3

FTDI_ADBUS2

DEBUG9

DEBUG8

DEBUG7

DEBUG4

DEBUG3

DEBUG2

DEBUG1

DEBUG0

IO IO IO IO

IO

IO

IO

IO IO

IO

IO

IO

A

B

C

D

E

1 2 3 4 5 6 7 8

A

B

C

D

E

1 2 3 4 5 6 7 8

Spartan Configuration Flash

Spartan IO Banks

Bank 2

Bank 0

Bank 1

Bank 3

2K4 max for CCLK = 2MHz (default)

Short in CONF guide, but 2K is fine

2K4 or 4K7 recommended,

but 2K is fine

Could DNP as this is driven by STM

Spartan JTAG

Pulls up IO's during configuration

Piksi 2.3.1

Copyright (C) 2011-2013 Swift Navigation Inc.

License : CC BY-SA 3.0

FPGA IO Banks / JTAG / Flash

v2.3.1

GND

4.7uF 0.47uF 0.47uF

4.7uF 4.7uF 4.7uF 0.47uF

GND

GND

6SLX9FTG256

6SLX9FTG256 6SLX9FTG256

V

C

C

I

O

V

C

C

I

O

V

C

C

I

N

T V

C

C

I

N

T

4.7uF 0.47uF 0.47uF

GND

V

C

C

I

O

4.7uF 0.47uF

GND

V

C

C

I

O

4.7uF 0.47uF 0.47uF

GND

V

C

C

I

O

4.7uF 0.47uF

GND

V

C

C

I

O

100uF

100uF

100uF

100uF

4.7uF 4.7uF

100uF

100uF

0.47uF 0.47uF 4.7uF 0.47uF 0.47uF

C8 C22 C23

C28 C29 C30 C31

U1BGND

GND

A1

GND

A16

GND

B11

GND

B7

GND

D13

GND

D4

GND

E9

GND

G15

GND

G2

GND

G8

GND

H12

GND

H7

GND

H9

GND

J5

GND

J8

GND

K7

GND

K9

GND

L15

GND

L2

GND

M8

GND

N13

GND

P3

GND

R10

GND

R6

GND

T1

GND

T16

U1BVCCAUX

VCCAUX

E5

VCCAUX

F11

VCCAUX

F8

VCCAUX

G10

VCCAUX

H6

VCCAUX

J10

VCCAUX

L6

VCCAUX

L9

U1BVCCINT

VCCINT

G7

VCCINT

G9

VCCINT

H10

VCCINT

H8

VCCINT

J7

VCCINT

J9

VCCINT

K10

VCCINT

K8

C60 C62 C63

C61 C67 C71 C72 C73

C76 C77

C86

C87

C21

C24 C10 C17

C25

C26

C43 C46 C78 C80 C81 IO

IO

INT

INT

IO

IO IO

IO

A

B

C

D

E

1 2 3 4 5 6 7 8

A

B

C

D

E

1 2 3 4 5 6 7 8

Spartan 6 Bypass - VCCAUX

Spartan 6 Bypass - VCCINT

Spartan 6 Bypass - Bank 3

Spartan 6 Bypass - Bank 0 Spartan 6 Bypass - Bank 1

Spartan 6 Bypass - Bank 2

Piksi 2.3.1

Copyright (C) 2011-2013 Swift Navigation Inc.

License : CC BY-SA 3.0

FPGA Power Pins / Bypassing

v2.3.1

Spartan 6 Power Bypassing Spartan 6 Power Pins

Ground Pins

VCCAUX Pins VCCINT Pins

MAX2769_ANALOG

MAX2769_DIGITAL

MAX2769_PWR

100pF

GND

20k

470pF 27pF

GND

0.047uF

GND

27nH

100pF

12pF

GND

0.47uF 0.47uF 0.47uF

GND

0.47uF

GND GND

V

C

C

VCC

VCC

GND

GND

GND

4.7uF 4.7uF 0.047uF 4.7uF

10

GND GND

V

C

C

GND

PT7M8206B33TA5EX

GND

7Q-16.368MBG-T

GND GND GND GND

GND GND

GND GND

100pF

V

D

D

100pF

XC2401

GND

600

0.047uF

V

C

C

GND GND

100pF

0.47uF 0.47uF

GND

VCCIO

VCCIO

VCCIO

100pF 0.47uF

DNP

3.3nH

10k

VCCIO VCCIO

10k

10k

GND

5.1nH

2nH

GND

100pF 0.47uF

SAW_1.4X1.1

C14

R2

C18 C19

C20

L2

C37

C38

C39 C40 C42

C44

C6 C7

C9

C11

R65

VIN

1

G

N

D

2

EN

3

NC

4

VOUT

5

U12

G

N

D

2

2

G

N

D

1

1

OUT

3

VDD

4

U4

1

2345

U5 U5

1 2 345

J1

C95 C16

V

D

D

RFOUT

V

S

S

RFIN

U9

R11

C15 C47

C96 C107

U10_ANA

LNA_IN1

27

ANT_BIAS

3

LNA_IN2

25

XTAL

15

L

N

A

_

O

U

T

2

M

IX

_

IN

5

C

P

_

O

U

T

1

2

IDLE

24

SHDN

7

SCLK

9

CS

10

PGM

26

SDATA

8

I1

21

I0

20

Q0

18

Q1

17

CLK_OUT

16

ANT_FLAG

1

LD

6

U10_DIG

V

C

C

V

C

O

1

1

V

C

C

IF

2

3

V

C

C

A

D

C

1

9

V

C

C

R

F

4

V

C

C

C

P

1

3

V

C

C

D

1

4

E

P

G

N

D

2

9

NC1

22

NC2

28

U10_PWR

C12 C13

L1

L3

R12 R19

R20

L4

L5

C36 C41

RFIN

1

RFOUT

4

G

N

D

1

2

G

N

D

2

3

G

N

D

3

5

U8

MAX_ANT_FLAG

MAX_LD

MAX_I1

MAX_I0

MAX_Q0

MAX_Q1

MAX_CLKOUT

MAX_NSHDN

SPI2SCK

SPI2NSS_MAX

SPI2MOSI

MAX_NIDLE

MAX_PGM

3V3_RF

IO

IO

IO

IO IO

A

B

C

D

E

1 2 3 4 5 6 7 8

A

B

C

D

E

1 2 3 4 5 6 7 8

RF Frontend - Analog Section

RF LDO Regulator

RF Frontend Power Bypassing

RF Frontend - Digital Section

RF Frontend - Power Pins

Piksi 2.3.1

Copyright (C) 2011-2013 Swift Navigation Inc.

License : CC BY-SA 3.0

RF Frontend / RF Power

v2.3.1

VCCINT

LTC3407A_DFN

10K

GND

GND

22pF 22pF

634K

140K 200k

200k

GND GND GND GND

VCCIO

4.7uH 4.7uH

V

+

10uF

10uF 10uF

IRLML6401

GND

V

D

D

VFB1

1

R

U

N

/S

S

1

2

V

IN

3

SW1

4

G

N

D

1

5

M

O

D

E

/S

Y

N

C

6

SW2

7

NPOR

8

R

U

N

/S

S

2

9

VFB2

10

G

N

D

2

1

1

U2

R1

C5 C1

R61

R62 R63

R64

L13

1 2

L14

1 2

C2

C3 C4

Q1

1V2 3V3

INT IO

A

B

C

D

E

1 2 3 4 5 6 7 8

A

B

C

D

E

1 2 3 4 5 6 7 8

Route FB lines away from SW

Piksi 2.3.1

Copyright (C) 2011-2013 Swift Navigation Inc.

License : CC BY-SA 3.0

Digital Power Rails

v2.3.1

lines so they don't feedback

Digital 3V3 / 1V2 Power Rails

(1%)

93LC56BT

FT232H

20pF

20pF

GND

GND

GND GND

VCCIO

GND

2K

10k 10k 10k

VCCIO VCCIO VCCIO

0.047uF

12k

GND GND

0.047uF

GND

10k

VCCIO VCCIO

4.7uF 0.047uF

4.7uF 0.047uF

GND GND

Ferrite 600/0.5

Ferrite 600/0.5

4.7uF 0.047uF

4.7uF 0.047uF

GND

GND

VCCIO

0.047uF 0.047uF

VCCIO

GND

0.047uF

GND

0.047uF

DO

1

VSS

2

DI

3

CLK

4

CS

5

VCC

6

U6

VREGIN

40

VCCD

39

VCCCORE

38

VCCA

37

DM

6

DP

7

NRESET

34

REF

5

EECS

45

EECLK

44

EEDATA

43

XCSI

1

XCSO

2

TEST

42

A

G

N

D

1

4

A

G

N

D

2

9

A

G

N

D

3

4

1

G

N

D

1

1

0

G

N

D

2

1

1

G

N

D

3

2

2

G

N

D

4

2

3

G

N

D

5

3

5

G

N

D

6

3

6

G

N

D

7

4

7

G

N

D

8

4

8

AC9

33

AC8

32

AC7

31

AC6

30

AC5

29

AC4

28

AC3

27

AC2

26

AC1

25

AC0

21

AD7

20

AD6

19

AD5

18

AD4

17

AD3

16

AD2

15

AD1

14

AD0

13

V

P

H

Y

3

V

P

L

L

8

V

C

C

IO

1

1

2

V

C

C

IO

2

2

4

V

C

C

IO

3

4

6

E

P

G

N

D

4

9

U7

C34

C35

R3

R4 R5 R6

C45

R7

C49

R9

C50 C56

C57 C58

L10

L11

C59 C64

C65 C68

C69 C70

X4

C75

C74

USB_DM

USB_DP

FTDI_NRST

UART6_RX/FTDI_ADBUS0

V_USB

FTDI_ADBUS5

FTDI_ADBUS6

FTDI_ADBUS7

FTDI_CLKOUT

FTDI_NWR

FTDI_NTXE

FTDI_NRXF

FTDI_NRD

FTDI_NSIWU

FTDI_NOE

FTDI_ADBUS4

FTDI_ADBUS3

FTDI_ADBUS2

UART6_TX/FTDI_ADBUS1

IO IO IO IO

IO IO

IO

IO

A

B

C

D

E

1 2 3 4 5 6 7 8

A

B

C

D

E

1 2 3 4 5 6 7 8

FT232H UART/FIFO to USB

Piksi 2.3.1

Copyright (C) 2011-2013 Swift Navigation Inc.

License : CC BY-SA 3.0

FTDI UART / FIFO to USB

v2.3.1

GND

MOUNT-PAD-ROUNDM3

MOUNT-PAD-ROUNDM3

MOUNT-PAD-ROUNDM3

MOUNT-PAD-ROUNDM3

BMI-S-208

GND

GND

GND

VCCIO

V+

1

0

K

GND

V+ VCCIO

GND

V+ VCCIO

GND

GND

V+

H2

H3

H4

H5

1234567

8

9

10

11

12

13

14

1

5

1

6

1

7

1

8

1

9

2

0

2

1

22

23

24

25

26

27

28

SHLD2

1

2

3

4

5

D1

X5

1 2

3 4

5 6

7 8

9 10

R

8

X6

1

2

3

4

5

X1

1

2

3

4

5

1

2

3

4

5

6

7

8

9

10

11

12

X3

USB_DM

USB_DP

JTAG_TMS

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_RST

V_USB

UART1_TX

UART1_RX

UART3_TX

UART3_RX

DEBUG6

DEBUG5

DEBUG4

DEBUG3

DEBUG2

DEBUG1

DEBUG0

DEBUG7

DEBUG8

DEBUG9

IO

IO

IO

Logo

A

B

C

D

E

1 2 3 4 5 6 7 8

A

B

C

D

E

1 2 3 4 5 6 7 8

TDI

TDO

STM32 SPARTAN6

RF shield

USB

JTAG

JTAG chain (for reference)

UART1

UART3

Mounting Holes

Fiducials

Logo

Piksi 2.3.1

Copyright (C) 2011-2013 Swift Navigation Inc.

License : CC BY-SA 3.0

Connectors / Misc

v2.3.1

FPGA DEBUG

Вам также может понравиться

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- Non Imaging Optics DizertationДокумент92 страницыNon Imaging Optics DizertationDanut Stanciu100% (1)

- Non Imagistic Optics Aop-10-2-4841Документ29 страницNon Imagistic Optics Aop-10-2-4841Danut StanciuОценок пока нет

- Ref BiblДокумент1 страницаRef BiblDanut StanciuОценок пока нет

- New Layout Dish StirlingДокумент10 страницNew Layout Dish StirlingDanut StanciuОценок пока нет

- LLC Multiple VoltageДокумент2 страницыLLC Multiple VoltageDanut StanciuОценок пока нет

- ZSWatch KicadДокумент1 страницаZSWatch KicadDanut StanciuОценок пока нет

- PFCДокумент1 страницаPFCDanut StanciuОценок пока нет

- LLC Transformer CalculationДокумент49 страницLLC Transformer CalculationDanut StanciuОценок пока нет

- KT1025A Datasheet: Shenzhen Qingyue Electronics Co., LTDДокумент12 страницKT1025A Datasheet: Shenzhen Qingyue Electronics Co., LTDDanut StanciuОценок пока нет

- Launch Ástudio Á Álisting Ádetails - AC692xДокумент3 страницыLaunch Ástudio Á Álisting Ádetails - AC692xDanut Stanciu0% (1)

- Ampliful MarcelДокумент15 страницAmpliful MarcelDanut StanciuОценок пока нет

- Design Guide LLC Resonant Tank Design 3 3kw Ev Board Charger Obc 20170505Документ7 страницDesign Guide LLC Resonant Tank Design 3 3kw Ev Board Charger Obc 20170505Danut StanciuОценок пока нет

- E1EEFQ 2016 v11n2 383Документ10 страницE1EEFQ 2016 v11n2 383Danut StanciuОценок пока нет

- Curves and Surfaces (MA3152) : DR J. M Inroy, Adapted From Lecture Notes by DR K. LeschkeДокумент90 страницCurves and Surfaces (MA3152) : DR J. M Inroy, Adapted From Lecture Notes by DR K. LeschkeDanut StanciuОценок пока нет

- L6598 PDFДокумент23 страницыL6598 PDFDanut StanciuОценок пока нет

- Direct Alcohol Fuel Cells Materials, Performance, Durability and ApplicationsДокумент377 страницDirect Alcohol Fuel Cells Materials, Performance, Durability and ApplicationsDanut StanciuОценок пока нет

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- WEST COAST PRODUCTIONS, INC 4:12-cv-00748-FRBДокумент11 страницWEST COAST PRODUCTIONS, INC 4:12-cv-00748-FRBcopyrightclerkОценок пока нет

- Instant Download Solution Manual For Computer Science An Overview 13th Edition Glenn Brookshear Dennis Brylow PDF ScribdДокумент23 страницыInstant Download Solution Manual For Computer Science An Overview 13th Edition Glenn Brookshear Dennis Brylow PDF Scribdmasonandersonphdkpgtrenxwf100% (13)

- Transcript of Summary Judgement HearingДокумент57 страницTranscript of Summary Judgement Hearingduffi6978100% (1)

- MCQs On Copyright Act in India Question and Answers - The Legal InfoДокумент3 страницыMCQs On Copyright Act in India Question and Answers - The Legal InfoAnupamОценок пока нет

- Othello Trademark LawsuitДокумент23 страницыOthello Trademark LawsuitMark Jaffe0% (1)

- Black Invention MythsДокумент16 страницBlack Invention MythsjoetylorОценок пока нет

- Eaton Fuller 15webДокумент4 страницыEaton Fuller 15webmancorabechОценок пока нет

- Men and Names of Old BirminghamДокумент113 страницMen and Names of Old Birminghamanthony1389Оценок пока нет

- HGM170 170HC V1.0 enДокумент6 страницHGM170 170HC V1.0 enMubashir AhmadОценок пока нет

- Ri 700Документ1 страницаRi 700Hung NguyenОценок пока нет

- Living The Good Life A Beginner's Thomistic Ethics - (Intro)Документ7 страницLiving The Good Life A Beginner's Thomistic Ethics - (Intro)FallenKiwi0% (1)

- SSRN Id3032076Документ49 страницSSRN Id3032076vanesa proyeccionОценок пока нет

- Black & Decker v. Positec - ComplaintДокумент11 страницBlack & Decker v. Positec - ComplaintSarah BursteinОценок пока нет

- ESPRIT Get StartedДокумент200 страницESPRIT Get StartedSandaruwan සුජීවОценок пока нет

- Britannica Mathematics in Context Data Analysis and Probability Great PredictionsДокумент69 страницBritannica Mathematics in Context Data Analysis and Probability Great Predictionskeynet4Оценок пока нет

- Sonicision 2Документ2 страницыSonicision 2Rinaldi SinagaОценок пока нет

- Case: Pickett V. Prince PONENTE: POSNER, Chief Judge. Recit ReadyДокумент3 страницыCase: Pickett V. Prince PONENTE: POSNER, Chief Judge. Recit ReadyjuslynsОценок пока нет

- Noriko BagДокумент4 страницыNoriko BagAshlin KATASTROPHE100% (10)

- Columbia Pictures Inc Vs CA - 1994Документ3 страницыColumbia Pictures Inc Vs CA - 1994Elead Gaddiel S. AlbueroОценок пока нет

- Astm 1157 - 20Документ5 страницAstm 1157 - 20nolanjc100% (1)

- Reading Comprehension Vegetables Copyright Teacher Created Resources PDFДокумент7 страницReading Comprehension Vegetables Copyright Teacher Created Resources PDFkieu oanh PhamОценок пока нет

- Salenillas V CAДокумент2 страницыSalenillas V CAcoun_marwinОценок пока нет

- FrontmatterДокумент11 страницFrontmatterMillian PasaribuОценок пока нет

- La Lengua Inglesa A Tu Alcance Manual de Preposiciones y Conjunciones 154 To 180Документ27 страницLa Lengua Inglesa A Tu Alcance Manual de Preposiciones y Conjunciones 154 To 180Geder Alex Mamani Nina100% (1)

- Chapter6 ConceptGenerationДокумент47 страницChapter6 ConceptGenerationAntaryami Mishra50% (2)

- Intellectual Property LawsДокумент66 страницIntellectual Property LawsMohammed RaeesОценок пока нет

- Interception License: RecitalsДокумент5 страницInterception License: RecitalsaguacateОценок пока нет

- Yr5 English Lesson5Документ24 страницыYr5 English Lesson5Mai - Patcharee RushОценок пока нет

- Model SheetДокумент2 страницыModel SheetRip BhennettОценок пока нет

- Google SWOT Analysis 2013 Strengths Weaknesses: Opportunities ThreatsДокумент1 страницаGoogle SWOT Analysis 2013 Strengths Weaknesses: Opportunities Threatsneha aggarwal0% (1)