Академический Документы

Профессиональный Документы

Культура Документы

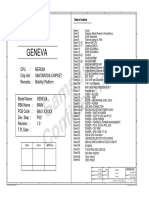

Schematic Content: TERASIC CYCLONE II EP2C35 Development & Education BOARD

Загружено:

Pablo VargasИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Schematic Content: TERASIC CYCLONE II EP2C35 Development & Education BOARD

Загружено:

Pablo VargasАвторское право:

Доступные форматы

5

TERASIC CYCLONE II EP2C35 Development & Education

D

SCHEMATIC

TOP

AUDIO

DISPLAY

EP2C35

ETHERNET

IN/OUT

MEMORY

POWER

USB BLASTER

USB DEVICE

VIDEO

BOARD

CONTENT

PAGE

COVER PAGE , TOP

WM8731

LCD , LED , 7SEGMENT

EP2C35 BANK1..BANK8 , POWER , CONFIG

DM9000A

CLOCK , PS2 , RS232 , KEY , SWITCH , CONNECT

SRAM , DRAM , FLASH , SD CARD

POWER

USB BLASTER

USB DEVICE

ADV7181 , ADV7123

01

04

05

07

12

13

18

20

21

22

23

~

~

~

~

~

~

~

~

~

~

~

03

04

06

11

12

17

19

20

21

22

24

Title

ALTERA DE2

Size

B

Date:

5

Document Number

COVER PAGE

Sunday, July 23, 2006

Rev

2.0

Sheet

1

of

24

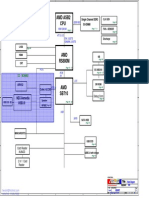

DC

9V

USB

BLASTER

USB

DEVICE

USB

HOST

LINE LINE MIC

IN

OUT IN

TV

DECODER

VGA

OUTPUT

RJ45

RS232

PS2

KEYBORAD

WM8731

ADV7181

ADV7123

DM9000A

GPIO_0

ISP1362

GPIO_1

FT245

M3128

LCD MODULE

EP2C35

SD CARD

EPCS16

SDRAM

SRAM

IrDA

FLASH

LEDG0

KEY0

LEDG1

LEDG2

KEY1

LEDG3

LEDG4

SW0

SW1

SW2

SW3

SW4

SW5

SW6

SW7

SW8

SW9

SW10

SW11

SW12

SW13

SW14

SW15

SW16

SW17

KEY2

LEDG5

KEY3

LEDG6

LEDG7

LEDR0

LEDR1

HEX0

LEDR2

HEX1

LEDR3

HEX2

LEDR4

LEDR5

LEDR6

HEX3

LEDR8

LEDR7

LEDR8

HEX4

LEDR9

HEX5

LEDR10

LEDR11

LEDR12

HEX6

LEDR13

LEDR14

LEDR15

LEDR16

LEDR17

HEX7

EXT CLK

Title

ALTERA DE2

Size

B

Date:

5

Document Number

PLACEMENT

Sunday, July 23, 2006

Rev

2.0

Sheet

1

of

24

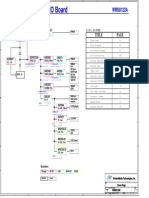

MEMORY

FLASH_RESET

FLASH_WE

FLASH_CE

FLASH_OE

FLASH_A[0..21]

DRAM_CLK

DRAM_CKE

DRAM_BA0

DRAM_BA1

DRAM_WE

DRAM_CAS

DRAM_RAS

DRAM_CS

DRAM_LDQM

DRAM_UDQM

DRAM_A[0..11]

SRAM_WE

SRAM_CE

SRAM_OE

SRAM_UB

SRAM_LB

SRAM_A[0..17]

SD_CLK

SD_CMD

SD_DAT3

FLASH_RESET

FLASH_WE

FLASH_CE

FLASH_OE

FLASH_A[0..21]

DRAM_CLK

DRAM_CKE

DRAM_BA0

DRAM_BA1

DRAM_WE

DRAM_CAS

DRAM_RAS

DRAM_CS

DRAM_LDQM

DRAM_UDQM

DRAM_A[0..11]

SRAM_WE

SRAM_CE

SRAM_OE

SRAM_UB

SRAM_LB

SRAM_A[0..17]

SD_CLK

SD_CMD

SD_DAT3

PWR

PAGE 18-19

FLASH_D[0..7]

DRAM_D[0..15]

SRAM_D[0..15]

SD_DAT

EP2S35

FLASH_D[0..7]

FLASH_RESET

FLASH_WE

FLASH_CE

FLASH_OE

FLASH_A[0..21]

FLASH_D[0..7]

DRAM_D[0..15]

DRAM_CLK

DRAM_CKE

DRAM_BA0

DRAM_BA1

DRAM_WE

DRAM_CAS

DRAM_RAS

DRAM_CS

DRAM_LDQM

DRAM_UDQM

DRAM_A[0..11]

DRAM_D[0..15]

SRAM_D[0..15]

SRAM_D[0..15]

SRAM_WE

SRAM_CE

SRAM_OE

SRAM_UB

SRAM_LB

SRAM_A[0..17]

SD_DAT

SD_DAT

SD_CLK

SD_CMD

SD_DAT3

PAGE 20

USB BLASTER

TDO

TDO

LINK_D3

LINK_D3

DCLK

NCSO

ASDO

TDI

TMS

TCK

NCE

NCONFIG

CONF_DONE

NSTATUS

DATA0

LINK_D0

LINK_D1

LINK_D2

12MHZ

USB DEVICE

12MHZ

DCLK

NCSO

ASDO

TDI

TMS

TCK

NCE

NCONFIG

CONF_DONE

NSTATUS

DATA0

LINK_D0

LINK_D1

LINK_D2

TDO

LINK_D3

AUD_ADCDAT

AUD_BCLK

AUD_DACDAT

AUD_ADCLRCK

AUD_DACLRCK

AUD_XCK

DRAM_D[0..15]

DRAM_CLK

DRAM_CKE

DRAM_BA0

DRAM_BA1

DRAM_WE

DRAM_CAS

DRAM_RAS

DRAM_CS

DRAM_LDQM

DRAM_UDQM

DRAM_A[0..11]

I2C_SDAT

I2C_SCLK

HEX0_D[0..6]

HEX1_D[0..6]

HEX2_D[0..6]

HEX3_D[0..6]

HEX4_D[0..6]

HEX5_D[0..6]

HEX6_D[0..6]

HEX7_D[0..6]

SRAM_D[0..15]

SRAM_WE

SRAM_CE

SRAM_OE

SRAM_UB

SRAM_LB

SRAM_A[0..17]

LCD_BLON

LCD_ON

LCD_WR

LCD_EN

LCD_RS

LCD_D[0..7]

LED[0..4]

LED[5..26]

SD_DAT

SD_CLK

SD_CMD

SD_DAT3

ENET_INT

ENET_D[0..15]

OTG_WE

OTG_OE

OTG_RESET

OTG_DACK0

OTG_DACK1

OTG_CS

OTG_A1

OTG_A0

OTG_INT1

OTG_INT0

OTG_DREQ1

OTG_DREQ0

OTG_LSPEED

OTG_FSPEED

OTG_D[0..15]

OTG_WE

OTG_OE

OTG_RESET

OTG_DACK0

OTG_DACK1

OTG_CS

OTG_A1

OTG_A0

PAGE 22

VIDEO

TD_RESET

VGA_CLOCK

VGA_BLANK

VGA_SYNC

VGA_HS

VGA_VS

VGA_R[0..9]

VGA_G[0..9]

VGA_B[0..9]

I2C_SCLK

TD_RESET

VGA_CLOCK

VGA_BLANK

VGA_SYNC

VGA_HS

VGA_VS

VGA_R[0..9]

VGA_G[0..9]

VGA_B[0..9]

I2C_SCLK

OTG_INT1

OTG_INT0

OTG_DREQ1

OTG_DREQ0

OTG_LSPEED

OTG_FSPEED

OTG_D[0..15]

OTG_INT1

OTG_INT0

OTG_DREQ1

OTG_DREQ0

OTG_LSPEED

OTG_FSPEED

OTG_D[0..15]

27MHz

TD_CLK27

TD_HS

TD_VS

TD_D[0..7]

PAGE 23-24

27MHz

TD_CLK27

TD_HS

TD_VS

TD_D[0..7]

I2C_SDAT

25MHZ

ENET_RESET

ENET_CMD

ENET_IOR

ENET_IOW

ENET_CS

DCLK

NCSO

ASDO

TDI

TMS

TCK

NCE

NCONFIG

CONF_DONE

NSTATUS

DATA0

LINK_D0

LINK_D1

LINK_D2

50MHZ

EXT_CLOCK

UART_RXD

UART_TXD

IRDA_RXD

IRDA_TXD

PS2_DAT

PS2_CLK

TDO

LINK_D3

GPIO_B[0..71]

12MHZ

12MHZ

OTG_WE

OTG_OE

OTG_RESET

OTG_DACK0

OTG_DACK1

OTG_CS

OTG_A1

OTG_A0

PAGE 21

27MHz

TD_CLK27

TD_HS

TD_VS

TD_D[0..7]

TD_RESET

VGA_CLOCK

VGA_BLANK

VGA_SYNC

VGA_HS

VGA_VS

VGA_R[0..9]

VGA_G[0..9]

VGA_B[0..9]

I2C_SDAT

PAGE 7-11

FLASH_D[0..7]

FLASH_RESET

FLASH_WE

FLASH_CE

FLASH_OE

FLASH_A[0..21]

DCLK

NCSO

ASDO

TDI

TMS

TCK

NCE

NCONFIG

CONF_DONE

NSTATUS

DATA0

LINK_D0

LINK_D1

LINK_D2

SW[0..2]

SW[3..5]

SW[6..9]

SW[10..17]

OTG_INT1

OTG_INT0

OTG_DREQ1

OTG_DREQ0

OTG_LSPEED

OTG_FSPEED

OTG_D[0..15]

OTG_WE

OTG_OE

OTG_RESET

OTG_DACK0

OTG_DACK1

OTG_CS

OTG_A1

OTG_A0

KEY[0..3]

AUDIO

AUD_ADCDAT

AUD_BCLK

AUD_DACDAT

AUD_ADCLRCK

AUD_DACLRCK

AUD_XCK

AUD_BCLK

AUD_DACDAT

AUD_ADCLRCK

AUD_DACLRCK

AUD_XCK

I2C_SCLK

I2C_SCLK

I2C_SDAT

I2C_SCLK

AUD_ADCDAT

AUD_ADCDAT

I2C_SDAT

I2C_SDAT

HEX0_D[0..6]

HEX1_D[0..6]

HEX2_D[0..6]

HEX3_D[0..6]

HEX4_D[0..6]

HEX5_D[0..6]

HEX6_D[0..6]

HEX7_D[0..6]

DISPLAY

HEX0_D[0..6]

HEX1_D[0..6]

HEX2_D[0..6]

HEX3_D[0..6]

HEX4_D[0..6]

HEX5_D[0..6]

HEX6_D[0..6]

HEX7_D[0..6]

LCD_BLON

LCD_ON

LCD_WR

LCD_EN

LCD_RS

LCD_D[0..7]

LCD_BLON

LCD_ON

LCD_WR

LCD_EN

LCD_RS

LCD_D[0..7]

LED[0..4]

LED[5..26]

LCD_BLON

LCD_ON

LCD_WR

LCD_EN

LCD_RS

LCD_D[0..7]

LED[0..26]

LED[0..26]

ENET_INT

ENET_D[0..15]

ETHERNET

25MHZ

ENET_RESET

ENET_CMD

ENET_IOR

ENET_IOW

ENET_CS

PAGE 5-6

HEX0_D[0..6]

HEX1_D[0..6]

HEX2_D[0..6]

HEX3_D[0..6]

HEX4_D[0..6]

HEX5_D[0..6]

HEX6_D[0..6]

HEX7_D[0..6]

25MHZ

PAGE 12

25MHZ

ENET_INT

ENET_INT

ENET_RESET

ENET_CMD

ENET_IOR

ENET_IOW

ENET_CS

ENET_RESET

ENET_CMD

ENET_IOR

ENET_IOW

ENET_CS

ENET_D[0..15]

ENET_D[0..15]

50MHZ

EXT_CLOCK

UART_RXD

UART_TXD

INPUT

PAGE 13-17

50MHZ

IRDA_RXD

IRDA_TXD

EXT_CLOCK

UART_TXD

PS2_DAT

PS2_CLK

IRDA_TXD

GPIO_B[0..71]

PS2_CLK

UART_TXD

UART_RXD

IRDA_TXD

IRDA_RXD

PS2_CLK

PS2_DAT

SW[0..2]

SW[3..5]

SW[6..9]

SW[10..17]

GPIO_B[0..71]

SW[0..17]

KEY[0..3]

KEY[0..3]

50MHZ

EXT_CLOCK

UART_RXD

IRDA_RXD

PS2_DAT

GPIO_B[0..71]

SW[0..17]

KEY[0..3]

27MHz

TD_CLK27

TD_HS

TD_VS

TD_D[0..7]

TD_RESET

VGA_CLOCK

VGA_BLANK

VGA_SYNC

VGA_HS

VGA_VS

VGA_R[0..9]

VGA_G[0..9]

VGA_B[0..9]

Title

ALTERA DE2

Size

B

Date:

PAGE 4

AUD_BCLK

AUD_DACDAT

AUD_ADCLRCK

AUD_DACLRCK

AUD_XCK

Document Number

TOP LEVEL

Wednesday, August 02, 2006

Rev

2.0

Sheet

1

of

24

C2 1U

R3

4.7K

R4

4.7K

5

2

4

1

3

C1 1U

LINE IN

NCL

R

NCR

L

GND

J2

PHONE JACK B

VCC33 VCC33

R1

R2

2K

2K

R5

R6

4.7K

4.7K

AGND

AGND

J1

R7

1U

21

20

19

18

17

16

15

680

C5 10U

AGND

A_VCC33

C4

R9

1000P

47K

AGND

J3

AGND

AGND

AGND

LINE OUT

NCL

R

NCR

L

GND

WM8731

R8

MBIAS

VMID

AGND

AVDD

ROUT

LOUT

HPGND

5

2

4

1

3

XTI/MCLK

XTO

DCVDD

DGND

DBVDD

CLKOUT

BCLK

PHONE JACK P

PHONE JACK G

8

9

10

11

12

13

14

1

2

3

4

5

6

7

DACDAT

DACLRCK

ADCDAT

ADCLRCK

HPVDD

LHPOUT

RHPOUT

A_VCC33

5

2

4

1

3

C3

SCLK

SDIN

CSB

MODE

LLINEIN

RLINEIN

MICIN

MIC IN

330

28

27

26

25

24

23

22

I2C ADDRESS READ IS 0x34

I2C ADDRESS WRITE IS 0x35 U1

AUD_XCK

AUD_BCLK

AUD_DACDAT

AUD_DACLRCK

AUD_ADCDAT

AUD_ADCLRCK

AGND

NCL

R

NCR

L

GND

I2C_SDAT

I2C_SCLK

TC1

100U/6.3V

TC2

100U/6.3V

A_VCC33

R10

R11

47K

47K

AGND

A_VCC33

AGND

L1

AGND

BEAD

AGND

BC1

BC2

BC3

BC4

0.1U

0.1U

0.1U

0.1U

Title

ALTERA DE2

AGND

Size

A

Date:

5

Document Number

AUDIO

Tuesday, July 25, 2006

2

Rev

2.0

Sheet

of

1

24

LEDR0

LEDR

LEDR1

LEDR

LEDR2

LEDR

LEDR3

LEDR

LEDR4

LEDR

LEDR5

LEDR

RN1

Q1

8050

Q2

LED0

LED1

LED2

LED3

8550

1

2

3

4

8

7

6

5

330

C6

VCC5

R12

VCC43

680

1U

RN2

LCD_ON

R13

680

Q3

8050

VCC43

Q4

LED4

LED5

LED6

LED7

8550

VCC43

1

2

3

4

330

R16

8

7

6

5

LEDR6

LEDR

LEDR7

LEDR

RN6

LED19

LED20

LED21

LED22

1

2

3

4

8

7

6

5

330

LEDG0

LEDG

LEDG1

LEDG

LEDG2

LEDG

LEDG3

LEDG

C

1K

LCD_D[0..7]

680

LCD_BLON

R14

680

Q5

8050

LEDR8

LCD_BL

LCD_D7

LCD_D6

LCD_D5

LCD_D4

LCD_D3

LCD_D2

LCD_D1

LCD_D0

LCD_EN

LCD_WR

LCD_RS

LCD_CONT

LCD_VCC

R15

LED[0..26]

LEDR

R17

47

LED8

LED9

LED18

1

2

3

4

8

7

6

5

LEDR9

LEDG8

RN7

LEDR

LEDG

LED23

LED24

LED25

LED26

1

2

3

4

8

7

6

5

330

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

330

GND

BL

D7

D6

D5

D4

D3

D2

D1

D0

EN

WR

RS

CONT

VCC

GND

U2

LEDG4

LEDG

LEDG5

LEDG

LEDG6

LEDG

LEDG7

LEDG

RN3

RN4

LED10

LED11

LED12

LED13

2 X 16 DIGIT LCD

1

2

3

4

8

7

6

5

330

LEDR10

LEDR

LEDR11

LEDR

LEDR12

LEDR

LEDR13

LEDR

LEDR14

LEDR

LEDR15

LEDR

LEDR16

LEDR

LEDR17

LEDR

LCD-2x16

RN5

LED14

LED15

LED16

LED17

1

2

3

4

8

7

6

5

330

Title

ALTERA DE2

Size

B

Date:

5

Document Number

LCD AND LED

Tuesday, July 25, 2006

Rev

2.0

Sheet

1

of

24

RN22

HEX0_D[0..6]

HEX1_D[0..6]

D

HEX7_D0

HEX7_D1

HEX7_D2

HEX7_D3

HEX2_D[0..6]

1

2

3

4

HEX4_D[0..6]

HEX7

8

7

6

5

A7

B7

C7

D7

330

RN23

HEX3_D[0..6]

HEX7_D4

HEX7_D5

HEX7_D6

HEX5_D[0..6]

1

2

3

4

8

7

6

5

E7

F7

G7

10

9

8

5

4

2

3

7

a

b

c

d

e

f

g

dp

RN20

HEX6_D0

HEX6_D1

HEX6_D2

HEX6_D3

VCC33

CA1

CA2

1

6

1

2

3

4

HEX6

8

7

6

5

A6

B6

C6

D6

10

9

8

5

4

2

3

7

330

RN21

HEX6_D4

HEX6_D5

HEX6_D6

7Segment Display

1

2

3

4

330

HEX6_D[0..6]

8

7

6

5

E6

F6

G6

8

7

6

5

A4

B4

C4

D4

a

b

c

d

e

f

g

dp

VCC33

CA1

CA2

1

6

7Segment Display

330

HEX7_D[0..6]

RN18

HEX5_D0

HEX5_D1

HEX5_D2

HEX5_D3

1

2

3

4

HEX5

8

7

6

5

A5

B5

C5

D5

330

RN19

HEX5_D4

HEX5_D5

HEX5_D6

1

2

3

4

8

7

6

5

E5

F5

G5

10

9

8

5

4

2

3

7

a

b

c

d

e

f

g

dp

RN16

HEX4_D0

HEX4_D1

HEX4_D2

HEX4_D3

VCC33

CA1

CA2

1

6

1

2

3

4

330

RN17

HEX4_D4

HEX4_D5

HEX4_D6

7Segment Display

1

2

3

4

330

1

2

3

4

HEX3

8

7

6

5

A3

B3

C3

D3

330

RN15

HEX3_D4

HEX3_D5

HEX3_D6

1

2

3

4

8

7

6

5

E3

F3

G3

10

9

8

5

4

2

3

7

a

b

c

d

e

f

g

dp

CA1

CA2

1

6

1

2

3

4

1

2

3

4

HEX2_D4

HEX2_D5

HEX2_D6

1

2

3

4

HEX1

8

7

6

5

1

2

3

4

A2

B2

C2

D2

CA2

1

6

HEX2

10

9

8

5

4

2

3

7

8

7

6

5

E2

F2

G2

a

b

c

d

e

f

g

dp

VCC33

CA1

CA2

1

6

7Segment Display

330

A1

B1

C1

D1

330

RN11

HEX1_D4

HEX1_D5

HEX1_D6

8

7

6

5

VCC33

CA1

7Segment Display

330

RN13

7Segment Display

RN10

HEX1_D0

HEX1_D1

HEX1_D2

HEX1_D3

E4

F4

G4

RN12

HEX2_D0

HEX2_D1

HEX2_D2

HEX2_D3

VCC33

330

8

7

6

5

a

b

c

d

e

f

g

dp

330

RN14

HEX3_D0

HEX3_D1

HEX3_D2

HEX3_D3

HEX4

10

9

8

5

4

2

3

7

8

7

6

5

E1

F1

G1

10

9

8

5

4

2

3

7

a

b

c

d

e

f

g

dp

RN8

HEX0_D0

HEX0_D1

HEX0_D2

HEX0_D3

VCC33

CA1

CA2

1

6

1

2

3

4

HEX0

8

7

6

5

A0

B0

C0

D0

10

9

8

5

4

2

3

7

330

RN9

HEX0_D4

HEX0_D5

HEX0_D6

7Segment Display

330

1

2

3

4

8

7

6

5

E0

F0

G0

a

b

c

d

e

f

g

dp

VCC33

CA1

CA2

1

6

7Segment Display

330

Title

ALTERA DE2

Size

B

Date:

5

Document Number

7 SEGMENT

Sunday, July 23, 2006

Rev

2.0

Sheet

1

of

24

HEX7_D[0..6]

LCD_D[0..7]

HEX6_D[0..6]

SW[10..17]

HEX5_D[0..6]

OTG_D[0..15]

HEX4_D[0..6]

DRAM_D[0..15]

DRAM_A[0..11]

U11A

U11B

DRAM_RAS

DRAM_CAS

DRAM_BA1

DRAM_BA0

DRAM_WE

DRAM_LDQM

DRAM_UDQM

DRAM_D15

DRAM_D14

DRAM_D13

DRAM_D12

DRAM_D11

DRAM_D10

DRAM_D9

DRAM_D6

DRAM_D5

AB4

AB3

AE3

AE2

AD3

AD2

Y5

AA5

AC1

AC2

AA3

AA4

AB1

AB2

T8

R8

LVDS0n

LVDS0p

LVDS1n

LVDS1p

LVDS2n

LVDS2p

LVDS3n

LVDS3p

LVDS4n

LVDS4p

LVDS5n

LVDS5p

LVDS6n

LVDS6p

LVDS7n

LVDS7p

DRAM_D4

DRAM_D3

DRAM_D2

DRAM_D1

DRAM_D0

DRAM_A11

DRAM_A9

DRAM_A8

DRAM_A6

DRAM_A5

DRAM_A4

DRAM_A3

DRAM_A2

DRAM_A1

DRAM_A0

SW13

Y4

Y3

AA1

AA2

V6

V5

W3

W4

U7

U6

W1

W2

V3

V4

T6

T7

DRAM_A7

DRAM_D7

DRAM_A10

DRAM_CS

U5

V7

Y1

AC3

LVDS8n

LVDS24n

BANK1

LVDS8p

LVDS24p

LVDS9n

LVDS25n

LVDS9p

LVDS25p

LVDS10n

LVDS26n

LVDS10p

LVDS26p/DPCLK1

LVDS11n

LVDS11p/CDPCLK1

LVDS12n

LVDS12p

LVDS13n

VREFB1N0

LVDS13p

VREFB1N1

LVDS14n

LVDS14p

CLK3/LVDSCLK1n

LVDS15n

CLK2/LVDSCLK1p

LVDS15p

PLL1_OUTn

IO1_0

PLL1_OUTp

IO1_1

IO1_2

IO1_3

LVDS16n

LVDS16p

LVDS17n

LVDS17p

LVDS18n

LVDS18p

LVDS19n

LVDS19p

LVDS20n

LVDS20p

LVDS21n

LVDS21p

LVDS22n

LVDS22p

LVDS23n

LVDS23p

V2

V1

U4

U3

U10

U9

U1

U2

R7

R6

T3

T2

P6

P7

T9

T10

SW17

SW16

SW15

SW14

R5

R4

R3

R2

P4

P3

HEX5_D4

HEX5_D5

HEX5_D6

HEX6_D0

HEX6_D1

HEX6_D2

T4

W6

HEX4_D3

DRAM_D8

P1

P2

SW11

SW12

AA6

AA7

HEX4_D0

HEX4_D1

HEX4_D2

HEX4_D4

HEX4_D5

HEX4_D6

HEX5_D0

HEX5_D1

HEX5_D2

HEX5_D3

DRAM_CKE

DRAM_CLK

CYCLONE II EP2C35

LCD_BLON

LCD_RS

LCD_EN

LCD_WR

LCD_D0

LCD_D1

LCD_D2

LCD_D3

LCD_D4

LCD_D5

LCD_D6

LCD_D7

OTG_OE

OTG_WE

OTG_CS

OTG_A1

K2

K1

K3

K4

J1

J2

H1

H2

J4

J3

H4

H3

G2

G1

F1

F2

LVDS32n

LVDS32p

LVDS33n

LVDS33p

LVDS34n

LVDS34p

LVDS35n

LVDS35p

LVDS36n

LVDS36p

LVDS37n

LVDS37p

LVDS38n

LVDS38p/CDPCLK0

LVDS39n

LVDS39p

OTG_A0

OTG_D15

OTG_D13

OTG_D12

OTG_D11

OTG_D10

OTG_D9

OTG_D8

OTG_D6

OTG_D5

OTG_D2

OTG_D1

OTG_D0

OTG_FSPEED

OTG_LSPEED

OTG_RESET

K7

K8

G3

G4

K5

K6

E1

E2

J7

J8

D1

D2

F4

F3

G6

G5

LVDS40n

LVDS40p

LVDS41n

LVDS41p

LVDS42n

LVDS42p

LVDS43n

LVDS43p

LVDS44n

LVDS44p

LVDS45n

LVDS45p

LVDS46n

LVDS46p

LVDS47n

LVDS47p

OTG_INT1

OTG_DACK0

OTG_INT0

OTG_DACK1

C3

C2

B3

B2

LVDS48n

LVDS48p

LVDS49n/CLKUSR

LVDS49p/CRCERR

LVDS27n

LVDS27p/DPCLK0

LVDS28n

LVDS28p

LVDS29n

LVDS29p

LVDS30n

LVDS30p

LVDS31n

LVDS31p

HEX6_D3

HEX6_D4

HEX6_D5

HEX6_D6

HEX7_D0

HEX7_D1

HEX7_D3

HEX7_D4

HEX7_D5

HEX7_D6

M2

M3

M5

M4

L3

L2

L6

L7

P9

N9

F7

H6

J6

L9

L10

OTG_D3

OTG_D7

OTG_D14

HEX7_D2

VREFB2N1

VREFB2N0

L4

J5

LCD_ON

OTG_D4

CLK1/LVDSCLK0n

CLK0/LVDSCLK0p

N1

N2

SW10

50MHZ

PLL3_OUTn

PLL3_OUTp

F6

E5

BANK2

IO2_0

IO2_1

IO2_2

IO2_3

IO2_4

OTG_DREQ0

OTG_DREQ1

CYCLONE II EP2C35

Title

ALTERA DE2

Size

B

Date:

5

Document Number

EP2C35 BANK1 AND BANK 2

Sunday, July 23, 2006

Rev

2.0

Sheet

1

of

24

SW[7..9]

TD_D[0..7]

VGA_R[0..9]

ENET_D[0..15]

VGA_G[0..9]

VGA_B[0..9]

U11C

U11D

TD_D4

TD_D3

TD_D7

TD_D6

VGA_HS

VGA_SYNC

VGA_R0

VGA_VS

VGA_R2

VGA_R1

VGA_R4

VGA_R3

VGA_R5

VGA_CLOCK

VGA_R7

VGA_R6

G9

H10

C7

D7

A7

B7

C8

D8

G10

F10

C9

D9

A8

B8

H12

H11

LVDS56n

LVDS56p

LVDS57n

LVDS57p

LVDS58n

LVDS58p

LVDS59n

LVDS59p

LVDS60n

LVDS60p

LVDS61n

LVDS61p

LVDS62n

LVDS62p/DPCLK11

LVDS63n

LVDS63p

VGA_R9

VGA_R8

VGA_G1

VGA_G0

VGA_G3

VGA_G2

VGA_G5

VGA_G4

VGA_G9

VGA_G8

VGA_B1

VGA_B0

VGA_B3

VGA_B2

VGA_B5

VGA_B4

E10

F11

A9

B9

D10

C10

A10

B10

D12

E12

J14

J13

G12

F12

J11

J10

LVDS64n

LVDS64p

LVDS65n

LVDS65p

LVDS66n

LVDS66p

LVDS67n

LVDS67p

LVDS68n

LVDS68p

LVDS69n

LVDS69p

LVDS70n

LVDS70p

LVDS71n

LVDS71p

VGA_B7

VGA_B6

VGA_B9

VGA_B8

B11

C11

B12

C12

LVDS50n/DEV_CLRN

LVDS50p

LVDS51n

LVDS51p

LVDS52n

LVDS52p

LVDS53n

LVDS53p/CDPCLK7

LVDS54n

LVDS54p

LVDS55n

LVDS55p

BANK3

LVDS72n

LVDS72p

LVDS73n

LVDS73p/DPCLK10

IO3_0

IO3_1

IO3_2

IO3_3

C5

C6

B4

A4

B5

A5

A6

B6

D5

C4

J9

K9

AUD_ADCLRCK

AUD_DACLRCK

AUD_BCLK

AUD_DACDAT

AUD_ADCDAT

AUD_XCK

I2C_SCLK

I2C_SDAT

TD_HS

TD_RESET

TD_D0

TD_VS

D6

F9

G11

H8

VGA_BLANK

TD_D5

VGA_G6

TD_D2

VREFB3N1

VREFB3N0

E8

D11

TD_D1

VGA_G7

CLK10/LVDSCLK5n

CLK11/LVDSCLK5p

C13

D13

SW7

27MHz

H16

H15

B17

A17

F15

G15

G16

F16

B18

A18

D17

C17

F17

G17

J17

H17

LVDS80n

LVDS80p

LVDS81n

LVDS81p

LVDS82n

LVDS82p

LVDS83n

LVDS83p

LVDS84n

LVDS84p

LVDS85n

LVDS85p/DPCLK8

LVDS86n

LVDS86p

LVDS87n

LVDS87p

ENET_INT

ENET_CMD

G18

F18

E18

D18

B19

A19

C19

D19

B20

A20

J16

K16

J18

K17

B21

A21

LVDS88n

LVDS88p

LVDS89n

LVDS89p

LVDS90n

LVDS90p

LVDS91n

LVDS91p

LVDS92n

LVDS92p

LVDS93n

LVDS93p

LVDS94n

LVDS94p

LVDS95n

LVDS95p

ENET_IOR

ENET_IOW

ENET_RESET

ENET_CS

A22

B22

B23

A23

LVDS96n

LVDS96p/CDPCLK6

LVDS97n

LVDS97p

ENET_D4

ENET_D5

ENET_D2

ENET_D3

ENET_D0

ENET_D1

ENET_D14

ENET_D15

ENET_D12

ENET_D13

ENET_D10

ENET_D11

ENET_D8

ENET_D9

LVDS74n

LVDS74p/DPCLK9

LVDS75n

LVDS75p

LVDS76n

LVDS76p

LVDS77n

LVDS77p

LVDS78n

LVDS78p

LVDS79n

LVDS79p

A14

B14

G14

F14

G13

F13

B15

C15

C16

B16

E15

D15

LVDS98n

LVDS98p

LVDS99n

LVDS99p

C21

D21

C23

C22

IO4_0

IO4_1

D14

D20

VREFB4N0

VREFB4N1

E20

D16

CLK8/LVDSCLK4n

CLK9/LVDSCLK4p

B13

A13

BANK4

LINK_D1

LINK_D0

LINK_D3

ENET_D7

TD_CLK27

ENET_D6

LINK_D2

SW8

SW9

CYCLONE II EP2C35

CYCLONE II EP2C35

Title

ALTERA DE2

Size

B

Date:

5

Document Number

EP2C35 BANK3 AND BANK 4

Wednesday, August 02, 2006

Rev

2.0

Sheet

1

of

24

GPIO_B[0..35]

KEY[0..3]

GPIO_B[36..71]

SW[0..2]

HEX1_D[0..6]

HEX2_D[0..6]

HEX3_D[0..6]

U11E

PS2_DAT

UART_RXD

GPIO_B0

PS2_CLK

GPIO_B3

GPIO_B2

GPIO_B5

GPIO_B4

GPIO_B7

GPIO_B6

GPIO_B9

GPIO_B8

GPIO_B11

GPIO_B10

GPIO_B13

GPIO_B12

C24

C25

D25

D26

E25

E26

F23

F24

J20

J21

F26

F25

P18

N18

G24

G23

KEY0

GPIO_B15

GPIO_B17

GPIO_B16

GPIO_B19

GPIO_B18

GPIO_B21

GPIO_B20

GPIO_B24

GPIO_B23

GPIO_B27

GPIO_B26

GPIO_B29

GPIO_B28

GPIO_B31

GPIO_B30

GPIO_B22

GPIO_B25

GPIO_B14

GPIO_B35

U11F

LVDS104n

LVDS104p

LVDS105n

LVDS105p

LVDS106n

LVDS106p

LVDS107n

LVDS107p

LVDS108n

LVDS108p

LVDS109n

LVDS109p

LVDS110n

LVDS110p

LVDS111n

LVDS111p

LVDS100n

LVDS100p

LVDS101n

LVDS101p

LVDS102n

LVDS102p

LVDS103n

LVDS103p

D23

E22

G22

G21

E24

E23

B25

B24

GPIO_B49

GPIO_B48

GPIO_B52

GPIO_B51

UART_TXD

25MHZ

G26

G25

H24

H23

J24

J23

H26

H25

K19

K18

K24

K23

L20

L21

J26

J25

LVDS120n

LVDS120p

LVDS121n

LVDS121p

LVDS122n

LVDS122p

LVDS123n

BANK5 LVDS123p

LVDS112n

LVDS112p/CDPCLK5

LVDS124n

LVDS113n

LVDS124p

LVDS113p

LVDS125n

LVDS114n

LVDS125p

LVDS114p

LVDS126n

LVDS115n

LVDS126p/DPCLK7

LVDS115p

LVDS116n

LVDS116p

LVDS117n

LVDS117p

VREFB5N0

LVDS118n

VREFB5N1

LVDS118p

LVDS119n

CLK5/LVDSCLK2n

LVDS119p

CLK4/LVDSCLK2p

L25

L24

K26

K25

M23

M22

M20

M19

M21

N20

M25

M24

N24

N23

GPIO_B34

GPIO_B33

GPIO_B37

GPIO_B36

GPIO_B39

GPIO_B38

GPIO_B41

GPIO_B40

GPIO_B43

GPIO_B42

GPIO_B45

GPIO_B44

GPIO_B46

KEY1

J22

L23

GPIO_B1

GPIO_B32

N26

N25

SW1

SW0

H19

H21

K21

K22

L19

IO5_0

IO5_1

IO5_2

IO5_3

IO5_4

F20

F21

PLL2_OUTn

PLL2_OUTp

GPIO_B55

GPIO_B59

GPIO_B58

GPIO_B61

GPIO_B60

GPIO_B63

GPIO_B62

R24

R25

T23

T22

P17

R17

T25

T24

T17

T18

U25

U26

U24

U23

T19

R19

GPIO_B65

GPIO_B64

GPIO_B67

GPIO_B66

GPIO_B69

GPIO_B68

GPIO_B70

KEY3

HEX3_D6

GPIO_B71

HEX3_D3

HEX3_D4

HEX3_D1

HEX3_D2

HEX2_D6

HEX3_D0

U21

U20

V25

V26

V23

V24

W25

W26

W24

W23

Y26

Y25

AA25

AA26

Y24

Y23

GPIO_B50

GPIO_B57

HEX3_D5

SD_CMD

R20

T20

U22

Y21

GPIO_B54

GPIO_B53

LVDS128n

LVDS128p

LVDS129n

LVDS129p

LVDS130n

LVDS130p

LVDS131n

LVDS131p

LVDS132n

LVDS132p

LVDS133n

LVDS133p

LVDS134n

LVDS134p

LVDS135n

LVDS135p

P24

P23

GPIO_B47

KEY2

LVDS144n

LVDS144p

LVDS145n

LVDS145p

LVDS146n

LVDS146p

LVDS147n

LVDS147p

LVDS148n

LVDS148p

LVDS149n

BANK6 LVDS149p

LVDS150n/INIT_DONE

LVDS150p/nCEO

AB26

AB25

AC25

AC26

AB24

AB23

AA24

AA23

W21

Y22

AD25

AD24

AE25

AE24

HEX2_D4

HEX2_D5

HEX2_D2

HEX2_D3

HEX1_D6

HEX2_D0

HEX1_D4

HEX1_D5

HEX1_D2

HEX1_D3

SD_CLK

SD_DAT

IRDA_RXD

IRDA_TXD

IO6_4

AC23

LVDS127n

LVDS127p/DPCLK6

LVDS136n

LVDS136p

LVDS137n

LVDS137p

LVDS138n

LVDS138p

LVDS139n

LVDS139p/CDPCLK4

LVDS140n

LVDS140p

LVDS141n

LVDS141p

LVDS142n

LVDS142p

LVDS143n

LVDS143p

IO6_0

IO6_1

IO6_2

IO6_3

SD_DAT3

VREFB6N0

VREFB6N1

T21

V22

GPIO_B56

HEX2_D1

CLK6/LVDSCLK3p

CLK7/LVDSCLK3n

P25

P26

SW2

EXT_CLOCK

PLL4_OUTn

PLL4_OUTp

V20

V21

HEX1_D0

HEX1_D1

CYCLONE II EP2C35

CYCLONE II EP2C35

Title

ALTERA DE2

Size

B

Date:

5

Document Number

EP2C35 BANK5 AND BANK 6

Sunday, July 23, 2006

Rev

2.0

Sheet

1

of

24

LED[0..26]

FLASH_A[0..21]

SW[3..6]

FLASH_D[0..7]

SRAM_D[0..15]

HEX0_D[0..6]

SRAM_A[0..17]

U11G

U11H

FLASH_D3

FLASH_D2

FLASH_D1

FLASH_D0

FLASH_RESET

FLASH_WE

FLASH_CE

FLASH_OE

FLASH_A0

FLASH_A1

FLASH_A2

FLASH_A3

FLASH_A4

FLASH_A5

FLASH_A6

FLASH_A7

AE20

AF20

AC19

AD19

AA18

AA17

V17

W17

AC18

AB18

AE19

AF19

AE18

AF18

Y16

AA16

LVDS160n

LVDS160p

LVDS161n

LVDS161p

LVDS162n

LVDS162p

LVDS163n

LVDS163p

LVDS164n

LVDS164p

LVDS165n

LVDS165p/DPCLK5

LVDS166n

LVDS166p

LVDS167n

LVDS167p

LVDS151n

LVDS151p

AE23

AF23

LED0

LED1

LVDS152n

LVDS152p

LVDS153n

LVDS153p

LVDS154n

LVDS154p/CDPCLK3

LVDS155n

LVDS155p

LVDS156n

LVDS156p

LVDS157n

LVDS157p

LVDS158n

LVDS158p

LVDS159n

BANK7

LVDS159p

AB21

AC22

AD22

AD23

AD21

AC21

AE22

AF22

W19

V18

U18

U17

AE21

AF21

AC20

AB20

LED2

LED3

LED4

LED5

LED6

LED7

LED19

LED20

LED21

LED22

LED23

LED24

FLASH_D7

FLASH_D6

FLASH_D5

FLASH_D4

FLASH_A8

FLASH_A9

FLASH_A10

FLASH_A11

FLASH_A12

FLASH_A13

FLASH_A15

FLASH_A16

FLASH_A17

FLASH_A18

FLASH_A19

FLASH_A20

FLASH_A21

LED8

LED9

LED10

AD17

AC17

AE17

AF17

W16

W15

AD16

AE16

AC15

AB15

AA15

Y15

Y14

AA14

Y13

AA13

LVDS168n

LVDS168p

LVDS169n

LVDS169p

LVDS170n

LVDS170p

LVDS171n

LVDS171p

LVDS172n

LVDS172p

LVDS173n

LVDS173p

LVDS174n

LVDS174p

LVDS175n

LVDS175p

IO7_0

IO7_1

AA20

AC14

LED25

LED11

VREFB7N0

VREFB7N1

Y18

AC16

LED26

FLASH_A14

LED12

LED13

AD15

AE15

CLK12/LVDSCLK6n

CLK13/LVDSCLK6p

AE14

AF14

SW3

SW4

LVDS176n

LVDS176p

CYCLONE II EP2C35

SRAM_CE

SRAM_OE

SRAM_UB

SRAM_LB

SRAM_D15

SRAM_D14

SRAM_D13

SRAM_D12

SRAM_D11

SRAM_D10

SRAM_D9

SRAM_D8

SRAM_D7

SRAM_D6

SRAM_D5

SRAM_D4

AC11

AD10

AF9

AE9

AC10

AC9

W12

W11

AF8

AE8

AF7

AE7

Y11

AA11

AB10

AA10

SRAM_D2

SRAM_D1

SRAM_D0

SRAM_A17

SRAM_A15

SRAM_A14

SRAM_A11

SRAM_A10

SRAM_A9

SRAM_A8

SRAM_A7

SRAM_A6

SRAM_A5

SRAM_A4

SRAM_A3

SRAM_A2

AF6

AE6

AD8

AC8

Y10

W10

V9

V10

AD7

AD6

AF5

AE5

AD5

AD4

AC6

AC5

LVDS192n

LVDS192p

LVDS193n

LVDS193p

LVDS194n

LVDS194p

LVDS195n

LVDS195p

LVDS196n

LVDS196p

LVDS197n

LVDS197p

LVDS198n

LVDS198p

LVDS199n

LVDS199p

SRAM_A1

SRAM_A0

AF4

AE4

LVDS200p

LVDS200n/DEV_OE

LVDS184n

LVDS184p

LVDS185n

LVDS185p

LVDS186n

LVDS186p

LVDS187n

LVDS187p

LVDS188n

LVDS188p/DPCLK2

LVDS189n

LVDS189p

LVDS190n

LVDS190p

LVDS191n

LVDS191p

LVDS177n

LVDS177p/DPCLK3

LVDS178n

LVDS178p

LVDS179n

LVDS179p

LVDS180n

LVDS180p

LVDS181n

LVDS181p

LVDS182n

LVDS182p

LVDS183n

LVDS183p

AF13

AE13

AE12

AD12

Y12

AA12

U12

V11

V13

V14

AE11

AD11

AF10

AE10

LED14

LED15

LED16

LED17

LED18

IO8_0

IO8_1

IO8_2

IO8_3

W8

AA9

AB8

AB12

SRAM_A13

SRAM_D3

SRAM_A16

HEX0_D1

VREFB8N0

VREFB8N1

AC12

AC7

HEX0_D2

SRAM_A12

CLK14/LVDSCLK7n

CLK15/LVDSCLK7p

AD13

AC13

SW5

SW6

BANK8

HEX0_D6

HEX0_D5

HEX0_D4

HEX0_D3

HEX0_D0

SRAM_WE

CYCLONE II EP2C35

Title

ALTERA DE2

Size

B

Date:

5

Document Number

EP2C35 BANK7 AND BANK 8

Sunday, July 23, 2006

Rev

2.0

Sheet

1

10

of

24

VCCIO

Y6

W7

E21

G20

E4

G7

W20

AA21

Y8

F19

F8

Y19

Y17

Y9

W22

W14

W13

W5

U19

U8

AF25

AF15

AF12

AF2

AE26

AE1

AD18

AD14

AD9

AC4

AB19

AB16

AB11

AB7

W9

V12

AF11

AF3

AB13

AB9

AB6

V16

U16

U15

U14

U13

U11

T16

T11

R16

R11

R10

P10

N17

N10

M17

M16

M11

M10

L18

L17

L16

L11

K15

K14

K13

K12

K11

K10

VCCD_PLL1

VCCD_PLL2

VCCD_PLL3

VCCD_PLL4

Y7

H20

H7

Y20

VCCA_PLL1

VCCA_PLL2

VCCA_PLL3

VCCA_PLL4

AA8

G19

G8

AA19

GNDA_PLL1

GNDA_PLL2

GNDA_PLL3

GNDA_PLL4

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

Power & GND

CYCLONE II EP2C35

BC7

BC8

BC9

0.1U

0.1U

0.1U

0.1U

VCCIO

BC10

BC11

BC12

BC13

BC14

0.1U

0.1U

0.1U

0.1U

0.1U

VCCIO

BC15

BC16

BC17

BC18

BC19

0.1U

0.1U

0.1U

0.1U

0.1U

VCCIO

VCC12

BC20

BC21

BC22

BC23

BC24

0.1U

0.1U

0.1U

0.1U

0.1U

VCCINT

T5

R26

R21

R1

P19

P8

N19

N8

M26

M1

L22

L5

K20

H22

H14

H13

H5

E19

E16

E11

E7

D24

D4

C18

C14

B26

B1

A25

A15

A12

A2

T15

T14

T13

T12

R15

R14

R13

R12

P16

P15

P14

P13

P12

P11

N16

N15

N14

N13

N12

N11

M15

M14

M13

M12

L15

L14

L13

L12

BC6

0.1U

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

GND_PLL1

GND_PLL1

GND_PLL2

GND_PLL2

GND_PLL3

GND_PLL3

GND_PLL4

GND_PLL4

BC5

VCCIO8

VCCIO8

VCCIO8

VCCIO8

VCCIO8

VCCIO8

VCCIO8

W18

V15

AF24

AF16

AD20

AB22

AB17

AB14

VCCIO7

VCCIO7

VCCIO7

VCCIO7

VCCIO7

VCCIO7

VCCIO7

VCCIO7

V19

T26

R18

P22

AD26

AA22

VCCIO

VCCIO6

VCCIO6

VCCIO6

VCCIO6

VCCIO6

VCCIO6

N22

M18

L26

J19

F22

C26

VCCIO5

VCCIO5

VCCIO5

VCCIO5

VCCIO5

VCCIO5

J15

H18

E17

E14

D22

C20

A24

A16

VCCIO4

VCCIO4

VCCIO4

VCCIO4

VCCIO4

VCCIO4

VCCIO4

VCCIO4

J12

H9

E13

E9

E6

A11

A3

N5

M9

L1

F5

C1

VCCIO

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

VCCIO3

VCCIO3

VCCIO3

VCCIO3

VCCIO3

VCCIO3

VCCIO3

VCCIO1

VCCIO1

VCCIO1

VCCIO1

VCCIO1

VCCIO1

U11I

VCCIO

VCCIO2

VCCIO2

VCCIO2

VCCIO2

VCCIO2

V8

T1

R9

P5

AD1

AB5

VCCIO

BC25

BC26

BC27

BC28

BC29

BC30

BC31

BC32

BC33

BC34

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

VCC12

U11J

ASDO

NCSO

TDI

TCK

TMS

TDO

DCLK

DATA0

NCONFIG

NCE

E3

D3

M8

M6

L8

M7

N6

N3

N7

N4

ASDO

nCSO

TDI

TCK

TMS

TDO

DCLK

DATA0

nCONFIG

nCE

Control Signal

nSTATUS

CONF_DONE

R22

R23

MSEL0

MSEL1

P20

P21

NC0

NC1

NC2

BC35

BC36

0.1U

0.1U

NSTATUS

CONF_DONE

Y2

N21

AC24

A

CYCLONE II EP2C35

Title

ALTERA DE2

Size

B

Date:

5

Document Number

EP2C35 POWER AND CONFIG

Tuesday, July 25, 2006

Rev

2.0

Sheet

1

11

of

24

N_VCC33

D

R18

N_VCC33

4.7K

ENET_D[0..15]

25MHZ

ENET_RESET

SPEED

ACT

ENET_CS

NGND

BEAD

NGND

10U

0.1U

0.1U

R19

C7

BC37

BC38

6.8K

U35

0.1U

CHSGND

N_VCC33

BGGND

RXGND

SD

GND

X1

X2

VDD

TEST

PWRST#

LED1

LED2

CS#

C8

48

47

46

45

44

43

42

41

40

39

38

37

L2

R20

4.7K

16

MNT0

15

N_VCC33

1

2

3

4

5

6

7

8

49R9 N_VCC25

L3

BEAD

RX+

RXNGND

TX+

TX-

N_VCC25

CHSGND

R23

R24

49R9

49R9

C9

CHSGND

NGND

R25

120

R26

DM9000A-8/16bit

DM9000AE

IOW#

IOR#

INT

GND

CMD

GP1/SD8

VDD

GP2/SD9

GP3/SD10

GP4/SD11

GP5/SD12

GP6/SD13

ENET_IOW

ENET_IOR

ENET_INT

ENET_CMD

ENET_D8

N_VCC33

ENET_D9

ENET_D10

ENET_D11

ENET_D12

ENET_D13

SPEED

120

ACT

ENET_D14

ENET_D15

ENET_D0

ENET_D1

ENET_D2

ENET_D3

ENET_D4

ENET_D5

ENET_D6

ENET_D7

N_VCC33

BGRES

RXVDD25

RX+

RXRXGND

TXGND

TX+

TXTXVDD25

SD7

SD6

SD5

36

35

34

33

32

31

30

29

28

27

26

25

13

14

15

16

17

18

19

20

21

22

23

24

0.1U

1

2

3

4

5

6

7

8

9

10

11

12

SD4

SD3

GND

SD2

SD1

SD0

EEDIO

EEDCK

EEDCS

WAKE/SD15

VDD

LED3/SD14

10

SMNT0

12

TD+

TDD4 YELLOW

RD+

CTT

RJ45INTLED

CTR

D2

RDNC

CHSG

D1 GREEN

MNT1

N_VCC33

D3

13

11

R22

49R9

SMNT1

J4

14

R21

N_VCC25

N_VCC33

NGND

BC39

BC40

BC41

BC42

BC43

BC44

BC45

BC46

BC47

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

Title

NGND

ALTERA DE2

CHSGND

Size

B

Date:

Document Number

DM9000AE

Tuesday, July 25, 2006

Rev

2.0

Sheet

1

12

of

24

VCC33

U14

BC48

0.1U

Y1

1

2

EN

VCC

GND

OUT

VCC33

IRDA_RXD

IRDA_TXD

50MHZ

R27

R28

120

120

VCC33

R29

47

50MHZ

EXT_CLOCK

GND

NC

VCC

AGND

SD

RXD

TXD

LEDA

SHIELD

IrDA

J5

VCC33

EXT CLOCK

1

2

3

4

5

6

7

8

9

R30

C10

C11

1K

1U

1U

Title

ALTERA DE2

Size

A

Date:

5

Document Number

CLOCK and IrDA

Tuesday, July 25, 2006

2

Rev

2.0

Sheet

13

of

1

24

UART_RXD

RXD

VCC33

RN24

LEDR

TXD

1

2

3

4

LEDG

RXD

C12 1U

1

3

4

5

2

6

C13 1U

VCC33

5

9

4

8

3

7

2

6

1

U15

13

8

11

10

330

UART_TXD

J6

8

7

6

5

BC49

C14

C15

0.1U

1U

1U

VCC5

R1OUT

R2OUT

T1OUT

T2OUT

12

9

14

7

C+ MAX232

C1C2+

VCC

C2GND

V+

V-

16

15

R1IN

R2IN

T1IN

T2IN

10

11

VCC33

RS232

VCC5

R31

R32

2K

2K

J7

TOP

R33

R34

120

120

PS2DAT

PS2CLK

BAT54S

BAT54S

VCC33

D2

D1

VCC5

1

2

3

5

6

8

3

2

BC50

9

10

11

PS2_DAT

PS2_CLK

0.1U

PS2

VCC33

Title

ALTERA DE2

Size

A

Date:

5

Document Number

PS2 AND RS232

Tuesday, July 25, 2006

2

Rev

2.0

Sheet

14

of

1

24

RN25

1

2

3

4

8

7

6

5

VCC33

U16

100K

GND

10

9

8

7

6

5

4

3

2

KEYIN0

KEYIN1

KEYIN2

KEYIN3

KEY0

KEY1

KEY2

KEY3

C16

C17

C18

C19

1U

1U

1U

1U

TACT SW

TACT SW

TACT SW

TACT SW

VCC33

GND

B8

B7

B6

B5

B4

B3

B2

B1

11

12

13

14

15

16

17

18

OE

VCC

19

20

A8

A7

A6

A5

A4

A3

A2

A1

DIR

RN26

8

7

6

5

KEY0

KEY1

KEY2

KEY3

1

2

3

4

120

GND

VCC33

74HC245

C

SW0

SW1

4

1

2

3

5

GND

VCC33

SW0

GND

GND

SLIDE SW

GND

VCC33

SW1

GND

GND

SLIDE SW

SW8

GND

VCC33

SW8

GND

GND

SLIDE SW

GND

VCC33

SW9

GND

GND

SLIDE SW

GND

VCC33

GND

GND

SLIDE SW

GND

VCC33

GND

VCC33

SW10

GND

GND

SW5

4

1

2

3

5

4

1

2

3

5

SLIDE SW

GND

VCC33

SW11

GND

GND

4

1

2

3

5

GND

VCC33

SW6

GND

GND

SLIDE SW

4

1

2

3

5

GND

VCC33

SW7

GND

GND

SLIDE SW

SW13

4

1

2

3

5

SLIDE SW

SW7

GND

VCC33

SW5

GND

GND

SLIDE SW

SW12

4

1

2

3

5

SW6

GND

VCC33

SW4

GND

GND

GND

VCC33

SW12

GND

GND

4

1

2

3

5

SLIDE SW

GND

VCC33

R35

120 SW13

GND

GND

SLIDE SW

SW17

4

1

2

3

5

GND

GND

GND

VCC33

SW3

GND

GND

SW11

4

1

2

3

5

SW16

4

1

2

3

5

SW4

4

1

2

3

5

SLIDE SW

SLIDE SW

SW15

4

1

2

3

5

GND

VCC33

SW2

GND

GND

SW10

4

1

2

3

5

SLIDE SW

SW14

SW3

4

1

2

3

5

SLIDE SW

SW9

4

1

2

3

5

SW2

4

1

2

3

5

SLIDE SW

GND

VCC33

GND

GND

4

1

2

3

5

GND

VCC33

RN27

8

7

6

5

GND

GND

SLIDE SW

KEY[0..3]

1

2

3

4

SW17

SW16

SW15

SW14

SW[0..17]

120

Title

ALTERA DE2

Size

A

Date:

5

Document Number

KEY AND SWITCH

Sunday, July 23, 2006

2

Rev

2.0

Sheet

15

of

1

24

VCC33

VCC33

VCC33

VCC33

VCC33

VCC33

VCC33

VCC33

VCC33

D3

D4

1

3

GPIO_B0

1

3

GPIO_B1

2

BAT54S

D12

GPIO_B9

GPIO_B10

2

BAT54S

D21

D22

1

3

GPIO_B18

GPIO_B19

2

BAT54S

D30

GPIO_B27

GPIO_B28

GPIO_B30

GPIO_B31

2

BAT54S

3

2

BAT54S

GPIO_B32

BAT54S

D38

3

GPIO_B34

2

BAT54S

GPIO_B35

BAT54S

GPIO_B33

D37

BAT54S

D36

GPIO_B25

2

BAT54S

D35

D29

3

GPIO_B26

BAT54S

GPIO_B24

D28

3

GPIO_B17

BAT54S

BAT54S

D34

3

BAT54S

2

BAT54S

GPIO_B29

2

BAT54S

GPIO_B23

D20

GPIO_B16

D27

3

GPIO_B8

BAT54S

BAT54S

3

2

GPIO_B15

D19

3

D26

GPIO_B22

GPIO_B7

BAT54S

BAT54S

D33

BAT54S

D32

BAT54S

2

BAT54S

D31

3

GPIO_B21

3

2

D18

GPIO_B14

D11

GPIO_B6

BAT54S

D25

3

3

2

BAT54S

D10

D17

GPIO_B13

GPIO_B20

GPIO_B5

BAT54S

D24

3

3

2

BAT54S

BAT54S

D23

GPIO_B12

D9

D16

3

BAT54S

GPIO_B4

BAT54S

GPIO_B11

2

BAT54S

3

2

D15

D8

BAT54S

D14

3

GPIO_B3

3

2

BAT54S

D7

GPIO_B2

D13

3

D6

BAT54S

D5

1

2

BAT54S

BAT54S

GPIO_B[0..35]

(GPIO 0)

RN28

GPIO_B0

GPIO_B1

GPIO_B2

GPIO_B3

1

2

3

4

RN29

8

7

6

5

IO_A0

IO_A1

IO_A2

IO_A3

GPIO_B4

GPIO_B5

GPIO_B6

GPIO_B7

1

2

3

4

47

RN31

GPIO_B12

GPIO_B13

GPIO_B14

GPIO_B15

1

2

3

4

GPIO_B24

GPIO_B25

GPIO_B26

GPIO_B27

1

2

3

4

RN30

8

7

6

5

IO_A4

IO_A5

IO_A6

IO_A7

GPIO_B8

GPIO_B9

GPIO_B10

GPIO_B11

1

2

3

4

47

RN32

8

7

6

5

IO_A12

IO_A13

IO_A14

IO_A15

GPIO_B16

GPIO_B17

GPIO_B18

GPIO_B19

1

2

3

4

8

7

6

5

IO_A24

IO_A25

IO_A26

IO_A27

GPIO_B28

GPIO_B29

GPIO_B30

GPIO_B31

1

2

3

4

47

RN34

IO_A8

IO_A9

IO_A10

IO_A11

8

7

6

5

IO_A16

IO_A17

IO_A18

IO_A19

GPIO_B20

GPIO_B21

GPIO_B22

GPIO_B23

1

2

3

4

8

7

6

5

IO_A28

IO_A29

IO_A30

IO_A31

GPIO_B32

GPIO_B33

GPIO_B34

GPIO_B35

1

2

3

4

8

7

6

5

IO_A20

IO_A21

IO_A22

IO_A23

8

7

6

5

IO_A32

IO_A33

IO_A34

IO_A35

47

RN36

47

IO_A0

IO_A2

IO_A4

IO_A6

IO_A8

VCC5

47

RN33

47

RN35

47

JP1

8

7

6

5

VCC33

IO_A10

IO_A12

IO_A14

IO_A16

IO_A18

IO_A20

IO_A22

IO_A24

IO_A26

IO_A28

IO_A30

IO_A32

IO_A34

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

IO_A1

IO_A3

IO_A5

IO_A7

IO_A9

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

IO_A11

IO_A13

IO_A15

IO_A17

IO_A19

IO_A21

IO_A23

IO_A25

IO_A27

IO_A29

IO_A31

IO_A33

IO_A35

BOX Header 2X20M

47

Title

ALTERA DE2

Size

B

Date:

5

Document Number

CONNECT A

Sunday, July 23, 2006

Rev

2.0

Sheet

1

16

of

24

VCC33

VCC33

D39

GPIO_B36

GPIO_B37

D48

GPIO_B45

GPIO_B46

2

BAT54S

3

2

D57

D58

1

3

GPIO_B54

GPIO_B55

2

BAT54S

3

2

BAT54S

D66

3

GPIO_B63

GPIO_B64

2

BAT54S

GPIO_B66

GPIO_B67

2

BAT54S

2

BAT54S

D74

GPIO_B69

BAT54S

D73

3

2

BAT54S

BAT54S

GPIO_B68

1

2

D72

GPIO_B61

2

BAT54S

D71

3

GPIO_B62

D65

GPIO_B60

BAT54S

D64

3

BAT54S

BAT54S

GPIO_B59

D70

3

BAT54S

GPIO_B53

1

2

D63

BAT54S

GPIO_B65

GPIO_B58

D69

1

2

BAT54S

GPIO_B52

2

BAT54S

D62

BAT54S

D68

GPIO_B57

2

BAT54S

D67

D56

3

2

BAT54S

D61

GPIO_B56

GPIO_B44

BAT54S

GPIO_B51

3

2

D55

3

BAT54S

GPIO_B50

GPIO_B43

D54

3

BAT54S

BAT54S

D47

GPIO_B42

D53

GPIO_B49

D60

BAT54S

VCC33

D46

GPIO_B41

BAT54S

D59

GPIO_B48

2

BAT54S

D52

3

VCC33

D45

BAT54S

GPIO_B47

GPIO_B40

D51

BAT54S

VCC33

D44

BAT54S

D50

GPIO_B39

2

BAT54S

D49

3

VCC33

D43

GPIO_B38

VCC33

D42

BAT54S

VCC33

D41

BAT54S

VCC33

D40

GPIO_B70

1

3

GPIO_B71

BAT54S

BAT54S

BAT54S

GPIO_B[36..71]

RN37

GPIO_B36

GPIO_B37

GPIO_B38

GPIO_B39

1

2

3

4

RN38

8

7

6

5

IO_B0

IO_B1

IO_B2

IO_B3

GPIO_B40

GPIO_B41

GPIO_B42

GPIO_B43

8

7

6

5

IO_B12

IO_B13

IO_B14

IO_B15

GPIO_B52

GPIO_B53

GPIO_B54

GPIO_B55

8

7

6

5

IO_B24

IO_B25

IO_B26

IO_B27

GPIO_B64

GPIO_B65

GPIO_B66

GPIO_B67

1

2

3

4

47

RN40

GPIO_B48

GPIO_B49

GPIO_B50

GPIO_B51

1

2

3

4

47

RN43

GPIO_B60

GPIO_B61

GPIO_B62

GPIO_B63

1

2

3

4

IO_B4

IO_B5

IO_B6

IO_B7

GPIO_B44

GPIO_B45

GPIO_B46

GPIO_B47

8

7

6

5

IO_B16

IO_B17

IO_B18

IO_B19

GPIO_B56

GPIO_B57

GPIO_B58

GPIO_B59

8

7

6

5

IO_B28

IO_B29

IO_B30

IO_B31

GPIO_B68

GPIO_B69

GPIO_B70

GPIO_B71

1

2

3

4

47

RN41

1

2

3

4

47

8

7

6

5

IO_B8

IO_B9

IO_B10

IO_B11

8

7

6

5

IO_B20

IO_B21

IO_B22

IO_B23

8

7

6

5

IO_B32

IO_B33

IO_B34

IO_B35

47

RN42

1

2

3

4

47

RN44

1

2

3

4

(GPIO 1)

RN39

8

7

6

5

JP2

IO_B0

IO_B2

IO_B4

IO_B6

IO_B8

VCC5

47

RN45

1

2

3

4

47

VCC33

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

IO_B10

IO_B12

IO_B14

IO_B16

IO_B18

IO_B20

IO_B22

IO_B24

IO_B26

IO_B28

IO_B30

IO_B32

IO_B34

47

IO_B1

IO_B3

IO_B5

IO_B7

IO_B9

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

IO_B11

IO_B13

IO_B15

IO_B17

IO_B19

IO_B21

IO_B23

IO_B25

IO_B27

IO_B29

IO_B31

IO_B33

IO_B35

BOX Header 2X20M

Title

ALTERA DE2

Size

B

Date:

5

Document Number

CONNECT B

Sunday, July 23, 2006

Rev

2.0

Sheet

1

17

of

24

R_VCC33

SRAM_D[0..15]

DRAM_A[0..11]

SRAM_A[0..17]

16

17

18

19

20

21

nWE

nCAS

nRAS

nCS

BA0

BA1

SRAM_CE

SRAM_OE

SRAM_WE

SRAM_LB

SRAM_UB

6

41

17

39

40

A0

A1

A2

A3

A4

D0

A5

D1

A6

D2

A7

D3

A8

D4

A9

D5

A10 SRAM 256Kx16 D6

A11

D7

A12

D8

A13

D9

A14

D10

A15

D11

A16

D12

A17

D13

A18

D14

D15

nCE

nOE

nWE

nLB

nUB

7

8

9

10

13

14

15

16

29

30

31

32

35

36

37

38

SRAM_D0

SRAM_D1

SRAM_D2

SRAM_D3

SRAM_D4

SRAM_D5

SRAM_D6

SRAM_D7

SRAM_D8

SRAM_D9

SRAM_D10

SRAM_D11

SRAM_D12

SRAM_D13

SRAM_D14

SRAM_D15

40

28

41

54

6

12

46

52

12

34

NC

1

2

3

4

5

18

19

20

21

22

23

24

25

26

27

42

43

44

28

VCC

VCC

DRAM_WE

DRAM_CAS

DRAM_RAS

DRAM_CS

DRAM_BA0

DRAM_BA1

DRAM_D0

DRAM_D1

DRAM_D2

DRAM_D3

DRAM_D4

DRAM_D5

DRAM_D6

DRAM_D7

DRAM_D8

DRAM_D9

DRAM_D10

DRAM_D11

DRAM_D12

DRAM_D13

DRAM_D14

DRAM_D15

2

4

5

7

8

10

11

13

42

44

45

47

48

50

51

53

SRAM_A0

SRAM_A1

SRAM_A2

SRAM_A3

SRAM_A4

SRAM_A5

SRAM_A6

SRAM_A7

SRAM_A8

SRAM_A9

SRAM_A10

SRAM_A11

SRAM_A12

SRAM_A13

SRAM_A14

SRAM_A15

SRAM_A16

SRAM_A17

GND

GND

A0

D0

A1

D1

A2

D2

A3

D3

A4

D4

A5

D5

A6

D6

A7

D7

A8

D8

A9

D9

A10

D10

A11 SDRAM 1Mx16x4 D11

A12

D12

CLK

D13

CKE

D14

LDQM

D15

UDQM

VSSQ

VSSQ

VSSQ

VSSQ

DRAM_CLK

DRAM_CKE

DRAM_LDQM

DRAM_UDQM

23

24

25

26

29

30

31

32

33

34

22

35

36

38

37

15

39

VSS

VSS

VSS

U18

VDDQ

VDDQ

VDDQ

VDDQ

DRAM_A0

DRAM_A1

DRAM_A2

DRAM_A3

DRAM_A4

DRAM_A5

DRAM_A6

DRAM_A7

DRAM_A8

DRAM_A9

DRAM_A10

DRAM_A11

VDD

VDD

VDD

U17

3

9

43

49

DRAM_D[0..15]

1

14

27

R_VCC33

11

33

SRAM_CE

R36

4.7K

DRAM_CS

R37

4.7K

R_VCC33

R_VCC33

BC51

BC52

BC53

BC54

BC55

BC56

BC57

BC58

BC59

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

Title

ALTERA DE2

Size

A

Date:

5

Document Number

SDRAM and SRAM

Tuesday, July 25, 2006

2

Rev

2.0

Sheet

18

of

1

24

FLASH_D[0..7]

FLASH_A[0..21]

F_VCC33

SD_DAT3

SD_CMD

SD_CLK

SD_DAT

F_VCC33

R38

R39

4.7K

4.7K

F_VCC33

9

1

2

3

4

5

6

7

8

U19

DAT2

DAT3

CMD

VSS

VCC

CLK

VSS

DAT0

DAT1

12

13

14

15

10 SW0

11 SW1

FLASH_A0

FLASH_A1

FLASH_A2

FLASH_A3

FLASH_A4

FLASH_A5

FLASH_A6

FLASH_A7

FLASH_A8

FLASH_A9

FLASH_A10

FLASH_A11

FLASH_A12

FLASH_A13

FLASH_A14

FLASH_A15

FLASH_A16

FLASH_A17

FLASH_A18

FLASH_A19

FLASH_A20

FLASH_A21

45

25

24

23

22

21

20

19

18

8

7

6

5

4

3

2

1

48

17

16

9

10

13

FLASH_WE

FLASH_RESET

11

12

14

15

26

28

47

SD Card Socket

F_VCC33

U20

R40

4.7K

FLASH_CE

FLASH_OE

F_VCC33

DQ15/A-1

A0

VCC

A1

A2

A3

DQ0

A4

DQ1

A5

DQ2

A6

DQ3

A7

DQ4

A8

DQ5

A9

DQ6

A10

DQ7

A11

DQ8

A12

DQ9

A13

DQ10

A14

DQ11

A15

DQ12

A16

DQ13

A17

DQ14

A18

A19

A20

A21

FLASH 512Kx8

WE#

RESET#

WP#ACC

RY/BY#

CE#

OE#

VSS

BYTE#

VSS

37

29

31

33

35

38

40

42

44

30

32

34

36

39

41

43

FLASH_D0

FLASH_D1

FLASH_D2

FLASH_D3

FLASH_D4

FLASH_D5

FLASH_D6

FLASH_D7

27

46

F_VCC33

BC60

BC61

0.1U

0.1U

Title

ALTERA DE2

Size

A

Date:

5

Document Number

FLASH and SD Card

Tuesday, July 25, 2006

2

Rev

2.0

Sheet

19

of

1

24

SW18

1

5V0

VCC5

5

6

SS14

U21

4

2

J8

3

D76

SS14

D77

SS14

D78

SS14

POWER SW

TC4

BC62

47U/16V

0.1U

INPUT

OUTPUT

1

2

3

VCC5

78D05AL-5V/1A

GND

D75

DC_9V

BC63

TC5

0.1U

220U/6.3V

TC3

47U/16V

VCC5

R41

U22

NC

Feedback

0.1U

ON/OFF

GND

BC65

VIN

GND

4.7K

CBoost

VOUT

VCC5

R42

VGA_VCC5

0

BC64

C20

C21

0.1U

10U

10U

VCC33

6

C22

0.01U

L4

47UH

TC6

TC7

BC66

220U/6.3V

220U/6.3V

0.1U

R44

R43

3V3

VCC33

LM2676-3.3V/3A

U_VCC5

0

D79

D80

SS14

SS14

120

VCC33

R45

F_VCC33

VCC33

POWER

R46

R_VCC33

VCC33

R47

V_VCC33

0

A_VCC33

VCC33

L5

C23

C24

C25

C26

C27

10U

10U

10U

10U

10U

BEAD

C28

10U

LEDB

AGND

1V8

VCC18

VCC18

VCC33

AME1117ECCTZ-1.8V/1A

INPUT

VOUT 4

VCC33

ADJ/GND

U23

3

BC67

TC8

N_VCC33

0

100U/6.3V

VCC18

ADJ/GND

AME1117ACCTZ-ADJ/1A

INPUT

VOUT 4

BC69

R52

TC10

BC70

R51

220U/6.3V

0.1U

330

0.1U

VCC33

R50

VCCIO

0

C29

C30

TC9

10U

10U

220U/6.3V

V_VCC18

0

VCC12

R53

VCCINT

C31

TC11

10U

220U/6.3V

AME1117ACCTZ-ADJ/1A

VOUT 4

INPUT

ADJ/GND

U27

3

U_VCC33

VCC12

U24

3

R49

0.1U

1V2

VCC12

B

VCC33

BC68

0.1U

R48

GND1

GND

GND2

GND

GND3

GND

GND4

GND

MH1

GND

MH2

GND

MH3

GND

MH4

GND

MH5

GND

MH6

GND

FID1

FID2

FID3

FID4

FIDUCIAL FIDUCIAL FIDUCIAL FIDUCIAL

FID5

FID6

FID7

FID8

Title

FIDUCIAL FIDUCIAL FIDUCIAL FIDUCIAL

ALTERA DE2

Size

Date:

Document Number

POWER

Friday, August 04, 2006

Rev

2.0

Sheet

1

20

of

24

R54

330

BC74

0.1U

BC75

0.1U

0.1U

0.1U

U25

D81

BAT54S

3V3OUT

1.5K

RSTOUT#

R56

22

USBDP

R57

22

USBDM

D82

BAT54S

2

USB5V

USB5V

R58

27

XTIN

28

120

ULED

6MHZ

XTOUT

RESET#

2

1

32

31

EEDATA

EESK

EECS

TEST

100K nRESET

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

LEDB

D0

D1

D2

D3

D4

D5

D6

D7

ISPTDI

UD0

UD1

UD2

UD3

UD4

UD5

GND

UD6

UD7

25

24

23

22

21

20

19

18

RD#

WR

TXE#

RXF#

16

15

14

12

SI/WU

PWREN#

11

10

ISPTMS

USB5V

U26

6MHZ R59

22

C32

FP3V

IO-A1

IO-A0

VCCIO

TDI

IO-B8

IO-B7

IO-B6

IO-B5

IO-B4

IO-B3

GNDIO

IO-B2

IO-B1

IO-B0

TMS

IO-C8

IO-C7

VCCIO

IO-C6

IO-C5

IO-C4

IO-C3

IO-C2

IO-C1

IO-C0

FP3V

D

IO-H0

GNDIO

TDO

IO-G7

IO-G6

IO-G5

IO-G4

IO-G3

IO-G2

VCCIO

GNDIO

IO-G1

IO-G0

TCK

IO-F7

IO-F6

GNDIO

IO-F5

IO-F4

IO-F3

IO-F2

IO-F1

GNDIO

IO-F0

VCCIO

EPM3128AT

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

ISPTDO

FPTDI

FPNCSO

FPTCK

FPNST

RN51

1

2

3

4

8

7

6

5

LINK_D0

LINK_D1

LINK_D2

LINK_D3

120

TDO

TCK

ISPTCK

TMS

TDI

TRGDCLK

TRGASDO

TRGNCS

TRGNST

C

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

29

9

17

47P

URD

UWR

TXE

RXF

12MHZ

PWRON

USBON

R60

FP3V

FT245BL

AGND

GND

GND

USB B-TYPE

FP3V

1

4

6

R55

GND VBUS

USB_DP

USB_DM

3

2

0.1U

BC76

J9

D-

0.1U

LOAD

BC73

D+

BC72

13

30

3

26

BEAD

VCCIO

AVCC

VCC

VCC

BEAD

L7

BC71

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

USB5V

USB5V

L6

24MHZ

IO-A2

IO-A3

IO-A4

IO-A5

IO-A6

GNDIO

IO-A7

IO-A8

IO-A9

VCCINT

INPUT/OE2/GCLK2

INPUT/GCLRn

INPUT/OE1

INPUT/GCLK1

GNDINT

IO-H8

IO-H7

IO-H6

VCCIO

IO-H5

IO-H4

IO-H3

GNDIO

IO-H2

IO-H1

GNDIO

IO-D8

IO-D7

IO-D6

IO-D5

IO-D4

IO-D3