Академический Документы

Профессиональный Документы

Культура Документы

Overlap 2

Загружено:

Anonymous fFl3xgWАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Overlap 2

Загружено:

Anonymous fFl3xgWАвторское право:

Доступные форматы

ELEC4240/9240

Power Electronics

Lectures 10-11 Effect of source inductance on phase

controlled AC-DC converters

10.1 Single-phase converters

10.1.1 Overlap in single-phase, CT fully controlled converter

T1

Ls

iL

i1

ip

vi

vo

L

V m ax sin t

vs

T2

Ls

i2

Figure 10.1 Single-phase C-T converter with source inductance

The presence of source inductance means that commutation of load current from

one thyristor to the next, as they are triggered with a firing angle , can not be

instantaneous. This source inductance, Ls, is invariably because of the inductance

of the supply lines and the leakage inductance of the input transformer. For this

circuit, the overlap of conduction for the duration makes the output voltage zero

(which is the mean of the overlapping input voltages) during this period .

Lectures 10&11 Overlap in AC-DC Converters

10&11-1

F. Rahman

ELEC4240/9240

Power Electronics

T1

Ls

iL

i1

ip

vi

vo

L

V m a x s in t

vs

T2

Ls

i2

Figure 10.2 Waveforms in the converter of figure 10.1, commutation overlap and

commutation notches, for = 45.

Lectures 10&11 Overlap in AC-DC Converters

10&11-2

F. Rahman

ELEC4240/9240

Power Electronics

T1

Ls

iL

i1

ip

vi

vo

L

V max sin t

vs

T2

Ls

i2

Figure 10.3 Waveforms in the converter of figure 10.1, commutation overlap and

commutation notches, for = 130.

Lectures 10&11 Overlap in AC-DC Converters

10&11-3

F. Rahman

ELEC4240/9240

Power Electronics

The part of the input voltage waveform which is missing from the output voltage

is given by

Vmax sin t = Ls

di

dt

10.1

Vmax sin ( t ) d ( t ) = Ls

Id

10.2

di

where Vmax is the peak of the input ac voltage and Id is the dc level of the output

(load) current.

Note that in each half cycle of the above waveform, the input current through the

incoming thyristor rises from zero to Id in time /, starting from the instant of

firing. Thus, integrating equation 10.2,

Vmax cos ( + ) cos = Ls I d

cos ( + ) = cos

Ls

Vmax

Id

10.3

The commutation or overlap angle can be found from expression 10.3. It

increases with load current Id at any firing angle. The output dc voltage is then

given by

Vd =

Vmax sin ( t ) d ( t )

Vmax sin ( t )d ( t )

10.4

=

2Vmax

cos

Ls

I

d

= 30

Vd

= 30

Id

= 120

(a)

(b)

Id

Figure 10. 4 Variation of Vd and commutation angle with Id and firing angle .

Lectures 10&11 Overlap in AC-DC Converters

10&11-4

F. Rahman

ELEC4240/9240

Power Electronics

10.1.2 Overlap in single-phase, fully controlled bridge converter

Without overlap, two thyristors conduct at all times, if turned on. With overlap, all

four thyristors conduct during overlap (or commutation of current from the out

going pair to the incoming pair of thyristors).

vo

ip

Ls

V maxsin t

T1

T3

Vd

vsi

T2

Id

Load

T4

(a)

vo

iL

vp

vp

ip

ip

v si

v s -v si

(b)

Figure 10.5 (a) Single-phase, F-C, bridge converter with source inductance and

(b) its waveforms, for = 45.

Lectures 10&11 Overlap in AC-DC Converters

10&11-5

F. Rahman

ELEC4240/9240

Power Electronics

vs

vs

-vs

vo

iL

vp

ip

vp

ip

vsi

vs-vsi

=145o

Figure 10.5(c) Waveforms in the converter of figure 10.5(a) for = 145

The part of the input voltage waveform which is missing from the output during

overlap is given by

Vmax sin t = Ls

di

dt

10.5

As before

Vmax sin ( t ) d ( t ) = Ls

cos ( + ) = cos

Id

Id

di = 2 Ls I d

2 Ls

Id

Vmax

Lectures 10&11 Overlap in AC-DC Converters

10.6

10&11-6

F. Rahman

ELEC4240/9240

Power Electronics

Note that during overlap, the input current i, which flows through Ls, changes by

2Id. The overlap angle can be found from the above expression. The angle

increases when larger load current is commutated.

The dc output voltage of the converter with overlap is given by

Vd =

2Vmax

Vmax sin ( t )d ( t )

cos

2 Ls

Vmax sin (t )d ( t )

Id

= 30

10.7

Vd

= 30

= 125

Id

Id

Figure 10.6(a) Variation of Vd and commutation angle with load current and

firing angle for the converter of figure 10.5.

Lectures 10&11 Overlap in AC-DC Converters

10&11-7

F. Rahman

ELEC4240/9240

Power Electronics

10.1.3 Overlap in single-phase, half-controlled converter

vo

ip

Ls

T1

T3

iL

Vd

Vmaxsint

Df

D2

LOAD

D4

Figure 10.7

The commutation of the load current through the thyristors and the diodes occur in

two stages. At first, the load current commutates to the freewheeling diode at the

zero crossings of the input voltage. When the incoming thyristor is triggered, the

freewheeling load current commutates to this thyristor. The part of the input

voltage waveform missing from the output is thus dropped across the source

inductance due to the load current rising to Id during the commutation overlap

angle when a thyristor is triggered. Consequently, the overlap angle and the dc

output voltage Vd for this converter with source inductance Ls are given by,

Vmax sin td( t ) = Ls

cos ( + ) = cos

Ls

Vmax

Id

di

Id

10.8

The dc output voltage is given by

1

Vd =

Vd =

Vmax

Vmax sin td( t )

[1 + cos ]

Vmax sin td( t )

Ls

Id

Lectures 10&11 Overlap in AC-DC Converters

10&11-8

10.9

F. Rahman

ELEC4240/9240

Power Electronics

500

vs

-500

vo

iL

iDf

ip

vp

vsi

vs-vsi

For = 45

Figure 10.8. Waveforms in the H-C converter with source inductance; for = 45.

Lectures 10&11 Overlap in AC-DC Converters

10&11-9

F. Rahman

ELEC4240/9240

Power Electronics

vs

vo

iL

iDf

vp

ip

vsi

vs-vsi

0

For = 145

Figure 10.9. Waveforms in the H-C converter with source inductance; for =

145

Lectures 10&11 Overlap in AC-DC Converters

10&11-10

F. Rahman

ELEC4240/9240

Power Electronics

10.2 Three-phase converters

10.2.1 Overlap in a three-phase, CT, fully-controlled converter,

Ls

ic

Ls

ia

T3

vcn

n

van

iL

vabi

vab

vbn

T1

Ls

ib

T2

vo

L

Figure 10.10

In this circuit, the converter output voltage during overlap is half of the incoming

and outgoing voltages. For instance, when T1 is triggered with angle , after the

crossover of van and vcn, the output voltage vo is given by

vo =

van + vcn

2

10.10

The voltage pulse missing from the output voltage waveform is bounded by va and

vo. This is given by

voL = van

van vcn van vcn vacl l

=

=

2

2

2

10.11

3 Vmax sin t

where Vmax is the peak of the line-neutral

2

By expressing vol =

voltage.

1

3 Vmax

2

sin td ( t ) = Ls

Hence cos ( + ) = cos

2 L s

3 V max

Id

di

2 L s

Id

V max l l

I d = cos

10.12

from which can be found. The dc output voltage is given by

Vd =

2 / 3

5

+

6

Vmax sin td ( t )

Lectures 10&11 Overlap in AC-DC Converters

3 Vmax

2

10&11-11

sin td ( t )

F. Rahman

ELEC4240/9240

Power Electronics

3 3Vmax

3 Ls

cos

Id

2

2

10.13

Figure 10.11 Waveforms in the circuit of figure 10.10 for = 45

Lectures 10&11 Overlap in AC-DC Converters

10&11-12

F. Rahman

ELEC4240/9240

Power Electronics

Figure 10.12 Waveforms in the circuit of figure 10.10 for = 130

Lectures 10&11 Overlap in AC-DC Converters

10&11-13

F. Rahman

ELEC4240/9240

Power Electronics

10.2.2 Overlap in 3-, fully-controlled bridge converter

vo

+VD/2

ia

van

T3

T1

Ls

ib

vbn

vcn

Ls

T4

T6

Load

Vd

ic

iL

T5

L

T2

VD/2

Figure 10.13

In this converter, overlap due to source inductance occur every 60. When a

thyristor connected with the positive voltage is triggered, the positive dc bus

voltage becomes the average of the incoming and the outgoing phase voltages.

The same happens when one of the thyristors connected with the negative dc bus

is triggered.

During the commutation angle , current in the outgoing line falls gradually to

zero, while the current in the incoming line rises to Id. The voltage pulse missing

from the output voltage waveform is the difference between the incoming line

voltage minus the average of the incoming and the outgoing line voltages. For

instance, when thyristor T1 is triggered with angle , this voltage is given by,

voL = van

van + vcn van vcn vacl l

=

=

2

2

2

from to + on the vac

waveform.

Using a similar analysis as in the previous section, it can be shown that for this

converter,

cos ( + ) = cos

and

Vd =

3Vmax l l

cos

2 Ls

Id

Vmax l l

3 Ls

Id

Lectures 10&11 Overlap in AC-DC Converters

10.14

10.15

10&11-14

F. Rahman

ELEC4240/9240

Power Electronics

Figure 10.14 Waveforms in the converter of figure 10.13; = 45

Lectures 10&11 Overlap in AC-DC Converters

10&11-15

F. Rahman

ELEC4240/9240

Power Electronics

Figure 10.15 Waveforms in the converter of figure 10.13; = 130

Lectures 10&11 Overlap in AC-DC Converters

10&11-16

F. Rahman

ELEC4240/9240

Power Electronics

10.2.3 Overlap in 3-, half-controlled bridge converter

vo

+VD/2

ia

van

Ls

T5

ib

vbn

n

T3

T1

Df

ic

vcn

Ls

T4

T6

iL

iDf

R

Load

Vd

L

T2

VD/2

Figure 10.16

It can be shown that

Vd =

3Vmax l l

3 Ls

Id

[1 + cos ]

2

2

10.16

The above equation assumes that load current transfers to the free-wheeling diode

completely before the next thyristor is triggered, and that the load current transfers

from the free-wheeling diode to the incoming thyristor when it is triggered.

Lectures 10&11 Overlap in AC-DC Converters

10&11-17

F. Rahman

ELEC4240/9240

Power Electronics

10.3 Converter voltage regulation due to source inductance

The commutation overlap affects the performance of all converter circuits,

including the rectifiers which rely for their operation on natural commutation. The

overlap phenomenon affects the operation of the converter in many ways, such as

introducing a voltage

regulation characteristic. The voltage regulation

characteristic of the converter is in general given by

Vd =Vdcmax cos XLIL

and

for fully controlled converters

Vd = Vdc max ( 1 + cos ) X L I L for half controlled converters.

10.17

10.18

Here Vdcmax is the maximum dc output voltage for the converter circuit and XL is

a parameter determined by the input source inductance Ls and the converter

circuit.

V dm ax

= 0

= 30

Vd

= 60

= 75

= 90

= 110

= 130

= 160

V dm ax

Id

Figure 10.17 Voltage regulation characteristic of the fully-controlled converter

Lectures 10&11 Overlap in AC-DC Converters

10&11-18

F. Rahman

ELEC4240/9240

Power Electronics

10.3.1 Other effects

A. Output voltage ripple

The output voltage waveform of the converter is modified by the loss of voltage

pulses due to overlap. Analysis of the output voltage waveforms shows that the

output ripple frequencies remain the same as for the converter without overlap.

Only the output ripple voltage amplitudes are affected. The overlap actually

reduces the amplitudes of the ripples. For a p-pulse converter the output ripple

voltages, assuming continuous conduction, are given by

n

Vd max cos n sina sinn (t + ) cos cos n (t + )

p

vn ( t ) =

2

+ n sin ( + ) sinnt cos ( + ) cos nt

n 1

10.19

where = firing angle

= commutation angle

n = order of the output voltage ripple

B Input current harmonics

The input current waveforms of the converter have gentler rise and fall of current,

rather than the abrupt changes in the converter without overlap. It is obvious that

the harmonic amplitudes of the input current are reduced as a result of overlap.

Assuming linear transitions, of duration m, the input current harmonics of a sixpulse converter is given by

n

2 sin

3

bn =

n

n

sin

2

n

2

10.20

C. Commutation notches

During commutation overlap, simultaneous conduction of two thyristors makes

the line to line voltage of the two input lines under commutation zero. Other line

to line voltages are found by obtaining the difference of their potentials taking into

account the commutation. If the converter input voltage terminals are shared with

other loads, (these voltages are invariably used as signals which control the

triggering of the thyristors), then adequate filter circuits must be used to reduce

the commutation notches to acceptable levels. If these notches are not adequately

filtered out, firing angles vary from thyristor to thyristor, leading to uneven output

voltage ripples and thyristor currents.

Lectures 10&11 Overlap in AC-DC Converters

10&11-19

F. Rahman

ELEC4240/9240

Power Electronics

10.4 Converter characteristics with discontinuous load current

In analyzing ac-dc converter circuits we have so far assumed that the load current

was continuous, i.e., positive at all times. This allowed the output voltage to be

described in terms of the firing angle and the input ac voltage, Vmax. When load

current becomes discontinuous, the output voltage becomes either zero or equal to

the voltage of the active dc source in the load. In general, it results in an increased

output dc voltage (because of the removal of part of the negative voltage of the ac

source in the load).

The dc output voltage of a fully-controlled converter with discontinuous

conduction and input source inductance are thus of the form as in the figure

below.

Consider the figure below in which a single-phase bridge supplies a load with a

back emf of Eb.

vo

ip

T1

T3

Id

is

R

Vmaxsint

Vd

L

T2

T4

Eb

Figure 10.18 Single-phase bridge rectifier with discontinuous current.

Lectures 10&11 Overlap in AC-DC Converters

10&11-20

F. Rahman

ELEC4240/9240

Power Electronics

For this circuit,

di

+ Ri = Vmax sin t Eb

dt

10.21

The solution for i is

V

E

R/L t

i = Ae ( ) + max sin( t ) b

Z

R

10.22

2

2

where Z = R + ( L )

and

10.23

= tan 1

10.24

The instantaneous load current i is obtained by noting that i = 0 at the effective

firing angle which is either the actual firing angle (when Eb < Vmaxsin) or the

angle sin 1(Eb/Vmax)

Thus

V

i = max

R

R

Eb

sin( t )

Vmax

Z

Eb

( t )

R

sin( ) e L

+

Z

Vmax

10.25

Current i falls to zero at angle which is obtained by equating the above equation

to zero. Thus

Eb

Vmax

eR / L

= e R / L

E

cos sin( ) b

Vmax

cos sin( )

10.26

The extinction angle is found by solving the above transcendental equation. Vd

can then be calculated.

By solving for for a firing angle , the Vd - IL characteristic of the converter for

different load parameter values (R, L and Eb) can be obtained. The boundary

between continuous and discontinuous conduction is a semicircle. The Vd - IL

Lectures 10&11 Overlap in AC-DC Converters

10&11-21

F. Rahman

ELEC4240/9240

Power Electronics

characteristics of a half controlled and a fully controlled converter are shown in

figures below. These also include the effect of commutation overlap.

Vd

V dmax

= 0

= 30

= 60

= 75

= 90

= 110

= 130

= 160

V dmax

Id

Figure 10.19 Converter Vd vs and regulation characteristic with source

inductance and discontinuous conduction.

Lectures 10&11 Overlap in AC-DC Converters

10&11-22

F. Rahman

Вам также может понравиться

- The Spin Force - A Collection of Articles & Experiments 2nd EditionДокумент187 страницThe Spin Force - A Collection of Articles & Experiments 2nd EditionJorge Casalini100% (3)

- George Salvan Architectural Utilities 2 Electrical and Mechanical Equipment PDFДокумент434 страницыGeorge Salvan Architectural Utilities 2 Electrical and Mechanical Equipment PDFclainОценок пока нет

- Power Electronics BookДокумент2 страницыPower Electronics Bookvenkatesh banavath33% (3)

- Ybus Formation For Load Flow StudiesДокумент40 страницYbus Formation For Load Flow Studiesgaurav100% (3)

- HBT-6200 Field TelephoneДокумент2 страницыHBT-6200 Field TelephonePanglima EtwinОценок пока нет

- Internship Report NewДокумент12 страницInternship Report NewSaad KhalidОценок пока нет

- Speeed ControlДокумент3 страницыSpeeed ControlChristine GomezОценок пока нет

- Undervoltage Relay MVTU11Документ10 страницUndervoltage Relay MVTU11Johan HendrawanОценок пока нет

- Science Course Outline: Grade 2: Be Friend With NatureДокумент30 страницScience Course Outline: Grade 2: Be Friend With NaturePuput Maharani100% (1)

- Breakdown in Insulations 2011 Update - QuizДокумент23 страницыBreakdown in Insulations 2011 Update - QuizKung ChinHanОценок пока нет

- HW4 SolutionsДокумент10 страницHW4 SolutionsBrooklyn Luqii100% (1)

- Questions & Answers On Useful Theorems in Circuit AnalysisДокумент53 страницыQuestions & Answers On Useful Theorems in Circuit Analysiskibrom atsbha100% (1)

- VTU Guide Measures Resistance Using Wheatstone BridgeДокумент18 страницVTU Guide Measures Resistance Using Wheatstone Bridgevnyshreyas100% (2)

- What is a transformerДокумент37 страницWhat is a transformerKritika MehtaОценок пока нет

- Datasheet: SF-CPV-205 High Efficiency Concentrator PV PanelДокумент2 страницыDatasheet: SF-CPV-205 High Efficiency Concentrator PV PanelsaaskinsОценок пока нет

- Microcontroller Lab ManualДокумент38 страницMicrocontroller Lab Manualharshitha100% (1)

- MATLAB Plots for Transfer Function AnalysisДокумент6 страницMATLAB Plots for Transfer Function AnalysisPuduru BharathiОценок пока нет

- Electronic Circuits & Logic Design Lab ManualДокумент83 страницыElectronic Circuits & Logic Design Lab ManualsunandaalurОценок пока нет

- Questions & Answers On Techniques of Circuit AnalysisДокумент47 страницQuestions & Answers On Techniques of Circuit Analysiskibrom atsbha100% (2)

- A Report On The "3-Phase Line Fault Detector" Ee344 Minor Project - IДокумент34 страницыA Report On The "3-Phase Line Fault Detector" Ee344 Minor Project - IDhruv PatelОценок пока нет

- Ps2113 Distributed Generation and Microgrid 2013 14Документ2 страницыPs2113 Distributed Generation and Microgrid 2013 14Eric Hernandez0% (1)

- Experiment 3 Economic Load DispatchДокумент12 страницExperiment 3 Economic Load DispatchMahesh KambleОценок пока нет

- Experiment# 10: Measure The Power and Power Factor by Three Ammeter MethodДокумент10 страницExperiment# 10: Measure The Power and Power Factor by Three Ammeter MethodFarwa MunirОценок пока нет

- Root location determines transient responseДокумент32 страницыRoot location determines transient responseWidya AstutiОценок пока нет

- Lecture 1 - Mesh and Nodal AnalysisДокумент50 страницLecture 1 - Mesh and Nodal AnalysisCindy KoechОценок пока нет

- CIT Raipur Class Test-I 2017 BE 4th Sem Mining Basic Electrical EngineeringДокумент1 страницаCIT Raipur Class Test-I 2017 BE 4th Sem Mining Basic Electrical EngineeringsunilsinghmОценок пока нет

- Ee1451 LPДокумент7 страницEe1451 LPGokulakrishnanОценок пока нет

- Primitive Network and Graph Theory PDFДокумент12 страницPrimitive Network and Graph Theory PDFDhavalVoraОценок пока нет

- Power System Stability Worked ExamplesДокумент17 страницPower System Stability Worked ExamplesJairo Fernandez100% (1)

- Question Bank Ac MachinesДокумент4 страницыQuestion Bank Ac Machinesashwin paulОценок пока нет

- Design of Electrical MachinesДокумент2 страницыDesign of Electrical MachinesAlluri Appa Rao64% (11)

- Electri Circuits Lab Manual 1Документ11 страницElectri Circuits Lab Manual 1Sri RoОценок пока нет

- Unit 3 - DC - MotorДокумент39 страницUnit 3 - DC - MotordhoniОценок пока нет

- Final Et NotesДокумент123 страницыFinal Et NotesyounusmohamadОценок пока нет

- Circuit Fundamentals and Basic Electronics: Z R J Z J ZДокумент4 страницыCircuit Fundamentals and Basic Electronics: Z R J Z J ZTarun JoshiОценок пока нет

- 1st Year - Basic Electrical EngineeringДокумент182 страницы1st Year - Basic Electrical EngineeringMurughesh MurughesanОценок пока нет

- Interconnection of Two-Port NetworkДокумент15 страницInterconnection of Two-Port Networkthanmay Vangaveeti100% (1)

- M.tech ThesisДокумент59 страницM.tech ThesisRama Krishna100% (1)

- Concordia University Department of Electrical and Computer Engineering ELEC 6411 - Power Electronics I Course Outline Fall 2015 Course InstructorДокумент30 страницConcordia University Department of Electrical and Computer Engineering ELEC 6411 - Power Electronics I Course Outline Fall 2015 Course InstructorAndrewJohnsonJenssonОценок пока нет

- I DT DT DT DT: Class Notes On Electrical Measurements & InstrumentationДокумент71 страницаI DT DT DT DT: Class Notes On Electrical Measurements & InstrumentationTia Nur AmaliahОценок пока нет

- Transformer Design Module 2 NewДокумент17 страницTransformer Design Module 2 NewRajath SuryaОценок пока нет

- Excitation Phenomena in Transformers Excitation Phenomena With Out HysteresisДокумент2 страницыExcitation Phenomena in Transformers Excitation Phenomena With Out Hysteresism_mustaqeem100% (1)

- Unit 1 DC Circuit Analysis PDF 1 8 MegДокумент31 страницаUnit 1 DC Circuit Analysis PDF 1 8 MegJoshua Duffy67% (3)

- Glover 10 ExДокумент13 страницGlover 10 ExAseel Bait MaditОценок пока нет

- Verification of Network Theorems Using MATLABДокумент32 страницыVerification of Network Theorems Using MATLABViresh100% (1)

- Controlled Rectifiers Chapter SummaryДокумент34 страницыControlled Rectifiers Chapter SummaryBilal HussainОценок пока нет

- Circuit Thoery Lab ManualДокумент57 страницCircuit Thoery Lab ManualsrisairampolyОценок пока нет

- Electrical Network Graph Theory TopologyДокумент76 страницElectrical Network Graph Theory TopologyJoyprakash LairenlakpamОценок пока нет

- Switching TransientsДокумент16 страницSwitching TransientsvenkatОценок пока нет

- Soal-Jawab TrafoДокумент5 страницSoal-Jawab TrafoNizar SyamsudinОценок пока нет

- EEE NT VivaДокумент12 страницEEE NT VivaAyyappa Javangula100% (2)

- TransformerДокумент20 страницTransformerKarthikeyanKarunОценок пока нет

- EE8261 Electric Circuits Lab Manual EEE 1Документ87 страницEE8261 Electric Circuits Lab Manual EEE 1Bala Anderson0% (1)

- Quiz I EEE 111 QuestionДокумент1 страницаQuiz I EEE 111 QuestionFaiza AkterОценок пока нет

- FET BiasingДокумент3 страницыFET BiasingAnj HernandezОценок пока нет

- 3320100XZ8L - Control System Engineering - Solution ManualДокумент232 страницы3320100XZ8L - Control System Engineering - Solution ManualSanthosh Kumar H OОценок пока нет

- A Balanced Star Connected Load Takes 90 A From A Balanced 3-Phase, 4-Wire Supply. If The Fuses in The Y and B Phases Are Removed, Find The Symmetrical Components of The Line CurrentsДокумент1 страницаA Balanced Star Connected Load Takes 90 A From A Balanced 3-Phase, 4-Wire Supply. If The Fuses in The Y and B Phases Are Removed, Find The Symmetrical Components of The Line CurrentsممشطОценок пока нет

- Wave Shaping CircuitsДокумент56 страницWave Shaping CircuitsWaltas KariukiОценок пока нет

- ET Lab ManualДокумент52 страницыET Lab Manualcholleti sriram100% (1)

- Data Sheets For Ieee 14 Bus System 19 - Appendix PDFДокумент19 страницData Sheets For Ieee 14 Bus System 19 - Appendix PDFaldiОценок пока нет

- Improved Power Quality AC-DC Converters With High Frequency Transformer IsolationДокумент69 страницImproved Power Quality AC-DC Converters With High Frequency Transformer IsolationZlatian RaduОценок пока нет

- Class Test - 2016: Power ElectronicsДокумент9 страницClass Test - 2016: Power ElectronicsarunОценок пока нет

- Circuit Theory: Diode Characteristics and AnalysisДокумент4 страницыCircuit Theory: Diode Characteristics and AnalysisSamman ShresthaОценок пока нет

- T494D476K016ATДокумент24 страницыT494D476K016ATfeltofsnakeОценок пока нет

- Substation 33/132 kV overviewДокумент1 страницаSubstation 33/132 kV overviewaldeto71Оценок пока нет

- 2021 10 ELEC4614 T1 2020 Course OutlineДокумент12 страниц2021 10 ELEC4614 T1 2020 Course OutlineRafael SilvaОценок пока нет

- Bus 2019 HELLA en Lampi AutocarДокумент112 страницBus 2019 HELLA en Lampi AutocarDumitru CorneliuОценок пока нет

- iSTAR Ultra LT QSG 8200 1335 01 D0 enДокумент27 страницiSTAR Ultra LT QSG 8200 1335 01 D0 enJan Andre RøeОценок пока нет

- LP 30 Self Monitoring Level ProbeДокумент2 страницыLP 30 Self Monitoring Level ProbeCardoso MalacaoОценок пока нет

- Engineering Electromagnetics Chapter 5Документ30 страницEngineering Electromagnetics Chapter 5BharatОценок пока нет

- XLA RMДокумент12 страницXLA RMNahla EsamОценок пока нет

- Smart TV Mainboard ZLS47HIS-V1 With Cannot Startup Problem SolvedДокумент6 страницSmart TV Mainboard ZLS47HIS-V1 With Cannot Startup Problem SolveduzenОценок пока нет

- Thermoelectric Cooler2Документ33 страницыThermoelectric Cooler2Ahmad ShujaОценок пока нет

- Getting Started With ATV312: Verify The Delivery of The DriveДокумент4 страницыGetting Started With ATV312: Verify The Delivery of The Driveteguh perkasaОценок пока нет

- Assignment 1 MДокумент4 страницыAssignment 1 MdharmОценок пока нет

- Lab 2 - Transistor BiasДокумент12 страницLab 2 - Transistor Biascrackintheshat100% (1)

- Kilowatt Labs Sirius-Technical Data Sheet-1000-48-B-1C-TM-A-GДокумент2 страницыKilowatt Labs Sirius-Technical Data Sheet-1000-48-B-1C-TM-A-GIvanОценок пока нет

- Activity Sheet No. 3 - Current Resistance EMFДокумент5 страницActivity Sheet No. 3 - Current Resistance EMFJoena EmejasОценок пока нет

- PARTNER Contact Closure Adjunct: Installation InstructionsДокумент6 страницPARTNER Contact Closure Adjunct: Installation InstructionslaurahotОценок пока нет

- Spec PA1049 (5720-5830+MHz+200W) Ver+1.3 180730Документ2 страницыSpec PA1049 (5720-5830+MHz+200W) Ver+1.3 180730phamОценок пока нет

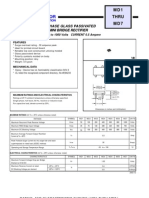

- Rectron Semiconductor Mini Bridge Rectifier Technical SpecificationДокумент2 страницыRectron Semiconductor Mini Bridge Rectifier Technical SpecificationMubashirriskОценок пока нет

- PM172 ManualДокумент82 страницыPM172 ManualLuis Christian Davila CangalayaОценок пока нет

- PVS-100-TL SX2 FULL Inverter: General InformationДокумент3 страницыPVS-100-TL SX2 FULL Inverter: General InformationAdda1Оценок пока нет

- JBL Manual - Northridge E150PДокумент8 страницJBL Manual - Northridge E150PionelflorinelОценок пока нет

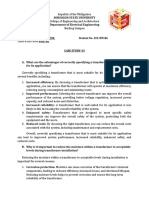

- Case Study #3 - Gigantone, JustineДокумент2 страницыCase Study #3 - Gigantone, JustineJustine LinesОценок пока нет

- Work As Senior Electrical Engineer/Maintenance Engineer / Design Engineer / Supervision / Qa-Qc Engineer /mep Engineer & Low Current EngineerДокумент5 страницWork As Senior Electrical Engineer/Maintenance Engineer / Design Engineer / Supervision / Qa-Qc Engineer /mep Engineer & Low Current Engineerconsultnadeem70Оценок пока нет

- Ultra Fast Avalanche Sinterglass Diode Specifications and Data SheetДокумент7 страницUltra Fast Avalanche Sinterglass Diode Specifications and Data SheetRey TiburonОценок пока нет