Академический Документы

Профессиональный Документы

Культура Документы

Preparatorio 8 DIGITALES

Загружено:

Ronald PillajoАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Preparatorio 8 DIGITALES

Загружено:

Ronald PillajoАвторское право:

Доступные форматы

ESCUELA POLITCNICA NACIONAL

LABORATORIO DE SISTEMAS DIGITALES

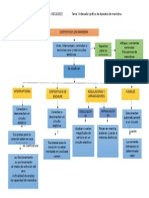

TEMA: DISEO FLIP-FLOPS

Objetivo: Entender el diseo y funcionamiento de multivibradores

biestables, ms conocidos como flip-flops, as como su utilidad prctica.

1. Consultar la distribucin de pines y la tabla de funcionamiento de los

circuitos integrados: 7476, 74107, 74109, 74112. Esta informacin

servir para elaborar el circuito para esa prctica.

7476

Ronald Pillajo GR8-3

ESCUELA POLITCNICA NACIONAL

LABORATORIO DE SISTEMAS DIGITALES

74107

74109

Ronald Pillajo GR8-3

ESCUELA POLITCNICA NACIONAL

LABORATORIO DE SISTEMAS DIGITALES

74112

Ronald Pillajo GR8-3

ESCUELA POLITCNICA NACIONAL

LABORATORIO DE SISTEMAS DIGITALES

2. Disear, utilizando solamente compuertas NOR, un flip-flop S-R

Asincrnico.

S

S

U1:A

2

3

7402

U1:B

5

6

7402

3. Disear, utilizando solamente compuertas NAND, flip-flop S-R

sincrnico activado con la seal de reloj CLK en estado alto y que

tenga PRESET y CLEAR.

1

U1:A

U2

1

3

2

74LS00

NAND_3

U1:B

U3

4

6

5

74LS00

NAND_3

4. Con el circuito integrado 7476, o algn equivalente, disear un flipflop tipo D y tipo T.

Tipo D

Ronald Pillajo GR8-3

ESCUELA POLITCNICA NACIONAL

LABORATORIO DE SISTEMAS DIGITALES

U1:A

U1:A

15

16

14

14

7476

R

3

U2:A

1

U2:A

15

Q

R

1 16

CLK

K

0

1

1

0

4 1

J CLK

7476

2

7404

Tipo T

7404

U1:B

5.

11

10

CLK

K

12

7476

Con el

circuito

integrado 7476, o algn equivalente, en configuracin de flip- flop

U7:A

1

2

13

U1

14

1

2

3

6

7

CKA

CKB

7411

U4

Q0

Q1

Q2

Q3

12

9

8

11

7

1

2

6

4

5

3

R0(1)

R0(2)

R9(1)

R9(2)

12

A

B

C

D

BI/RBO

RBI

LT

QA

QB

QC

QD

QE

QF

QG

13

12

11

10

9

15

14

74LS48

74LS90

U2

14

1

2

3

6

7

CKA

CKB

U5

Q0

Q1

Q2

Q3

12

9

8

11

7

1

2

6

4

5

3

R0(1)

R0(2)

R9(1)

R9(2)

A

B

C

D

BI/RBO

RBI

LT

QA

QB

QC

QD

QE

QF

QG

13

12

11

10

9

15

14

74LS48

74LS90

U3

14

1

2

3

6

7

CKA

CKB

R0(1)

R0(2)

R9(1)

R9(2)

U6

Q0

Q1

Q2

Q3

12

9

8

11

7

1

2

6

4

5

3

A

B

C

D

BI/RBO

RBI

LT

QA

QB

QC

QD

QE

QF

QG

13

12

11

10

9

15

14

74LS48

74LS90

tipo J-K, disear un contador asincrnico mdulo 109 ascendente.

Incluya el circuito de borrado manual.

Referencias

Ronald Pillajo GR8-3

ESCUELA POLITCNICA NACIONAL

LABORATORIO DE SISTEMAS DIGITALES

http://documentation.renesas.com/doc/products/logic/rej03d0425_hd74ls10

7a.pdf

file:///C:/Users/User/Downloads/HD74LS109A.pdf

http://www.electronicaembajadores.com/datos/pdf1/sm/smci/74ls76.pdf

Ronald Pillajo GR8-3

Вам также может понравиться

- Instalación Eléctrica de Un EdificioДокумент13 страницInstalación Eléctrica de Un EdificioRonald Pillajo0% (1)

- Vectores en El EspacioДокумент1 страницаVectores en El EspacioRonald PillajoОценок пока нет

- Elementos de La Optica GeometricaДокумент28 страницElementos de La Optica GeometricaRonald PillajoОценок пока нет

- Conceptos 1ro BachilleratoДокумент1 страницаConceptos 1ro BachilleratoRonald PillajoОценок пока нет

- Óptica geométrica y elementosДокумент15 страницÓptica geométrica y elementosRonald PillajoОценок пока нет

- Preparatorio 1 Control AutomaticoДокумент2 страницыPreparatorio 1 Control AutomaticoRonald PillajoОценок пока нет

- El PlagioДокумент1 страницаEl PlagioRonald PillajoОценок пока нет

- Antro Poce NoДокумент1 страницаAntro Poce NoRonald PillajoОценок пока нет

- Curva Fotométrica de Lámpara IncandescenteДокумент3 страницыCurva Fotométrica de Lámpara IncandescenteRonald PillajoОценок пока нет

- Planificacion Estrategica ComercilaizacionДокумент12 страницPlanificacion Estrategica ComercilaizacionRonald PillajoОценок пока нет

- Fi Ann CieraДокумент4 страницыFi Ann CieraRonald PillajoОценок пока нет

- POBLACIONДокумент1 страницаPOBLACIONRonald PillajoОценок пока нет

- Planificacion Estrategica ComercilaizacionДокумент12 страницPlanificacion Estrategica ComercilaizacionRonald PillajoОценок пока нет

- BarridoTecladoSubrutinasДокумент4 страницыBarridoTecladoSubrutinasRonald PillajoОценок пока нет

- Análisis comparativo PLC de Seguridad Allen-Bradley vs PLC Estándar SiemensДокумент5 страницAnálisis comparativo PLC de Seguridad Allen-Bradley vs PLC Estándar SiemensRonald PillajoОценок пока нет

- Análisis comparativo PLC de Seguridad Allen-Bradley vs PLC Estándar SiemensДокумент5 страницAnálisis comparativo PLC de Seguridad Allen-Bradley vs PLC Estándar SiemensRonald PillajoОценок пока нет

- El Cambio Climatic GlobalДокумент2 страницыEl Cambio Climatic GlobalRonald PillajoОценок пока нет

- Informe 10 de Circuitos IIДокумент14 страницInforme 10 de Circuitos IIRonald PillajoОценок пока нет

- Deber 4 de Cotrol IndustrialДокумент1 страницаDeber 4 de Cotrol IndustrialRonald PillajoОценок пока нет

- Familias Lógicas Mos y CmosДокумент26 страницFamilias Lógicas Mos y CmosRonald Pillajo50% (2)

- Proyecto de InstrumetnacionДокумент2 страницыProyecto de InstrumetnacionRonald PillajoОценок пока нет

- VlanДокумент7 страницVlanRonald PillajoОценок пока нет

- Apartos de ManiobraДокумент1 страницаApartos de ManiobraRonald PillajoОценок пока нет

- Practica #4Документ8 страницPractica #4Pablo David EОценок пока нет

- Curva Fotométrica de Lámpara IncandescenteДокумент3 страницыCurva Fotométrica de Lámpara IncandescenteRonald PillajoОценок пока нет

- Preparatorio 1 Control AutomaticoДокумент2 страницыPreparatorio 1 Control AutomaticoRonald PillajoОценок пока нет

- Informe 10 de Circuitos IIДокумент14 страницInforme 10 de Circuitos IIRonald PillajoОценок пока нет

- Preparatorio 6 de ConversionДокумент6 страницPreparatorio 6 de ConversionRonald PillajoОценок пока нет