Академический Документы

Профессиональный Документы

Культура Документы

Familii de Circuite Integrate Digitale

Загружено:

LupRaduАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Familii de Circuite Integrate Digitale

Загружено:

LupRaduАвторское право:

Доступные форматы

Laborator 04

2007/2008

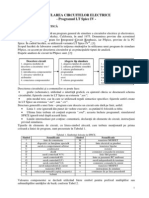

FAMILII DE CIRCUITE INTEGRATE DIGITALE

1. FAMILIA TTL

Familia TTL (Transistor Transistor Logic) a fost introdus de firma Texas Instruments (SUA) n anul

1965 i a fost realizat n tehnologie bipolar. Este cea mai rspndit familie de circuite integrate digitale i a

influenat constant dezvoltarea echipamentelor numerice. n prezent aria de utilizare a circuitelor TTL este

limitat (datorit dezvoltrii aplicaiilor cu microcontroler i a circuitelor de tip ASIC) dar conceptele i

blocurile funcionale din aceast familie sunt utilizate n majoritatea proiectelor moderne.

Toate subfamiliile (seriile) TTL sunt compatibile ntre ele pin la pin ct i se pot interconecta direct, cu

respectarea ncrcrii ieirilor i a timpilor de propagare, conform valorilor specificate n tabelul 4.2.

Circuitele logice din familia TTL sunt fabricate cu tranzistoare bipolare npn, funcioneaz n logica

de nivel pozitiv i sunt alimentate cu o tensiune pozitiv fa de masa de 5V.

1.1. CIRCUITUL 74LS00 4 PORI I-NU cu 2 intrri

Circuitul integrat, din seria TTL-LS, 74LS00 conine 4 pori I-NU (NAND) cu cte 2

intrri. Configuraia pinilor capsulei i modul de amplasare al porilor este redat n figura 4.1.

14 13

Vcc

12

11

10

U1C

U1D

U1A

U1B

GND

1

Figura 4.1 Configuraia pinilor circuitului 74LS00.

n cazul oricrui circuit integrat, ntotdeauna pinul 1 se afl n partea stng a

marcajului (a cheii), numerotarea realizndu-se n mod circular antiorar, astfel nct ultimul

pin s fie n dreapta cheii. Privirea se face de sus, spre partea marcat (nscris, cu pinii n

jos).

Alimentarea circuitului, de altfel a majoritii circuitelor digitale, pinul 7 (8 sau

ultimul din stnga jos fa de cheie) reprezint masa (GND, -) iar pinul 14 (16 sau ultimul din

dreapta sus fa de cheie) reprezint Vcc (+).

La proiectarea schemelor cu circuite logice (pori logice) se face referire la numrul de

ordine (poziia) fiecrei pori, prin numele de referin A,B,C sau D (sau pn la litera care

reprezint ultima poart din capsul). Notaia U (IC sau CI) exprim referina capsulei

(a circuitului n totalitate). De exemplu, dac U1 este denumirea circuit integrat din figura 4.1,

atunci U1A reprezint prima poart, respectiv U1B, U1C i U1D celelalte pori.

Laborator 04

2007/2008

1.2. CARACTERISTICILE CIRCUITELOR INTEGRATE TTL

A). Tensiunea de alimentare (Vcc)

Este de +5V (5%, adic 4,75V 5,25V) pentru seriile standard (74xxx) i de +5V

(10%, adic 4,5V 5,5V) pentru seria militar (54xxx).

Nu este permis alimentarea invers a circuitului integrat, acest lucru, chiar i pe

durate relativ reduse de timp, conduce la distrugerea acestuia.

B). Niveluri logice garantate

Principalele tensiuni care descriu nivelurile de intrare i de ieire ale unui circuit TTL:

ViL - tensiunea de intrare n starea Low (nivelul de tensiune recunoscut de circuit ca fiind

corespunztor valorii 0 logic);

ViH - tensiunea de intrare n starea High (nivelul de tensiune recunoscut de circuit ca fiind

corespunztor valorii 1 logic);

VOL - tensiunea de ieire n starea Low (nivelul de tensiune furnizat de circuit n stare 0 logic);

VOH - tensiunea de ieire n starea High (nivelul de tensiune furnizat de circuit n stare 1logic);

VTh - tensiunea de prag (threshold), reprezint tensiunea de intrare la care se produce comutarea

ieirii dintr-o stare logic n alta.

Valorile limit pentru parametrii enumerai anterior sunt redate n Tabelul 4.1.

Tabelul 4.1

Niveluri logice garantate pentru seria TTL-LS.

Tensiune

ViL

ViH

VOL

VOH

Valori limit

minim [V] maxim [V]

0

0,8

2

Vcc

0

0,5

2,4

Vcc

C). Unitatea de sarcin TTL

O unitate de sarcin TTL reprezint consumul, n curent, al unei intrri TTL conectate

la ieirea unui circuit din aceeai serie (sau dintr-o serie compatibil TTL). Valorile indicate

n tabelul 4.2 se refer att la unitatea de sarcin TTL (IIL i IIH) ct i la capabilitatea n curent

a ieirilor (IOL i IOH).

Tabelul 4.2

Curenii de intrare i ieire ai circuitelor din seriile TTL.

Laborator 04

2007/2008

D). Marginea de zgomot de curent continuu

Marginea de zgomot de curent continuu reprezint nivelul maxim al unui semnal

perturbator aplicat la intrarea unei pori TTL (aflat n starea Low respectiv High) care nu i

afecteaz funcionarea (ieirea nu comut n alt stare).

Pentru valorile limit specificate n tabelul 4.1, se poate deduce c marginea de

zgomot de curent continuu este de 400mV. Aceast valoare este garantat de productori dar,

n practic, se constat c ea poate s ating valoarea de 1V (pentru familia TTL standard).

E). Marginea de zgomot de curent alternativ

Marginea de zgomot de curent alternativ depinde de energia (durata i amplitudinea)

impulsului perturbator. Cu ct semnalul perturbator are durata mai mic, cu att amplitudinea

sa trebuie s fie mai mare pentru a putea determina comutarea ieirii porii. Imunitatea porii

I-NU la tranziii ieirii din 0 n 1 este n general mai bun dect pentru o tranziie din

1 n 0 datorit timpului de propagare mai mare tpLH fa de tpHL.

F). Factorul de branament (FAN-out)

Factorul de branament reprezint numrul maxim de intrri care pot fi conectate

simultan la ieirea unei pori din aceeai serie. Se determin pe baza ncrcrii statice a ieirii

raportnd curenii de ieire la curenii de intrare. NH=20 (pt.0,8mA); NL=10 (pt.16mA). Se

obine, pentru seria standard N = 10.

G). Timpul de propagare

Timpul de propagare reflect o relaie temporal ntre semnalul se intrare i de ieire.

El reprezint un interval de timp ntre puncte de referin specificate pe formele de und ale

semnalelor de intrare i ieire. Mai poate fi definit ca fiind ntrzierea introdus de circuit

n propagarea semnalelor de la intrare la ieire.

Se definete un timp de propagare la tranziia din 0 n 1 a ieirii (tpLH), un timp de

propagare la tranziia din 1 n 0 a ieirii (tpHL) i un timp mediu de propagare:

t pLH + t pHL

tp =

2

Se determin pentru o poart I-NU avnd semnalul de intrare ui aplicat unei singure

intrri, celelalte fiind conectate la nivelul UiH, n condiii normale de temperatur (25C) i

tensiune de alimentare (5V).

ui

UiH

UiH

ui

0,5U iH

UiL

u0

U0H

u0

0,5U0H

Pentru seria standard se obin urmtoarele valori tipice:

t pLH = 12ns

t p = 10ns

t

pHL = 8ns

U0L

tpHL

t pLH

Laborator 04

2007/2008

Principalii parametri electrici ai circuitelor din seriile TTL sunt prezentai succint n

tabelul 4.3.

Tabelul 4.3

Parametrii electrici ai circuitelor din seriile TTL.

1.3 . DESFURAREA LUCRRII

Placa experimental (figura 4.3) permite msurarea parametrilor electrici ai circuitului

integrat 74xx00.

Figura 4.3 Vedere de ansamblu asupra plcii experimentale.

Amplasarea componentelor i numerotarea pinilor de test (de msurare) este redat n

figura 4.4.

Figura 4.4 Vedere spre faa plantat i numerotarea pinilor de test.

Laborator 04

2007/2008

Alimentarea circuitului se realizeaz prin intermediul pinilor notai +5V, GND i +2V

i GND, cu ajutorul unei surse duble externe.

1.3.1. Determinarea potenialului intrrilor nefolosite i a ieirilor corespunztoare

Pentru Vcc = 5V se msoar potenialul intrrii nefolosite a porii U1B, conectnd un

voltmetru ntre pinii de test 7 i 8. n continuare se msoar nivelul ieirii aceleiai pori ntre

pinii de test 9 i 10, pentru comutatorul K2 pe poziia (a) respectiv (b). Se vor compara i

comenta rezultatele.

Figura 4.5 ilustreaz zona de interes a plcii de test pentru msurrile cerute.

Figura 4.5 Pinii utilizai la msurarea potenialelor intrrilor i ieirii aferente

1.3.2. Verificarea nivelului de tensiune 0 logic la intrare

Se verific dac ViLmax 0,8 V pe o intrare, la testarea n cazul cel mai defavorabil.

Schema electronic de test este redat n figura 4.6a i necesit folosirea a dou

voltmetre numerice, un semireglabil i o poart logic I-NU.

5V

+V

5V

+V

U1A

P1

+

+

Vi

Vo

-

a).

b).

Figura 4.6 Verificarea nivelului ViLmax.

Se va utiliza poarta U1A, semireglabilul P1, comutatorul K1 i pinii de test 1, 2, 3 i 4.

Tensiunea de alimentare se fixeaz la Vccmin = 4,75V iar intrarea necomandat se conecteaz

la 1 logic prin plasarea comutatorului K1 pe poziia (a). Voltmetrul Vi se conecteaz ntre

pinii de test 1 i 2 iar voltmetrul Vo ntre pinii de test 3 i 4. Prin ajustarea semireglabilului

P1, se regleaz descresctor tensiunea aplicat la intrare de la Vcc la ViLmax, valoare la care

tensiunea la ieirea porii devine VoH. Schimbarea nivelului logic la ieire se poate urmri i

prin iluminarea ledului Out (verde) de pe placa de test.

Zona de interes a plcii de test pentru msurrile cerute este ilustrat n figura 4.6b.

Se vor msura seturi de valori pentru ViLmax pentru diferite serii din familia TTL.

5

Laborator 04

2007/2008

1.3.3. Verificarea nivelului de tensiune 1 logic la intrare

Se verific dac ViHmin 2 V pe o intrare pentru cazul cel mai defavorabil. Se fixeaz

Vccmax = 5,25V. Se utilizeaz dou voltmetre numerice, un semireglabil i o poart I-NU, aa

cum se poate observa din figura 4.7a.

5V

+V

U1A

P1

+

+

Vi

Vo

a).

b).

Figura 4.7 Verificarea nivelului ViHmin.

Se va utiliza poarta U1A, semireglabilul P1, comutatorul K1 i pinii de test 1, 2, 3 i 4.

Cele dou intrri ale pori U1A se conecteaz mpreun, prin comutarea lui K1 pe poziia (b).

Prin ajustarea semireglabilului P1 se aplic la intrare o tensiune ntre 0 i ViH pn cnd

tensiunea de la ieirea porii testate devine VoL, notndu-se astfel valoarea ViHmin. Voltmetrul

Vi se conecteaz ntre pinii de test 1 i 2 iar voltmetrul Vo ntre pinii de test 3 i 4.

Schimbarea nivelului logic la ieire se poate urmri i prin stingerea ledului Out

(verde) de pe placa de test.

Se vor nota seturi de valori msurate pentru ViHmin aferente diferitelor serii TTL.

Zona de interes a plcii de test pentru msurrile cerute este ilustrat n figura 4.7b.

1.3.4. Verificarea curentului de intrare IiL

Se verific dac IiL | -1,6 mA | pe o intrare, n cazul cel mai defavorabil. Se verific

pentru seria standard i apoi pentru celelalte serii. Se alege Vcc = Vccmax = 5,25V i se

folosete un voltmetru (Vi) i un miliampermetru (Ii) conectate aa ca n figura 4.9.

Vcc

+V

U1B

U1A

P1

Ii

+

Vi

-

a).

b).

Figura 4.8 Verificarea curentului IiL.

Se experimenteaz utiliznd poarta U1B, pinii de test 5, 6, 7 i 8, comutatorul K2 i

semireglabilul P2. Intrarea neutilizat se aduce la 1 logic prin comutarea lui K2 n poziia (a).

6

Laborator 04

2007/2008

Prin ajustarea poziiei semireglabilului P2 se fixeaz tensiunea la intrare ViL = 0,4V prin

urmrirea indicaiei voltmetrului Vi conectat ntre pinii de test 7 i 8 i se citete valoarea

curentului IiL indicat de ctre miliampermetrul conectat ntre pinii de test 5 i 6. Pe parcursul

experimentrii, ieirea se menine n gol.

Se vor repeta msurrile pentru diferite serii de circuite din familia TTL studiat.

Zona de interes a plcii de test pentru msurrile cerute este ilustrat n figura 4.8b.

1.3.5. Verificarea curentului de intrare n starea 1 logic

Se verific dac IiH 40 A pentru seria standard i apoi pentru alte serii TTL, n cele

mai defavorabile condiii de testare.

U1B

Ii

+

Vih

a).

b).

Figura 4.9 Verificarea curentului IiH.

Schema electronic a montajului experimental cuprinde un miliampermetru conectat

ntre tensiunea ViHmin = 2V i o intrare a unei pori I-NU (figura 4.9a). Circuitul se

alimenteaz la Vcc = Vccmax = 5,25V. Ieirea se menine n gol.

Pentru experimentare se va utiliza poarta U1B, iar K2 se va aduce n poziia (b) pentru

a conecta la mas intrarea nefolosit. Miliampermetrul se conecteaz ntre borna de

alimentare +2V i pinul de test 6 i se citete valoarea indicat.

Zona de interes a plcii de test pentru msurrile cerute este ilustrat n figura 4.9b.

1.3.6. Verificarea nivelului de tensiune 0 logic la ieire

Se verific dac n cazul cel mai defavorabil se menine VoLmax 0,4V. Schema de

testare experimental, prezentat n figura 4.10a, cuprinde o surs de alimentare de +2V

pentru generarea nivelului ViHmin la intrare, un voltmetru i un miliampermetru nseriat cu

ieirea unei pori I-NU conectate printr-un semireglabil la Vcc.

+V

Vccmin

P1

Vihmin

Io

+

U1C

+

+

Vo

-

a).

b).

Figura 4.10 Determinarea nivelului VoL la ieire.

Laborator 04

2007/2008

Circuitul se alimenteaz la Vccmin = 4,75V. Pentru experimentare se va utiliza poarta

U1C, voltmetrul se conecteaz la ieirea porii, ntre pinii de test 11 i 14 iar miliampermetrul

ntre 12 i 13. Prin ajustarea semireglabilului P3 se stabilete curentul de ieire la IoLmax

corespunztor seriei din care face parte circuitul, echivalent cu o ncrcare FAN-OUT = 10.

Se citete valoarea indicat de voltmetru.

Zona de interes a plcii de test pentru msurrile cerute este ilustrat n figura 4.10b.

1.3.7. Verificarea nivelului de tensiune 1 logic la ieire

Se verific dac n cazul cel mai defavorabil se menine valoarea VoH 2,4 V. Pentru

aceasta, se stabilete alimentarea circuitului la Vcc = 4,75V i se utilizeaz schema de testare

din figura 4.11.

Vccmin

+V

Vo

Vi

P1

Io

+

U1C

P2

a).

b).

Figura 4.11 Determinarea nivelului VoH.

Pentru determinarea experimental se va utiliza poarta U1D, un voltmetru conectat

ntre pinii de test 15 i 16 pentru citirea tensiunii la intrare, un voltmetru conectat ntre pinii

de test 17 i 16 pentru urmrirea tensiunii de ieire i un miliampermetru ntre 18 i 19. Prin

ajustarea semireglabilului P5 se asigur la intrare tensiunea ViLmax = 0,4V i apoi se stabilete

din P4 un curent IoHmax = 20 IiH echivalent cu FAN-OUT = 20. Se citete i se noteaz

valoarea tensiunii la ieirea porii indicat de voltmetrul aferent.

Zona de interes a plcii de test pentru msurrile cerute este ilustrat n figura 4.11b.

1.3.8. Msurarea curentului de scurtcircuit la ieire

Se efectueaz doar pentru seria standard i se verific dac valoarea curentului de

ieire n condiia conectrii acesteia la mas printr-un miliampermetru, este cuprins ntre

22mA i 55mA. Ambele intrri se vor conecta mas (figura 4.12a).

U1B

I0

a).

b).

Figura 4.12 Determinarea curentului de scurtcircuit.

Circuitul se alimenteaz la Vccmax = 5,25V. Se va utiliza poarta U1B, comutatorul K2

se trece n poziia (b) iar pinul de test 7 se conecteaz cu pinul de test 8 printr-un conductor.

8

Laborator 04

2007/2008

Miliampermetrul se nseriaz ntre pinii de test 9 i 10 i se citete valoarea indicat. Se

evalueaz rezultatul. Zona de interes este ilustrat n figura 4.12b.

1.3.9. Determinarea curentului de alimentare al capsulei

Acest curent are valori diferite funcie de starea logic a ieirilor. Pentru o msurare

concludent, toate porile din capsul trebuie meninute n aceeai stare. Dac toate ieirile

sunt n stare 1, se determin curentul ICCH iar dac sunt pe 0 se determin ICCL.

Tensiunea de alimentare se fixeaz la valoarea maxim i se nseriaz cu alimentarea

plcii de test un miliampermetru. Se noteaz valorile msurate ale curentului de alimentare

(ICCH i ICCL) pentru diferite serii de circuite TTL.

1.3.10. Reprezentarea caracteristicii de transfer statice

Pentru o poart I-NU din seria standard, se va urmri, prin msurri succesive,

dependena tensiunii de ieire Vo de tensiunea de intrare Vi.

5V

+V

U1A

P1

+

+

Vi

Vo

a).

b).

Figura 4.13 Determinarea caracteristicii de transfer statice.

Se va utiliza poarta U1A (figura 4.13a), ntre pinii de test 1 i 2 se conecteaz

voltmetrul ce va indica valoarea tensiunii Vi iar ntre pinii de test 3 i 4 voltmetrul care indic

valoarea lui Vo. Comutatorul K1 se fixeaz n poziia (b). Cu ajutorul semireglabilului P1 se

ajusteaz valoarea tensiunii de la intrare, ntre 0 i Vcc, cu pasul de cretere 0,1V. Zona de

interes pentru msurare este reprezentat n figura 4.13b. Pentru fiecare valoare a acestei

tensiuni se noteaz corespondentul de la ieire (Vo) completnd urmtorul tabel:

Seria TTL Standard

Vi [V]

0,1

0,2

0,3

0,4

0,5

0,6

0,7

0,8

0,9

1,1

1,2

1,3

1,4

1,5

1,6

1,7

0,1

0,2

0,3

0,4

0,5

0,6

0,7

0,8

0,9

1,1

1,2

1,3

1,4

1,5

1,6

1,7

Vo [V]

Seria TTL -LS

Vi [V]

Vo [V]

Pe baza rezultatelor, se vor reprezenta grafic valorile, pentru fiecare serie n parte, pe

aceeai diagram.

Se vor calcula marginile de zgomot de curent continuu n starea 1 i 0 la intrare.

9

Laborator 04

2007/2008

Vo

Figura 4.14 Caracteristica de transfer static.

Vi

1.3.11. Determinarea timpului de propagare

Utiliznd un generator de impulsuri GEN, la intrarea porii U1B se aplic un semnal

dreptunghiular, periodic, cu amplitudinea 3,5 V, frecvena 1MHz i factorul de umplere 50%

(figura 4.15a). Zona de interes aferent experimentrii este redat n figura 4.15b.

Se utilizeaz pinii de test 7 i 8 pentru intrare (OSC1) iar K2 se fixeaz n poziia (a).

ntre pinii de test 9 i 10 se va conecta sonda unui osciloscop pentru vizualizarea semnalului

de ieire (OSC2). Pentru simularea condiiilor nefavorabile de ncrcare cu sarcin a ieirii, se

vor conecta n paralel cu pinii 9 i 10 capaciti de valori diferite (C = 1nF, 10nF, 100nF) i se

va urmri, pe osciloscop, efectul acestora asupra timpului de propagare.

OSC2

U1B

GEN

C = 1nF

OSC1

a).

b).

Figura 4.12 Determinarea timpului de propagare.

n urma tuturor msurrilor experimentale, se va completa tabelul urmtor i se va

realiza un studiu comparativ concludent.

tpLH

tpHL

n gol

TTL Standard

TTL-LS

10

tpLH

tpHL

sarcin 1nF

Вам также может понравиться

- 4 Circuite Integrate NumericeДокумент36 страниц4 Circuite Integrate NumericefuqUPGОценок пока нет

- Circuit IntegratДокумент3 страницыCircuit IntegratSfatolea RaduОценок пока нет

- Proiect Didactic Conversia NumerelorДокумент8 страницProiect Didactic Conversia NumerelorLudmila BivolОценок пока нет

- CID 05 Familii de Circuite LogiceДокумент27 страницCID 05 Familii de Circuite LogiceYanBОценок пока нет

- Eprofu - Ro Tehnic Curriculum Tehnic Electronica AutomatizДокумент2 страницыEprofu - Ro Tehnic Curriculum Tehnic Electronica AutomatizTrofin Petro100% (1)

- Fisa5 OnlineДокумент5 страницFisa5 OnlineAna BadeaОценок пока нет

- OscilatorДокумент34 страницыOscilatorFeta MirayОценок пока нет

- Circuite Digitale CursДокумент266 страницCircuite Digitale CursfirenzeОценок пока нет

- Model de Subnetizare 2Документ1 страницаModel de Subnetizare 2Ionescu Valentin AlexandruОценок пока нет

- Lucrare 3 Laborator ASCN IIДокумент5 страницLucrare 3 Laborator ASCN IIperyplatipuОценок пока нет

- Anul 4Документ6 страницAnul 4Anghel AndreiОценок пока нет

- C1 Cna PDFДокумент31 страницаC1 Cna PDFAlexandru Marian MoțeiОценок пока нет

- Grafuri Si Arbori Teorie UltimДокумент9 страницGrafuri Si Arbori Teorie UltimArcan Radu AlexandruОценок пока нет

- Fisa Experimentala Focuri Flacari ArtificiiДокумент2 страницыFisa Experimentala Focuri Flacari ArtificiiMVОценок пока нет

- EXAMEN FINAL - PSC - Etti - Bucuresti - v2Документ8 страницEXAMEN FINAL - PSC - Etti - Bucuresti - v2Raluca IrimiaОценок пока нет

- 1.circuite Electrice Liniare de Curent ContinuuДокумент39 страниц1.circuite Electrice Liniare de Curent ContinuuGalea DuminicaОценок пока нет

- Comparatoare NumericeДокумент23 страницыComparatoare NumericeZisu CorneliuОценок пока нет

- Subiecte Rezolvate EADBДокумент81 страницаSubiecte Rezolvate EADBAdelina GruianuОценок пока нет

- Curs 6 TEC-JДокумент10 страницCurs 6 TEC-JAlexandra PopescuОценок пока нет

- Test de Evaluare Initiala Clasa A XII-a ELECTRONICA SI AUTOMATIZARIДокумент3 страницыTest de Evaluare Initiala Clasa A XII-a ELECTRONICA SI AUTOMATIZARIGheorghe SauciucОценок пока нет

- Modul de Reglare Al Amplificatorului Catv Ai-233Документ5 страницModul de Reglare Al Amplificatorului Catv Ai-233Valentin ŢîţuОценок пока нет

- Probleme Rezolvate 1 ElectronicaДокумент3 страницыProbleme Rezolvate 1 ElectronicanykuОценок пока нет

- Plan Circuite de BasculanteДокумент5 страницPlan Circuite de BasculanteragneluОценок пока нет

- Probleme DeeaДокумент13 страницProbleme DeeaJelihovsky IgorОценок пока нет

- Dioda Semiconductoare1Документ14 страницDioda Semiconductoare1Alina JumoleaОценок пока нет

- Laborator Arhitectura Micriprocesoarelor ETTIДокумент14 страницLaborator Arhitectura Micriprocesoarelor ETTIValyMADDОценок пока нет

- Comunicatii Cu Modulatie LiniaraДокумент26 страницComunicatii Cu Modulatie Liniaramatrionel100% (1)

- VLSIДокумент25 страницVLSITudor ZadorojneaacОценок пока нет

- DocumentatieДокумент40 страницDocumentatietimo amvОценок пока нет

- Reactia in Amplificatoare. Particularitatile Reactiei Pozitive (Întrebarea 10)Документ5 страницReactia in Amplificatoare. Particularitatile Reactiei Pozitive (Întrebarea 10)Inna MunteanОценок пока нет

- Subiecte Examen Dispozitive ElectroniceДокумент1 страницаSubiecte Examen Dispozitive ElectroniceDoru PascaОценок пока нет

- Verilog HDL TutorialДокумент29 страницVerilog HDL TutorialstefanОценок пока нет

- Fisa de Lucru AtomulДокумент1 страницаFisa de Lucru Atomulalbaretto13Оценок пока нет

- Cap1 Subnetizare ExempleДокумент7 страницCap1 Subnetizare Exempleflorinciocan0% (1)

- Subiecte Atestat Programare IntensivДокумент17 страницSubiecte Atestat Programare IntensivLavinia MitranОценок пока нет

- Test X Operatori Var ExpresiiДокумент1 страницаTest X Operatori Var ExpresiiCosmi Feli Chira VadaОценок пока нет

- Test Powerpoint Cls 6Документ1 страницаTest Powerpoint Cls 6ritamosnoiОценок пока нет

- Realizare Practica LiftДокумент29 страницRealizare Practica LiftCiprian Cosmin MiroiuОценок пока нет

- Practica HardwareДокумент97 страницPractica Hardwarestars14july6863Оценок пока нет

- 2.1. Tablou UnidimensionalДокумент16 страниц2.1. Tablou UnidimensionalMoisa VicaОценок пока нет

- Structuri de Date Si AlgoritmiДокумент71 страницаStructuri de Date Si AlgoritmijackОценок пока нет

- Algoritmi de AproximareДокумент94 страницыAlgoritmi de AproximareValy LupascuОценок пока нет

- Implement Area CLC Cu Demultiplexoare Si PLAДокумент7 страницImplement Area CLC Cu Demultiplexoare Si PLAlaszlo123Оценок пока нет

- 5 GhiocelДокумент2 страницы5 GhiocelMicky BОценок пока нет

- Tester TiristoareДокумент2 страницыTester Tiristoarepaulmx13Оценок пока нет

- 4 - Proiectare VLSI - HDL3Документ104 страницы4 - Proiectare VLSI - HDL3GeorgeAntonОценок пока нет

- Simularea Circuitelor Electrice - LTSpice Facultatea UPTДокумент4 страницыSimularea Circuitelor Electrice - LTSpice Facultatea UPTDaniel-Costel DamianОценок пока нет

- ASDNДокумент16 страницASDNDan CojucariОценок пока нет

- EXAMEN FINAL - PSC - Etti - Bucuresti - v1Документ9 страницEXAMEN FINAL - PSC - Etti - Bucuresti - v1Raluca IrimiaОценок пока нет

- ACR Examen FinalДокумент14 страницACR Examen FinalCаша КушниренкоОценок пока нет

- Analiza Circuitelor ElectroniceДокумент128 страницAnaliza Circuitelor ElectroniceMarius Viorel100% (1)

- 3 Planificare calendaristica-M1-Bazele Electronicii Analogice - X - Liceu - Electronica AutomatizariДокумент5 страниц3 Planificare calendaristica-M1-Bazele Electronicii Analogice - X - Liceu - Electronica Automatizarimatt100% (1)

- Lab - 4 - Tranzistorul Cu Efect de Camp TEC-J - 2020Документ5 страницLab - 4 - Tranzistorul Cu Efect de Camp TEC-J - 2020Olesea Nicolai100% (1)

- Echilibre Chimice in Solutie TeorieДокумент14 страницEchilibre Chimice in Solutie TeorieToma Alexandru TiberiuОценок пока нет

- 03 Familia TTLДокумент36 страниц03 Familia TTLmaximmaxim159100% (1)

- Poarta Logica TTL StandardДокумент9 страницPoarta Logica TTL StandardSirghii FiodorОценок пока нет

- Porti LogiceДокумент110 страницPorti LogicetataraseanuОценок пока нет

- Circuite Integrate Numerice - IndrumatorДокумент47 страницCircuite Integrate Numerice - IndrumatorGal Adrian-FaithОценок пока нет

- Familia TTLДокумент9 страницFamilia TTLSergiu ChistolОценок пока нет

- 8&9 TTL PDFДокумент12 страниц8&9 TTL PDFAndrei BujaОценок пока нет

- Psurt - 01 01 2017Документ58 страницPsurt - 01 01 2017LupRaduОценок пока нет

- Piata Serviciilor de TransportДокумент10 страницPiata Serviciilor de TransportMadalina MihalceaОценок пока нет

- Analiza Transportatorilor Din Romania PDFДокумент21 страницаAnaliza Transportatorilor Din Romania PDFPopescuОценок пока нет

- Lup Radu Sisteme SCADA in Stati ElectriceДокумент23 страницыLup Radu Sisteme SCADA in Stati ElectriceLupRaduОценок пока нет

- Dispozitia Nr.9 - Majorare TIMДокумент28 страницDispozitia Nr.9 - Majorare TIMLupRaduОценок пока нет

- Amplificatoare OperationaleДокумент44 страницыAmplificatoare OperationalegheoangelОценок пока нет

- Circuit MakerДокумент9 страницCircuit MakerLupRaduОценок пока нет

- Automatizari Proiect-TeorieДокумент65 страницAutomatizari Proiect-TeorieCălin RoxanaОценок пока нет

- Technologia Electromagnetilor de Curent AlternativДокумент17 страницTechnologia Electromagnetilor de Curent AlternativLup RaduОценок пока нет

- Amplificatoare Cu AOДокумент7 страницAmplificatoare Cu AOLupRaduОценок пока нет

- 05 - Sisteme de Reglare Automata IДокумент97 страниц05 - Sisteme de Reglare Automata IMelissa ShafferОценок пока нет