Академический Документы

Профессиональный Документы

Культура Документы

Chapter 08 BJT Small Signal Analysis

Chapter 08 BJT Small Signal Analysis

Загружено:

cinematic300650%(4)50% нашли этот документ полезным (4 голоса)

3K просмотров58 страницThe transistor models introduced in chapter 7 will be used to perform smull signal ac analysis of a number of standard transistor network configurations. The effect of an output impedance is examined as provided by the hoe parameter of the hybrid equivalant model. A section is devoted to the small-signal analysis of BIT networks lIsing solely the hybrid equivalent model.

Исходное описание:

Оригинальное название

Chapter 08 Bjt Small Signal Analysis

Авторское право

© Attribution Non-Commercial (BY-NC)

Доступные форматы

PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документThe transistor models introduced in chapter 7 will be used to perform smull signal ac analysis of a number of standard transistor network configurations. The effect of an output impedance is examined as provided by the hoe parameter of the hybrid equivalant model. A section is devoted to the small-signal analysis of BIT networks lIsing solely the hybrid equivalent model.

Авторское право:

Attribution Non-Commercial (BY-NC)

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

50%(4)50% нашли этот документ полезным (4 голоса)

3K просмотров58 страницChapter 08 BJT Small Signal Analysis

Chapter 08 BJT Small Signal Analysis

Загружено:

cinematic3006The transistor models introduced in chapter 7 will be used to perform smull signal ac analysis of a number of standard transistor network configurations. The effect of an output impedance is examined as provided by the hoe parameter of the hybrid equivalant model. A section is devoted to the small-signal analysis of BIT networks lIsing solely the hybrid equivalent model.

Авторское право:

Attribution Non-Commercial (BY-NC)

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 58

336

BJT Small-Signal

Analysis

8.1 INTRODUCTION

‘The transistor models introduced in Chapter 7 will now be used to perform asm

signal ac analysis of a number of standard transistor network configu

networks analyzed represent the majority of those appearing in practice today.

fications of the standard configurations will be relatively easy to examine

content of this chapter is reviewed and understood.

Since the r, model is sensitive to the actual point of operation it will be

primary model for the analysis to be performed. For each configuration, however,

effect of an output impedance is examined as provided by the /i,. parameter of

hybrid equivalant model. To demonstrate the similarities in analysis that exist

tween models a section is devoted to the small-signal analysis of BIT networks

solely the hybrid equivalent model. The analysis of this chapter does not ine

load resistance R;, or source resistance R,. The effect of both parameters is reser

for a systems approach in Chapter 10.

‘The computer analysis section includes a brief description of the transistor mod

employed in the PSpice software package. It demonstrates the range and depth of th

computer analysis systems available today and how relatively easy it is to enter

‘complex network and print out the desired results. A program in BASIC is includ

permit a comparison between the use of a software package and a computer languag

8.2 COMMON-EMITTER FIXED-BIAS

CONFIGURATION

The first configuration to be analyzed in detail is the common-emitter fixed-bids

network of Fig, 8.1, Note that the input signal V, is applied to the base of the transis:

tor while the output V,, is off the collector. In addition, recognize that the inpul

current /, is not the base current but the source current, while the output current {iy

the collector current. The small-signal ac analysis begins by removing the de effects

of Vec and replacing the de blocking capacitors C, and C, by short-circuit equiva

ents, resulting in the network of Fig. 8.

Note in Fig. 8.2 that the common ground of the de supply and the transistor

emitter terminal permits the relocation of Ry and Re: in parallel with the input and

output sections of the transistor, respectively. In addition, note the placement of the

important network parameters Z,, Z,,. [;, and I, on the redrawn network. Substituting

the r, model for the common-emitter configuration of Fig. 8.2 will result in the

network of Fig. 8.3

Figure 8.1 Common-cmitter fixed-bias con: Figure 8.2 Network of Figure 8.1 following

figueation, the removal of the effects of Vee, Cy and Cs

1

Figure 8.3. Substituting the r,

model into the network of Fig

82.

‘The next step is find @ and r,. The magnitude of f is typically obtained from a

specification sheet or by direct measurement using a curve tracer or transistor testing

instrument. The value of r, must be determined from a de analysis of the system.

Assuming that both and , have been determined will result in the following equa-

tions for the important two-port characteristics of the system.

Zz Figure 8.3 clearly reveals that

ohms: B.D

For the majority of situations Rp is greater than Bre by more than a factor of 10

(recall from the analysis of parallel elements that the total resistance of two parallel

resistors is always less than the smallest and very close to the smallest if one is much

larger than the other), permitting the following approximation:

_Zi= Bre ohms. (8.2)

Zp: Recall that the output impedance of any system is defined as the impedance

Z, determined when V; = 0. For Fig. 8.3, when V; = 0, J; 0, resulting in an

open-circuit equivalence for the current source. The result is

Z=Re ‘ohms (8.3)

Solving for V,, gives

Vo = —tRe

‘The minus sign specifies that the polarity of V,, is opposite to that defined by the

indicated direction of /,, Substituting /, = Bly yields

Vo = ~BloRe

8.2 Common-Emitter Fixed-Bias Configuration

337

Figure 85 Including r, in che

output circuit ofthe common:

emiter equivalent circuit.

338

Assuming that Ry > Br, permits the approximation J, = J, resulting in

—BLRe

7 Miz

os iz oe:

Vv,

and v, -al Ae)Re

. EE]

Note the explicit absence of 6 in Eq. (8.4), although we recognize that B

utilized to determine r,.

Ag The current gain is determined in the following manner:

Jo = Bly = Bly

and

‘The approximation sign of Eq. (8.5) is present due to the assumption that Ry >

Phase Relationship: The negative sign in the resulting equation for A, r

that a 180° phase shift occurs between the input and output signals, as shown j

8.4.

Mo

v 7

Vee

Re

¥ .

ol 7

Figure 8.4 Demonstrating

180° phase shift between

and output waveforms

Effect of r,: Including r, in the output circuit of Fig. 8.3 will result in the

network of Fig. 8.5. Z; will remain the same but Z, is now defined by

However, r, is typically so much larger than Re that Eq. (8.3) can often be

with a high degree of accuracy. In fact, if we assume that r,l|Rc = Ro, the equ

for A, and A; are unaffected. If r, must be included, the voltage gain is now

To determine A;, the current gain, 1, of Fig. 8.5, is first determined by the

divider rule:

Tolga NOs BIN

To + Re Ty to + Re

he

Chapter 8 BJT Small-Signal Analysis

and the current gain

and Ae (8.8)

For the network of Fig, 8.6 EXAMPLE 8.1

(a) Determine r,.

(b) Find Z; (with r, = 2 ©),

(©) Calculate Z, (with r, = 9).

(d) Determine A, (with r, OD).

(e) Find A; (with r, = » 0).

(f) Repeat parts (c) through (e) including r, = 50 kQ in all calculations and compare

results.

Figure 8.6 Example 8.1

Solution

(a) De analysis:

— Veo = Var _ 12V=0.1V

Ra 470 KO.

Tp = (B+ ly = (101)(24.04 pA) =

= 24.04 pA

Z; = Rpl|Br. = 470 kO)|1.071 kOQ = 1.069 kQ

(©) Z, = Ro = 3kO

Re ___3kO

r 10.710

= 100

role = 50 kO||3 kO = 2.83 kO vs. 3 kQ

rllRe _ 2.83 kO

arnt 10 71

roB — _ (50 kQ)C100)

ret Re S0KD+ 3 KO

= = 280.11

he

264.24 vs, —280.11

= 94.34 vs. 100

8.2 Common-Emitter Fixed:Bias ‘Configuration 339

8.3 VOLTAGE-DIVIDER BIAS

The next configuration to be analyzed is the voltage-divider bias network of

Recall that the name of the configuration is a result of the voltage-divider

input side to determine the de level of Vy.

Figure 8.7 Volagedivi

configuration

Substituting the r, equivalent circuit will result in the network of Fig. 8:

the absence of Rr duc to the low-impedance shorting effect of the bypass

Ce. That is, at the frequency (or frequencies) of operation, the reactance

capacitor is so small compared to Ry that it is treated as a short circuit

When Vcc is set to zero it places one end of R, and Re at ground potential as

Fig. 8.8. In addition, note that R, and Ry remain part of the input circuit while

part of the output circuit, The parallel combination of R, and Rp is

oy ee

RR =p |

Rit Re

R

From Fig. 8.8,

Dy

From Fig. 8.8,

Chapter 8 BJT Small-Signal Analysis

Vo = —loRe = —BlyRe

-a( +) re

and (8.12)

Ag Since the resistance R' is often too close in magnitude to Br, to be ignored,

the effect of R’ should be included in the current gain equation. Referencing Fig. 8.8,

we have

RIL

Ip = Rt pr (current-divider rule)

Be cop eae

i R+ Bre

For the output side,

or

The current gain

and, (8.13)

Phase relationship: The negative sign of Eq. (8.12) reveals a 180° phase shift

between V, and V;

Effect of r,: If r, is included, the output circuit will have the same appearance as

Fig. 8.5. The input impedance is unaffected and

alle (8.14)

For the voltage gain,

Rellro

te

(8.15)

For the current gain the following equation was derived from Fig. 8.5:

i, ne

Th to +Re

83. Voltage-Divider Bias 341

while the following was derived for this configuration:

ty

Using the fact that

we have

‘The complexity of Eq. (8.16) suggests that we return fo an equation such

(7.10) which utilizes the above results. That is,

EXAMPLE 8.2 For the network of Fig. 8.9, determine:

@) Fe

() Z.

© Z,.

@) A).

(©) Ai.

(£) The parameters of parts (b) through (€) if ry = 1/Aye = 50 kO and comy

sults.

Solution

(a) DC: Testing BR: > 10 Ro

(90)(1.5 kQ) > 10(8.2 kA)

135 KO > 82 KO satisfied

342 ‘Chapter 8 BJT Small-Signal Analysis

Вам также может понравиться

- Chapter 2: Avr Architecture & Assembly Language Programming: Section 2.1: The General Purpose Registers in The AvrДокумент8 страницChapter 2: Avr Architecture & Assembly Language Programming: Section 2.1: The General Purpose Registers in The AvrOsama MalikОценок пока нет

- Chapter 11 Part 4 Multistage Amplifier - Sem1 1617Документ9 страницChapter 11 Part 4 Multistage Amplifier - Sem1 1617Yue KaiОценок пока нет

- Modern Control Project FinalДокумент45 страницModern Control Project Finalyohannes100% (1)

- ProblemsAC FundamentalsДокумент3 страницыProblemsAC Fundamentalskrishneel100% (1)

- HW 6Документ3 страницыHW 6Miles GrubbsОценок пока нет

- Homework Assignment 7 SolutionДокумент7 страницHomework Assignment 7 SolutionKL Chiang0% (1)

- Lab1 VHDLДокумент9 страницLab1 VHDLGautam GowdaОценок пока нет

- Network Analysis and Synthesis QBДокумент11 страницNetwork Analysis and Synthesis QBGowthamОценок пока нет

- Lab Report 4Документ10 страницLab Report 4abdulbabulОценок пока нет

- Signals and Systems - MjrobertsДокумент3 страницыSignals and Systems - Mjrobertspriyakanthr5883100% (1)

- Clase 17 Diseño Por Medio Del LGR PIDДокумент46 страницClase 17 Diseño Por Medio Del LGR PIDCristhian RamosОценок пока нет

- EE 311 Final Exam SolutionsДокумент15 страницEE 311 Final Exam SolutionsamjadakramОценок пока нет

- Bài Tập Tuần 1 Và 2Документ4 страницыBài Tập Tuần 1 Và 2Ƭhôngßáo MesseƞgerОценок пока нет

- Electrical and Electronics Lab Manual For Mechanical EngineeringДокумент21 страницаElectrical and Electronics Lab Manual For Mechanical EngineeringSreerag Kunnathu SugathanОценок пока нет

- Generation of Complex ExponentialДокумент5 страницGeneration of Complex Exponentialirum jafriОценок пока нет

- RP Jain Adc DacДокумент27 страницRP Jain Adc DacAnand SinghОценок пока нет

- Questions On Small Signal Model of AmpДокумент2 страницыQuestions On Small Signal Model of AmpdevsrivastavaОценок пока нет

- EC 6302 2-Marks and 16 Marks QuestionsДокумент12 страницEC 6302 2-Marks and 16 Marks QuestionsskaruppaiaheceОценок пока нет

- Intro To BJT Small SignalДокумент35 страницIntro To BJT Small SignalVallestero SiegfredОценок пока нет

- Clipper Clamper CircuitsДокумент15 страницClipper Clamper CircuitsAnilaSaghirОценок пока нет

- Assignment2 SolutionДокумент22 страницыAssignment2 Solutionyamen.nasser7Оценок пока нет

- SEEA1301Документ137 страницSEEA1301Chintapalli Ramesh KumarОценок пока нет

- Chapter 3: Ac Power AnalysisДокумент40 страницChapter 3: Ac Power AnalysisAtyia Javed100% (1)

- 1semexam 2015Документ185 страниц1semexam 2015Cham Raul100% (1)

- EDC - Old Question Papers For Unit 3, 4, 5Документ19 страницEDC - Old Question Papers For Unit 3, 4, 5Deepak SahuОценок пока нет

- Exp4 (Study of DSB-SC Demodulation)Документ4 страницыExp4 (Study of DSB-SC Demodulation)TA TiusОценок пока нет

- Assignment 1Документ2 страницыAssignment 1kartik0% (1)

- Huawei AR2200 SeriesДокумент2 страницыHuawei AR2200 SeriesComptest Polska Sp z o oОценок пока нет

- AC DC Analysis BJT Diffrential Amp PDFДокумент8 страницAC DC Analysis BJT Diffrential Amp PDFtanishk jainОценок пока нет

- Ec8361-Adc Lab ManualДокумент118 страницEc8361-Adc Lab ManualmuminthajОценок пока нет

- Sheet 3Документ3 страницыSheet 3Mohab SamehОценок пока нет

- Gate 1991 EeДокумент15 страницGate 1991 EeParayatham ManasaОценок пока нет

- Multisim 10 Component Reference GuideДокумент450 страницMultisim 10 Component Reference Guideredoctober24100% (2)

- Small Signal Model MOSFETДокумент8 страницSmall Signal Model MOSFETRAHUL100% (1)

- Chapter 1 Micro Electronics Circuit NotesДокумент59 страницChapter 1 Micro Electronics Circuit NotesswamySLR100% (1)

- PART IV. Instrument TransformersДокумент30 страницPART IV. Instrument TransformersuplbselesОценок пока нет

- M2 (6) The DC Shunt Motor REPORT FinalДокумент9 страницM2 (6) The DC Shunt Motor REPORT FinalEric CalejaОценок пока нет

- Polyphase System QUESTIONДокумент5 страницPolyphase System QUESTIONmaruf048Оценок пока нет

- Assignment 4Документ9 страницAssignment 4Salil ChourasiaОценок пока нет

- Solution Sheet 2 Electronic CircuitsДокумент15 страницSolution Sheet 2 Electronic CircuitsWajdi BELLILОценок пока нет

- Digital 16 Marks.Документ4 страницыDigital 16 Marks.Saranya PrabhuОценок пока нет

- Voltage Regulator (FINAL)Документ33 страницыVoltage Regulator (FINAL)usama khattakОценок пока нет

- Cmps Paper Objective PaperДокумент27 страницCmps Paper Objective PaperJeetu Bhardwaj0% (2)

- LOGIC - CIRCUITS Final Exam Q2 2010 - 2011 Problems and Answer KeyДокумент2 страницыLOGIC - CIRCUITS Final Exam Q2 2010 - 2011 Problems and Answer KeySimon Gregory Mabanta100% (1)

- Linear Integrated Circuits NotesДокумент53 страницыLinear Integrated Circuits NotesSudershan DolliОценок пока нет

- Hopkinson Test On DC Shunt MotorДокумент5 страницHopkinson Test On DC Shunt MotorVarun VadluriОценок пока нет

- BJT Amplifier Sheet: Figure 1: Problem 1Документ3 страницыBJT Amplifier Sheet: Figure 1: Problem 1Ali AhmedОценок пока нет

- Electrical Engineering Lab ReportДокумент7 страницElectrical Engineering Lab ReportFrancis Paul SantiagoОценок пока нет

- Capacitor Input FilterДокумент2 страницыCapacitor Input FilterAgbarakwe IkechukwuОценок пока нет

- Magnitude ComparatorДокумент15 страницMagnitude ComparatorJeterine AriasОценок пока нет

- Electronic System Design PPT - Electrical Behavior of CMOS and BiCMOSДокумент6 страницElectronic System Design PPT - Electrical Behavior of CMOS and BiCMOSAnoop MathewОценок пока нет

- DC-DC ConvertersДокумент30 страницDC-DC ConvertersTema HassanОценок пока нет

- 5Документ100 страниц5arvind pandeyОценок пока нет

- Electronics Lab Manual Bipolar Junction TransistorДокумент16 страницElectronics Lab Manual Bipolar Junction Transistormyxomatosis33Оценок пока нет

- Edc 7Документ8 страницEdc 729viswa12100% (1)

- II B.Tech II Semester, Regular Examinations, April - 2012 Electrical Circuit Analysis - IiДокумент8 страницII B.Tech II Semester, Regular Examinations, April - 2012 Electrical Circuit Analysis - IiViswa ChaitanyaОценок пока нет

- 5 EE 2151 - Circuit TheoryДокумент4 страницы5 EE 2151 - Circuit TheoryBIBIN CHIDAMBARANATHANОценок пока нет

- Edc 3Документ10 страницEdc 329viswa12Оценок пока нет

- EDC Question-Papers Complete SetДокумент13 страницEDC Question-Papers Complete Setselvi04120% (1)

- Question Paper Code:: Reg. No.Документ0 страницQuestion Paper Code:: Reg. No.aishuvc1822Оценок пока нет

- A1 8051 Interfacing and ApplicationsДокумент78 страницA1 8051 Interfacing and Applicationscinematic3006Оценок пока нет

- Catalog Optocuploare - Temic 1996Документ77 страницCatalog Optocuploare - Temic 1996Borcan CristiОценок пока нет

- Monitor LCD IBM Model-T56AДокумент42 страницыMonitor LCD IBM Model-T56Acinematic3006Оценок пока нет

- Monitor LCD Sharp Model-Va550Документ4 страницыMonitor LCD Sharp Model-Va550cinematic3006Оценок пока нет

- 6 Electrical Parts ListДокумент10 страниц6 Electrical Parts Listcinematic3006Оценок пока нет

- 8 Diagram WiringДокумент2 страницы8 Diagram Wiringcinematic3006Оценок пока нет

- Service: ManualДокумент2 страницыService: Manualcinematic3006Оценок пока нет

- CopyrightДокумент1 страницаCopyrightcinematic3006Оценок пока нет

- Color Monitor: Service ManualДокумент34 страницыColor Monitor: Service Manualcinematic30060% (1)

- 5 Exploded ViewДокумент2 страницы5 Exploded Viewcinematic3006Оценок пока нет

- 9 Schematic Diagrams: 9-1 Scaler Part Schematic DiagramДокумент6 страниц9 Schematic Diagrams: 9-1 Scaler Part Schematic Diagramcinematic3006Оценок пока нет

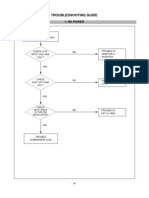

- Troubleshooting Guide: 1. No PowerДокумент6 страницTroubleshooting Guide: 1. No Powercinematic3006Оценок пока нет

- Monitor AOC Mod LM729 Manual de Servià oДокумент61 страницаMonitor AOC Mod LM729 Manual de Servià oapi-3703813100% (2)

- LS882C 2Документ1 страницаLS882C 2cinematic3006Оценок пока нет

- Schematic Diagram: 1. Input SwitchingДокумент10 страницSchematic Diagram: 1. Input Switchingcinematic3006Оценок пока нет

- Exploded View Parts ListДокумент1 страницаExploded View Parts Listcinematic3006Оценок пока нет

- LS882C 10Документ2 страницыLS882C 10cinematic3006Оценок пока нет

- Service Manual: Xga Color Monitor Model: L510B1Документ36 страницService Manual: Xga Color Monitor Model: L510B1cinematic3006Оценок пока нет

- Schematic Diagram: 1. TDA8752 (PRE-AMP/PLL/ADC)Документ7 страницSchematic Diagram: 1. TDA8752 (PRE-AMP/PLL/ADC)cinematic3006Оценок пока нет

- LS882C 6BДокумент2 страницыLS882C 6Bcinematic3006Оценок пока нет

- Lm568e 2Документ1 страницаLm568e 2cinematic3006Оценок пока нет

- Schematic Diagram: 1. GMZAN1Документ7 страницSchematic Diagram: 1. GMZAN1cinematic3006Оценок пока нет

- Lm568e 6 (1) .BДокумент2 страницыLm568e 6 (1) .Bcinematic3006Оценок пока нет

- Troubleshooting Guide: 1. No PowerДокумент5 страницTroubleshooting Guide: 1. No Powercinematic3006Оценок пока нет

- Exploded View Parts ListДокумент1 страницаExploded View Parts Listcinematic3006Оценок пока нет

- Lm568e 4Документ1 страницаLm568e 4cinematic3006Оценок пока нет

- Lm568e 1Документ1 страницаLm568e 1cinematic3006Оценок пока нет

- Manual C2 4000 SeriesДокумент108 страницManual C2 4000 Seriescinematic3006Оценок пока нет

- LCD Video ControllerДокумент8 страницLCD Video Controllercinematic3006Оценок пока нет

- Theory Board MCU 1Документ5 страницTheory Board MCU 1cinematic3006Оценок пока нет