Академический Документы

Профессиональный Документы

Культура Документы

Ex1 Ch5

Загружено:

haimstИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Ex1 Ch5

Загружено:

haimstАвторское право:

Доступные форматы

ארכיטקטורת מחשבים

1 תרגיל מספר

ד"ר כרמי מרימוביץ

ד"ר אלון שקלר

Question 1

Explain why each of the following microoperations cannot be executed during a single clock pulse in the

system shown in Fig. 5-4. Specify a sequence of microoperations that will perform the operation.

1. IR ← M[PC]

2. AC ← AC + TR

3. DR ← DR + AC (AC does not change)

Question 2

Make the following changes to the basic computer.

1. Add a register to the bus system CTR (count register) to be selected with S2S1S0 = 000.

2. Replace the ISZ instruction with an instruction that loads a number into CTR.

LDC Address CTR ← M[Address]

3. Implement the LDC instruction by a minimal set of micro-operations

4. Add a register reference instruction ICSZ: Increment CTR and skip next instruction if zero.

5. Implement the ICSZ instruction by a minimal set of micro-operations

6. Discuss the advantage of this change.

Question 3

The operations to be performed with a flip-flop F (not used in the basic computer) are specified by the

following register transfer statements:

xT3: F ← l Set F to 1

yT1: F ← 0 Clear F to 0

zT2: F ← F' Complement F

wT5: F ← G Transfer value of G to F

Otherwise, the content of F must not change. Draw the logic diagram showing the connections of the gates

that form the control functions and the inputs of flip-flop F. Use a JK flip-flop and minimize the number of

gates.

Question 4

The memory unit of the basic computer shown in Fig. 5-3 is to be changed to a 65,536 x 16 memory,

requiring an address of 16 bits. The instruction format of a memory-reference instruction shown in Fig. 5-

5(a) remains the same for I = 1 (indirect address) with the address part of the instruction residing in

positions 0 through 11. But when I = 0 (direct address), the address of the instruction is given by the 16 bits

in the next word following the instruction. Modify the microoperations during time T2, T3, (and T4 if

necessary) to conform with this configuration.

Question 5

Derive the Boolean expression for the gate structure that clears the sequence counter SC to 0. Draw the

logic diagram of the gates and show how the output is connected to the INR and CLR inputs of SC (see Fig.

5-6). Minimize the number of gates.

rd

All questions are taken from Chapter 5 in M. Mano/Computer Design and Architecture 3 Ed.

Вам также может понравиться

- Computer Applications and ManagementДокумент11 страницComputer Applications and ManagementParag PaliwalОценок пока нет

- COA Assignment - 3Документ2 страницыCOA Assignment - 3KomalОценок пока нет

- Final Apr 03 SolnsДокумент16 страницFinal Apr 03 Solnsapi-3755462Оценок пока нет

- Csa 2022Документ6 страницCsa 2022Jha StockesОценок пока нет

- CA Assignment IIДокумент9 страницCA Assignment IISomesh ThakurОценок пока нет

- COA QuestionBank - 1Документ3 страницыCOA QuestionBank - 1itzzsandeshОценок пока нет

- BEE (Electronics) Assignment 2 QPДокумент1 страницаBEE (Electronics) Assignment 2 QPbala krishnaОценок пока нет

- Tutorial Module 4Документ9 страницTutorial Module 4Neupane Er KrishnaОценок пока нет

- Individual Assignment QuestionsДокумент3 страницыIndividual Assignment QuestionsGemechisОценок пока нет

- Mock Exams Q1Документ3 страницыMock Exams Q1Sophia JardelezaОценок пока нет

- E6995ca TutДокумент14 страницE6995ca Tutrabinoss0% (1)

- S.V. National Institute of Technology, Surat: EC306: Embedded SystemsДокумент2 страницыS.V. National Institute of Technology, Surat: EC306: Embedded SystemsBittu GoswamiОценок пока нет

- Fallsem2012-13 CP0194 Cat02ansДокумент2 страницыFallsem2012-13 CP0194 Cat02ansChaitanya MsskОценок пока нет

- SLR-N - 331: T.E. (Electronics and Telecommunication) (Part - II) Examination, 2009 MicrocontrollersДокумент2 страницыSLR-N - 331: T.E. (Electronics and Telecommunication) (Part - II) Examination, 2009 Microcontrollersaksaltaf9137Оценок пока нет

- Roll No TCS 402/TIT 402: Time: Two (2) Hrs. Maximum Marks: 60Документ18 страницRoll No TCS 402/TIT 402: Time: Two (2) Hrs. Maximum Marks: 60Obsii ChalaОценок пока нет

- Computer Organization and Design 2010Документ2 страницыComputer Organization and Design 2010Stanly KurianОценок пока нет

- DLD Question BankДокумент5 страницDLD Question BankHarshad ThiteОценок пока нет

- Deld QB EndsemДокумент4 страницыDeld QB EndsemUV New MoviesОценок пока нет

- 21CS34 SIMP Questions - 21SCHEME: Module-1 (Study Any 5 Questions)Документ4 страницы21CS34 SIMP Questions - 21SCHEME: Module-1 (Study Any 5 Questions)Rohan RОценок пока нет

- NVIDIA QuestionsДокумент5 страницNVIDIA QuestionsJibin P John0% (1)

- DDCO UPDATED QUESTION BANKttttДокумент4 страницыDDCO UPDATED QUESTION BANKttttbrahmareddy.22iseОценок пока нет

- CSE 331 - Final - Assignment - v2Документ5 страницCSE 331 - Final - Assignment - v2S.M. Imam Jahed Hossain 1511500642Оценок пока нет

- 15 151001 Microcontroller and InterfacingДокумент1 страница15 151001 Microcontroller and InterfacingManthan PandyaОценок пока нет

- Digital Logic Design and Microprocessor 2Документ4 страницыDigital Logic Design and Microprocessor 2Aditya VibhuteОценок пока нет

- Your Name:: Final ExamДокумент9 страницYour Name:: Final ExamDaniel EcheverriaОценок пока нет

- Question Bank: Ec6302 Digital ElectronicsДокумент14 страницQuestion Bank: Ec6302 Digital ElectronicsBarry SmithОценок пока нет

- Solution To Assignments For BScCSIT 3rd Semester (2069)Документ8 страницSolution To Assignments For BScCSIT 3rd Semester (2069)Bijay MishraОценок пока нет

- Model QPДокумент6 страницModel QPvlsisivaОценок пока нет

- DLD GTU Question Bank: Chapter-1 Binary SystemДокумент5 страницDLD GTU Question Bank: Chapter-1 Binary Systemnirav34Оценок пока нет

- DLD GTU Question Bank: Chapter-1 Binary SystemДокумент129 страницDLD GTU Question Bank: Chapter-1 Binary Systemnirav34Оценок пока нет

- Assignments For BScCSIT 3rd Semester (2069)Документ2 страницыAssignments For BScCSIT 3rd Semester (2069)jijibishamishraОценок пока нет

- MTech QBДокумент2 страницыMTech QBRaj Kumar SinghОценок пока нет

- Must Also Perform The Necessary Arithmetic Using Signed 2's Complement Notation and Show The Results Indicating Overflow, If AnyДокумент18 страницMust Also Perform The Necessary Arithmetic Using Signed 2's Complement Notation and Show The Results Indicating Overflow, If AnyramkumarОценок пока нет

- Summer2022 AnnotatedДокумент4 страницыSummer2022 AnnotatedSarojkumar BhosleОценок пока нет

- April 2005 WithsloutionДокумент21 страницаApril 2005 Withsloutionapi-3755462Оценок пока нет

- DSP Unit 1 To 5 QBДокумент12 страницDSP Unit 1 To 5 QBSamuel WhiteОценок пока нет

- D.J. College of Engineering & Technology, ModinagarДокумент2 страницыD.J. College of Engineering & Technology, ModinagarjavedynОценок пока нет

- Digital Electronics CSEДокумент2 страницыDigital Electronics CSEcihalab698Оценок пока нет

- Caassgnsem 1Документ12 страницCaassgnsem 1Sunil GawaskerОценок пока нет

- 2019 20 COA Mid PaperДокумент2 страницы2019 20 COA Mid PaperDoraemon हिंदीОценок пока нет

- EE6301 QB FinalДокумент21 страницаEE6301 QB FinallithijanarОценок пока нет

- Homework 2Документ2 страницыHomework 2Friona PoçariОценок пока нет

- Computer Architecture-QBANKДокумент13 страницComputer Architecture-QBANKjascnj100% (1)

- Quiz 1 Solutions CS252 Graduate Computer ArchitectureДокумент12 страницQuiz 1 Solutions CS252 Graduate Computer Architectureadchy7Оценок пока нет

- Me 1Документ436 страницMe 1Akshay Mane0% (1)

- EC 6302 2-Marks and 16 Marks QuestionsДокумент12 страницEC 6302 2-Marks and 16 Marks QuestionsskaruppaiaheceОценок пока нет

- Itpc 29 Mid Term-IДокумент3 страницыItpc 29 Mid Term-IRahul YadavОценок пока нет

- Computer Organisation and ArchitectureДокумент2 страницыComputer Organisation and ArchitectureSelin DandpatОценок пока нет

- Dem QB Ut-1 110120Документ2 страницыDem QB Ut-1 110120ABHI THORATОценок пока нет

- CSA Test PaperДокумент65 страницCSA Test Paperhimanshumis2022Оценок пока нет

- Electrical Engineering Department Academic SessionДокумент17 страницElectrical Engineering Department Academic SessionShavitra 30Оценок пока нет

- Question Bank of Unit-III COAДокумент4 страницыQuestion Bank of Unit-III COAYamini BishtОценок пока нет

- Ee6008 Fiat QBДокумент2 страницыEe6008 Fiat QBAthithyaОценок пока нет

- Ee6008 Fiat QBДокумент2 страницыEe6008 Fiat QBAthithyaОценок пока нет

- ECET 340 CART Expect Success Ecet340cartdotcomДокумент17 страницECET 340 CART Expect Success Ecet340cartdotcommadelyan86Оценок пока нет

- Unit - IДокумент2 страницыUnit - IPranathi NimmuОценок пока нет

- Ec2203 Digital ElectronicsДокумент8 страницEc2203 Digital ElectronicspappujayaОценок пока нет

- Mathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsОт EverandMathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsRoderick MelnikОценок пока нет

- Programmable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysОт EverandProgrammable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysОценок пока нет

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationОт EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationОценок пока нет

- OFV-5000 Vibrometer Controller: Measuring VibrationsДокумент4 страницыOFV-5000 Vibrometer Controller: Measuring VibrationsvnetawzОценок пока нет

- EE251 Notes1 - Short Circuit CalculationsДокумент61 страницаEE251 Notes1 - Short Circuit CalculationsPrime MoverОценок пока нет

- Panasonic Sa En28Документ19 страницPanasonic Sa En28boroda2410Оценок пока нет

- Wollo UniversityДокумент13 страницWollo UniversitySISAy AyalewОценок пока нет

- AC Hipots 15-200kVДокумент4 страницыAC Hipots 15-200kVHung NguyenОценок пока нет

- Plasma Antenna: A Seminar Presentation ONДокумент16 страницPlasma Antenna: A Seminar Presentation ONbalu54Оценок пока нет

- 1720D/L Low Range Process Turbidimeter ManualДокумент102 страницы1720D/L Low Range Process Turbidimeter ManualHamed YadegariОценок пока нет

- Protection Instrument TransformersДокумент21 страницаProtection Instrument TransformersSyed Muzammil AliОценок пока нет

- 7485658-Pioneer Pdp-R06u Pro-R06u Media Receiver Service ManualДокумент104 страницы7485658-Pioneer Pdp-R06u Pro-R06u Media Receiver Service ManualChicagos PoolhallОценок пока нет

- Literature Review On Gifi TechnologyДокумент6 страницLiterature Review On Gifi Technologyzyfofohab0p2100% (1)

- 42LS3450, 345S, 345TДокумент53 страницы42LS3450, 345S, 345TAndres Fermin OchoaОценок пока нет

- O Plus Dry Bushings - Technical GuideДокумент16 страницO Plus Dry Bushings - Technical GuidePABLO BELTRANОценок пока нет

- Multilayer Ceramic CapacitorsДокумент12 страницMultilayer Ceramic CapacitorscostpopОценок пока нет

- Wistron GodzillaДокумент61 страницаWistron Godzillarodrigootavio5Оценок пока нет

- 873P Ultrasonic Sensors With Dual Discrete/Single Analog OutputsДокумент4 страницы873P Ultrasonic Sensors With Dual Discrete/Single Analog Outputsmanduca matthewОценок пока нет

- Chapter 4 - Synchronous GeneratorsДокумент21 страницаChapter 4 - Synchronous GeneratorsnehmeОценок пока нет

- Ts 590sg Idm OkДокумент76 страницTs 590sg Idm OkLoco Soy Loco SoyОценок пока нет

- m1 2006Документ4 страницыm1 2006spoof183Оценок пока нет

- System Verilog Basic Introduction && Assertions: Presenter - Suman HalderДокумент18 страницSystem Verilog Basic Introduction && Assertions: Presenter - Suman HalderSuman HalderОценок пока нет

- NEC Table 220.19Документ2 страницыNEC Table 220.19Anderson GohОценок пока нет

- Electrical Principles Peter Phillips Full ChapterДокумент51 страницаElectrical Principles Peter Phillips Full Chaptertami.cobb436100% (5)

- Pratt & Whitney Ft4 Three Shaft Gas Turbine Generator Drive Application Control PackageДокумент3 страницыPratt & Whitney Ft4 Three Shaft Gas Turbine Generator Drive Application Control PackageJose Medina AnguloОценок пока нет

- Dynamic Testing of Machines and StructuresДокумент13 страницDynamic Testing of Machines and Structuresjjiitthhiinn0% (1)

- Digital ElectronicsДокумент20 страницDigital Electronics1balamanianОценок пока нет

- Manual Partes Millermatic 350Документ43 страницыManual Partes Millermatic 350Miguel Angel Pavon CarbonellОценок пока нет

- Honeywell XNX Data SheetДокумент5 страницHoneywell XNX Data SheetpОценок пока нет

- Etap PDFДокумент2 страницыEtap PDFAmandaОценок пока нет

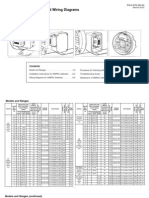

- Installation Instructions and Wiring Diagrams For All Models and RangesДокумент8 страницInstallation Instructions and Wiring Diagrams For All Models and RangesMaria MusyОценок пока нет

- Digital Signal Processing (EE-394) : Practical Work BookДокумент13 страницDigital Signal Processing (EE-394) : Practical Work BookHermain Fayyaz KarimОценок пока нет

- DB224-E Product SpecificationsДокумент2 страницыDB224-E Product SpecificationsTo VT3Оценок пока нет