Академический Документы

Профессиональный Документы

Культура Документы

Tecnología CMOS

Загружено:

api-3762100100%(2)100% нашли этот документ полезным (2 голоса)

14K просмотров6 страницАвторское право

© Attribution Non-Commercial (BY-NC)

Доступные форматы

DOC, PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Attribution Non-Commercial (BY-NC)

Доступные форматы

Скачайте в формате DOC, PDF, TXT или читайте онлайн в Scribd

100%(2)100% нашли этот документ полезным (2 голоса)

14K просмотров6 страницTecnología CMOS

Загружено:

api-3762100Авторское право:

Attribution Non-Commercial (BY-NC)

Доступные форматы

Скачайте в формате DOC, PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 6

Tecnología CMOS

Un inversor en tecnología CMOS

CMOS (del inglés Complementary Metal Oxide Semiconductor, "Metal Óxido

Semiconductor Complementario") es una de las familias lógicas empleadas

en la fabricación de circuitos integrados (chips). Su principal característica

consiste en la utilización de conjunta de transistores de tipo pMOS y tipo

nMOS configurados de tal forma que, en estado de reposo, el consumo de

energía es únicamente el debido a las corrientes parásitas.

En la actualidad, la inmensa mayoría de los circuitos integrados que se

fabrican son de tecnología CMOS. Esto incluye microprocesadores,

memorias, DSPs y muchos otros tipos de chips digitales.

Tabla de contenidos

[ocultar]

1 Principio de funcionamiento

2 Ventajas e inconvenientes

3 Historia

4 CMOS analógicos

5 CMOS y Bipolar

6 Enlaces externos

Principio de funcionamiento editar]

[

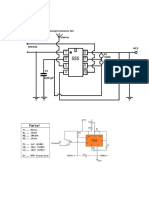

Inversor estático CMOS

En un circuito CMOS, la función lógica a sintetizar se implementa por

duplicado mediante dos circuitos: uno basado exclusivamente en

transistores pMOS, y otro basado exclusivamente en transistores nMOS. El

circuito pMOS es empleado para propagar el valor binario 1 , y el circuito

nMOS para propagar el valor binario 0. Véase la figura. Representa una

puerta lógica NOT o inversor.

Cuando la entrada es 1, el transistor nMOS está en estado de

conducción. Al estar su fuente conectada a tierra (0), el valor 0 se

propaga al drenador y por tanto a la salida de la puerta lógica. El

transisor pMOS, por contra, está en estado de no conducción

Cuando la entrada es 0, el transistor pMOS está en estado de

conducción. Al estar su fuente conectada a la alimentación (1), el valor 1

se propaga al drenador y por tanto a la salida de la puerta lógica. El

transisor nMOS, por contra, está en estado de no conducción.

Otra de las características importantes de los circuitos CMOS es que son

regenerativos: una señal degradada que acometa una puerta lógica CMOS

se verá restaurada a su valor lógico inicial 0 o 1, siempre y cuando aún esté

dentro de los márgenes de ruido.

Ventajas e inconvenientes [editar]

La familia lógica tiene una serie de ventajas que la hacen superior a otras

en la fabricación de circuitos integrados digitales:

El bajo consumo de potencia, gracias a la alta impedancia de entrada de

los transistores de tipo MOSFET y a que, en estado de reposo, un

circuito CMOS sólo experimentará corrientes parásitas.

Gracias a su carácter regenerativo, los circuitos CMOS son robustos

frente a ruido o degradación de señal debido a la impedancia del metal

de interconexión.

Los circuitos CMOS son sencillos de diseñar.

La tecnología de fabricación está muy desarrollada, y es posible

conseguir densidades de integración muy altas a un precio mucho menor

que otras tecnologías

Algunos de los inconvenientes son los siguientes:

Debido al carácter capacitivo de los transistores MOSFET, y al hecho de

que estos son empleados por duplicado en parejas nMOS-pMOS, la

velocidad de los circuitos CMOS es comparativamente menor que la de

otras familias lógicas.

Son vulnerables a latch-up: Consiste en la existencia de un tiristor

parásito en la estructura CMOS que entra en conducción cuando la

salida supera la alimentación. Esto se produce con relativa facilidad

debido a la componente inductiva de la red de alimentación de los

circuitos integrados. El latch-up produce un camino de baja resistencia a

la corriente de alimentación que acarrea la destrucción del dispositivo.

Siguiendo las técnicas de diseño adecuadas este riesgo es

practicamente nulo. Generalmente es suficiente con espaciar contactos

de sustrato y pozos de difusión con suficiente regularidad, para

asegurarse de que está sólidamente conectado a masa o alimentación.

Según se va reduciendo el tamaño de los transistores, las corrientes

parásitas empiezan a ser comparables a las corrientes dinámicas

(debidas a la conmutación de los dispositivos).

Historia editar]

[

La tecnología CMOS fue desarrollada por Wanlass y Sah, de Fairchild

Semiconductor, a principios de los años 60. Sin embargo, su introducción

comercial se debe a RCA, con su famosa familia lógica CD4000.

Posteriormente, la introducción de un búfer y mejoras en el proceso de

oxidación local condujeron a la introducción de la serie 4000B, de gran éxito

debido a su bajo consumo (prácticamente cero, en condiciones estáticas) y

gran margen de alimentación (de 3 a 18 V). RCA también fabricó LSI en

esta tecnología, como su familia COSMAC de amplia aceptación en

determinados sectores, a pesar de ser un producto caro, debido a la mayor

dificultad de fabricación frente a dispositivos nmos.

Pero su talón de Aquiles consistía en su reducida velocidad. Cuando se

aumenta la frecuencia de reloj, su consumo sube proporcionalmente,

haciéndose mayor que el de otras tecnologías. Esto se debe a dos factores:

La capacidad MOS, intrínseca a los transistores MOS, y

La utilización de mos de canal P, más lentos que los de canal N, por ser

la movilidad de los huecos menor que la de los electrones.

El otro factor negativo era la complejidad que conlleva el fabricar los dos

tipos de transistores, que obliga a utilizar un mayor número de máscaras.

Por estos motivos, a comienzos de los 80, algunos autores pronosticaban el

final de la tecnología cmos, que sería sustituida por la novedosa I2L,

entonces prometedora.

Esta fue la situación durante una década, para, en los ochenta, cambia el

escenario rápidamente:

Por un lado, las mejoras en los materiales, técnicas de litografía y

fabricación, permitían reducir el tamaño de los transistores, con lo que la

capacidad mos resultaba cada vez menor.

Por otro, la integración de dispositivos cada vez más complejos obligaba

a la introducción de un mayor número de máscaras para asegurar el

aislamiento entre transistores, de modo que no era más difícil la

fabricación de cmos que de nmos.

En este momento empezó un eclosión de memorias cmos, pasando de

256x4 bits de la 5101 a 2kx8 de la 6116 y 8Kx8 en la 6264, superando, tanto

en capacidad como consumo reducido y velocidad a sus contrapartidas

nmos. También los microprocesadores, nmos hasta la fecha, comenzaron a

aparecer en versiones cmos (80C85, 80C88, 65C02...).

Y aparecieron nuevas familias lógicas, HC y HCT en competencia directa

con la TTL-LS, dominadora del sector digital hasta el momento.

Para entender la velocidad de estos nuevos cmos, hay que considerar la

arquitectura de los circuitos nmos:

Uso de cargas activas. Esto es: un transistor se polariza con otros

transistores y no con resistencias debido al menor tamaño de aquellos.

Además, el transistor mos funciona fácilmente como fuente de corriente

constante. Entonces un inversor se hace conectando el transistor

inversor a la carga activa. Cuando se satura el transistor, drena toda la

corriente de la carga y el nivel da salida baja. Cuando se corta, la carga

activa inyecta cooriente hasta que el nivel de salida sube. Y aquí está el

compromiso: es deseable una corriente pequeña porque reduce la

necesidad de superficie en el silicio (transistores más pequeños) y la

disipación (menor consumo). Pero las transiciones de nivel bajo a nivel

alto se realizan porque la carga activa carga la capacidad mos del

siguiente transistor, además de las capacidades parásitas que existan,

por lo que una corriente elevada es mejor, pues se cargan las

capacidades rápidamente.

Estructuras de almacenamiento dinámicas. La propia capacidad mos

se puede utilizar para retener la información durante cortos periodos de

tiempo. Este medio ahorra transistores frente al biestable estático. Como

la capacidad mos es relativamente pequeña, en esta aplicación hay que

usar transistores grandes y corrientes reducidas, lo que lleva a un

dispositivo lento.

La tecnología cmos mejora estos dos factores:

Elimina la carga activa. La estructura complementaria hace que sólo se

consuma corriente en las transiciones, de modo que el transistor de

canal P puede aportar la corriente necesaria para cargar rápidamente las

capacidades parásitas, con un transistor de canal N más pequeño, de

modo que la célula resulta más pequeña que su contrapartida en nmos.

En cmos se suelen sustituir los registros dinámicos por estáticos, debido

a que así se puede bajar el reloj hasta cero y las reducidas dimensiones

y bajo consumo de la celda cmos ya no hacen tan atractivos los registros

dinámicos.

Por último, se suelen emplear transistores pequeños, poniendo una celda

mayor para la interfaz con las patillas, ya que las necesidades de corriente

son mucho mayores en las líneas de salida del chip.

La disminución del tamaño de los transistores y otras mejoras condujo a

nuevas familias cmos: AC, ACT, ACQ...

CMOS analógicos editar]

[

Los transistores MOS también se emplean en circuitos analógicos, debido a

dos características importantes:

Alta impedancia de entrada: La puerta de un transistor MOS viene a

ser un pequeño condensador, por lo que no existe corriente de

polarización.

Reducida resistencia de canal: Un MOS saturado se comporta como

una resistencia cuyo valor depende de la superficie del transistor. Es

decir, que si se le piden corrientes reducidas, la caída de tensión en el

transistor llega a ser muy reducida.

Estas características posibilitan la fabricación de amplificadores

operacionales "Rail-to-Rail, en los que el margen de la tensión de salida

abarca desde la alimentación negativa a la positiva. También es útil en la

realización de reguladores de tensión "Low-Dropout, filtros de capacidades

conmutadas, etc.

CMOS y Bipolar editar]

[

Se emplean circuitos mixtos bipolar y CMOS tanto en circuitos analógicos

como digitales, en un intento de aprovechar lo mejor de ambas tecnologías.

En el ámbito analógico destaca la tecnología BiCMOS, que permite

mantener la velocidad y precisión de los circuitos bipolares, pero con la alta

impedancia de entrada y márgenes de tensión CMOS. En cuanto a las

familias digitales, la idea es cortar las líneas de corriente entre alimentación

y masa de un circuito bipolar, colocando transistores MOS. Esto debido a

que un transistor bipolar se controla por corriente, mientras que uno MOS,

por tensión.

Вам также может понравиться

- Proyecto Final de Síntesis de Filtros AnalógicosДокумент3 страницыProyecto Final de Síntesis de Filtros AnalógicosrogerОценок пока нет

- Informe Modulacion AMДокумент7 страницInforme Modulacion AMChristian Iannuzzi KunkelОценок пока нет

- P2 Concepto Celular Parte 1Документ49 страницP2 Concepto Celular Parte 1Carlos CarriОценок пока нет

- 17-Reduccion de Estados EquivalentesДокумент7 страниц17-Reduccion de Estados EquivalentesMarcial HsОценок пока нет

- Red GSM Utilizando Open BTSДокумент4 страницыRed GSM Utilizando Open BTSCesar CoronaОценок пока нет

- Sobrecarga de Operadores - ProgramacionДокумент43 страницыSobrecarga de Operadores - Programacionvitevo56Оценок пока нет

- Guía de OndasДокумент2 страницыGuía de OndasMiguel Rodriguez100% (1)

- Estrategias de handoff en comunicaciones móvilesДокумент2 страницыEstrategias de handoff en comunicaciones móvilesKevin Villacis AvelinoОценок пока нет

- Sensores y Transductores2Документ14 страницSensores y Transductores2German RodriguezОценок пока нет

- Filtro en Coseno AlzadoДокумент2 страницыFiltro en Coseno AlzadoNineuk023Оценок пока нет

- Proyecto Final SeñalesДокумент4 страницыProyecto Final SeñalesÄlëJä GiirälDoОценок пока нет

- Problemas resueltos de ondas electromagnéticas y espectro electromagnéticoДокумент2 страницыProblemas resueltos de ondas electromagnéticas y espectro electromagnéticoJavier TGОценок пока нет

- Zona de FresnelДокумент8 страницZona de FresnelEduardo DF7Оценок пока нет

- Banda TransportadoraДокумент14 страницBanda TransportadoraArmand Galvan100% (1)

- Medidor de Potencia RF y Carga Fantasma para menos de 40WДокумент1 страницаMedidor de Potencia RF y Carga Fantasma para menos de 40WMiguel De Los Santos PavisicОценок пока нет

- Unidad 2:: Análisis en Estado Transitorio Y PermanenteДокумент28 страницUnidad 2:: Análisis en Estado Transitorio Y PermanenteNicolas BotelloОценок пока нет

- Especificaciones Tecnicas Sistema VsatДокумент13 страницEspecificaciones Tecnicas Sistema VsatElvis Zi Alaban DiazОценок пока нет

- Codigo Carro BluetoothДокумент3 страницыCodigo Carro BluetoothJhonatan Andres Lamus FigueroaОценок пока нет

- Estructura de Un RobotДокумент3 страницыEstructura de Un RobotDaniel CastroОценок пока нет

- Temporizadores electrónicos ajustablesДокумент13 страницTemporizadores electrónicos ajustablesRoger GaitanОценок пока нет

- ServomotorДокумент3 страницыServomotorJavier RicardoОценок пока нет

- Diodo ImpattДокумент7 страницDiodo ImpattAngel RocabadoОценок пока нет

- TD Práctica1Документ5 страницTD Práctica1Deniel San Keiroz Escemilla MillaguiОценок пока нет

- Tarea 1.2Документ3 страницыTarea 1.2sonomyОценок пока нет

- Arreglos para Accesos Múltiples Al SatéliteДокумент24 страницыArreglos para Accesos Múltiples Al SatéliteFisica 2Оценок пока нет

- Eficiencia Cuántica y Respuesta Espectral (José Campos-Yasuhiro Matsumoto)Документ31 страницаEficiencia Cuántica y Respuesta Espectral (José Campos-Yasuhiro Matsumoto)senseicoroОценок пока нет

- Modelo de propagación Longley-RiceДокумент2 страницыModelo de propagación Longley-Ricefersonvill92100% (1)

- SCRДокумент5 страницSCRWiner Huarhua ChipaoОценок пока нет

- Fundamentos de Electrónica AnálogaДокумент20 страницFundamentos de Electrónica AnálogaAndrey JimenezОценок пока нет

- SEMAFOROДокумент13 страницSEMAFORORonny Roy Villalta LizanaОценок пока нет

- Receptor RakeДокумент5 страницReceptor RakeEduardo RomeroОценок пока нет

- Practica 1 - Unidad 1 Arquitectura de ComputadorasДокумент23 страницыPractica 1 - Unidad 1 Arquitectura de Computadorasjuan pabloОценок пока нет

- T MagicaДокумент9 страницT MagicaMaholy Alejandra100% (1)

- Modulacion de Señales PDFДокумент10 страницModulacion de Señales PDFoscarblanco84Оценок пока нет

- Guia de OndaДокумент4 страницыGuia de OndaDaniel Noriega MezaОценок пока нет

- Cambiadores de FaseДокумент4 страницыCambiadores de FaseKrlos OrtizОценок пока нет

- Tarea VHDLДокумент13 страницTarea VHDLJulio Cesar Romero100% (1)

- G703Документ2 страницыG703ERIK DAVID USSA SOTOОценок пока нет

- 1.2.3 Analisis de Circuitos RLCДокумент3 страницы1.2.3 Analisis de Circuitos RLCLuis Mendoza Lopez0% (1)

- Diseño de transformadores elevador y reductor a escala para equipo de rayos XДокумент4 страницыDiseño de transformadores elevador y reductor a escala para equipo de rayos XNancy QuirogaОценок пока нет

- Conversor DC Ac Con PWMДокумент13 страницConversor DC Ac Con PWMDiego Moreno BasmaОценок пока нет

- Laboratorio - SIMULINK QAM BPSK PDFДокумент15 страницLaboratorio - SIMULINK QAM BPSK PDFLuis LópezОценок пока нет

- Proceso de Comunicación Por Medio de Bus de CampoДокумент10 страницProceso de Comunicación Por Medio de Bus de CampoHermilo López MendozaОценок пока нет

- Ventajas y Desventajas 2.4GHZ VS 5.8GHZДокумент1 страницаVentajas y Desventajas 2.4GHZ VS 5.8GHZRicardo MerizaldeОценок пока нет

- Ej Varicap Zener Con RptasДокумент4 страницыEj Varicap Zener Con RptasluisОценок пока нет

- Circuito EquivalenteДокумент1 страницаCircuito EquivalenteWilliam Cetina100% (1)

- Introduccion MicroondasДокумент2 страницыIntroduccion MicroondasCarlos Enrique Jimenez50% (2)

- Tema MosfetДокумент55 страницTema MosfetOscar ZavaletaОценок пока нет

- Taller 1Документ1 страницаTaller 1david rueda0% (1)

- Reporte Primer ParcialДокумент17 страницReporte Primer ParcialOmar Huerta KananОценок пока нет

- Acondicionamiento de Señal y ProtocolosДокумент6 страницAcondicionamiento de Señal y ProtocolosMalom MarquezОценок пока нет

- Bandas de Frecuencia GSMДокумент4 страницыBandas de Frecuencia GSMDaniel CaballeroОценок пока нет

- FOДокумент5 страницFONixon IsraelОценок пока нет

- Conceptos básicos de control: Introducción a los sistemas de control, tipos de señales y sistemasДокумент12 страницConceptos básicos de control: Introducción a los sistemas de control, tipos de señales y sistemasEugenio PelaezОценок пока нет

- Realice Transmisor AM FMДокумент5 страницRealice Transmisor AM FMFelipe OrtizОценок пока нет

- M.C. Mapa Conceptual ConstructorДокумент6 страницM.C. Mapa Conceptual Constructorfco__2114Оценок пока нет

- Inmunidad Al RuidoДокумент17 страницInmunidad Al RuidoPaul R. ZamudioОценок пока нет

- MODULACION AM y FMДокумент13 страницMODULACION AM y FMFreddyGutierrezОценок пока нет

- Complementary Metal Oxide Semiconductor (JCMOS)Документ7 страницComplementary Metal Oxide Semiconductor (JCMOS)Karina Chavez MoctezumaОценок пока нет

- Semiconductor Complementario de Óxido MetálicoДокумент4 страницыSemiconductor Complementario de Óxido MetálicoRommel LoayzaОценок пока нет

- DSD (Pic 16f84)Документ9 страницDSD (Pic 16f84)api-3762100100% (1)

- Carta DEFДокумент2 страницыCarta DEFapi-3762100Оценок пока нет

- Codigo para El RobotДокумент3 страницыCodigo para El Robotapi-3762100Оценок пока нет

- Derivada ParcialДокумент55 страницDerivada Parcialapi-376210067% (3)

- Visualización de La Página Web FinalizadaДокумент13 страницVisualización de La Página Web Finalizadaapi-3762100100% (1)

- Tare AДокумент1 страницаTare Aapi-3762100Оценок пока нет

- CongresoДокумент6 страницCongresoapi-3762100Оценок пока нет

- Java DecoderДокумент2 страницыJava Decoderapi-3762100100% (1)

- ParábolaДокумент3 страницыParábolaapi-3762100100% (1)

- Historia Del MicroДокумент4 страницыHistoria Del Microapi-3762100100% (1)

- Matemáticas Taller Avanzado #17Документ4 страницыMatemáticas Taller Avanzado #17Luis NicolaoОценок пока нет

- Herramienta MWDДокумент8 страницHerramienta MWDCony MarОценок пока нет

- Modelo Guia de Observacion para Actividad 4 Tini 2023Документ8 страницModelo Guia de Observacion para Actividad 4 Tini 2023MARIA JOSE LOAIZA QUINTEROОценок пока нет

- Anotaciones Entrega Jueves 29Документ1 страницаAnotaciones Entrega Jueves 29javi_ariОценок пока нет

- A4 Taller de Controles Exixtenciales - 4491Документ7 страницA4 Taller de Controles Exixtenciales - 4491milena alapeОценок пока нет

- Auditoria Financiera Empresa La Esperanza S.ac.Документ5 страницAuditoria Financiera Empresa La Esperanza S.ac.DERY GERALDINE CAHUANA TICONAОценок пока нет

- Plan de Acción Felinos Del Valle Del CaucaДокумент74 страницыPlan de Acción Felinos Del Valle Del Caucapompi_258046Оценок пока нет

- Clasificación de bienes culturales según su escala patrimonialДокумент12 страницClasificación de bienes culturales según su escala patrimonialjeanОценок пока нет

- Avance 2Документ35 страницAvance 2henry estradaОценок пока нет

- 3° Proyecto Desarrollo Sostenible - II Semestre 2022Документ6 страниц3° Proyecto Desarrollo Sostenible - II Semestre 2022Luis Alejandro GranadosОценок пока нет

- PucaráДокумент5 страницPucaráBernard Dorian GuamanОценок пока нет

- Informe Inyectores DieselДокумент9 страницInforme Inyectores DieselJulian David VelezОценок пока нет

- Gestion IntergeneracionalДокумент7 страницGestion IntergeneracionalEridany Santiago100% (1)

- Pa 2 - Laboratorio de Liderazgo OkДокумент4 страницыPa 2 - Laboratorio de Liderazgo OkCatalina Ancalla AraujoОценок пока нет

- CV Sara JassoДокумент1 страницаCV Sara JassoBello ClauОценок пока нет

- Em07 Hoja CalculoДокумент1 страницаEm07 Hoja CalculoAlvaro VaroОценок пока нет

- Manual de Frutas MinionsДокумент8 страницManual de Frutas MinionsUSUARIO MARCEОценок пока нет

- Torches - Foster The People - MP3 DownloadsДокумент6 страницTorches - Foster The People - MP3 DownloadsImpulso DigitalОценок пока нет

- PSST - Edificio Paseo VerdanaДокумент57 страницPSST - Edificio Paseo VerdanaWild BanegasОценок пока нет

- Geografia: Geodinámica ExternaДокумент4 страницыGeografia: Geodinámica ExternaAlejandra ServínОценок пока нет

- Rúbrica de evaluación para proyecto demostrativoДокумент5 страницRúbrica de evaluación para proyecto demostrativoAndrewAndy100% (2)

- Conclusion Descriptiva InicialДокумент7 страницConclusion Descriptiva InicialGuisoù FusterОценок пока нет

- Texto Distopía Con ComprensiónДокумент4 страницыTexto Distopía Con ComprensiónMaríaPazUrrejola100% (2)

- Mobiliario UrbanoДокумент2 страницыMobiliario UrbanoBloopi10Оценок пока нет

- Reto Vitónica Sixpack 2013 - Semana 2 (III)Документ14 страницReto Vitónica Sixpack 2013 - Semana 2 (III)Antonio SaucaОценок пока нет

- LiderazgoДокумент4 страницыLiderazgopamejamОценок пока нет

- Evolución histórica de la GeomorfologíaДокумент9 страницEvolución histórica de la GeomorfologíaGian Marco Escobar CruzОценок пока нет

- Enunciado AEC Teoría Del Cambio IntergeneracionalДокумент4 страницыEnunciado AEC Teoría Del Cambio IntergeneracionalDani Sanchez HernandezОценок пока нет

- Modelo de Formato de Cotizacion para Proy AguaДокумент2 страницыModelo de Formato de Cotizacion para Proy AguaSmith Acuña VeraОценок пока нет

- Empresa Santa MariaДокумент19 страницEmpresa Santa MariaJepherson C HuaricapchaОценок пока нет