Академический Документы

Профессиональный Документы

Культура Документы

Q5 Solution

Загружено:

api-3801329Исходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Q5 Solution

Загружено:

api-3801329Авторское право:

Доступные форматы

Section: TE-C Roll #

Computer Organization and Architecture TE-C

Wednesday, May 16, 2007

QUIZ # 6: RISC PIPELINE

Max Marks = 15; Max Time: 15 minutes

A RISC processor has the following pipeline stages (Not all the stages are used for all the instructions,

therefore please do not use a stage if not used by the instruction):

• IFD : Instruction fetch & decode

• RR: Register(s) Read

• EAL: Execute ALU Operation

• RW: Register Write

• TSF: Test Status Flag i.e. a carry flag for a conditional branch

• MR: Memory to Register Transfer

• RM: Register to Memory Transfer

For the following Instructions in Table A (location A100 contains value 100).

No. Address Instruction Operation

1 FF00 MOV #200 AC 200

2 FF01 MOV R1, (A100) R1 (A100)

3 FF02 SUB R1 AC AC – R1

4 FF03 BRZ FF00 If Zero flag is set jump to

the address FF00 i.e. PC

FF00

5 FF04 STORE (A100) AC (A100)

Please complete the pipeline in Table B. Please watch out for data dependencies and insert NOOP (No

Operation) Instruction where needed.

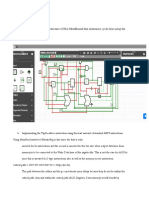

TABLE B – TIME

PIPELINE T1 T2 T3 T4 T5 T6 T7 T8 T9 T10 T11 T12 T13 T14

Stgaes

Instruction

No.

1 (1) IFD RW

2 (2) IFD MR

3 (3) IFD RR EAL RW

4(NOOP) IFD

5 (NOOP) IFD

6 (4) IFD RR TSF

7 (NOOP) IFD

8 (NOOP) IFD

9 (5) IFD RR RM

The values in brackets show the original instruction number from Table A

Вам также может понравиться

- Midterm Solutions Mar 30Документ6 страницMidterm Solutions Mar 30Sahil SethОценок пока нет

- 8Документ2 страницы8DuoDrenchОценок пока нет

- 4.multicycle and ExceptionsДокумент75 страниц4.multicycle and ExceptionsasaksjaksОценок пока нет

- E91 (11) C&asmДокумент12 страницE91 (11) C&asmAlekso GjakovskiОценок пока нет

- Apollo 7 RDVZДокумент10 страницApollo 7 RDVZmathgntОценок пока нет

- F2010 552 Project DescriptionДокумент6 страницF2010 552 Project DescriptionJamil_fawadОценок пока нет

- Quiz 3 SolutionsДокумент3 страницыQuiz 3 SolutionsP o o P o o H e a dОценок пока нет

- Adv Topic Compiler Supported ILPSlidesДокумент18 страницAdv Topic Compiler Supported ILPSlidesAtharvaОценок пока нет

- COA GTU Study Material Presentations Unit-5 11022020053257AMДокумент64 страницыCOA GTU Study Material Presentations Unit-5 11022020053257AMJanvi PatelОценок пока нет

- Microprocessors Memory Map: Outline of The LectureДокумент3 страницыMicroprocessors Memory Map: Outline of The LectureSaherОценок пока нет

- MIT6 004s09 Tutor21 SolДокумент20 страницMIT6 004s09 Tutor21 SolAbhijith RanguduОценок пока нет

- Workshop SlidesДокумент73 страницыWorkshop Slidesoscar tebarОценок пока нет

- Lecture 4Документ3 страницыLecture 4Md KamalОценок пока нет

- Geometric CommandsДокумент9 страницGeometric CommandschanhОценок пока нет

- Advanced Microprocessors: Session - 24 Prof. Venkataramaiah. P. PДокумент46 страницAdvanced Microprocessors: Session - 24 Prof. Venkataramaiah. P. Pvishu212167% (3)

- BH345 Final1Документ6 страницBH345 Final1jakirakaОценок пока нет

- Lecture 26Документ8 страницLecture 26VINAYОценок пока нет

- Ar4 Movement Commands: Command Line ExampleДокумент3 страницыAr4 Movement Commands: Command Line ExampleKshitijОценок пока нет

- Lab 4Документ6 страницLab 4حساب ويندوزОценок пока нет

- TDA7499Документ4 страницыTDA7499Angel ParraОценок пока нет

- Week 04Документ68 страницWeek 04aroosa naheedОценок пока нет

- Computers and Processors: Reference ManualДокумент40 страницComputers and Processors: Reference ManualbarryОценок пока нет

- Delta Ia-Hmi Omron Cj1-Cs1 Series PLC CM en 20130823Документ4 страницыDelta Ia-Hmi Omron Cj1-Cs1 Series PLC CM en 20130823cristiano eziquielОценок пока нет

- Performance Specification: Basic InstructionДокумент3 страницыPerformance Specification: Basic InstructionMangnimit SomlakОценок пока нет

- Delta Ia-Hmi Mks By125 Low Cost Synchrocontroller CM en 20111122Документ3 страницыDelta Ia-Hmi Mks By125 Low Cost Synchrocontroller CM en 20111122kaushal kumarОценок пока нет

- Exam 1: EE319K Spring 2013 Exam 1 (Practice 1)Документ6 страницExam 1: EE319K Spring 2013 Exam 1 (Practice 1)SRITHA PОценок пока нет

- Ar4 Movement CommandsДокумент3 страницыAr4 Movement Commandsbmw5gtОценок пока нет

- Stack Segment and Flag RegisterДокумент21 страницаStack Segment and Flag Registerاحمد عاصم عواجهОценок пока нет

- V Semester B. Tech (Electrical & Electronics Engineering) End Semester Examinations, November 2019Документ3 страницыV Semester B. Tech (Electrical & Electronics Engineering) End Semester Examinations, November 2019DuoDrenchОценок пока нет

- CortexM4 FPUДокумент14 страницCortexM4 FPUMohamedAliFerjaniОценок пока нет

- A RISC-Architecture As Target: 9.1. Resources and RegistersДокумент64 страницыA RISC-Architecture As Target: 9.1. Resources and RegistersanikaОценок пока нет

- 8051 Microcontroller ArchitectureДокумент28 страниц8051 Microcontroller ArchitectureAyan AcharyaОценок пока нет

- ESD Mid Sem Exam 2019 - KeyДокумент5 страницESD Mid Sem Exam 2019 - Keyashish6789Оценок пока нет

- Lab 7Документ14 страницLab 7MuhammadSaeedTahirОценок пока нет

- Delta Ia-Hmi Omron C Series PLC CM en 20111122Документ3 страницыDelta Ia-Hmi Omron C Series PLC CM en 20111122cristiano eziquielОценок пока нет

- Fetch Execute CycleДокумент17 страницFetch Execute CycleMuhammad Ehtisham HassanОценок пока нет

- Last Experiment MicroДокумент11 страницLast Experiment MicroRuth DVОценок пока нет

- 8085 - Short SummaryДокумент14 страниц8085 - Short SummaryTarunVarmaОценок пока нет

- Chapter 8Документ30 страницChapter 8Saifullah BhuttoОценок пока нет

- Lab Sheet For Chapter 9Документ26 страницLab Sheet For Chapter 9karnsushantlalОценок пока нет

- 5 PIC18 AddressingModes FSRs Table Part2Документ15 страниц5 PIC18 AddressingModes FSRs Table Part2Zain UL ABIDINОценок пока нет

- Ft-2000 Cat Manual Eng Eh025h124Документ20 страницFt-2000 Cat Manual Eng Eh025h124Carlos LimaОценок пока нет

- Coa 4th LessonДокумент23 страницыCoa 4th LessonMukeshОценок пока нет

- 2012 Spring MidtermДокумент6 страниц2012 Spring Midtermjust todaystalkОценок пока нет

- LCDF3 Chap 10 P2Документ32 страницыLCDF3 Chap 10 P2Hanif Nur IlhamОценок пока нет

- Microprocessor and Microcontrroller Module 1 - Calicut UniversityДокумент32 страницыMicroprocessor and Microcontrroller Module 1 - Calicut UniversityAshwin GopinathОценок пока нет

- Data Sheet: HEF4104B MSIДокумент5 страницData Sheet: HEF4104B MSIGoodLookingPirateОценок пока нет

- L3 - Representing Instructions in The ComputerДокумент13 страницL3 - Representing Instructions in The ComputerJaisaiarun P SrinivasanОценок пока нет

- 4731BДокумент3 страницы4731BRaul Sedano LauОценок пока нет

- Microcontroller 8051Документ13 страницMicrocontroller 8051Emon RoyОценок пока нет

- Cao Notes Mca First SemДокумент31 страницаCao Notes Mca First SemANKUR CHOUDHARYОценок пока нет

- 80511Документ123 страницы80511snehith009100% (1)

- Computer Architechture ReportДокумент15 страницComputer Architechture ReportNguyn LОценок пока нет

- Midterm1 SolДокумент5 страницMidterm1 SolLiaqat Hussain BhattiОценок пока нет

- Lec 11Документ19 страницLec 11jyothibellary4233Оценок пока нет

- Central Processing UnitДокумент49 страницCentral Processing UnitFaizal KhanОценок пока нет

- DLX-Phases of Instruction CycleДокумент12 страницDLX-Phases of Instruction Cyclesyma masoodОценок пока нет

- Module IV LOCДокумент21 страницаModule IV LOCrahulОценок пока нет

- Q6 SolutionДокумент1 страницаQ6 Solutionapi-3801329Оценок пока нет

- ErrataДокумент42 страницыErrataTamára SalvatoriОценок пока нет

- Q1 SolutionДокумент3 страницыQ1 Solutionapi-3801329Оценок пока нет

- Pentium 4 StructureДокумент38 страницPentium 4 Structureapi-3801329100% (6)

- Computer Structure and ComponentsДокумент18 страницComputer Structure and Componentsapi-3801329100% (1)

- Pentium 4 Pipe LiningДокумент7 страницPentium 4 Pipe Liningapi-3801329100% (5)

- Multiple Interrupts and Buses StructureДокумент17 страницMultiple Interrupts and Buses Structureapi-3801329100% (2)

- Binomial & Fibonacci Heap Advanced)Документ60 страницBinomial & Fibonacci Heap Advanced)api-3801329100% (3)

- Height-Biased Leftist Heaps Advanced)Документ91 страницаHeight-Biased Leftist Heaps Advanced)api-3801329Оценок пока нет

- Weight-Biased Leftist Heaps Advanced)Документ64 страницыWeight-Biased Leftist Heaps Advanced)api-3801329Оценок пока нет

- ProbingДокумент5 страницProbingapi-3801329Оценок пока нет

- Red-Black Trees Advanced)Документ44 страницыRed-Black Trees Advanced)api-3801329100% (2)

- Easynn-Plus Help: The User Interface ManualДокумент174 страницыEasynn-Plus Help: The User Interface Manualmiherea558Оценок пока нет

- Business Writing As A Tool of Management ControlДокумент13 страницBusiness Writing As A Tool of Management Controlkapeel77Оценок пока нет

- Variuos Types of Creative NonfictionДокумент2 страницыVariuos Types of Creative NonfictionRodolfo ObanilОценок пока нет

- Limitations To Economics ModelДокумент84 страницыLimitations To Economics ModelLesterОценок пока нет

- Microsoft Windows Server Network InfrastructureДокумент2 страницыMicrosoft Windows Server Network Infrastructurerocks66aryan100% (1)

- The Holy Quran in ItalianДокумент199 страницThe Holy Quran in Italianweird johnОценок пока нет

- ICP DAS WISE User Manual - V1.1.1en - 52xxДокумент288 страницICP DAS WISE User Manual - V1.1.1en - 52xxYevgeniy ShabelnikovОценок пока нет

- BENGALI (Code: 105) Syllabus: CLASS-XII (2018 - 2019)Документ2 страницыBENGALI (Code: 105) Syllabus: CLASS-XII (2018 - 2019)Nilabha DasОценок пока нет

- (Review of International Studies 2004-Apr Vol. 30 Iss. 2) Review by - JefДокумент17 страниц(Review of International Studies 2004-Apr Vol. 30 Iss. 2) Review by - JefBianca SferleОценок пока нет

- A Couple Tips of Registry Below Only Dedicated For Windows XP UserДокумент36 страницA Couple Tips of Registry Below Only Dedicated For Windows XP UsermaddalakrishnakanthОценок пока нет

- SAP Proxy ConfigurationДокумент6 страницSAP Proxy ConfigurationDanar Andri PrasetyoОценок пока нет

- LIMA & MELLO - Social Representation and MimesisДокумент21 страницаLIMA & MELLO - Social Representation and MimesisHugo R. MerloОценок пока нет

- Zaki NassifpresentationДокумент13 страницZaki Nassifpresentationfarah abdallahОценок пока нет

- Doctrine of The Sabbath.Документ73 страницыDoctrine of The Sabbath.Steve SparksОценок пока нет

- LYX TutorialДокумент37 страницLYX TutorialDan WeinsteinОценок пока нет

- Chapters - M.Shovel-Making Sense of Phrasal Verbs PDFДокумент95 страницChapters - M.Shovel-Making Sense of Phrasal Verbs PDFMartinОценок пока нет

- HL ENG Gr1 B1Документ142 страницыHL ENG Gr1 B1Alexandra MackinnonОценок пока нет

- Licensed To Arun Kumar Das: ,."bu'OII'Документ5 страницLicensed To Arun Kumar Das: ,."bu'OII'OMEGA CONSULTANT SERVICESОценок пока нет

- f5 Bigip v13 Secassessment PDFДокумент105 страницf5 Bigip v13 Secassessment PDFBttrngrmОценок пока нет

- Hộp chỉnh lực căng (TENSION CONTROLLER MITSUBISHI) LE-40MTB-EДокумент76 страницHộp chỉnh lực căng (TENSION CONTROLLER MITSUBISHI) LE-40MTB-ENguyễn Văn DũngОценок пока нет

- Verri Puku ScribdДокумент584 страницыVerri Puku Scribdajax248590Оценок пока нет

- Cs161 Sp08 Mt1 Sol-Computer SecurityДокумент14 страницCs161 Sp08 Mt1 Sol-Computer SecurityAshesh ParmarОценок пока нет

- Lesson 32 - Festivals VIIДокумент9 страницLesson 32 - Festivals VIIMilan KokowiczОценок пока нет

- CPDB Basic User Manual v3.0 PDFДокумент19 страницCPDB Basic User Manual v3.0 PDFRelebohileОценок пока нет

- C Structure and FunctionДокумент5 страницC Structure and FunctionKamal NarayanОценок пока нет

- Obser 1Документ4 страницыObser 1api-307396832Оценок пока нет

- CH 04Документ84 страницыCH 04Bindu Handa MahandruОценок пока нет

- Lec9 Lab CSC371 Database SystemsДокумент19 страницLec9 Lab CSC371 Database SystemsAbdullah ShabbirОценок пока нет

- Jing Ye SiДокумент2 страницыJing Ye SiG. Donald Cribbs0% (1)

- 17th Century Vocal Solo MusicДокумент0 страниц17th Century Vocal Solo MusicEduardo Jahnke RojasОценок пока нет