Академический Документы

Профессиональный Документы

Культура Документы

FSMs in VHDL Using Enumeration

Загружено:

Manoj KasareИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

FSMs in VHDL Using Enumeration

Загружено:

Manoj KasareАвторское право:

Доступные форматы

FSMs in VHDL Using Enumeration Data Types Consider a falling edge triggered FSM that performs the following

state diagram functionality. We want to write a VHDL model using enumeration data types.

0X 0X 10 0X 11

This FSM is a Moore machine since its outputs (RST and SHIFT) are a function of the current state only. The four states in the state diagram have not been assigned and are represented by the variable names: Reset, BIST, Result, and NOP (all are valid VHDL names). Since the FSM is falling edge triggered, all state transitions occur on the falling edge of the clock (which we will assume is named CLK). Finally, recall that a signal will retain its value when not explicitly specified. As a result, we only need to address changes in states in our model.

Reset 10

11

BIST 00

10

Result 01

10 11

10

Input Ordering: EN TDI Output Ordering: RST SHIFT

11

NOP 00

0X

entity FSM is port (CLK, EN, TDI: in bit; RST, SHIFT: out bit); end entity FSM; architecture RTL of FSM is type STATES is (Reset, BIST, Result, NOP); signal CS: STATES; -- current state begin SYNC: process (CLK) begin if (CLKevent and CLK=0) then if (EN = 1) then if (CS = Reset) then if (TDI=0) then CS <= BIST; end if; elsif (CS = BIST) then if (TDI=1) then CS <= Result; end if; elsif (CS = Result) then if (TDI=1) then CS <= NOP; end if; elsif (CS = NOP) then if (TDI=0) then CS <= BIST; else CS <= Reset; end if; end if; end if; end if; end process SYNC; COMB: process (CS) begin if (CS = Reset) then RST <= 1; SHIFT <= 0; elsif (CS = Result) then RST <= 0; SHIFT <= 1; else RST <= 0; SHIFT <= 0; end if; end process COMB; end architecture RTL;

C. E. Stroud, Dept. of ECE, Auburn Univ.

8/06

Вам также может понравиться

- Lumayaga Homework3Документ9 страницLumayaga Homework3Satoshi EugarnОценок пока нет

- CATIA V5 FEA Tutorials - Bent Rod AnalysisДокумент24 страницыCATIA V5 FEA Tutorials - Bent Rod AnalysisroandlucОценок пока нет

- Telecom Based Inventory ManagementДокумент7 страницTelecom Based Inventory ManagementEly DalimanОценок пока нет

- 09-Logic Design With ASM Chart-11-07Документ58 страниц09-Logic Design With ASM Chart-11-07Sandeep ChaudharyОценок пока нет

- Digital Design Using VHDL: Using Xilinx'S Tool For Synthesis and Modelsim For Verification Part (Iv)Документ17 страницDigital Design Using VHDL: Using Xilinx'S Tool For Synthesis and Modelsim For Verification Part (Iv)Rakesh Kumar DОценок пока нет

- ASIC Va VHDL Toan TapДокумент76 страницASIC Va VHDL Toan TapCường VũОценок пока нет

- EEE 70 Advanced Topics in Logic Design: Read Before ClassДокумент30 страницEEE 70 Advanced Topics in Logic Design: Read Before ClassPraveen MeduriОценок пока нет

- FSM in VHDLДокумент10 страницFSM in VHDLkunalsekhri123Оценок пока нет

- Lec17 FSM PDFДокумент27 страницLec17 FSM PDFNithin KumarОценок пока нет

- El5067 13 Lec03 FSM and HLSM in VHDLДокумент28 страницEl5067 13 Lec03 FSM and HLSM in VHDLhasbiiieОценок пока нет

- FSM, Asm, FSMD, Asmd: EECE-4740/5740 Advanced VHDL and FPGA DesignДокумент34 страницыFSM, Asm, FSMD, Asmd: EECE-4740/5740 Advanced VHDL and FPGA DesignCuong PhamОценок пока нет

- Universidad Nacional Tecnologica de Lima SurДокумент5 страницUniversidad Nacional Tecnologica de Lima SurJoseph JesusОценок пока нет

- VHDL CodesДокумент9 страницVHDL CodesSaneesh KarayilОценок пока нет

- Universidad Nacional Tecnologica de Lima SurДокумент5 страницUniversidad Nacional Tecnologica de Lima SurJoseph JesusОценок пока нет

- Examples of Finite State Machines (FSMS) : Counters and Pattern GeneratorsДокумент71 страницаExamples of Finite State Machines (FSMS) : Counters and Pattern GeneratorsflowarОценок пока нет

- Finite State Machine Design Using VHDLДокумент8 страницFinite State Machine Design Using VHDLJoe MannОценок пока нет

- Tutorial: Modeling and Testing Finite State Machines (FSM)Документ5 страницTutorial: Modeling and Testing Finite State Machines (FSM)rajesh4172003Оценок пока нет

- Ee529 Asg3Документ22 страницыEe529 Asg3dd23015Оценок пока нет

- ADC-DAC Tutorial on Spartan 3E BoardДокумент6 страницADC-DAC Tutorial on Spartan 3E BoardNguyễn Hữu DuyОценок пока нет

- Lec19 FSMДокумент14 страницLec19 FSMGAURAV KUMARОценок пока нет

- Digital Logic Design: Register Transfer Specification & DesignДокумент22 страницыDigital Logic Design: Register Transfer Specification & Designsunny louisОценок пока нет

- VeriLog RTL DesignДокумент32 страницыVeriLog RTL Designhuuquan1994Оценок пока нет

- Finite State Machine DesignДокумент64 страницыFinite State Machine Designivanf15Оценок пока нет

- EE 459/500 - HDL Based Digital Design With Programmable Logic FSM, Asm, FSMD, AsmdДокумент15 страницEE 459/500 - HDL Based Digital Design With Programmable Logic FSM, Asm, FSMD, AsmdMushtaq sheikhОценок пока нет

- Bit masking and TRAP functions in LC3 assemblyДокумент5 страницBit masking and TRAP functions in LC3 assemblyAnonymous zN7CjfgnEОценок пока нет

- State Graphs For Control NetworksДокумент37 страницState Graphs For Control Networksashudiya100% (1)

- SEQUENTIAL LOGIC IMPLEMENTATIONДокумент18 страницSEQUENTIAL LOGIC IMPLEMENTATIONchristytangОценок пока нет

- FSM Design Using VHDLДокумент19 страницFSM Design Using VHDLrajivsharma1610Оценок пока нет

- VHDL - Practical Example - Designing An UARTДокумент18 страницVHDL - Practical Example - Designing An UARTPrabakaran EllaiyappanОценок пока нет

- CSE 260 ExamДокумент10 страницCSE 260 ExammaddogmljОценок пока нет

- Tutorial For Running A Stepper-Motor Using Krypton Board (Wel - Lab, Iit Bombay)Документ12 страницTutorial For Running A Stepper-Motor Using Krypton Board (Wel - Lab, Iit Bombay)Chiquita WhiteОценок пока нет

- 8 Bit Hex To Decimal ConversionДокумент20 страниц8 Bit Hex To Decimal ConversionManoj Kavedia100% (1)

- ECE448 Lecture6 FSMДокумент77 страницECE448 Lecture6 FSMHoàng Việt CườngОценок пока нет

- Finite-State Machine (FSM) : TaskДокумент7 страницFinite-State Machine (FSM) : TaskelexboyОценок пока нет

- Lecture 4: Continuation of SystemverilogДокумент17 страницLecture 4: Continuation of SystemverilogSivasubramanian ManickamОценок пока нет

- Divide by 3 FSMДокумент14 страницDivide by 3 FSMGirish ChukkaОценок пока нет

- State Encoding: One-Hot Encoding Output EncodingДокумент24 страницыState Encoding: One-Hot Encoding Output EncodingRajesh BathijaОценок пока нет

- VHDL Cheat Sheet Exam 1Документ3 страницыVHDL Cheat Sheet Exam 1Kevin Wilczak100% (1)

- FSMD PressДокумент29 страницFSMD PressshoaibkhaliqОценок пока нет

- Digital Logic Design: Register Transfer Specification & DesignДокумент21 страницаDigital Logic Design: Register Transfer Specification & DesignTrần Thảo NguyênОценок пока нет

- 2.micro Controller 8086 Instruction SetДокумент88 страниц2.micro Controller 8086 Instruction SetManu MohanОценок пока нет

- FSM Design for Vending Machine ProblemДокумент6 страницFSM Design for Vending Machine ProblemCheka CurativoОценок пока нет

- VHDL ProjectДокумент4 страницыVHDL ProjectJayp MistryОценок пока нет

- I8086 Instruction Set-With ExamplesДокумент53 страницыI8086 Instruction Set-With ExamplesNarsimha PuttaОценок пока нет

- A Finite State MachineДокумент2 страницыA Finite State Machinesantosh861986Оценок пока нет

- White Line Follower Circuit and CodeДокумент10 страницWhite Line Follower Circuit and Codepratheep01Оценок пока нет

- Steps Involved in LPC2148Документ8 страницSteps Involved in LPC2148Ravi RajanОценок пока нет

- Examples of Finite State Machines (FSMS) : Counters and Pattern GeneratorsДокумент71 страницаExamples of Finite State Machines (FSMS) : Counters and Pattern GeneratorsArif Sumardiono100% (1)

- Lec8 Slides RTLДокумент25 страницLec8 Slides RTLAbdalrhman juberОценок пока нет

- VHDL of The Moore Machine With A Synchronous Reset and MEALY SEQ DETECTORДокумент5 страницVHDL of The Moore Machine With A Synchronous Reset and MEALY SEQ DETECTORdhr893Оценок пока нет

- ADE Lecture7Документ27 страницADE Lecture7محمد ياسر محي الدينОценок пока нет

- Algorithmic State Machine (ASM) Charts: VHDL Code & Timing DiagramsДокумент32 страницыAlgorithmic State Machine (ASM) Charts: VHDL Code & Timing DiagramsManuel Garay GutierrezОценок пока нет

- SIDDHI_E23CSEU2200_ASSIGNMENT 8Документ7 страницSIDDHI_E23CSEU2200_ASSIGNMENT 8chipichipichapachapa2121Оценок пока нет

- MAQUINA DE ESTADOS1 (Autoguardado)Документ19 страницMAQUINA DE ESTADOS1 (Autoguardado)YealsatoОценок пока нет

- FSM DesignДокумент24 страницыFSM DesignNazim Ali100% (1)

- MPMC Assignment-1Документ8 страницMPMC Assignment-1Praveen kumarОценок пока нет

- Controler Cu FSMДокумент2 страницыControler Cu FSMBianca TeodoraОценок пока нет

- Projects With Microcontrollers And PICCОт EverandProjects With Microcontrollers And PICCРейтинг: 5 из 5 звезд5/5 (1)

- Learn Digital and Microprocessor Techniques On Your Smartphone: Portable Learning, Reference and Revision Tools.От EverandLearn Digital and Microprocessor Techniques On Your Smartphone: Portable Learning, Reference and Revision Tools.Оценок пока нет

- Chapter-2.1: Limit and ContinuityДокумент9 страницChapter-2.1: Limit and ContinuityAtique FaisalОценок пока нет

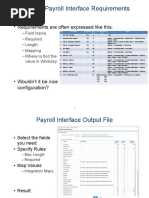

- Typically Payroll Interface Requirements: - Requirements Are Often Expressed Like ThisДокумент56 страницTypically Payroll Interface Requirements: - Requirements Are Often Expressed Like Thissyedmehar100% (1)

- Logistics Management and Industrial Engineering (PDFDrive) PDFДокумент220 страницLogistics Management and Industrial Engineering (PDFDrive) PDFGosspel Bernauli SihalohoОценок пока нет

- Discovery 26: Configure Control Plane Policing: Task 1: Configure and Verify Copp On R1Документ2 страницыDiscovery 26: Configure Control Plane Policing: Task 1: Configure and Verify Copp On R1Ionut StanciuОценок пока нет

- Fanuc LR Mate 200ib 200ib 3lДокумент4 страницыFanuc LR Mate 200ib 200ib 3lHector Calvillo GtzОценок пока нет

- OOPs Assignment For Btech 2nd YearДокумент13 страницOOPs Assignment For Btech 2nd YearVARUN UTSAVОценок пока нет

- Negros Oriental State University Bayawan - Sta. Catalina CampusДокумент6 страницNegros Oriental State University Bayawan - Sta. Catalina CampusKit EdrialОценок пока нет

- Air Writing and Recognition SystemДокумент8 страницAir Writing and Recognition SystemIJRASETPublicationsОценок пока нет

- AN4088Документ71 страницаAN4088Bo SОценок пока нет

- State of Cyber-Security in IndonesiaДокумент32 страницыState of Cyber-Security in IndonesiaharisОценок пока нет

- R Datasheet Fi8170Документ2 страницыR Datasheet Fi8170comunicacionecuacopiaОценок пока нет

- HCI-case Study - B262Документ10 страницHCI-case Study - B262Saket SinghОценок пока нет

- Guidelines For RF PCB Layout 1317765607Документ14 страницGuidelines For RF PCB Layout 1317765607smsarmadОценок пока нет

- Photoshop LessonДокумент4 страницыPhotoshop LessonXzyl BantoloОценок пока нет

- XPT System - Application Notes - R6.0 PDFДокумент118 страницXPT System - Application Notes - R6.0 PDFCamilo TОценок пока нет

- PGDC Syllabus - 19102022 - 221105 - 133044Документ27 страницPGDC Syllabus - 19102022 - 221105 - 133044Arjun ManeОценок пока нет

- Barangay Records Management System Chapter 1Документ6 страницBarangay Records Management System Chapter 1Job Edison DungcaОценок пока нет

- Fire Detection and Extinguishing RobotДокумент1 страницаFire Detection and Extinguishing RobotTalha HanifОценок пока нет

- Focusrite Red7Документ1 страницаFocusrite Red7titoОценок пока нет

- PT No3 - ALU Using ARDUINOДокумент16 страницPT No3 - ALU Using ARDUINOLouieJay LayderosОценок пока нет

- SAS Interview Questions and Answers 1Документ22 страницыSAS Interview Questions and Answers 1SASTechies83% (6)

- Eegame LogcatДокумент24 страницыEegame LogcatBINXX훼 VОценок пока нет

- Defibrillators, External, Automated Semiautomated - 030223112503Документ105 страницDefibrillators, External, Automated Semiautomated - 030223112503CLAUDIA PAOLA HOLGUIN VELEZОценок пока нет

- Rab MessageДокумент203 страницыRab MessageBechir BrahmiОценок пока нет

- LNX Cheat SheetДокумент5 страницLNX Cheat SheetKruno KartusОценок пока нет

- BSIT 1 2 PUP Webmail AccountДокумент2 страницыBSIT 1 2 PUP Webmail AccountMiguel Jose DavantesОценок пока нет

- Discovery of BGP MPLS VPNs PDFДокумент13 страницDiscovery of BGP MPLS VPNs PDFGelu IonitaОценок пока нет

- Multile Choice Questions - Unit - 3Документ8 страницMultile Choice Questions - Unit - 3Harshad LokhandeОценок пока нет