Академический Документы

Профессиональный Документы

Культура Документы

New Lab Manual (ECA)

Загружено:

Shrinivas SaptalakarИсходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

New Lab Manual (ECA)

Загружено:

Shrinivas SaptalakarАвторское право:

Доступные форматы

EC LAB MANUAL

ECE DEPARTMENT

SPHOORTHY ENGINEERING COLLEGE

Nadargul (V), Saroornagar (M), R.R. (Dist.), A.P.

LABORATORY MANUAL For Electronic circuits

(FOR II ECE-REGULATION R07)

Department Of

ELECTRONICS & COMMUNICATION ENGINEERING

Academic Year: 2009-2010.

SPHOORTHY Engg.College.

EC LAB MANUAL

ECE DEPARTMENT

INDEX

S.NO. 1. 2. 3. 4. 5. 6. . S.NO. 7. 8. 9. 10. 11 12 SOFTWARE NAME OF THE EXPERIMENT COMMON EMITTER AND COMMON SOURCE AMPLIFIER TWO STAGE RC COUPLED AMPLIFIER RC PHASE SHIFT OSCILLATOR USING TRANSISTORS CLASS A POWER AMPLIFIER(TRANSFORMERLESS) CLASS B COMPLEMENTARY SYMMETRY AMPLIFIER HIGH FREQUENCY COMMON BASE(BJT) AND COMMON GATE (JFET)AMPLIFIER HARDWARE NAME OF THE EXPERIMENT COMMON EMITTER AND COMMON SOURCE AMPLIFIER TWO STAGE RC COUPLED AMPLIFIER RC PHASE SHIFT OSCILLATOR USING TRANSISTORS SINGLE TUNED VOLTAGE AMPLIFIER SERIES VOLTAGE REGULATOR SHUNT VOLTAGE REGULATOR PAGE NO. 3 7 11 15 18 21

PAGE NO 24 30 36 39 41 44

Principal (Dr.SYED S BASHA, M.E., Ph.D.)

Head of the Department (Mr.T.RAVICHANDRA BABU)

SPHOORTHY Engg.College.

EC LAB MANUAL

ECE DEPARTMENT

EXP . NO. 1 COMMON EMITTER AMPLIFIER AND COMMON SOURCE AMPLIFIER

COMMON EMITTER AMPLIFIER: AIM To design and simulate the frequency response of common emitter amplifier by using multisim software and calculate the band width. SPECIFICATIONS 1. 1k Resistor 1 No. 2. 33k Resistor 3 No. 3. 3.3K Resistor 1 No 4. 4.7k Resistor 1 No 5. 470 Resistor 1 No 6. 10 F/ 25 V Electrolytic Capacitor 2 No. 7. 100 F/ 25 V Electrolytic Capacitor 1 No. 8. Transistors BC107 1No 9. Function generator 10. CRO 11. Regulated power supply APPARATUS 1. Multisim software 2. Personal computer CIRCUIT DIAGRAM

VCC VCC R4 33k 12V R5 3.3k 4 R1 1 1k 14.14mVrms 100 Hz 0 2 C1 10uF R3 4.7k Q1 3 BC107BP 7 R2 470 10uF

A + _ + B _

C3

XSC1

Ext T rig + _

5 C2 100uF 0

V1

SPHOORTHY Engg.College.

EC LAB MANUAL THEORY

ECE DEPARTMENT

The CE amplifier provides high gain & wide frequency response. The emitter lead is common to both input and output circuits and is grounded. The emitter base circuit is forward biased. The collector current is controlled by the base current rather than emitter current. The input signal is applied to base terminal of the transistor and amplifier output is taken across collector terminal. A very small change in base current produces a much larger change in collector current. Frequency response of an amplifier is defined as the variation of gain with respective frequency. The gain of the amplifier increases as the frequency increases from zero till it becomes maximum at lower cut-off frequency and remains constant till higher cut-off frequency and then it falls again as the frequency increases. At low frequencies the reactance of coupling capacitor CC is quite high and hence very small part of signal will pass through from one stage to the next stage. At high frequencies the reactance of inter electrode capacitance is very small and behaves as a short circuit. This increases the loading effect on next stage and service to reduce the voltage gain due to these reasons the voltage gain drops at high frequencies. At mid frequencies the effect of coupling capacitors is negligible and acts like short circuit, where as inter electrode capacitors acts like open circuit. So, the circuit becomes resistive at mid frequencies and the voltage gain remains constant during this range. PROCEDURE 1. 2. 3. 4. 5. 6. 7. Open multisim software to design the circuit. Select on new editor window and place the required component on the circuit window. Make the connections using wire and check the connections of power supply and oscillator. Go for simulation using run key and observe the output waveforms on oscillator. Indicate the node names and go for AC analysis with output node. Observe the AC analysis and draw the magnitude and phase response curves. Calculate the bandwidth of the amplifier. Where Bandwidth f2-f1 f1 is Lower cutoff frequency f2 is Upper cutoff frequency

OBSERVATIONS Maximum gain in dB 3dB gain Lower cutoff frequency f1 Upper cutoff frequency f2 Bandwidth f2-f1 = = = = =

SPHOORTHY Engg.College.

EC LAB MANUAL OUTPUT WAVE FORM

ECE DEPARTMENT

EXPECTED GRAPH

SPHOORTHY Engg.College.

EC LAB MANUAL RESULT

ECE DEPARTMENT

Thus the frequency response of a common emitter amplifier is verified and band width is calculated . VIVA QUESTIONS 1. 2. 3. 4. 5. 6. 7. 8. What are the advantages and disadvantages of single-stage amplifiers? Why gain falls at HF and LF? Why the gain remains constant at MF? Explain the function of emitter bypass capacitor, Ce? How the band width will effect as more number of stages are cascaded? Define frequency response? What is the phase difference between input and output waveforms of a CE amplifier? What is early effect?

SPHOORTHY Engg.College.

EC LAB MANUAL COMMON SOURCE AMPLIFIER AIM

ECE DEPARTMENT

To design and simulate the frequency response of common source amplifier by using multisim software and calculate the band width. SPECIFICATIONS 1. 1k Resistor 1 No. 2. 1M Resistor 3 No. 3. 10K Resistor 1 No. 4. 4.7k Resistor 1 No. 5. 10 F/ 25 V Electrolytic Capacitor 2 No. 6. 100 F/ 25 V Electrolytic Capacitor 1 No. 7. FET 2N4392 1No. 8. Function generator. 9. CRO. 10. Regulated power supply. APPARATUS 1. Multisim software. 2. Personal computer. CIRCUIT DIAGRAM

VDD 12V VDD R5 10k 5 10uF R1 1 1k 14.14mVrms 100 Hz 0 2 C1 10uF R3 1M 0 4 R4 4.7k C3 100uF 3 Q1 2N4392

+ A _ + B _

C2

XSC1

Ext Trig + _

V1

SPHOORTHY Engg.College.

EC LAB MANUAL THEORY

ECE DEPARTMENT

The FET is a type of transistor commonly used for weak signal amplification. The device can amplify analog or digital signals. It can also switch DC or function as an oscillator. In the FET current flows along a semiconductor path called the channel. At one end of the channel, there is an electrode called source. At the other end of the channel there is an electrode called the drain. Frequency response of an amplifier is defined as the variation of gain with respective frequency. The gain of the amplifier increases as the frequency increases from zero till it becomes maximum at lower cut-off frequency and remains constant till higher cut-off frequency and then it falls again as the frequency increases. At low frequencies the reactance of coupling capacitor CC is quite high and hence very small part of signal will pass through from one stage to the next stage. At high frequencies the reactance of inter electrode capacitance is very small and behaves as a short circuit. This increases the loading effect on next stage and service to reduce the voltage gain due to these reasons the voltage gain drops at high frequencies. At mid frequencies the effect of coupling capacitors is negligible and acts like short circuit, where as inter electrode capacitors acts like open circuit. So, the circuit becomes resistive at mid frequencies and the voltage gain remains constant during this range PROCEDURE 1. 2. 3. 4. 5. 6. 7. Open multisim software to design the circuit. Select on new editor window and place the required component on the circuit window. Make the connections using wire and check the connections of power supply and oscillator. Go for simulation using run key and observe the output waveforms on oscillator. Indicate the node names and go for AC analysis with output node. Observe the AC analysis and draw the magnitude and phase response curves. Calculate the bandwidth of the amplifier. Bandwidth f2-f1 Where f1 is Lower cutoff frequency f2 is Upper cutoff frequency

OBSERVATIONS Maximum gain in dB 3dB gain Lower cutoff frequency f1 Upper cutoff frequency f2 Bandwidth f2-f1 = = = = =

SPHOORTHY Engg.College.

EC LAB MANUAL OUTPUTWAVEFORM

ECE DEPARTMENT

EXPECTED GRAPH

SPHOORTHY Engg.College.

EC LAB MANUAL RESULT

ECE DEPARTMENT

Thus the frequency response of a common source amplifier is verified and band width is calculated . VIVA QUESTIONS 1. 2. 3. 4. 5. What is the difference between FET and BJT? FET is unipolar or bipolar? Draw the symbol of FET? What are the applications of FET? FET is voltage controlled or current controlled?

10

SPHOORTHY Engg.College.

EC LAB MANUAL EXP . NO. 2 TWO STAGE RC-COUPLED AMPLIFIER AIM

ECE DEPARTMENT

To design and simulate the frequency response of a two stage RC-coupled amplifier and calculate its band width SPECIFICATIONS 1. 2.2k Resistor 1 No. 2. 150k Resistor 1No. 3. 22k Resistor 1 No 4. 10k Resistor 1 No 5. 560 Resistor 1 No 6. 4.7k Resistor 3No. 7. 47k Resistor 1 No. 8. 33k Resistor 1 No 9. 220 Resistor 1 No 10. 10 F/ 25 V Electrolytic Capacitor 5 No. 11. Transistors BC107 2 No. 12. CRO (Dual channel) 13. Regulated power supply 14. Function generator APPARATUS 1. Multisim software 2. Personal computer CIRCUIT DIAGRAM

VCC VCC R3 150k 10k R4 C2 9 R1 2.2k 2 V1 14.14mVrms 100 Hz 0 C4 10uF 4 Q1 10uF 11 10 Q2 5 BC107BP 6 R8 560 R2 22k 7 R11 4.7k C3 10uF 220 R7 33k BC107BP 1

+ Ext T rig + _ A _ + B _

12V R5 47k R9 4.7k C5 10uF XSC1

R10 8

R6 4.7k

C1 10uF

11

SPHOORTHY Engg.College.

EC LAB MANUAL THEORY

ECE DEPARTMENT

As the gain provided by a single stage amplifier is usually not sufficient to drive the load, so to achieve extra gain multi-stage amplifier are used. In multi-stage amplifiers output of one-stage is coupled to the input of the next stage. The coupling of one stage to another is done with the help of some coupling devices. If it is coupled by RC then the amplifier is called RC-coupled amplifier. Frequency response of an amplifier is defined as the variation of gain with respective frequency. The gain of the amplifier increases as the frequency increases from zero till it becomes maximum at lower cut-off frequency and remains constant till higher cut-off frequency and then it falls again as the frequency increases. At low frequencies the reactance of coupling capacitor CC is quite high and hence very small part of signal will pass through from one stage to the next stage. At high frequencies the reactance of inter electrode capacitance is very small and behaves as a short circuit. This increases the loading effect on next stage and service to reduce the voltage gain due to these reasons the voltage gain drops at high frequencies. At mid frequencies the effect of coupling capacitors is negligible and acts like short circuit, where as inter electrode capacitors acts like open circuit. So, the circuit becomes resistive at mid frequencies and the voltage gain remains constant during this range. PROCEDURE 1. Open multisim software to design the circuit. 2. Select on new editor window and place the required component on the circuit window. 3. Make the connections using wire and check the connections of power supply and oscillator. 4. Go for simulation using run key and observe the output waveforms on oscillator. 5. Indicate the node names and go for AC analysis with output node. 6. Observe the AC analysis and draw the magnitude and phase response curves. 7. Calculate the bandwidth of the amplifier. Bandwidth f2-f1 Where f1 is Lower cutoff frequency f2 is Upper cutoff frequency OBSERVATIONS Maximum gain in dB 3dB gain Lower cutoff frequency f1 Upper cutoff frequency f2 Bandwidth f2-f1 = = = = =

12

SPHOORTHY Engg.College.

EC LAB MANUAL OUTPUTWAVEFORM

ECE DEPARTMENT

EXPECTED GRAPH

RESULT Thus the frequency response of a two stage RC coupled amplifier is verified and band width is calculated . 13 SPHOORTHY Engg.College.

EC LAB MANUAL VIVA QUESTIONS 1. 2. 3. 4. 5. 6. 7.

ECE DEPARTMENT

What are the advantages and disadvantages of multi-stage amplifiers? Why gain falls at HF and LF? Why the gain remains constant at MF? Explain the function of emitter bypass capacitor, Ce? How the band width will effect as more number of stages are cascaded? Define frequency response? Give the formula for effective lower cut-off frequency, when N-number of stages are cascaded. 8. Explain the effect of coupling capacitors and inter-electrode capacitances on overall gain. 9. By how many times effective upper cut-off frequency will be reduced, if three identical stages are cascaded? 10. Mention the applications of two-stage RC-coupled amplifiers.

14

SPHOORTHY Engg.College.

EC LAB MANUAL EXP . NO. 3 RC PHASE SHIFT OSCILLATOR AIM

ECE DEPARTMENT

To design an RC phase shift oscillator and compare theoritical and practical frequency of oscillations. SPECIFICATIONS 1. 2. 3. 4. 5. 6. 7. 8. 9. 10k Resistor 3No. 47k Resistor 1No. 2.2k Resistor 1 No 1k Resistor 1 No 100 F/ 25 V Electrolytic Capacitor 1 No. 1nF/47nF Capacitors 3 each. Transistors BC107 1 No. CRO (Dual channel) Regulated power supply

APPARATUS 1. Multisim software 2. Personal computer CIRCUIT DIAGRAM

R5 47k C1 1nF C3 1nF R2 10k C2 1nF R4 10k R3 10k

2 R6 2.2k

V1 12 V 0

XSC1 Q1

Ext T rig + _ A + _ + B _

3 BC107BP 4 R1 1k 1 0

C4 100uF

15

SPHOORTHY Engg.College.

EC LAB MANUAL THEORY

ECE DEPARTMENT

RC phase shift oscillator has a CE amplifier followed by three sections of RC phase shift feedback networks. The output of the last stage is return to the input of the amplifier.the values of R and C are chosen such that the phase shift of each RC section is 600.thus,the RC ladder network produces a total phase shift of 1800 between its input and output voltage for the given frequencies.since CE amplifier produces 1800 phase shift the total phase shift from the base of the transistor around the circuit and back to the transistor will be exactly 3600 or 00.The frequency of oscillation is given by F = 1/2RC6 PROCEDURE 1. 2. 3. 4. 5. Open multisim software to design the circuit. Select on new editor window and place the required component on the circuit window. Make the connections using wire and check the connections properly. Go for simulation key and observe waveform on CRO. Note the frequency of oscillation and compare theoretical and practical values of oscillations.

Theoritical Frequency ,FTH = 1/2RC6 OBSERVATIONS S.No RESISTOR(ohm) CAPACITOR(F) THEORETICAL PRACTICAL FREQUENCY(Hz) FREQUENCY(Hz)

OUTPUTWAVEFORM

RESULT Thus, design of RC phase shift oscillator is verified and frequencies are compared.

16

SPHOORTHY Engg.College.

EC LAB MANUAL VIVA QUESTIONS 1. 2. 3. 4. 5. What are the conditions of oscillations? Give the formula for frequency of oscillations? What is the total phase shift produced by RC ladder network? What are the types of oscillators? What is the gain of RC phase shift oscillator?

ECE DEPARTMENT

17

SPHOORTHY Engg.College.

EC LAB MANUAL

ECE DEPARTMENT EXP. NO. 4 CLASS-A POWER AMPLIFIER(TRANSFORMERLESS)

AIM To design a class-A power amplifier and to calculate the bandwidth by using multisim software. SPECIFICATIONS 1. 2. 3. 4. 5. 6. 7. 8. 9. 220 Resistor No. 30k Resistor 1No. 100 Resistor 1 No 50k variable Resistor 1 No 10 F/ 25 V Capacitor 1 No.. Transistors BC107 1 No. CRO (Dual channel) Regulated power supply Function generator

APPARATUS 1. Multisim software 2. Personal computer CIRCUIT DIAGRAM

VCC VCC 50% 50k R3 Key=A R1 1 V1 220 120mVpk 1kHz 0 2 C1 10uF 3 R2 30k 12V R4 100 5 Q1

+ A _ + B _

XSC1

Ext T rig + _

TIP31A 0

18

SPHOORTHY Engg.College.

EC LAB MANUAL THEORY

ECE DEPARTMENT

Power amplifiers are mainly used to deliver more power to the load. To deliver more power it requires large input signals, so generally power amplifiers are preceded by a series of voltage amplifiers. In class-A power amplifiers, Q-point is located in the middle of DC-load line. So output current flows for complete cycle of input signal. Under zero signal condition, maximum power dissipation occurs across the transistor. As the input signal amplitude increases power dissipation reduces. The maximum theoretical efficiency is 25%. PROCEDURE 1. 2. 3. 4. 5. 6. 7. Open multisim software to design the circuit. Select on new editor window and place the required component on the circuit window. Make the connections using wire and check the connections of power supply and oscillator. Go for simulation using run key and observe the output waveforms on oscillator. Indicate the node names and go for AC analysis with output node. Observe the AC analysis and draw the magnitude and phase response curves. Calculate the bandwidth of the amplifier. Bandwidth f2-f1 Where f1 is Lower cutoff frequency f2 is Upper cutoff frequency

OBSERVATIONS Maximum gain in dB 3dB gain Lower cutoff frequency f1 Upper cutoff frequency f2 Bandwidth f2-f1 OUTPUTWAVEFORM = = = = =

19

SPHOORTHY Engg.College.

EC LAB MANUAL

ECE DEPARTMENT

EXPECTEDGRAPH

RESULT Thus the frequency response of a class A power amplifier is designed and band width is calculated . VIVA QUESTIONS 1. Differentiate between voltage amplifier and power amplifier 2. Why power amplifiers are considered as large signal amplifier? 3. When does maximum power dissipation happen in this circuit ?. 4. What is the maximum theoretical efficiency? 5. Sketch wave form of output current with respective input signal. 6. What are the different types of class-A power amplifiers available? 7. What is the theoretical efficiency of the transformer coupled class-A power amplifier? 8. What is difference in AC, DC load line?. 9. How do you locate the Q-point ? 10. What are the applications of class-A power amplifier?

20

SPHOORTHY Engg.College.

EC LAB MANUAL

ECE DEPARTMENT

EXP. NO. 5 CLASS-B COMPLEMENTARY-SYMMETRY POWER AMPLIFIER AIM To design a complementary-symmetry class-B push-pull power amplifier in order to achieve maximum out put AC power and efficiency and calculate its bandwidth. SPECIFICATIONS 1. 1k Resistor 1No. 2. 220k Resistor 2No. 3. 18k Resistor 2 No 4. 1 Resistor 2 No 5. 470 Resistor 1No. 6. 10 F/ 25 V Capacitor 2 No.. 7. Transistors BD 237(npn) 1 No. 8. Transistors BD 242C(pnp) 1 No 9. CRO (Dual channel) 10. Regulated power supply 11. Function generator APPARATUS 1. Multisim software 2. Personal computer CIRCUIT DIAGRAM

V1

8 R5 220k C1 5 4 10uF R7 18k 0 1k R4 7 C2 14.5 Vpk 10uF 10kHz 0 0 R8 18k 6

0 12 V XSC1

Ext T rig +

Q1 BD237 R1 2 1 1 R2 1 Q2 3 R3 470 0

+

_ A _ + B _

V3

R6 220k

BD242C

V2 12 V

21

SPHOORTHY Engg.College.

EC LAB MANUAL THEORY

ECE DEPARTMENT

Power amplifiers are designed using different circuit configuration with the sole purpose of delivering maximum undistorted output power to load. Push-pull amplifiers operating either in class-B are class-AB are used in high power audio system with high efficiency. In complementary-symmetry class-B power amplifier two types of transistors, NPN and PNP are used. These transistors acts as emitter follower with both emitters connected together. In class-B power amplifier Q-point is located either in cut-off region or in saturation region. So, that only 180o of the input signal is flowing in the output. In complementary-symmetry power amplifier, during the positive half cycle of input signal NPN transistor conducts and during the negative half cycle PNP transistor conducts. Since, the two transistors are complement of each other and they are connected symmetrically so, the name complementary symmetry has come Theoretically efficiency of complementary symmetry power amplifier is 78.5%. PROCEDURE 1. 2. 3. 4. 5. 6. 7. Open multisim software to design the circuit. Select on new editor window and place the required component on the circuit window. Make the connections using wire and check the connections of power supply and oscillator. Go for simulation using run key and observe the output waveforms on oscillator. Indicate the node names and go for AC analysis with output node. Observe the AC analysis and draw the magnitude and phase response curves. Calculate the bandwidth of the amplifier. Bandwidth f2-f1 Where f1 is Lower cutoff frequency f2 is Upper cutoff frequency

OBSERVATIONS Maximum gain in dB 3dB gain Lower cutoff frequency f1 Upper cutoff frequency f2 Bandwidth f2-f1 OUTPUTWAVEFORM = = = = =

22

SPHOORTHY Engg.College.

EC LAB MANUAL EXPECTED GRAPH

ECE DEPARTMENT

RESULT Thus the frequency response of a class B complementary symmetry power amplifier is designed and band width is calculated . VIVA QUESTIONS 1. Differentiate between voltage amplifier and power amplifier? 2. Explain impedance matching provided by transformer? 3. Under what condition power dissipation is maximum for transistor in this circuit? 4. What is the maximum theoretical efficiency? 5. Sketch current waveform in each transistor with respective input signal? 6. How do you test matched transistors required for this circuit with DMM?. 7. What is the theoretical efficiency of the complementary stage amplifier. 8. How do you measure DC and AC out put of this amplifier? 9. Is this amplifier working in class A or B. ? 10. How can you reduce cross over distortion?

23

SPHOORTHY Engg.College.

EC LAB MANUAL

ECE DEPARTMENT

EXP . NO. 6 HIGH FREQUENCY COMMON BASE(BJT) AND COMMON GATE (JFET)AMPLIFIER

COMMON BASE AMPLIFIER AIM To design and simulate the frequency response of common base amplifier by using multisim software and note down the maximum gain. SPECIFICATIONS 1. 2. 3. 4. 5. 6. 7. 8. 1k Resistor 2 No. 10k Resistor 2 No. 5K Resistor 1 No 10 F/ 25 V Electrolytic Capacitor 3 No. Transistors BC107BP 1No Function generator CRO Regulated power supply

APPARATUS 1. Multisim software 2. Personal computer CIRCUIT DIAGRAM

R1 1k 3 V3

C1 10uF 1

Q1 BC107BP

C3 10uF R3 5k 8 R5 1k

A + _

XSC1

Ext Trig + _ B + _

50mVpk 100 Hz 0

R2 10k 5 V2 10 V

6 100k R4 C2 10uF 0

V1 10 V

24

SPHOORTHY Engg.College.

EC LAB MANUAL THEORY

ECE DEPARTMENT

In common base amplifier the base lead is common to both input and output circuits and is grounded. The base emitter circuit is forward biased. The input signal is applied to emitter terminal of the transistor and amplifier output is taken across collector terminal. Frequency response of an amplifier is defined as the variation of gain with respective frequency. The gain of the amplifier increases as the frequency increases from zero till it becomes maximum at lower cut-off frequency and remains constant till higher cut-off frequency and then it falls again as the frequency increases. . PROCEDURE 1. 2. 3. 4. 5. 6. 7. Open multisim software to design the circuit. Select on new editor window and place the required component on the circuit window. Make the connections using wire and check the connections of power supply and oscillator. Go for simulation using run key and observe the output waveforms on oscillator. Indicate the node names and go for AC analysis with output node. Observe the AC analysis and draw the magnitude and phase response curves. Calculate the bandwidth of the amplifier. Bandwidth f2-f1 Where f1 is Lower cutoff frequency f2 is Upper cutoff frequency

OBSERVATIONS Maximum gain in dB OUTPUTWAVEFORM =

25

SPHOORTHY Engg.College.

EC LAB MANUAL EXPECTED GRAPH

ECE DEPARTMENT

RESULT Thus the frequency response of common base amplifier is verified and gain is analysed. VIVA QUESTIONS 1. 2. 3. 4. 5. What are the advantages and disadvantages of common base amplifier? Why the gain remains constant at MF? Define frequency response? What is the phase difference between input and output waveforms of a CB amplifier? What are the applications of CB amplifier?

26

SPHOORTHY Engg.College.

EC LAB MANUAL COMMON GATE AMPLIFIER AIM

ECE DEPARTMENT

To design and simulate the frequency response of common gate amplifier by using multisim software and note down the maximum gain. SPECIFICATIONS 1. 2. 3. 4. 5. 6. 7. 8. 4.7k Resistor 2 No. 5k Resistor 1 No. 2.2k Resistor 1 No 10 F/ 25 V Electrolytic Capacitor 3 No. FET(npn) 2N4392 1No Function generator CRO Regulated power supply

APPARATUS 1. Multisim software 2. Personal computer CIRCUIT DIAGRAM

C1 10uF 1 V1 50mVpk 100 Hz 0

2 R1 4.7k 3 V2 5V

Q1 2N4392

C2 10uF 7

R2 2.2k 4 5 R4 56k C3 10uF V3 5V R3 4.7k

+ A _

XSC1

Ext Trig + _ B + _

27

SPHOORTHY Engg.College.

EC LAB MANUAL THEORY

ECE DEPARTMENT

The FET is a type of transistor commonly used for weak signal amplification. The device can amplify analog or digital signals. It can also switch DC or function as an oscillator. In the FET current flows along a semiconductor path called the channel. At one end of the channel, there is an electrode called source. At the other end of the channel there is an electrode called the drain. Frequency response of an amplifier is defined as the variation of gain with respective frequency. The gain of the amplifier increases as the frequency increases from zero till it becomes maximum at lower cut-off frequency and remains constant till higher cut-off frequency and then it falls again as the frequency increases. PROCEDURE 1. 2. 3. 4. 5. 6. 7. Open multisim software to design the circuit. Select on new editor window and place the required component on the circuit window. Make the connections using wire and check the connections of power supply and oscillator. Go for simulation using run key and observe the output waveforms on oscillator. Indicate the node names and go for AC analysis with output node. Observe the AC analysis and draw the magnitude and phase response curves. Calculate the bandwidth of the amplifier. Bandwidth f2-f1 Where f1 is Lower cutoff frequency f2 is Upper cutoff frequency

OBSERVATIONS Maximum gain in dB OUTPUTWAVEFORM =

28

SPHOORTHY Engg.College.

EC LAB MANUAL EXPECTED GRAPH

ECE DEPARTMENT

RESULT Thus the frequency response of common base amplifier is verified and gain is analysed. VIVA QUESTIONS 1. 2. 3. 4. 5. What is the difference between FET and BJT? FET is unipolar or bipolar? Draw the symbol of FET? What are the applications of FET? FET is voltage controlled or current controlled?

29

SPHOORTHY Engg.College.

EC LAB MANUAL

ECE DEPARTMENT

EXP . NO. 7 COMMON EMITTER AMPLIFIER AND COMMON SOURCE AMPLIFIER

COMMON EMITTER AMPLIFIER AIM To study and plot the frequency response of common emitter amplifier and calculate the band width. APPARATUS 1. 1k Resistor 1 No. 2. 33k Resistor 3 No. 3. 3.3K Resistor 1 No 4. 4.7k Resistor 1 No 5. 470 Resistor 1 No 6. 10 F/ 25 V Electrolytic Capacitor 2 No. 7. 100 F/ 25 V Electrolytic Capacitor 1 No. 8. Transistors BC107 1No 9. Function generator 10. CRO 11. Regulated power supply CIRCUIT DIAGRAM

VCC VCC R4 33k 12V R5 3.3k 4 R1 1 1k 14.14mVrms 100 Hz 0 2 C1 10uF R3 4.7k Q1 3 BC107BP 7 R2 470 10uF

A + _ + B _

C3

XSC1

Ext Trig + _

5 C2 100uF 0

V1

30

SPHOORTHY Engg.College.

EC LAB MANUAL THEORY

ECE DEPARTMENT

The CE amplifier provides high gain & wide frequency response. The emitter lead is common to both input and output circuits and is grounded. The emitter base circuit is forward biased. The collector current is controlled by the base current rather than emitter current. The input signal is applied to base terminal of the transistor and amplifier output is taken across collector terminal. A very small change in base current produces a much larger change in collector current. Frequency response of an amplifier is defined as the variation of gain with respective frequency. The gain of the amplifier increases as the frequency increases from zero till it becomes maximum at lower cut-off frequency and remains constant till higher cut-off frequency and then it falls again as the frequency increases. At low frequencies the reactance of coupling capacitor CC is quite high and hence very small part of signal will pass through from one stage to the next stage. At high frequencies the reactance of inter electrode capacitance is very small and behaves as a short circuit. This increases the loading effect on next stage and service to reduce the voltage gain due to these reasons the voltage gain drops at high frequencies. At mid frequencies the effect of coupling capacitors is negligible and acts like short circuit, where as inter electrode capacitors acts like open circuit. So, the circuit becomes resistive at mid frequencies and the voltage gain remains constant during this range. PROCEDURE 1. Connect the circuit as per the circuit diagram. 2. By keeping the amplitude of the input signal constant at 40mv(p-p), vary the frequency from 100Hz to 1 MHz. 3. Note down the amplitude of the output signal for corresponding values of input frequencies. 4. Calculate the voltage gain in decibels. 5. Plot in semi-log graph between gain vs frequency and calculate the band width. OBSERVATIONS S.NO GAIN in dB= 20log(Vo/Vi)

FREQUENCY

VOUT

GAIN= VOUT /VIN

CALCULATIONS i. ii. Determine lower cut-off frequency and upper cut-off frequency from the graph. Calculate Band width.

31

SPHOORTHY Engg.College.

EC LAB MANUAL EXPECTED GRAPH

ECE DEPARTMENT

RESULT Thus, the frequency response of ce amplifier is obtained and Lower cut-off frequency = Upper cut-off frequency = Band width =

32

SPHOORTHY Engg.College.

EC LAB MANUAL

ECE DEPARTMENT

COMMON SOURCE AMPLIFIER AIM To study and plot the frequency response of common source amplifier and calculate the band width. APPARATUS 1. 1k Resistor 1 No. 2. 1M Resistor 3 No. 3. 10K Resistor 1 No. 4. 4.7k Resistor 1 No. 5. 10 F/ 25 V Electrolytic Capacitor 2 No. 6. 100 F/ 25 V Electrolytic Capacitor 1 No. 7. FET 2N4392 1No 8. Function generator 9. CRO 10. Regulated power supply CIRCUIT DIAGRAM

VDD 12V VDD R5 10k 5 10uF R1 1 1k 14.14mVrms 100 Hz 0 2 C1 10uF R3 1M 0 4 R4 4.7k C3 100uF 3 Q1 2N4392

+ A _ + B _

C2

XSC1

Ext Trig + _

V1

33

SPHOORTHY Engg.College.

EC LAB MANUAL

ECE DEPARTMENT

THEORY The FET is a type of transistor commonly used for weak signal amplification. The device can amplify analog or digital signals. It can also switch DC or function as an oscillator. In the FET current flows along a semiconductor path called the channel. At one end of the channel, there is an electrode called source. At the other end of the channel there is an electrode called the drain. Frequency response of an amplifier is defined as the variation of gain with respective frequency. The gain of the amplifier increases as the frequency increases from zero till it becomes maximum at lower cut-off frequency and remains constant till higher cut-off frequency and then it falls again as the frequency increases. At low frequencies the reactance of coupling capacitor CC is quite high and hence very small part of signal will pass through from one stage to the next stage. At high frequencies the reactance of inter electrode capacitance is very small and behaves as a short circuit. This increases the loading effect on next stage and service to reduce the voltage gain due to these reasons the voltage gain drops at high frequencies. At mid frequencies the effect of coupling capacitors is negligible and acts like short circuit, where as inter electrode capacitors acts like open circuit. So, the circuit becomes resistive at mid frequencies and the voltage gain remains constant during this range PROCEDURE 1. Connect the circuit as per the circuit diagram. 2. By keeping the amplitude of the input signal constant at 40mv(p-p), vary the frequency from 100Hz to 1 MHz. 3. Note down the amplitude of the output signal for corresponding values of input frequencies. 4. Calculate the voltage gain in decibels. 5. Plot in semi-log graph between gain vs frequency and calculate the band width. OBSERVATIONS S.NO GAIN in dB= 20log(Vo/Vi)

FREQUENCY

VOUT

GAIN= VOUT /VIN

CALCULATIONS 1. Determine lower cut-off frequency and upper cut-off frequency from the graph. 2. Calculate Band width.

34

SPHOORTHY Engg.College.

EC LAB MANUAL

ECE DEPARTMENT

EXPECTED GRAPH

RESULT Thus, the frequency response of ce amplifier is obtained and Lower cut-off frequency = Upper cut-off frequency = Band width =

35

SPHOORTHY Engg.College.

EC LAB MANUAL

ECE DEPARTMENT

EXP . NO. 8 TWO STAGE RC-COUPLED AMPLIFIER AIM To study the frequency response of a two stage RC-coupled amplifier and calculation of gain and band width. APPARATUS 1. 2.2k Resistor 1 No. 2. 150k Resistor 1No. 3. 22k Resistor 1 No 4. 10k Resistor 1 No 5. 560 Resistor 1 No 6. 4.7k Resistor 3No. 7. 47k Resistor 1 No. 8. 33k Resistor 1 No 9. 220 Resistor 1 No 10. 10 F/ 25 V Electrolytic Capacitor 5 No. 11. Transistors BC107 2 No. 12. CRO (Dual channel) 13. Regulated power supply 14. Function generator CIRCUIT DIAGRAM

VCC VCC R3 150k 10k R4 C2 9 R1 2.2k 2 V1 14.14mVrms 100 Hz 0 C4 10uF 4 Q1 10uF 11 10 Q2 5 BC107BP 6 R8 560 R2 22k 7 R11 4.7k C3 10uF BC107BP 1 220 R10 R7 33k 8 R6 4.7k C1 10uF 0

+ Ext T rig + _ A _ + B _

12V R5 47k R9 4.7k C5 10uF XSC1

36

SPHOORTHY Engg.College.

EC LAB MANUAL THEORY

ECE DEPARTMENT

As the gain provided by a single stage amplifier is usually not sufficient to drive the load, so to achieve extra gain multi-stage amplifier are used. In multi-stage amplifiers output of one-stage is coupled to the input of the next stage. The coupling of one stage to another is done with the help of some coupling devices. If it is coupled by RC then the amplifier is called RC-coupled amplifier. Frequency response of an amplifier is defined as the variation of gain with respective frequency. The gain of the amplifier increases as the frequency increases from zero till it becomes maximum at lower cut-off frequency and remains constant till higher cut-off frequency and then it falls again as the frequency increases. At low frequencies the reactance of coupling capacitor CC is quite high and hence very small part of signal will pass through from one stage to the next stage. At high frequencies the reactance of inter electrode capacitance is very small and behaves as a short circuit. This increases the loading effect on next stage and service to reduce the voltage gain due to these reasons the voltage gain drops at high frequencies. At mid frequencies the effect of coupling capacitors is negligible and acts like short circuit, where as inter electrode capacitors acts like open circuit. So, the circuit becomes resistive at mid frequencies and the voltage gain remains constant during this range. PROCEDURE 1. Connect the circuit as per the circuit diagram. 2. By keeping the amplitude of the input signal constant, vary the frequency from zero to 1 MHz. 3. Note down the amplitude of the output signal for corresponding values of input frequencies. 4. Calculate the voltage gain in decibels. 5. Plot in semi-log graph between gain vs frequency and calculate the band width. OBSERVATIONS S.NO GAIN in dB= 20log(Vo/Vi)

FREQUENCY

VOUT

GAIN= VOUT /VIN

CALCULATIONS 1. Determine lower cut-off frequency and upper cut-off frequency from the graph. 2. Calculate Band width.

37

SPHOORTHY Engg.College.

EC LAB MANUAL EXPECTED-GRAPH

ECE DEPARTMENT

RESULT Thus, the frequency response of ce amplifier is obtained and Lower cut-off frequency = Upper cut-off frequency = Band width =

38

SPHOORTHY Engg.College.

EC LAB MANUAL EXP . NO. 9 RC PHASE SHIFT OSCILLATOR AIM

ECE DEPARTMENT

To design an RC phase shift oscillator and compare theoritical and practical frequency of oscillations. APPARATUS 1. 2. 3. 4. 5. 6. 7. 8. 9. 10k Resistor 3No. 47k Resistor 1No. 2.2k Resistor 1 No 1k Resistor 1 No 100 F/ 25 V Electrolytic Capacitor 1 No. 1nF/47nF Capacitors 3 each. Transistors BC107 1 No. CRO (Dual channel) Regulated power supply

CIRCUIT DIAGRAM

R5 47k C1 1nF C3 1nF R2 10k C2 1nF R4 10k R3 10k

2 R6 2.2k

V1 12 V 0

XSC1 Q1

Ext Trig + _ A + _ + B _

3 BC107BP 4 R1 C4 100uF 1k 0

39

SPHOORTHY Engg.College.

EC LAB MANUAL THEORY

ECE DEPARTMENT

RC phase shift oscillator has a CE amplifier followed by three sections of RC phase shift feedback networks. The output of the last stage is return to the input of the amplifier.the values of R and C are chosen such that the phase shift of each RC section is 600.thus,the RC ladder network produces a total phase shift of 1800 between its input and output voltage for the given frequencies.since CE amplifier produces 1800 phase shift the total phase shift from the base of the transistor around the circuit and back to the transistor will be exactly 3600 or 00.The frequency of oscillation is given by F = 1/2RC6 PROCEDURE 1. Connect the circuit as per the circuit diagram. 2. Observe the output signal and note down the output amplitude and time period. 3. Calculate the frequency of oscillations theoretically and verify it practically. Theoretical Frequency FTH = 1/2RC6. OBSERVATIONS S.No RESISTOR(ohm) CAPACITOR(F) THEORETICAL PRACTICAL FREQUENCY(Hz) FREQUENCY(Hz)

RESULT Thus, theoretical and practical frequencies of RC phase shift oscillator are compared.

40

SPHOORTHY Engg.College.

EC LAB MANUAL

ECE DEPARTMENT

EXP. NO. 10 TUNED VOLTAGE AMPLIFIER AIM To Obtain the Frequency Response of Single Tuned Voltage Amplifier. APPARATUS 1.Trainer Kit FT 18122.CRO 20 MHz 3.Function generator ! MHz 4.Connecting Wires CIRCUIT DIAGRAM

VCC 12V VCC L1 140mH R3 10k C1 3 V1 100nF C4 100nF C3 4 Q1 2 BC107BP 1 R1 4.7k R2 10k C2 1uF 10uF 5

A + _ + B _ Ext T rig + _

1 No 1 No 1 No.

XSC1

35.36mVrms 1.5kHz 0

THEORY Single tuned Amplifier uses one parallel Tuned Circuit as a load in each stage with Tuned circuit s in all stages tuned the same frequency .Ass shown in the fig.Tuned circuit formed by L and C elements acts as collector load and resonates at frequency of operation. Resistors R1 R2 and Re along with Capacitor Ce provides self bias for the circuit. The function of resonant circuits are: 1. To provide correct load impedance to the amplifier. 2. To reject unwanted harmonics. 41 SPHOORTHY Engg.College.

EC LAB MANUAL 3.To couple the power to load The resonant circuits in tuned power amplifier are called tank circuits. PROCEDURE

ECE DEPARTMENT

1. Connect the circuit as shown in diagram. 2. The input signal of 50mv(p-p) at 1kHz is applied from function generator and output terminals are connected to CRO. 3. Adjust the input frequency such that output voltage is a perfect since sinusoidal waveform at a fixed frequency.. 4. Note down corresponding output voltages at different frequencies. 5. Plot the waveforms of both input and output 6. The frequency at which the voltage is max , should be compared with theoretical values. Theoretical Resonant frequency F=1/2LC OBSERVATIONS S.NO FREQUENCY VOUT GAIN= VOUT /VIN GAIN in dB= 20log(Vo/Vi)

The value of Resonant frequency at which maximum gain occurred is _________. CALCULATIONS Theoretical value of resonant frequency =____________________ EXPECTED GRAPH

42

SPHOORTHY Engg.College.

EC LAB MANUAL RESULT

ECE DEPARTMENT

Thus, the frequency response of tuned voltage amplifier is obtained and the maximum resonant frequency is _________.

43

SPHOORTHY Engg.College.

EC LAB MANUAL

ECE DEPARTMENT EXP.NO. 11 SERIES VOLTAGE REGULATOR

AIM To design a transistorized series voltage regulator and study the regulation action for i. Different values of input voltages ii. Different values of load resistors and also to find percentage regulation. APPARATUS 1. 2. 3. 4. 5. 6. 7. Bread Board- 1 No. . Regulated power supply- (0-30)V -1 No. DVM (0-20)V - 1No 1k Resistor - 1 No. Zener diode(BZ8V2) - 1 No Transistor ( SL100 ) - 1 No DRB. -1 No

CIRCUIT DIAGRAM

THEORY Voltage regulator is a device designed to maintain the output voltage as nearly constant as possible. It monitors the output voltage and generates feed back that automatically increases are decreases the supply voltage to compensate for any changes in output voltage that might occur because of change in load are changes in load voltages. In transistorized series voltage regulator the control element is a transistor which is in series with load. must be operated in reverse break down region, where it provides constant voltage irrespective of changes in applied voltages.The output voltage of the series voltage regulator is Vo = Vz Vbe. Since, Vz is constant, any change in Vo must cause a change in Vbe in order to maintain the above equation. So, when Vo decreases Vbe increases, which causes the transistor to conduct 44 SPHOORTHY Engg.College.

EC LAB MANUAL

ECE DEPARTMENT

more and to produce more load current, this increase in load causes an increase in Vo and makes Vo as constant. Similarly, the regulation action happens when Vo increases. PROCEDURE 1. Connect the circuit as shown in the circuit diagram. 2. Apply the input voltage from power supply. 3. For a specific value of load resistor, vary the input voltage from 10 to a maximum of 20 volts and not the values of output voltage. 4. Change the load resistor and repeat steps 2 and 3. 5. Remove the load resistor and note down the voltage at no load. V VFL 6. Find percentage regulation.Percentage regulation = NL x100 VFL 7. Plot the graph for load regulation and line regulation. OBSERVATIONS Load Regulation Load resistance RL(kohm) Output Voltage,V0(V) Line Regulation Line Voltage,Vin(V) Output Voltage,V0(V)

CALCULATIONS Percentage load regulation =

V NL V FL x100 = VFL

Percentage Line Regulation = (change in output ) / (change in input) X 100

45

SPHOORTHY Engg.College.

EC LAB MANUAL GRAPH

ECE DEPARTMENT

RESULT For RL = ----------------, Regulation range is____________ For VL = ----------------, Regulation range is____________ VIVA QUESTIONS 1. Define voltage regulator. 2. Give the advantages of series voltage regulator. . 3. Explain the feed back mechanism in series voltage regulator. 4. In series voltage regulator which is control element and explain its function. 5. Define load and line regulation. What is ideal value ?. 6. Which element determines output ripple ? 7. What determines maximum load current allowed in this circuit ? 8. Mention the applications of series voltage regulator. 9. Define no load voltage and full load voltage. 10. Explain the term percentage regulation.

46

SPHOORTHY Engg.College.

EC LAB MANUAL EXP .NO. 12

ECE DEPARTMENT

SHUNT VOLTAGE REGULATOR

AIM To design a transistorized shunt voltage regulator and observing the regulation action for 1. Different values of input voltages 2. Different values of load resistors and also to find percentage regulation. APPARATUS 1. 2. 3. 4. 5. 6. 7. Bread Board - 1 No. . Regulated power supply- 0-30v - 1 No. DVM(0-20)V - 1No 1k Resistor - 1 No. Zener diode BZ8V2 - 1No. Transistor SL100 1No. DRB -1No

CIRCUIT DIAGRAM

47

SPHOORTHY Engg.College.

EC LAB MANUAL THEORY

ECE DEPARTMENT

A voltage regulator is a device or a combination of devices, design to maintain the output voltage of a power supply as nearly constant as possible even if there are changes in load or in input voltage. In shunt voltage regulator transistor Q1 acts as control element, which is in shunt with load voltage. The output voltage is given as Vo = Vz + VR1 = Vz + Vbe1 + Vbe2 The regulation action of the circuit is explained below : Since Vz is constant, any changes in output voltage reflects a propositional change in R1. If the output voltage decreases, voltage across R1 decreases which in turn decreases the base voltage of Q2. As a result the base current of Q1 decreases which allows the load voltage to rise and makes it constant the same regulation action follows even if the output voltage increases. PROCEDURE 1. Connect the circuit as shown in the circuit diagram. 2. Apply the input voltage from power supply. 3. For a specific value of load resistor, vary the input voltage from zero to a maximum of 20 volts and note the values of output voltage. 4. Change the load resistor and repeat steps 2 and 3. 5. Remove the load resistor and note down the voltage at no load. 6. Find percentage regulation. V VFL 7. Percentage regulation = NL x100 VFL 8. Plot the graph for load regulation and line regulation. OBSERVATIONS Line Regulation Line Output Voltage,Vin(V) Voltage,V0(V) Load Regulation

48

SPHOORTHY Engg.College.

EC LAB MANUAL

Load Output resistance Voltage,V0(V) RL(kohm) ECE DEPARTMENT

CALCULATIONS

V NL V FL x100 VFL Line Regulation = Change in Vo Change in Vi

Percentage regulation = GRAPH

RESULT For RL = ----------------, Regulation range is____________ For VL = ----------------, Regulation range is____________ VIVA QUESTIONS 1. Mention the differences between shunt and series voltage regulators. 2. What is the function of Q1 and Q2 in the shunt regulator .circuit ? 3. Define the line regulation. And load regulation. 4. What is current through zener in this circuit ? 5. When is dissipation maximum in this circuit ? 6. In the circuit of shunt voltage regulator which element is considered control 7. element and explain its function. 8. Can you do the experiment without Q2 ?. 9. How can you increase current range of regulator ? 10. If output is 1.4 v for input of 20v what was the wrongly connected ? 11. Mention the applications of shunt voltage regulator. 49 SPHOORTHY Engg.College.

EC LAB MANUAL

ECE DEPARTMENT

50

SPHOORTHY Engg.College.

Вам также может понравиться

- Eca Lab Manual PDFДокумент56 страницEca Lab Manual PDFrppvch100% (5)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Оценок пока нет

- Expt 6Документ3 страницыExpt 6sabitavabiОценок пока нет

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Рейтинг: 2.5 из 5 звезд2.5/5 (3)

- 2 Two Stage RC Coupled AmplifierДокумент7 страниц2 Two Stage RC Coupled AmplifierdamasОценок пока нет

- Eca Lab ManualДокумент78 страницEca Lab ManualNageswariah.MОценок пока нет

- Eca Lab-Min PDFДокумент87 страницEca Lab-Min PDFAkashita SharmaОценок пока нет

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsОт EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsРейтинг: 3.5 из 5 звезд3.5/5 (6)

- ECA ManualДокумент50 страницECA ManualkrajenderreddyОценок пока нет

- Sharmi ECE a-D-Circuits Lab ManualДокумент74 страницыSharmi ECE a-D-Circuits Lab ManualSharmila83Оценок пока нет

- Lab Manual AECДокумент20 страницLab Manual AECDynmc ThugzОценок пока нет

- CE AmplifierДокумент3 страницыCE AmplifierhimeshemraanОценок пока нет

- Ae Hardware PDFДокумент55 страницAe Hardware PDFIshani JhaОценок пока нет

- Adc Lab Manual PDFДокумент74 страницыAdc Lab Manual PDFJega Deesan75% (4)

- AEC LabManualДокумент30 страницAEC LabManualPrateek PaliwalОценок пока нет

- RC CoupledДокумент3 страницыRC CoupledRavi TejaОценок пока нет

- EDC II Lab ManualДокумент46 страницEDC II Lab Manualshreeyak841Оценок пока нет

- ECA ManualДокумент62 страницыECA ManualAnonymous gP8ivl7fОценок пока нет

- Electronic Devices and Circuit LabДокумент30 страницElectronic Devices and Circuit LabAОценок пока нет

- Ao Lab Report 5Документ7 страницAo Lab Report 5Umar Ali BaigОценок пока нет

- Analog Circuits Lab Manual: Atria Institute of TechnologyДокумент60 страницAnalog Circuits Lab Manual: Atria Institute of TechnologyTháHäKâduvàyîLzОценок пока нет

- 566 LIC Expt 2Документ22 страницы566 LIC Expt 2Hrivu Dasmunshi (RA1911004010566)Оценок пока нет

- AnalogIntegratedCircuts LAB MANUAL by Prabhu Kumar SurarapuДокумент80 страницAnalogIntegratedCircuts LAB MANUAL by Prabhu Kumar Surarapuprabhu4scribdОценок пока нет

- IC and ECAD LabДокумент88 страницIC and ECAD LabVeerayya JavvajiОценок пока нет

- Wein Bridge Oscillator: f =1/2π√R1C1R2C2Документ11 страницWein Bridge Oscillator: f =1/2π√R1C1R2C2krishna goggiОценок пока нет

- ECE3204 D2013 Lab2Документ9 страницECE3204 D2013 Lab2Khalil2097Оценок пока нет

- Amplifiers and OscillatorsДокумент109 страницAmplifiers and OscillatorsAdilОценок пока нет

- Integrator Circuits: 7.0.1 ReadingДокумент5 страницIntegrator Circuits: 7.0.1 Readingnaveenkv10_105528408Оценок пока нет

- Integrator DiffentiatorДокумент7 страницIntegrator Diffentiatorআব্দুল্লাহ আল ইমরানОценок пока нет

- Ecd LR - 8Документ10 страницEcd LR - 8Faaran Ahmed Zaheer AhmedОценок пока нет

- Mulvaney Graham 352 Lab 1Документ6 страницMulvaney Graham 352 Lab 1api-125239608Оценок пока нет

- AKNM - 3049 - AKNMGptcДокумент53 страницыAKNM - 3049 - AKNMGptchod eceОценок пока нет

- LINEAR INTEGRATED CIRCUIT LAB MANUAL by PRABHU PDFДокумент76 страницLINEAR INTEGRATED CIRCUIT LAB MANUAL by PRABHU PDFprabhu4scribd100% (5)

- Analog and Digital Ic'S Short Questions With AnswersДокумент41 страницаAnalog and Digital Ic'S Short Questions With Answerspriya adhavanОценок пока нет

- LIC Manual PDFДокумент55 страницLIC Manual PDFmekalajesiОценок пока нет

- AEC Lab ManualДокумент70 страницAEC Lab ManualRohan BoseОценок пока нет

- Basic ElectronicsДокумент126 страницBasic ElectronicsFarazОценок пока нет

- Ex05 Lim OpampДокумент9 страницEx05 Lim OpampLIM Sheryl M.Оценок пока нет

- ECE - Lab ReportsДокумент58 страницECE - Lab ReportsSamОценок пока нет

- Lab 9Документ7 страницLab 9Salman AliОценок пока нет

- Aec Lab ManualДокумент17 страницAec Lab ManualprofharishjoshiОценок пока нет

- Linear Wave Shaping: Department of Electronics and Communication EngineeringДокумент0 страницLinear Wave Shaping: Department of Electronics and Communication EngineeringanishadandaОценок пока нет

- Fermin Energy LevelДокумент13 страницFermin Energy LevelSemiu AdelekeОценок пока нет

- LIC Question BankДокумент7 страницLIC Question BankParvathy S ParvathyОценок пока нет

- Experiment 04 Common Source Amplifier Name: DateДокумент5 страницExperiment 04 Common Source Amplifier Name: DateJuay Mae RianoОценок пока нет

- Basic Electronics Course Lab WorkbookДокумент103 страницыBasic Electronics Course Lab WorkbookApril ShowersОценок пока нет

- RC Phase Shift Oscillator and RC Coupled Ce Amplifier - Lab ExperimentДокумент8 страницRC Phase Shift Oscillator and RC Coupled Ce Amplifier - Lab ExperimentMani BharathiОценок пока нет

- Elvis and Bode PlotsДокумент7 страницElvis and Bode PlotsKashif AmjadОценок пока нет

- Ac Lab Manual NewДокумент52 страницыAc Lab Manual NewKranthi KumarОценок пока нет

- Ae Exp 5 Student ManualДокумент4 страницыAe Exp 5 Student ManualAIОценок пока нет

- Slyt155 - An Audio Circuit Collection 1Документ6 страницSlyt155 - An Audio Circuit Collection 1EduardoSánchezОценок пока нет

- Lic QB - 2 Marks Unit I & IiДокумент7 страницLic QB - 2 Marks Unit I & Iisanthosh sekarОценок пока нет

- Lab#9 (Common Emitter Amplifier)Документ6 страницLab#9 (Common Emitter Amplifier)Muhammad HamzaОценок пока нет

- Scan Design and Secure Chip: 2.1. ControllabilityДокумент6 страницScan Design and Secure Chip: 2.1. ControllabilityShrinivas SaptalakarОценок пока нет

- Test Planning and Test Access Mechanism Design For 3D SicsДокумент6 страницTest Planning and Test Access Mechanism Design For 3D SicsShrinivas SaptalakarОценок пока нет

- Encounter Conformal Low Power Datasheet PDFДокумент4 страницыEncounter Conformal Low Power Datasheet PDFShrinivas SaptalakarОценок пока нет

- Modified March C - Algorithm For Embedded Memory TestingДокумент6 страницModified March C - Algorithm For Embedded Memory TestingShrinivas SaptalakarОценок пока нет

- Writing Test BenchДокумент20 страницWriting Test BenchNitesh MittalОценок пока нет

- Art of Writing TestBenchesДокумент14 страницArt of Writing TestBenchesShrinivas SaptalakarОценок пока нет

- Logic Built-In Self TestДокумент76 страницLogic Built-In Self TestShrinivas SaptalakarОценок пока нет

- IJERT Paper TemplateДокумент3 страницыIJERT Paper TemplateShrinivas Saptalakar0% (1)

- Chapter 1Документ19 страницChapter 1Shrinivas SaptalakarОценок пока нет

- Performance Comparison of Multipliers For Power-Speed Trade-Off in VLSI DesignДокумент5 страницPerformance Comparison of Multipliers For Power-Speed Trade-Off in VLSI DesignShrinivas SaptalakarОценок пока нет

- Application of Elliptic Curve Cryptography On Data Encryption Over A NetworkДокумент4 страницыApplication of Elliptic Curve Cryptography On Data Encryption Over A NetworkShrinivas SaptalakarОценок пока нет

- Switching Regulator Applications: Absolute Maximum RatingsДокумент6 страницSwitching Regulator Applications: Absolute Maximum RatingsIvanilto Martins da CruzОценок пока нет

- 2N3819 JFET VHF/UHF AmplifierДокумент8 страниц2N3819 JFET VHF/UHF AmplifierJaysonОценок пока нет

- Experiment 0 1: Software Used TheoryДокумент18 страницExperiment 0 1: Software Used TheoryUjjaval Electronics parkОценок пока нет

- Chapter 9 - Single Transistor Amplifier Stages - (Analog Devices Wiki)Документ24 страницыChapter 9 - Single Transistor Amplifier Stages - (Analog Devices Wiki)Himanshu KumarОценок пока нет

- 2N5911 Datasheet Rev BДокумент2 страницы2N5911 Datasheet Rev BytnateОценок пока нет

- CMOS Amplifiers - Problems PDFДокумент20 страницCMOS Amplifiers - Problems PDFAnurag AnandОценок пока нет

- 13 MOSFET AmplifierДокумент1 страница13 MOSFET AmplifierAbhishek PandeyОценок пока нет

- Relay Drive, DC-DC Converter and Motor Drive Applications: Absolute Maximum RatingsДокумент6 страницRelay Drive, DC-DC Converter and Motor Drive Applications: Absolute Maximum RatingsRr hardiyantoОценок пока нет

- Lecture 8 - Multistage AmplifiersДокумент43 страницыLecture 8 - Multistage AmplifiersRanjan KarkiОценок пока нет

- Sub Harmonic MixerДокумент7 страницSub Harmonic MixerMukthaPadakandlaОценок пока нет

- Homework 2Документ8 страницHomework 2A.A.RON33% (3)

- K13A50D TransistorДокумент6 страницK13A50D TransistorVictor Hugo Flores IsunzaОценок пока нет

- Electronis 2 PDFДокумент14 страницElectronis 2 PDFMarco ReusОценок пока нет

- Electronics Circuits Analysis and Design: Prepared By: Engr. Maurine C. Panergo AY 2020-2021Документ149 страницElectronics Circuits Analysis and Design: Prepared By: Engr. Maurine C. Panergo AY 2020-2021MARINELA CademiaОценок пока нет

- 2N3819 PDFДокумент5 страниц2N3819 PDFDeni KhanОценок пока нет

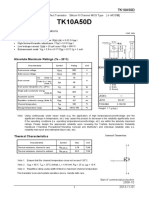

- TK10A50D: Switching Regulator ApplicationsДокумент6 страницTK10A50D: Switching Regulator Applicationsfiuxy webОценок пока нет

- Electronic II Lab ManualДокумент0 страницElectronic II Lab ManualSriram Chandrasekar100% (2)

- Electronic Devices and Circuit TheoryДокумент30 страницElectronic Devices and Circuit TheoryIñaki Zuriel ConstantinoОценок пока нет

- EC8661 VLSI Design Lab Manual Regulation 2017 Anna University, ChennaiДокумент43 страницыEC8661 VLSI Design Lab Manual Regulation 2017 Anna University, ChennaiDarwin75% (8)

- D2011KДокумент2 страницыD2011KGilmar Ferreira67% (3)

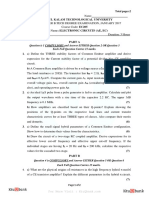

- KTU EC205 ELECTRONIC CIRCUITS (AE, EC) - MAin - Jan - 2017 - Ktu Qbank-MergedДокумент16 страницKTU EC205 ELECTRONIC CIRCUITS (AE, EC) - MAin - Jan - 2017 - Ktu Qbank-MergedsunОценок пока нет

- Fet RF Amplifier Design TechniquesДокумент5 страницFet RF Amplifier Design TechniqueshsongunОценок пока нет

- Fet (2014) PDFДокумент87 страницFet (2014) PDFJoanne Mendoza IlaoОценок пока нет

- Evaluation Scheme & Syllabus For B. Tech. Second Year (Electronics and Communication Engineering)Документ41 страницаEvaluation Scheme & Syllabus For B. Tech. Second Year (Electronics and Communication Engineering)UMANG JAISWAL IET LucknowОценок пока нет

- A 2-10 GHZ Digital Cmos Phase Shifter For Ultra-Wideband Phased Array SystemДокумент4 страницыA 2-10 GHZ Digital Cmos Phase Shifter For Ultra-Wideband Phased Array SystemHuy LuongОценок пока нет

- Zvp3306a 77267Документ4 страницыZvp3306a 77267nemoneoОценок пока нет

- MRF186 MotorolaДокумент8 страницMRF186 MotorolaRoiser DelgadoОценок пока нет

- Design Methdology For Differential Pair and Operational Transconductance AmplifierДокумент18 страницDesign Methdology For Differential Pair and Operational Transconductance AmplifierjitendraОценок пока нет

- Design of Common Source Amplifier: September 2016Документ7 страницDesign of Common Source Amplifier: September 2016Trọng HùngОценок пока нет