Академический Документы

Профессиональный Документы

Культура Документы

Asynchronous FIFO

Загружено:

Roshan KumarАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Asynchronous FIFO

Загружено:

Roshan KumarАвторское право:

Доступные форматы

Asynchronous FIFO

Feb-15-2012

Ads by Google

Verilog

Verilog VHDL

Verilog FPGA

HDL Verilog

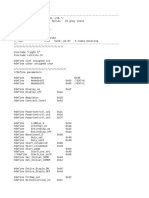

Asynchronous FIFO Note: This code is written in Verilog 2001.

1 //==========================================

: Asynchronous FIFO (w/ 2 asynchronous clocks). : Alex Claros F. 4 // Date : 15/May/2005. 5 // Notes : This implementation is based on the article 6 // 'Asynchronous FIFO in Virtex-II FPGAs' 7 // writen by Peter Alfke. This TechXclusive 8 // article can be downloaded from the 9 // Xilinx website. It has some minor modifications. 1 //========================================= 0

3 // Coder

2 // Function

Enter tutorial you want to buy

1 1 1 `timescale 1 s 1 s 2 n/p 1 3 1 module a i o 4 Ff 1 5 1 6 1 7 1 8 1 9 2 0 2 1 2 2 2 3 2 4 2 5 2 6 2 7 2 8 2 9 3 0 3 1 3 3 3 4 3 5 3 6 3 7 3 8 3 9 4 0 4 2 4 3 4 4 4 5 4 6 4 7 4 8 4 9 5 0 5 1 5 2 5 3 5 4 5 5 5 6 5 7 5 8 5 9 6 0 6 1 6 2 6 3 # parameter ( DT_IT AAWDH

=8 ,

A D E S W D H= 4 DRS_IT , FF_ET IODPH =( < ADESWDH) 1 < DRS_IT) //Reading port ( output reg [ A A W D H 1 0 DT_IT-:] Dt_u, aaot output reg Epyot mt_u, input wire RaE_n edni, input wire Rl, Ck //Writing port. input wire [ A A W D H 1 0 DT_IT-:] Dt_n aai, output reg Fl_u, ulot input wire Wieni, rtE_n input wire Wl, Ck

Ads by Google

Verilog Verilog VHDL Verilog FPGA

input wire // 3 2 wire wire wire wire reg wire reg

[AAWDH10 DT_IT-:]

Ceri) la_n; Mm[IODPH10; e FF_ET-:] petodort,petodoed NxWrTWie NxWrTRa; Euldrse; qaAdess NxWiedrsE,NxRaAdesn etrtAdesn eteddrsE; StSau,RtSau; e_tts s_tts Sau; tts PeeFl,PeeEpy rstul rstmt;

[DRS_IT-:] ADESWDH10

// 4 1 //Data ports logic: //(Uses a dual-port RAM). //'Data_out' logic: always @ ( posedge R l ) Ck if ( e d n i & ! E p y o t RaE_n mt_u) D t _ u <= M m p e t o d o e d ; aaot e[NxWrTRa] //'Data_in' logic: always @ ( posedge W l ) Ck if ( r t E _ n& ! F l _ u ) Wieni ulot M m p e t o d o r t ] <= D t _ n e[NxWrTWie aai; //Fifo addresses support logic: //'Next Addresses' enable logic: assign N x W i e d r s E = W i e n i & ~F l _ u ; etrtAdesn rtE_n ulot assign N x R a A d e s n = R a E _ n & ~E p y o t eteddrsE edni mt_u; //Addreses (Gray counters) logic:

GaCutrGaCutrpr ryone ryone_W (GaCutotpetodort) .ryon_u(NxWrTWie, .nbei(etrtAdesn, Eal_nNxWiedrsE) .la_nCeri) Ceri(la_n,

www.asic-world.com/examples/verilog/asyn_fifo.html

1/3

6 3 6 4 6 5 6 6 6 7 6 8 6 9 7 0 7 1 7 2 7 3 7 4 7 5 7 6 7 7 7 8 7 9 8 0 8 2 8 3 8 5 8 6 8 7 8 8 8 9 9 0 9 1 9 2 9 3 9 4 9 5 9 6 9 7 9 8 9 9 10 0 11 0 12 0 13 0 14 0 15 0 16 0 17 0 18 0

.la_nCeri) Ceri(la_n, .l(Ck CkWl) ) ; GaCutrGaCutrpd ryone ryone_R (GaCutotpetodoed, .ryon_u(NxWrTRa) .nbei(eteddrsE) Eal_nNxRaAdesn, .la_nCeri) Ceri(la_n, .l(Ck CkRl) ) ;

//'EqualAddresses' logic: assign E u l d r s e = ( N x W r T W i e == p e t o d o e d ; qaAdess petodort NxWrTRa) //'Quadrant selectors' logic: assign S t S a u = ( N x W r T W i e A D E S W D H 2 ~^ p e t o d o e d A D E S W D H 1 )& e_tts petodort[DRS_IT-] NxWrTRa[DRS_IT-] assign R t S a u = ( N x W r T W i e A D E S W D H 2 ^ p e t o d o e d A D E S W D H 1 )& s_tts petodort[DRS_IT-] NxWrTRa[DRS_IT-] //'Status' latch logic: always @ ( e _ t t s R t S a u , C e r i ) //D Latch w/ Asynchronous Clear & Preset. StSau, s_tts la_n if ( s _ t t s | C e r i ) RtSau la_n S a u = 0 //Going 'Empty'. tts ; else if ( e _ t t s StSau) S a u = 1 //Going 'Full'. tts ; //'Full_out' logic for the writing port: assign P e e F l = S a u & E u l d r s e ; //'Full' Fifo. rstul tts qaAdess always @ ( posedge W l , posedge P e e F l ) //D Flip-Flop w/ Asynchronous Preset. Ck rstul if ( r s t u l PeeFl) F l _ u <= 1 ulot ; else F l _ u <= 0 ulot ; //'Empty_out' logic for the reading port: assign P e e E p y= ~S a u & E u l d r s e ; //'Empty' Fifo. rstmt tts qaAdess always @ ( posedge R l , posedge P e e E p y //D Flip-Flop w/ Asynchronous Preset. Ck rstmt) if ( r s t m t ) PeeEpy E p y o t <= 1 mt_u ; else E p y o t <= 0 mt_u ;

8 1 8 4

19 0 10 1 1 1 endmodule 1

You could download file aFifo.v here

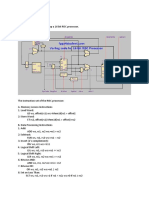

1 //========================================== 2 // Function 3 // Coder

: Code Gray counter. : Alex Claros F. 4 // Date : 15/May/2005. 5 //=======================================

6 7 `timescale 1 s 1 s n/p 8 9 module G a C u t r ryone 1 0 1 1 1 2 1 3 1 4 1 5 1 6 1 7 1 8 1 9 2 1 2 2 2 4 2 5 2 6 2 7 2 8 2 9 # parameter ( ( output C U T R W D H= 4 ONE_IT ) [ONE_IT-:] CUTRWDH10 GaCutot ryon_u, Eal_n nbei, Ceri, la_n Ck; l) [ONE_IT-:] CUTRWDH10 BnrCut iayon;

reg

//'Gray' code count output.

input wire input wire input wire // 2 0 reg

//Count enable. //Count reset.

www.asic-world.com/examples/verilog/asyn_fifo.html

// 2 3 always @ ( posedge C k l) if ( l a _ n begin Ceri) B n r C u t <= { O N E _ I T { ' 0 }+ 1 //Gray count begins @ '1' with iayon CUTRWDH1b } ; G a C u t o t <= { O N E _ I T { ' 0 } ryon_u CUTRWDH1b }; // first 'Enable_in'. end else if ( n b e i ) begin Eal_n

2/3

2 9 3 0 3 1 3 2

else if ( n b e i ) begin Eal_n B n r C u t <= B n r C u t+ 1 iayon iayon ; G a C u t o t <= { i a y o n [ O N E _ I T - ] ryon_u BnrCutCUTRWDH1,

BnrCutCUTRWDH20 ^BnrCutCUTRWDH11} iayon[ONE_IT-:] iayon[ONE_IT-:];

3 3 end 3 4 3 endmodule 5

You could download file GrayCounter.v here

Design and verification

Modern programming environment for e, SystemVerilog, Verilog

www.DVTEclipse.com

Copyright 1998-2012 Deepak Kumar Tala - All rights reserved Do you have any Comment? mail me at:deepak@asic-wor

www.asic-world.com/examples/verilog/asyn_fifo.html

3/3

Вам также может понравиться

- File: D:/Automation/oz8/ozonend.c, Date: 7/28/2011, Time: 4:20:33 PMДокумент20 страницFile: D:/Automation/oz8/ozonend.c, Date: 7/28/2011, Time: 4:20:33 PMPhan Truong HaiОценок пока нет

- FifoДокумент5 страницFifoVenky KoolchipОценок пока нет

- Experiment No: 11 Design of 10 Bit Shift Register AIMДокумент8 страницExperiment No: 11 Design of 10 Bit Shift Register AIMPraveen KumarОценок пока нет

- CodemauДокумент8 страницCodemauTiến Bùi ĐìnhОценок пока нет

- Tutorial Week 5 AnswersДокумент8 страницTutorial Week 5 Answerspotato moon berryОценок пока нет

- Verilog Modules For Common Digital FunctionsДокумент30 страницVerilog Modules For Common Digital Functionselle868Оценок пока нет

- #Define #Define #Define #Define #Define #Define #Define #DefineДокумент6 страниц#Define #Define #Define #Define #Define #Define #Define #Defineอํานาจ จันทรОценок пока нет

- AppendicesДокумент5 страницAppendicesRyan Ceasar MianoОценок пока нет

- ERC16064-1 DemoCode 4 Wire SPIДокумент19 страницERC16064-1 DemoCode 4 Wire SPIDVTОценок пока нет

- Codigo LCD C ModificadoДокумент3 страницыCodigo LCD C ModificadoMartinQuintanaCasusol100% (1)

- Keyboard - C: Programa en C USB PIC18FДокумент11 страницKeyboard - C: Programa en C USB PIC18FLuis GonzalesОценок пока нет

- Scilab Manual For Electronics Design Automation LAB by Prof Shanu N Electronics Engineering College of Engineering AttingalДокумент14 страницScilab Manual For Electronics Design Automation LAB by Prof Shanu N Electronics Engineering College of Engineering AttingalBinsi KedaramОценок пока нет

- Lab 13Документ11 страницLab 13ubaidОценок пока нет

- Lap Trinh He Thong Nhung - Bui Quoc Bao - Codemau (Cuuduongthancong - Com) Đã G P Đã G PДокумент91 страницаLap Trinh He Thong Nhung - Bui Quoc Bao - Codemau (Cuuduongthancong - Com) Đã G P Đã G PKhánh Trịnh MinhОценок пока нет

- Lap-Trinh-He-Thong-Nhung - Bui-Quoc-Bao - Codemau - (Cuuduongthancong - Com)Документ8 страницLap-Trinh-He-Thong-Nhung - Bui-Quoc-Bao - Codemau - (Cuuduongthancong - Com)Uy Phạm MinhОценок пока нет

- ADXL345 Sensor I2C InterfaceДокумент5 страницADXL345 Sensor I2C Interfaceavi kishuОценок пока нет

- Display "Hello World"message Using Internal UARTДокумент16 страницDisplay "Hello World"message Using Internal UARTAkshathaОценок пока нет

- VerilogДокумент22 страницыVerilogSyurga FathonahОценок пока нет

- Balancebot CodeДокумент8 страницBalancebot CodeSam Fisher LambertОценок пока нет

- Wifi Module Interfacing With AVRДокумент33 страницыWifi Module Interfacing With AVRMH 108812Оценок пока нет

- OrgcmdДокумент13 страницOrgcmdMuhammad Jalal AldeenОценок пока нет

- Main CДокумент28 страницMain Cindramora2003Оценок пока нет

- VHDL Suma Con CarryДокумент15 страницVHDL Suma Con CarryNatalia MoralezОценок пока нет

- ECEN 248 Lab8 - ReportДокумент16 страницECEN 248 Lab8 - ReportRebecca Sontheimer0% (1)

- My First Program On D Flip FlopДокумент39 страницMy First Program On D Flip FlopAswinCvrnОценок пока нет

- LCD 16x2Документ6 страницLCD 16x2teguh iman100% (2)

- Giao tiếp I2C vs DS1302Документ14 страницGiao tiếp I2C vs DS1302lizhi0007Оценок пока нет

- Template For Lab 5 SoCДокумент5 страницTemplate For Lab 5 SoCTOSONAMiОценок пока нет

- Pic 18f452 Implementation of Digital FiltersДокумент5 страницPic 18f452 Implementation of Digital FiltersishakubalamiОценок пока нет

- LLI RttTimer.VДокумент4 страницыLLI RttTimer.Vkumarsanjeev.net9511Оценок пока нет

- 20IE10051 RITIK Tuesday HW4Документ10 страниц20IE10051 RITIK Tuesday HW4ritikОценок пока нет

- Griet DSP ProgramsДокумент14 страницGriet DSP ProgramsJaipaul CheernamОценок пока нет

- Arduino Pellet Boiler Data Logger v1 My Nerd StuffДокумент36 страницArduino Pellet Boiler Data Logger v1 My Nerd StuffmyEbooks0% (1)

- File: F:/HARDWARE/Program Robot Manual 2011/manual 08-01-1011/SIC/manual/manual.c Date: 1/9/2011Документ3 страницыFile: F:/HARDWARE/Program Robot Manual 2011/manual 08-01-1011/SIC/manual/manual.c Date: 1/9/2011Faizal Nur KarimОценок пока нет

- (09 Interrupt and ISR ProgrammingДокумент4 страницы(09 Interrupt and ISR ProgrammingFahad AliОценок пока нет

- Mini Project RtsДокумент11 страницMini Project RtsOng Xuan YaoОценок пока нет

- 4bit ProcessorДокумент6 страниц4bit ProcessorRaffi SkОценок пока нет

- Ec 1201digital Electronics: 91-9444067484 (Cellphone)Документ30 страницEc 1201digital Electronics: 91-9444067484 (Cellphone)Subathra Devi MourouganeОценок пока нет

- Orcad PLDДокумент8 страницOrcad PLDmeeduma4582Оценок пока нет

- Assignment3 2021HT80531Документ14 страницAssignment3 2021HT80531crypto.investnmentОценок пока нет

- International Islamic University, Islamabad: FPGA Based Design LABДокумент5 страницInternational Islamic University, Islamabad: FPGA Based Design LABMuhammad SaudОценок пока нет

- Proiecte ArduinoДокумент46 страницProiecte ArduinoSyad AlyОценок пока нет

- Electronics Design Lab Manual - VLSI Prog-V3Документ14 страницElectronics Design Lab Manual - VLSI Prog-V3shanmugasundatamОценок пока нет

- Main Code Lab 7Документ4 страницыMain Code Lab 7William HuangОценок пока нет

- Lab 5 DR Muslim (Latest)Документ15 страницLab 5 DR Muslim (Latest)a ThanhОценок пока нет

- ScriptДокумент5 страницScriptSilviuDragomirОценок пока нет

- Program Initial For CCS CommandДокумент15 страницProgram Initial For CCS CommandThuhtay AgОценок пока нет

- STM32F0 C Code For Remote Control InputДокумент15 страницSTM32F0 C Code For Remote Control InputLuke Maximo Bell100% (1)

- NS3 TutorialДокумент46 страницNS3 TutorialahmedabdullaОценок пока нет

- Experiment 4 Stepper Motor Control With Systick Timer: 1 ObjectivesДокумент5 страницExperiment 4 Stepper Motor Control With Systick Timer: 1 ObjectivesEVD18I001 A BALAVIGNESHОценок пока нет

- Lecture2 CuongДокумент51 страницаLecture2 Cuongsongoku711Оценок пока нет

- H 1Документ7 страницH 1nilton_9365611Оценок пока нет

- Led 123 DesimalДокумент4 страницыLed 123 DesimalAmrie Abenq100% (1)

- CED19I032Документ13 страницCED19I032Pranavram VОценок пока нет

- DSD Lab 11 HandoutДокумент5 страницDSD Lab 11 HandoutMuhammad AnasОценок пока нет

- Projects With Microcontrollers And PICCОт EverandProjects With Microcontrollers And PICCРейтинг: 5 из 5 звезд5/5 (1)

- Huawei CX311 Switch Module V100R001C00 White Paper 09Документ41 страницаHuawei CX311 Switch Module V100R001C00 White Paper 09zain_zedanОценок пока нет

- Agribusiness GlosaryДокумент6 страницAgribusiness GlosaryJosé RamirezОценок пока нет

- I Used To Be A Desgin StudentДокумент256 страницI Used To Be A Desgin StudentMLОценок пока нет

- Kantar Worldpanel - Accelerating The Growth of Ecommerce in FMCG - ReportДокумент16 страницKantar Worldpanel - Accelerating The Growth of Ecommerce in FMCG - ReportAbhishek GoelОценок пока нет

- Ricoh MP C4502 C5502 D143, D144 Parts ListДокумент148 страницRicoh MP C4502 C5502 D143, D144 Parts Listdarwinabad83% (6)

- EV SynopsisДокумент10 страницEV Synopsissuresh mpОценок пока нет

- M123SP Service ManualДокумент57 страницM123SP Service ManualJhonatan Diaz100% (1)

- Masurare Grosime Vopsea 1 - Fisa-tehnica-Extech-CG204Документ1 страницаMasurare Grosime Vopsea 1 - Fisa-tehnica-Extech-CG204RizzoRo1Оценок пока нет

- Checklist Applicants (1) Senior HighДокумент1 страницаChecklist Applicants (1) Senior HighdonОценок пока нет

- Ofelia L. Mendoza - Drug StudyДокумент3 страницыOfelia L. Mendoza - Drug StudyMaenard JavierОценок пока нет

- An Embedded Real-Time Object Detection and Measurement of Its SizeДокумент5 страницAn Embedded Real-Time Object Detection and Measurement of Its SizeThong NguyenОценок пока нет

- Literary CriticismДокумент3 страницыLiterary CriticismAnnabelle LerioОценок пока нет

- Grace & The Double LifeДокумент34 страницыGrace & The Double LifeSanty Pogo50% (2)

- Occupational Noise Hazard Assessment: A Case Study of Bangladesh Rail Transport SystemДокумент27 страницOccupational Noise Hazard Assessment: A Case Study of Bangladesh Rail Transport SystemShuvashish RoyОценок пока нет

- C Programming Questions and AnswersДокумент18 страницC Programming Questions and AnswerschitranshpandeyОценок пока нет

- Ministry of PowerДокумент4 страницыMinistry of PowerVivek KumarОценок пока нет

- Report HRTP Sanofi PakistanДокумент13 страницReport HRTP Sanofi PakistanANUS AHMED KHANОценок пока нет

- Tamiya Model Magazine - November 2019Документ70 страницTamiya Model Magazine - November 2019temp userОценок пока нет

- Itron Meter Data Management With MicrosoftДокумент4 страницыItron Meter Data Management With MicrosoftBernardo Mendez-aristaОценок пока нет

- Java Virtual Machine NeutralДокумент14 страницJava Virtual Machine NeutralScorpionОценок пока нет

- Performance Appraisal Form: Part 1 Personal ParticularsДокумент3 страницыPerformance Appraisal Form: Part 1 Personal ParticularsYoan LetsoinОценок пока нет

- TDS - 2 Pack PU Clear Sealer - Exterior (F92N0ECS)Документ2 страницыTDS - 2 Pack PU Clear Sealer - Exterior (F92N0ECS)Krishna Vacha100% (1)

- Bugreport 2022 01 04 15 15 29 Dumpstate - Log 29625Документ3 страницыBugreport 2022 01 04 15 15 29 Dumpstate - Log 29625Yorman Ruiz AcstaОценок пока нет

- Audit Quality and Audit Firm ReputationДокумент10 страницAudit Quality and Audit Firm ReputationEdosa Joshua AronmwanОценок пока нет

- Types of EntreprenursДокумент2 страницыTypes of EntreprenursValar Morghulis100% (2)

- Job and Process IДокумент19 страницJob and Process IsajjadОценок пока нет

- National Food Safety Standard - General Safety Requirements On Food Contact Materials and ArticlesДокумент4 страницыNational Food Safety Standard - General Safety Requirements On Food Contact Materials and ArticlesShariq HaiderОценок пока нет

- Consumer Decision MakingДокумент8 страницConsumer Decision Making9986212378Оценок пока нет

- PricelistДокумент3 страницыPricelistZakaria ZebbicheОценок пока нет

- Decline of RomeДокумент3 страницыDecline of RomeTruman Younghan IsaacsОценок пока нет