Академический Документы

Профессиональный Документы

Культура Документы

מעבדה למעגלים ספרתיים- דפי נתונים של 7475 - LATCH

Загружено:

RonАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

מעבדה למעגלים ספרתיים- דפי נתונים של 7475 - LATCH

Загружено:

RonАвторское право:

Доступные форматы

DM74LS75 Quad Latch

August 1986 Revised March 2000

DM74LS75 Quad Latch

General Description

These latches are ideally suited for use as temporary storage for binary information between processing units and input/output or indicator units. Information present at a data (D) input is transferred to the Q output when the enable is HIGH, and the Q output will follow the data input as long as the enable remains HIGH. When the enable goes LOW, the information (that was present at the data input at the time the transition occurred) is retained at the Q output until the enable is permitted to go HIGH. These latches feature complementary Q and Q outputs from a 4-bit latch, and are available in 16-pin packages.

Ordering Code:

Order Number DM74LS75M DM74LS75N Package Number M16A N16E Package Description 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also available in Tape and Reel. Specify by appending the suffix letter X to the ordering code.

Logic Diagram

(Each Latch)

Connection Diagram

Function Table

Inputs D L H X

(Each Latch) Outputs Q L H Q0 Q H L Q0

Enable H H L

H = HIGH Level L = LOW Level X = Don't Care Q0 = The Level of Q Before the HIGH-to-LOW Transition of ENABLE

2000 Fairchild Semiconductor Corporation

DS006374

www.fairchildsemi.com

DM74LS75

Absolute Maximum Ratings(Note 1)

Supply Voltage Input Voltage Operating Free Air Temperature Range Storage Temperature Range 7V 7V 0C to +70C 65C to +150C

Note 1: The Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The Recommended Operating Conditions table will define the conditions for actual device operation.

Recommended Operating Conditions

Symbol VCC VIH VIL IOH IOL tW tSU tH TA Supply Voltage HIGH Level Input Voltage LOW Level Input Voltage HIGH Level Output Current LOW Level Output Current Enable Pulse Width (Note 5) Setup Time (Note 5) Hold Time (Note 5) Free Air Operating Temperature 20 20 0 0 70 Parameter Min 4.75 2 0.8 0.4 8 Nom 5 Max 5.25 Units V V V mA mA ns ns ns C

Electrical Characteristics

over recommended operating free air temperature range (unless otherwise noted) Symbol VI VOH VOL Parameter Input Clamp Voltage HIGH Level Output Voltage LOW Level Output Voltage II IIH IIL IOS ICC Input Current @ Max Input Voltage HIGH Level Input Current LOW Level Input Current Short Circuit Output Current Supply Current VCC = Max (Note 2) VCC = Max (Note 3) VCC = Max, VI = 0.4V VCC = Max, VI = 2.7V Conditions VCC = Min, II = 18 mA VCC = Min, IOH = Max VIL = Max, VIH = Min VCC = Min, IOL = Max VIL = Max, VIH = Min IOL = 4 mA, VCC = Min VCC = Max, VI = 7V D Enable D Enable D Enable 20 6.3 2.7 3.5 0.35 0.25 0.5 0.4 0.1 0.4 20 80 0.4 1.6 100 12 mA A mA mA mA Min Typ (Note 2) Max 1.5 Units V V

Note 2: All typicals are at VCC = 5V, TA = 25C. Note 3: Not more than one output should be shorted at a time, and the duration should not exceed one second. Note 4: ICC is measured with all outputs open and all inputs grounded. Note 5: TA = 25C and V CC = 5V.

www.fairchildsemi.com

DM74LS75

Switching Characteristics

at VCC = 5V and TA = 25C From (Input) Symbol Parameter To (Output) CL = 15 pF Min tPLH tPHL tPLH tPHL tPLH tPHL tPLH tPHL Propagation Delay Time LOW-to-HIGH Level Output Propagation Delay Time HIGH-to-LOW Level Output Propagation Delay Time LOW-to-HIGH Level Output Propagation Delay Time HIGH-to-LOW Level Output Propagation Delay Time LOW-to-HIGH Level Output Propagation Delay Time HIGH-to-LOW Level Output Propagation Delay Time LOW-to-HIGH Level Output Propagation Delay Time HIGH-to-LOW Level Output D to Q D to Q Max 27 17 RL = 2 k CL = 50 pF Min Max 30 25 ns ns Units

D to Q

20

25

ns

D to Q Enable to Q Enable to Q

15 27 25

20 30 30

ns ns ns

Enable to Q

30

30

ns

Enable to Q

15

20

ns

www.fairchildsemi.com

DM74LS75

Physical Dimensions inches (millimeters) unless otherwise noted

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow Package Number M16A

www.fairchildsemi.com

DM74LS75 Quad Latch

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide Package Number N16E

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications. LIFE SUPPORT POLICY FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein: 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user. 5 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. www.fairchildsemi.com

www.fairchildsemi.com

Вам также может понравиться

- מבוא לחישוב- הצעת פתרון לתרגיל בית 3 - 2010Документ3 страницыמבוא לחישוב- הצעת פתרון לתרגיל בית 3 - 2010RonОценок пока нет

- מבוא לחישוב- הצעת פתרון לתרגיל בית 1 - 2010Документ1 страницаמבוא לחישוב- הצעת פתרון לתרגיל בית 1 - 2010RonОценок пока нет

- מבוא לחישוב- הצעת פתרון לתרגיל בית 5 - 2010Документ20 страницמבוא לחישוב- הצעת פתרון לתרגיל בית 5 - 2010RonОценок пока нет

- מבוא לחישוב- תרגיל כיתה 5 - לולאות, ENUM, CASTINGДокумент3 страницыמבוא לחישוב- תרגיל כיתה 5 - לולאות, ENUM, CASTINGRonОценок пока нет

- מבוא לחישוב- תרגיל כיתה 14 - קריאה וכתיבה לקובץДокумент2 страницыמבוא לחישוב- תרגיל כיתה 14 - קריאה וכתיבה לקובץRonОценок пока нет

- מבוא לחישוב- הצעת פתרון לתרגיל בית 6 - 2010Документ12 страницמבוא לחישוב- הצעת פתרון לתרגיל בית 6 - 2010RonОценок пока нет

- מבוא לחישוב- הצעת פתרון לתרגיל בית 2 - 2010Документ2 страницыמבוא לחישוב- הצעת פתרון לתרגיל בית 2 - 2010RonОценок пока нет

- מל"ס- מועד ב ופתרון - חורף 2010Документ13 страницמל"ס- מועד ב ופתרון - חורף 2010RonОценок пока нет

- מל"ס- בוחן אמצע מועד ב - חורף 2009Документ1 страницаמל"ס- בוחן אמצע מועד ב - חורף 2009RonОценок пока нет

- מבוא לחישוב- הצעת פתרון לתרגיל בית 4 - 2010Документ8 страницמבוא לחישוב- הצעת פתרון לתרגיל בית 4 - 2010RonОценок пока нет

- מערכות הפעלה- תרגיל בית 3 - 2013Документ2 страницыמערכות הפעלה- תרגיל בית 3 - 2013RonОценок пока нет

- VLSI- הרצאה 2 - Design FlowДокумент35 страницVLSI- הרצאה 2 - Design FlowRonОценок пока нет

- עיבוד תמונה- נספח לתרגיל בית 4 - בניית פילטר בתחום התדרДокумент2 страницыעיבוד תמונה- נספח לתרגיל בית 4 - בניית פילטר בתחום התדרRonОценок пока нет

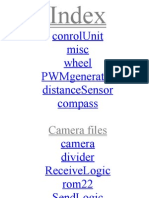

- משובצות- קוד רפרנסДокумент29 страницמשובצות- קוד רפרנסRonОценок пока нет

- VLSI- הרצאה 3 - ManufacturingДокумент48 страницVLSI- הרצאה 3 - ManufacturingRonОценок пока нет

- מערכות הפעלה- תרגיל בית 2 - 2013Документ2 страницыמערכות הפעלה- תרגיל בית 2 - 2013RonОценок пока нет

- הצעת פתרון לתרגיל בית 4 - 2011Документ9 страницהצעת פתרון לתרגיל בית 4 - 2011RonОценок пока нет

- מערכות הפעלה- תרגיל בית 1 - 2013Документ2 страницыמערכות הפעלה- תרגיל בית 1 - 2013RonОценок пока нет

- מונחה עצמים- תרגול 4Документ10 страницמונחה עצמים- תרגול 4RonОценок пока нет

- סיכום תמציתי של פקודות ותחביר ב-VHDLДокумент4 страницыסיכום תמציתי של פקודות ותחביר ב-VHDLRonОценок пока нет

- VLSI- הרצאה 1 - מבואДокумент51 страницаVLSI- הרצאה 1 - מבואRonОценок пока нет

- VLSI- תרגול 0 - Mosfet CapacitanceДокумент2 страницыVLSI- תרגול 0 - Mosfet CapacitanceRonОценок пока нет

- Quick Start Guide: For Quartus II SoftwareДокумент6 страницQuick Start Guide: For Quartus II SoftwareRonОценок пока нет

- VHDL HandbookДокумент76 страницVHDL HandbookAngel EdoraОценок пока нет

- שפות סימולציה- הצעת פתרון למעבדה 1Документ5 страницשפות סימולציה- הצעת פתרון למעבדה 1RonОценок пока нет

- מדריך modelsim למתחיליםДокумент22 страницыמדריך modelsim למתחיליםRonОценок пока нет

- עיבוד תמונה- תרגיל כיתה 5 - 2D DFT, חלק 1Документ23 страницыעיבוד תמונה- תרגיל כיתה 5 - 2D DFT, חלק 1RonОценок пока нет

- עיבוד תמונה- תרגיל כיתה 10 - morphology, חלק 1Документ31 страницаעיבוד תמונה- תרגיל כיתה 10 - morphology, חלק 1RonОценок пока нет

- עיבוד תמונה- תרגיל כיתה 6 - 2D DFT, חלק 2Документ33 страницыעיבוד תמונה- תרגיל כיתה 6 - 2D DFT, חלק 2RonОценок пока нет

- עיבוד תמונה- מועד ב - 2009Документ2 страницыעיבוד תמונה- מועד ב - 2009RonОценок пока нет

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- Manual de Partes Gen Dqdac 300 Kw-1Документ184 страницыManual de Partes Gen Dqdac 300 Kw-1Daniel Lopez100% (2)

- Devireg 535 PDFДокумент28 страницDevireg 535 PDFFabián GarófaloОценок пока нет

- HT7 L4815 V 100Документ9 страницHT7 L4815 V 100Enéas BaroneОценок пока нет

- Eee 11 15Документ5 страницEee 11 15aswakrishОценок пока нет

- Spacelogic VBB/VBS: NoticeДокумент4 страницыSpacelogic VBB/VBS: Noticehamza alhassanОценок пока нет

- Manual NSD70D EnglishДокумент155 страницManual NSD70D Englishnarvis1Оценок пока нет

- TeslaДокумент5 страницTeslaВанёк ГресьОценок пока нет

- General Residential Service: Puerto Rico Electric Power AuthorityДокумент76 страницGeneral Residential Service: Puerto Rico Electric Power AuthorityMonica DiazОценок пока нет

- AcuRev 2100 Multi Circuit Power Energy Meter InstallationДокумент11 страницAcuRev 2100 Multi Circuit Power Energy Meter InstallationDiogo RomeroОценок пока нет

- Figure 1 A Typical Starting System Converts Electrical Energy Into Mechanical Energy To Turn The EngineДокумент8 страницFigure 1 A Typical Starting System Converts Electrical Energy Into Mechanical Energy To Turn The EngineAniruddh TrivediОценок пока нет

- Manual-LVD Low Voltage DisconnectДокумент4 страницыManual-LVD Low Voltage DisconnectronniedakingpouОценок пока нет

- 02 SpectrophotometerДокумент40 страниц02 SpectrophotometerHassan GillОценок пока нет

- Coax Switches: Series CCR-33S/CR-33SДокумент10 страницCoax Switches: Series CCR-33S/CR-33SMuhammad ArslanОценок пока нет

- Mobile SubstationsДокумент12 страницMobile Substationsengineer_2009Оценок пока нет

- Testing Guidelines For Power Park Modules 2017Документ31 страницаTesting Guidelines For Power Park Modules 2017syafiqishamuddinОценок пока нет

- Intertek IEC EN 60079 25 Intrinsically Safe Electrical SystemsДокумент2 страницыIntertek IEC EN 60079 25 Intrinsically Safe Electrical Systemssofiane mokhtariОценок пока нет

- Chapter 7 Optical AmplifiersДокумент23 страницыChapter 7 Optical AmplifiersNur AmalinaОценок пока нет

- FF EcuДокумент9 страницFF EcuEduardo J CondeОценок пока нет

- A6. Design Features of Low Speed Permanent Magnet GeneratorДокумент4 страницыA6. Design Features of Low Speed Permanent Magnet Generatorwalidghoneim1970Оценок пока нет

- Digital Interface ModuleДокумент12 страницDigital Interface ModuleakramhomriОценок пока нет

- Aether Gravity TechnologyДокумент328 страницAether Gravity Technologyrossix1100% (2)

- SANYO - Cg21ys2s PDFДокумент38 страницSANYO - Cg21ys2s PDFAsallimitОценок пока нет

- Project Proposal: Universiti Teknikal Malaysia MelakaДокумент3 страницыProject Proposal: Universiti Teknikal Malaysia MelakaMohammad FaisalОценок пока нет

- Abstract AntennaДокумент3 страницыAbstract AntennaMohit KumarОценок пока нет

- Electricity Questions and SolutionsДокумент41 страницаElectricity Questions and SolutionsDaveyОценок пока нет

- Areva&hvdc PDFДокумент167 страницAreva&hvdc PDFAbdallah Salem100% (1)

- Elexia FP2 RELAY Axicom D3016Документ4 страницыElexia FP2 RELAY Axicom D3016Коресендович ЮрийОценок пока нет

- Schneider Tm100c24rn Controller m100 14i 10o Relay 220vacДокумент3 страницыSchneider Tm100c24rn Controller m100 14i 10o Relay 220vachobiesam0% (1)

- XR C7200Документ37 страницXR C7200Selvin ReyesОценок пока нет

- PANASONIC Panasonic TH-L32X10M Chassis KM02 Service Manual PDFДокумент130 страницPANASONIC Panasonic TH-L32X10M Chassis KM02 Service Manual PDFAbhiОценок пока нет