Академический Документы

Профессиональный Документы

Культура Документы

Experiment No 2

Загружено:

azzam_aliИсходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Experiment No 2

Загружено:

azzam_aliАвторское право:

Доступные форматы

Department of Electrical Engineering

The University of Faisalabad

Experiment No. 2

To design a multiplexer (4 to 1) in VHDL using CPLD development platform or FPGA circuit

board.

=============================================================================

-- It is a 4 input multiplexer with the function as:

-sel

Input => output

-MSB LSB

-0

0

in0 => output

-0

1

in1 => output

-1

0

in2 => output

-1

1

in3 => output

-----------------------------------------------------------------------------IF

and CASE can only be used inside a process.

-WHEN and WITH can only be used outside a process.

--IF

corresponds to WHEN

-CASE corresponds to WITH

-=============================================================================

VLSI Lab Work taught By: Ubaid Umar

Department of Electrical Engineering

The University of Faisalabad

=============================================================================

USING CASE

=============================================================================

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity multiplexer_4to1_case is

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

c : in STD_LOGIC;

d : in STD_LOGIC;

e : in STD_LOGIC;

sel : in STD_LOGIC_VECTOR (1 downto 0);

output : out STD_LOGIC);

end multiplexer_4to1_case;

architecture Behavioral of multiplexer_4to1_case is

begin

process (a, b, c, d, e, Sel) is

begin

case Sel is

when "00" => Output <= a;

when "01" => Output <= b;

when "10" => Output <= c;

when "11" => Output <= d;

when others => Output <= e;

end case;

end process;

end Behavioral;

VLSI Lab Work taught By: Ubaid Umar

Department of Electrical Engineering

The University of Faisalabad

=============================================================================

USING IF

=============================================================================

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity multiplexer_4to1_if is

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

c : in STD_LOGIC;

d : in STD_LOGIC;

sel0 : in STD_LOGIC;

sel1 : in STD_LOGIC;

output : out STD_LOGIC);

end multiplexer_4to1_if;

architecture Behavioral of multiplexer_4to1_if is

begin

PROCESS(sel0, sel1, a, b, c, d)

BEGIN

IF

(sel0='0' AND sel1='0') THEN

output <= a;

ELSIF (sel0='1' AND sel1='0') THEN

output <= b;

ELSIF (sel0='0' AND sel1='1') THEN

output <= c;

ELSIF (sel0='1' AND sel1='1') THEN

output <= d;

ELSE

-- (sel0 or sel1 are not 0 or 1)

output <= 'X';

END IF;

END PROCESS;

end Behavioral;

VLSI Lab Work taught By: Ubaid Umar

Department of Electrical Engineering

The University of Faisalabad

=============================================================================

USING WITH

=============================================================================

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity multiplexer_4to1_with is

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

c : in STD_LOGIC;

d : in STD_LOGIC;

sel0 : in STD_LOGIC;

sel1 : in STD_LOGIC;

output : out STD_LOGIC);

end multiplexer_4to1_with;

architecture Behavioral of multiplexer_4to1_with is

SIGNAL

sel

STD_LOGIC_VECTOR(1 DOWNTO 0);

begin

sel <= sel1 & sel0; -- concatenate s1 and s0

WITH sel SELECT

output <= a WHEN "00",

b WHEN "01",

c WHEN "10",

d WHEN "11",

'X' WHEN OTHERS;

end Behavioral;

VLSI Lab Work taught By: Ubaid Umar

Department of Electrical Engineering

The University of Faisalabad

=============================================================================

USING WHEN

=============================================================================

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity multiplexer_4to1_when is

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

c : in STD_LOGIC;

d : in STD_LOGIC;

sel0 : in STD_LOGIC;

sel1 : in STD_LOGIC;

output : out STD_LOGIC);

end multiplexer_4to1_when;

architecture Behavioral of multiplexer_4to1_when is

begin

output <= a WHEN

b WHEN

c WHEN

d WHEN

'X';

(sel1

(sel1

(sel1

(sel1

&

&

&

&

sel0)="00"

sel0)="01"

sel0)="10"

sel0)="11"

ELSE

ELSE

ELSE

ELSE

end Behavioral;

VLSI Lab Work taught By: Ubaid Umar

Вам также может понравиться

- 6th Central Pay Commission Salary CalculatorДокумент15 страниц6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Lecture 3 - PQ IssuesДокумент35 страницLecture 3 - PQ Issuesazzam_aliОценок пока нет

- Chapter 1 SolutionДокумент2 страницыChapter 1 SolutionnoimportaОценок пока нет

- Solutions To Chapter 4:: N N N N RДокумент3 страницыSolutions To Chapter 4:: N N N N Razzam_aliОценок пока нет

- Power Quality Course Plan AnalysisДокумент5 страницPower Quality Course Plan Analysisazzam_aliОценок пока нет

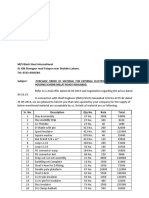

- Purchase Order HardwareДокумент2 страницыPurchase Order Hardwareazzam_aliОценок пока нет

- Transportation Problem: Instructor Name: Dr. M. Omer Khan (Omerkhan@riphahfsd - Edu.pk)Документ38 страницTransportation Problem: Instructor Name: Dr. M. Omer Khan (Omerkhan@riphahfsd - Edu.pk)azzam_aliОценок пока нет

- EE-5050 Power Quality Course OverviewДокумент14 страницEE-5050 Power Quality Course Overviewazzam_aliОценок пока нет

- Power Quality Course Plan AnalysisДокумент5 страницPower Quality Course Plan Analysisazzam_aliОценок пока нет

- Transportation Problem: Instructor Name: Dr. M. Omer Khan (Omerkhan@riphahfsd - Edu.pk)Документ38 страницTransportation Problem: Instructor Name: Dr. M. Omer Khan (Omerkhan@riphahfsd - Edu.pk)azzam_aliОценок пока нет

- Chapter 2 Soln PVДокумент2 страницыChapter 2 Soln PVazzam_aliОценок пока нет

- 2 Exe6 SolДокумент2 страницы2 Exe6 Solazzam_aliОценок пока нет

- Medical Allowance Bps 16 17Документ1 страницаMedical Allowance Bps 16 17azzam_aliОценок пока нет

- AnalysisandOptimizationofRadialDistributionNetworkUsingGISandGPSTechniques PDFДокумент7 страницAnalysisandOptimizationofRadialDistributionNetworkUsingGISandGPSTechniques PDFazzam_aliОценок пока нет

- Advertisement IДокумент1 страницаAdvertisement Iazzam_aliОценок пока нет

- NTS IPC Cultural Exchange ScholarshipsДокумент2 страницыNTS IPC Cultural Exchange Scholarshipsazzam_aliОценок пока нет

- Generator & Exciter BasicДокумент8 страницGenerator & Exciter Basictowfiqeee100% (1)

- ApplicationForm CivilianStaff PPIC3 CentreДокумент5 страницApplicationForm CivilianStaff PPIC3 CentreKhalid MahmoodОценок пока нет

- MEPCOДокумент99 страницMEPCOazzam_aliОценок пока нет

- Generator & Exciter BasicДокумент8 страницGenerator & Exciter Basictowfiqeee100% (1)

- 3 1 119-125Документ7 страниц3 1 119-125azzam_aliОценок пока нет

- NTS FESCO Test Composition 12-13-14/05/2015Документ2 страницыNTS FESCO Test Composition 12-13-14/05/2015BeTechieОценок пока нет

- MathematicsДокумент66 страницMathematicsazzam_ali100% (1)

- Latest Current AffairsДокумент4 страницыLatest Current Affairsazzam_aliОценок пока нет

- Northern Power Generation Company Limited Recrutiment Test Content WeightagesДокумент7 страницNorthern Power Generation Company Limited Recrutiment Test Content WeightagesBeTechie100% (1)

- Zteuet MSC FormДокумент3 страницыZteuet MSC Formazzam_aliОценок пока нет

- Cover Letter 1Документ1 страницаCover Letter 1azzam_aliОценок пока нет

- Northern Power Generation Company Limited Recrutiment Test Content WeightagesДокумент1 страницаNorthern Power Generation Company Limited Recrutiment Test Content WeightagesSyed Ali RazaОценок пока нет

- GR Phase I 2015 Public NoticeДокумент1 страницаGR Phase I 2015 Public Noticeazzam_aliОценок пока нет

- NTS MS admission test registrationДокумент3 страницыNTS MS admission test registrationazzam_aliОценок пока нет

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (119)

- Sanction Letter 49366481Документ3 страницыSanction Letter 49366481Dr. Shashank RkОценок пока нет

- Review Case Study of Various Types of DSL SystemДокумент4 страницыReview Case Study of Various Types of DSL SystemInternational Journal of Innovations in Engineering and ScienceОценок пока нет

- America's PowerДокумент1 страницаAmerica's PoweralabamacoalОценок пока нет

- Solar Turbines Taurus 65 Data SheetДокумент2 страницыSolar Turbines Taurus 65 Data SheetLuis SanguinettiОценок пока нет

- SC750-1 60HZ Cummins Generator STAMFORDДокумент4 страницыSC750-1 60HZ Cummins Generator STAMFORDChen CarolineОценок пока нет

- WindingsДокумент2 страницыWindingsCarlo Jay VizcarraОценок пока нет

- Freesmachine Falcon HandleidingДокумент198 страницFreesmachine Falcon Handleidingmad zollaОценок пока нет

- Wuolah Free Exercises7Документ17 страницWuolah Free Exercises7Don José Antonio García-Trevijano ForteОценок пока нет

- Zurc-Cat Analogicos GBДокумент20 страницZurc-Cat Analogicos GBAhmad DanishОценок пока нет

- Voltage Detector Ic With Counter Timer: Bd45Xxxg Bd46XxxgДокумент5 страницVoltage Detector Ic With Counter Timer: Bd45Xxxg Bd46XxxgPham LongОценок пока нет

- Building WireДокумент57 страницBuilding WireDinesh Guna100% (1)

- Smart-UPS SMC2000IДокумент3 страницыSmart-UPS SMC2000IMothafukin MorrisseyОценок пока нет

- Group 15 Fuel Warmer System Specs and OperationДокумент1 страницаGroup 15 Fuel Warmer System Specs and OperationDavidОценок пока нет

- FMG31R Thru FMG36R: PB Free Plating ProductДокумент3 страницыFMG31R Thru FMG36R: PB Free Plating ProductTspi RitzelОценок пока нет

- High-Voltage Compact Switchgear 3AP1 DTC For 145 KV and 245 KVДокумент8 страницHigh-Voltage Compact Switchgear 3AP1 DTC For 145 KV and 245 KVJunaid LankerОценок пока нет

- Cisco Power Calculator ASR9010Документ2 страницыCisco Power Calculator ASR9010Carlos Hoyos RosembluthОценок пока нет

- NEMSAДокумент48 страницNEMSACharis YoungОценок пока нет

- R6013e MVTRДокумент6 страницR6013e MVTRlucnhamdaidon8426Оценок пока нет

- Om On280Документ38 страницOm On280yonasОценок пока нет

- A-1.JSA-Service Panel & U.P.SДокумент1 страницаA-1.JSA-Service Panel & U.P.SVivek SinghОценок пока нет

- Adi Design SolutionДокумент7 страницAdi Design SolutionMark John Servado AgsalogОценок пока нет

- R6 Hotel Project Electrical, Mechanical and Plumbing Works SpecificationДокумент42 страницыR6 Hotel Project Electrical, Mechanical and Plumbing Works SpecificationGabriella EllaОценок пока нет

- Cross-Reference Information For Diagnostic CodesДокумент9 страницCross-Reference Information For Diagnostic CodesEdwin Alfonso Hernandez MontesОценок пока нет

- Q EN CEOCOR GUIDELINES To Measurement Techniques 2001 PDFДокумент143 страницыQ EN CEOCOR GUIDELINES To Measurement Techniques 2001 PDFNur Muhammad AbdurrahmanОценок пока нет

- Fast Decoupled Load Flow MethodДокумент11 страницFast Decoupled Load Flow MethodSanthosh Reddy KanthalaОценок пока нет

- Project Report ThesisДокумент62 страницыProject Report ThesisSAIPRAKASH BONALAОценок пока нет

- KTI20Документ888 страницKTI20NunoОценок пока нет

- KahootsДокумент2 страницыKahootsA CОценок пока нет

- IEC 61378 1@transformermagДокумент188 страницIEC 61378 1@transformermagMohammad KhodadadОценок пока нет