Академический Документы

Профессиональный Документы

Культура Документы

Lab 1

Загружено:

sean_bostic7193Исходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Lab 1

Загружено:

sean_bostic7193Авторское право:

Доступные форматы

Version: 4 September 2012 University of Cincinnati School of Electronic and Computing Systems EECE1975 Introduction to Digital Systems Laboratory

y Project 1

Design a Door Code Detector

Fall 2012

1 Introduction This is a continuation of Lab 9 from the Spring Quarter. The purpose of this laboratory is to fully understand the sequential circuit design process, from specification to the final circuit design, using Verilog and FPGA. It is important to note that you are not allowed to re-use the structurallevel (i.e., gate-level) design from Lab 9. You MUST use data-flow design and behaviorallevel design. 2 Tasks You have probably seen doors that require a person to press a particular sequence of buttons. For example, there might be 16 buttons including 0-9, and A-F. You have to press the start button and then the following sequence 5, A, 4, F to unlock the door, while any other sequence does not unlock the door. Design a door code detector (Moore machine) that has two inputs S and Y where S is the start signal (by a push button) and Y gives the code that is a sequence of logic 0s and 1s (by a switch). The detector has one output Z (LED). To open the door (i.e., Z=1), you have to press the S button once and then input Y with sequence 101*0*10 where 1* (0*) means one or more logic 1 (0). Once a correct sequence to unlock the door has been detected, the machine goes back to the initial state unconditionally, and be ready for the next input sequence. You have to use data-flow modeling and behavioral modeling for the sequential circuit design. 2.1 Task 1: Data-Flow Design An architectural-level diagram of the circuit to be implemented in the FPGA is shown in Figure 1. Design the sequential circuit using D-flip-flops. First, implement the sequential circuit in Verilog using data-flow modeling, that is using assign statements to implement the combinational circuit of the sequential machine in Verilog. The D-FF model is provided in Figure 2. 2.2 Task 2: Behavioral Design In this task, implement the sequential circuit using behavioral modeling, i.e., using always, case, ... instructions. 2.3. Clock model and debouncing model One practical design issue using FPGA is that the clock signal of the board is too fast (e.g., 50 MHz) for you to enter the inputs. Thus, you have to reduce the clock frequency. Further, the push buttons on the Basys board are not debounced. Verilog modules for a debounce circuit and related clock model are shown in Figures 3 and 4 below. The relationship between these two modules, and the sequential circuit module is defined by the input/output ports of the modules.

1/5

Version: 4 September 2012

2.4 Implementation Details The organization of these modules along with any modules created to implement the door code detector should be consistent with the architecture shown in Figure 1. Note that the goal of the design of this project is a synthesizable. Use a top module instantiating all components (sequence detector, debounce, clock, etc.) to create a single interface to the testbench (for simulation) or the Basys board physical components (for synthesis). In your Verilog design, you should have at least the following modules: D_FF, Clock_down_converter, Debouncing, Code_detector (i.e., the sequential circuit), and Top. Note that the Top module is used to connect all modules together. Also note that a Reset signal must be used to initialize the sequential circuit.

Z LED Y D Combinational circuit R . . . D 1.5Hz R Reset

Debouncing CKT

CLK 50MHz

CLK-down converter

Figure 1. Overall architecture of the door code decoder.

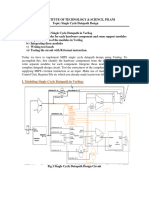

module D_FF( // File name: // Description: input clk, input clr, input D, output reg q ); always @ (posedge clk, posedge clr) if (clr) q=0; // clear else q = D; // latch D input endmodule

DFF_wCLear D flip-flop with asynch clear

Figure 2. Verilog module of a D flip-flop with asynch clear

2/5

Version: 4 September 2012

module Debounce( // File name: debounce.v // Description: Delays output of pushbutton until bounce has // settled out. input clock, // Delays pushbutton by three 4-ms clock periods input clear, // Resets the debounce action to start of delay input dbin, // from un-debounced push button output dbout // debounced output from pushbutton ); reg delay1; reg delay2; reg delay3; always @ (posedge clock, posedge clear) begin if (clear) begin delay1 <= 1'b0; delay2 <= 1'b0; delay3 <= 1'b0; end else begin delay1 <= dbin; delay2 <= delay1; delay3 <= delay2; end end assign dbout = delay1 & delay2 & delay3; endmodule

Figure 3. Verilog model of a push-button debounce circuit. Use with the clock downconverter shown in Figure 4.

module Clock_down_converter( input clock, // 50 MHz clock input clear, // Reset down-converter output clk1, // ~1.5 Hz clock output clk200 // 200 Hz clock ); // 25-bit counter reg[24:0] q; always @ (posedge clock, posedge clear) begin if (clear) q <= 0; else q <= q+1;

3/5

Version: 4 September 2012

end // Uncomment and comment following statements as needed for // simulation and synthesis assign clk200 = q[0]; //40 ns period (for simulation) assign clk1 = q[1]; //80 ns period (for simulation) // assign clk200 = q[17]; //200 Hz (for board) // assign clk1 = q[24]; //~1.5 Hz (for board) endmodule

Figure 4. Verilog model of a clock down-converter to provide a 200-Hz clock for the debounce circuit shown in Figure 3, and an approximate 1.5-Hz clock to clock the counter FFs slow enough to visually read the counter output.

3.0 Reports The design report must include Verilog codes (data flow and behavioral) for the sequential circuit (combinational gates and FFs), the testbench, and simulation waveforms for both codes. This will greatly help the TA to judge the design correctness. A 30% bonus will be given if ALL components/modules are properly integrated in a top module and are working. The final report must include: 1. A short description of the design requirements, and the overall system architecture (like Fig. 1). 2. Codes of all modules that are fully functional. 3. Testbench used for simulation. 4. Test plan including tests. You must design at least two or more test set with each one represented as a table shown in Table 1. You must have the TA sign for each test, including testbench simulation and Basys board execution. 5. Simulation Waveform or Text Display Results Attach at end of report a signed window capture of the full output waveform, or complete text display of inputs vs outputs showing the simulation results of your Verilog component model. The waveform or text display showing the output of your simulation must be viewed in person during the laboratory session, and the hardcopy signed, by the TA. 6. Photo Documenting Correct Hardware Implementation

Attach at end of report a still photo of your Basys board correctly executing the door code detector design. The hardware executing the synthesized Verilog model must be viewed in person during

the laboratory session, and the photo signed, by the TA.

4/5

Version: 4 September 2012

INPUTS Reset CLK1 CLK2 Y S Expected

RESULTS Simulation Basys Board

TA Signature Simulation: ______________________________ Basys Board: ______________________________

Table 1. Test set to be used to test the implemented door code detector.

5/5

Вам также может понравиться

- Birla Institute of Technology & Science, Pilani Lab Sheet - 1Документ7 страницBirla Institute of Technology & Science, Pilani Lab Sheet - 1SATYAVRAT SHARMAОценок пока нет

- Lab 6Документ11 страницLab 6vivek2mbОценок пока нет

- FPGA Design Flow & Experiment 1Документ5 страницFPGA Design Flow & Experiment 1Faid MuzahidОценок пока нет

- Lab 07Документ10 страницLab 07api-241454978Оценок пока нет

- Verilog ModuleДокумент14 страницVerilog ModuleMuskan YadavОценок пока нет

- BME 438 Digital Logic Design and Computer Architecture LabДокумент73 страницыBME 438 Digital Logic Design and Computer Architecture LabHafiz Muhammad Ahmad RazaОценок пока нет

- Lab 4 Verilog Gate Level ModellingДокумент11 страницLab 4 Verilog Gate Level Modellingsafdarmunir070Оценок пока нет

- VlogДокумент14 страницVlogUday KumarОценок пока нет

- Programming FPGAsДокумент38 страницProgramming FPGAssayuri8910Оценок пока нет

- PWM Driver VerilogДокумент24 страницыPWM Driver Veriloglizhi0007Оценок пока нет

- Tutorial ProjectДокумент16 страницTutorial ProjectMuhammadNizarArifansyahОценок пока нет

- Lab ECAD 5Документ11 страницLab ECAD 5Noor AfiqОценок пока нет

- LAB#1Документ5 страницLAB#1Unsa Jan Abdul QayyumОценок пока нет

- Department of Electrical Engineering: Ee-421: Digital Sysem DesignДокумент20 страницDepartment of Electrical Engineering: Ee-421: Digital Sysem DesignAhmed AliОценок пока нет

- Ee201 TestbenchДокумент19 страницEe201 TestbenchSamОценок пока нет

- 3 Bit Down CounterДокумент6 страниц3 Bit Down CounterMustafa IqbalОценок пока нет

- Lab # 2 Verilog Structure: 2.1 ModulesДокумент5 страницLab # 2 Verilog Structure: 2.1 ModulesThe Common YoutuberОценок пока нет

- You Could Download File D - FF.VДокумент133 страницыYou Could Download File D - FF.VPradeep BabuОценок пока нет

- Eee446 Lab Manual Spring2015Документ23 страницыEee446 Lab Manual Spring2015vognarОценок пока нет

- Debugging of Verilog Hardware Designs On DE2Документ19 страницDebugging of Verilog Hardware Designs On DE2CharismaztexОценок пока нет

- CE 264 Lab Project: Kuwait UniversityДокумент9 страницCE 264 Lab Project: Kuwait UniversityCalvin SaldanhaОценок пока нет

- Chapter1: Introduction To VerilogДокумент15 страницChapter1: Introduction To Verilogarunguptha_gsОценок пока нет

- Digital Design BEC30503 Instruction Sheet: Lab No. Lab Title Semester Session Lab Durations Independent StudiesДокумент30 страницDigital Design BEC30503 Instruction Sheet: Lab No. Lab Title Semester Session Lab Durations Independent StudiesKarti ViveygenОценок пока нет

- 333 - Lab - 6 - 2017 Clarified 4 - 8 - 17Документ8 страниц333 - Lab - 6 - 2017 Clarified 4 - 8 - 17abdul nurudeenОценок пока нет

- Vlsi Manual 2013-2014Документ36 страницVlsi Manual 2013-2014hr_suresh_kОценок пока нет

- ECNG3016 Practical 3Документ12 страницECNG3016 Practical 3Marlon BoucaudОценок пока нет

- Writing Test Benches: A Free Application NoteДокумент8 страницWriting Test Benches: A Free Application NoteEhsan MahdaviОценок пока нет

- VLSI Lab Manual Student Copy 21-22 04.10.21Документ76 страницVLSI Lab Manual Student Copy 21-22 04.10.21RanjithОценок пока нет

- Lab 1 Spring 13Документ3 страницыLab 1 Spring 13Kumaraguru RauОценок пока нет

- 04using Library ModulesДокумент20 страниц04using Library ModulesHaoyuan LiuОценок пока нет

- Circuit Design and Simulation Exercises 2Документ6 страницCircuit Design and Simulation Exercises 2Aarjan KhadkaОценок пока нет

- Lab 5Документ3 страницыLab 5Arun MehraОценок пока нет

- Xilinx WorkbookДокумент94 страницыXilinx WorkbookdmctekОценок пока нет

- Verilog Lecture 3 - NoopurДокумент64 страницыVerilog Lecture 3 - NoopurMonis KhanОценок пока нет

- Exp - 08 Flight86Документ6 страницExp - 08 Flight86Muhammad SaqibОценок пока нет

- CSE20221 Keyboard Interface ProjectДокумент2 страницыCSE20221 Keyboard Interface ProjectpranjalОценок пока нет

- Verilog HDL: Dr. Shoab KhanДокумент61 страницаVerilog HDL: Dr. Shoab KhanSufyan AsgharОценок пока нет

- Vlsi Lab DocumentДокумент18 страницVlsi Lab DocumentRaffi SkОценок пока нет

- Writing A Testbench in Verilog & Using To Test 1. SynopsisДокумент19 страницWriting A Testbench in Verilog & Using To Test 1. SynopsissubashОценок пока нет

- FPGA-Based-System-Design LAB JOURNAL 2Документ56 страницFPGA-Based-System-Design LAB JOURNAL 2talha42103Оценок пока нет

- RTL2GDSFLOWДокумент23 страницыRTL2GDSFLOWAbhishek Gupta0% (1)

- Lab1 SpecДокумент6 страницLab1 Spec星期三的配音是對的Оценок пока нет

- Exp1 dSPACEДокумент19 страницExp1 dSPACEVisheshОценок пока нет

- Lab Experiment No. 11Документ4 страницыLab Experiment No. 11NoorОценок пока нет

- LAB 1: TO Fpga Hardware, Control Design and Simulation: ObjectivesДокумент13 страницLAB 1: TO Fpga Hardware, Control Design and Simulation: ObjectivesAidil AzharОценок пока нет

- Experiment No. 1: Switch and Gate Level Modeling Pre Lab TaskДокумент17 страницExperiment No. 1: Switch and Gate Level Modeling Pre Lab TaskMuhammad ShoaibОценок пока нет

- Lab Sheet 6 Single Cycle Datapath FinalДокумент3 страницыLab Sheet 6 Single Cycle Datapath FinalSANJEEV MALLICKОценок пока нет

- EE 2174 Lab 9 NewДокумент6 страницEE 2174 Lab 9 NewnotdrphilОценок пока нет

- Webfpga Docs Table of Contents Chapter 1 - Webfpga Quick Start GuidesДокумент47 страницWebfpga Docs Table of Contents Chapter 1 - Webfpga Quick Start GuidesyayaОценок пока нет

- Lec3Документ38 страницLec3love639111Оценок пока нет

- CPE 316 - Laboratory 1-2 - BABATIO-1Документ17 страницCPE 316 - Laboratory 1-2 - BABATIO-1GERLAND ANDREI CUEVASОценок пока нет

- HDL Based DesignДокумент7 страницHDL Based DesignSriramamurthy GurugubelliОценок пока нет

- VO FinalДокумент140 страницVO Finalsudhasesh2000Оценок пока нет

- Verilog For PrintДокумент15 страницVerilog For PrintrppvchОценок пока нет

- Lab 7Документ9 страницLab 7zaqОценок пока нет

- PLC Programming from Novice to Professional: Learn PLC Programming with Training VideosОт EverandPLC Programming from Novice to Professional: Learn PLC Programming with Training VideosРейтинг: 5 из 5 звезд5/5 (1)

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.От EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Оценок пока нет

- Projects With Microcontrollers And PICCОт EverandProjects With Microcontrollers And PICCРейтинг: 5 из 5 звезд5/5 (1)

- Xilinx Training CoursesДокумент16 страницXilinx Training CoursesM Madan GopalОценок пока нет

- VLSI Resume SampleДокумент2 страницыVLSI Resume SampleNavdeep Panwar100% (1)

- Verilog Mobile PDFДокумент32 страницыVerilog Mobile PDFAnonymous Wu14iV9dqОценок пока нет

- VHDLДокумент33 страницыVHDLsansureОценок пока нет

- Embedded Linux Hands-On Tutorial - Zedboard: Design Is Shown in Figure 1Документ46 страницEmbedded Linux Hands-On Tutorial - Zedboard: Design Is Shown in Figure 1Federico Garcia CОценок пока нет

- Structured Digital Design Syllabus Jntuk 4-2 EceДокумент3 страницыStructured Digital Design Syllabus Jntuk 4-2 Ecevasantha_btech100% (1)

- Test Logic Insertion For Optimization of Testing Parameters On Lower Technology NodeДокумент6 страницTest Logic Insertion For Optimization of Testing Parameters On Lower Technology NodeshaguftaОценок пока нет

- Verilog® QuickstartДокумент347 страницVerilog® QuickstartYoussef ThelordОценок пока нет

- EC 6302 2-Marks and 16 Marks QuestionsДокумент12 страницEC 6302 2-Marks and 16 Marks QuestionsskaruppaiaheceОценок пока нет

- 13.M.E. Applied ElectronicsДокумент63 страницы13.M.E. Applied Electronicssushmitha vОценок пока нет

- 3 LECTURE 4 - Introduction To Verilog - EC601-DSD-AD - Lecture 3Документ120 страниц3 LECTURE 4 - Introduction To Verilog - EC601-DSD-AD - Lecture 3Divy JagetiaОценок пока нет

- Computer Engineering I (ECE290) : Digital System Design With VerilogДокумент136 страницComputer Engineering I (ECE290) : Digital System Design With VerilogTrần MạnhОценок пока нет

- ModelsimДокумент47 страницModelsimKishor KumarОценок пока нет

- LabcxfbДокумент15 страницLabcxfbRAZОценок пока нет

- Laboratory Exercise 5: Timers and Real-Time ClockДокумент3 страницыLaboratory Exercise 5: Timers and Real-Time ClockTuân PhạmОценок пока нет

- Simulation of A Communication System Using Verilog LanguageДокумент13 страницSimulation of A Communication System Using Verilog LanguageJournal of TelecommunicationsОценок пока нет

- Verilog Notes (John Wawrzynek)Документ26 страницVerilog Notes (John Wawrzynek)h.moradmand4458Оценок пока нет

- "Car Parking System in VHDL": A Micro Project Report ONДокумент12 страниц"Car Parking System in VHDL": A Micro Project Report ONParth Sushil InamdarОценок пока нет

- Synopsys' Educational Generic Memory CompilerДокумент4 страницыSynopsys' Educational Generic Memory CompilerSnehaОценок пока нет

- DDV Tutorial NewformatДокумент3 страницыDDV Tutorial NewformatChintamaneni VijayalakshmiОценок пока нет

- Digital ASIC IC Design GP RoadmapДокумент11 страницDigital ASIC IC Design GP RoadmapMina Mounir100% (1)

- Ece745: Asic Verification Lab Assignment #1: Questa Systemverilog TutorialДокумент12 страницEce745: Asic Verification Lab Assignment #1: Questa Systemverilog TutorialGarry ManochaОценок пока нет

- Basic VHDL Programming Using Xilinx FpgaДокумент6 страницBasic VHDL Programming Using Xilinx FpgaantmonibrittoОценок пока нет

- ADC DAC Interfacing With FPGA - ADC DAC VHDL CodeДокумент8 страницADC DAC Interfacing With FPGA - ADC DAC VHDL CodeAshok kumarОценок пока нет

- Lab2 Synopsys DCДокумент12 страницLab2 Synopsys DCkrunalОценок пока нет

- LitexДокумент42 страницыLitexBairon100% (1)

- Quartus TutorialДокумент13 страницQuartus TutorialFarin MahzabeenОценок пока нет

- Verilog HDL SyllabusДокумент2 страницыVerilog HDL Syllabussuhas RОценок пока нет

- EE 2174 Lab 9 NewДокумент6 страницEE 2174 Lab 9 NewnotdrphilОценок пока нет

- SystemVerilog 20041201165354Документ34 страницыSystemVerilog 20041201165354sumit kumarОценок пока нет