Академический Документы

Профессиональный Документы

Культура Документы

MOD 4-K Simple Computer - Advance Extensions

Загружено:

John DoeИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

MOD 4-K Simple Computer - Advance Extensions

Загружено:

John DoeАвторское право:

Доступные форматы

MOD 4-K: Simple Computer Advance Extensions

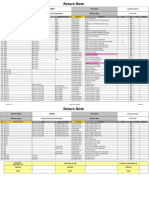

Illustration of Stack Growth:

Top of Memory

Top of Memory

Top of Memory

Top of Memory

Top of Memory

Top of Memory

Top of Memory

Top of Memory

Top of Memory

Adding Stack Manipulation Instructions

The opcodes that will be used for PSH and POP are as follows:

PSH save value in A register on stack Step 1: Decrement SP register Step 2: Store value in A register at the location pointed to by SP register

Implementation of PSH requires two execute cycles: First Execute Cycle: Second Execute Cycle: decrement SP register* (SPD) output new value of SP on address bus (SPA), enable a memory write operation (MSL and MWE), and tell the ALU to output value in the A register on the data bus (AOE)

. *Note: The new value of SP must be available (and stable) before it can be used to address memory

POP: load A with value on stack Step 1: Load A register from memory location pointed to by SP register Step 2: Increment SP register

Implementation of POP requires only one execute cycle: First Execute Cycle: -Output value of SP on address bus (SPA), enable a memory read operation (MSL and MOE) -Tell the ALU to load the A register with the value on the data bus (ALE and ALX) -Tell the SP register to increment* (SPI) *Note: The SP register will be incremented after the A register is loaded with the contents of the location pointed to by the SP register, i.e., the SP increment is overlapped with the fetch of the next instruction

" System control equations MSL = RUN.q&(S0 # S1&(LDA # STA # ADD # SUB # AND # POP)# S2&PSH); MOE = S0 # S1&(LDA # ADD # SUB # AND # POP); MWE = S1&STA # S2&PSH; ARS = START; PCC = RUN.q&S0; POA = S0; IRL = RUN.q&S0; IRA = S1&(LDA # STA # ADD # SUB # AND); AOE = S1&STA # S2&PSH; ALE = RUN.q&S1&(LDA # ADD # SUB # AND # POP); ALX = S1&(LDA # AND # POP); ALY = S1&(SUB # AND); SPI = S1&POP; SPD = S1&PSH; SPA = S1&POP # S2&PSH; RST = S1&(LDA # STA # ADD # SUB # AND # POP) # S2&PSH; END

Adding Subroutine Linkage Instructions JSR addr Jump to SubRoutine at memory location addr Step 1: Decrement SP register Step 2: Store return address* at location pointed to by SP register

Step 3: Load PC with value in IR address field The opcodes that will be used for JSR and RTS:

Implementation of JSR requires three execute cycles: First Execute Cycle: Second Execute Cycle: Decrement SP register (SPD) Output new value of SP on address bus (SPA), enable a memory write operation (MSL and MWE), and tell the PC register to output its value on the data bus (POD) Tell IR register to output its operand field on the address bus (IRA), and tell the PC register to load the value on the address bus (PLA)

Third Execute Cycle:

RTS Return From Subroutine Step 1: Load PC from memory location pointed to by SP register Step 2: Increment SP register

Implementation of RTS requires only one execute cycle: First Execute Cycle: output value of SP on address bus (SPA), enable a memory read operation (MSL and MOE), tell the PC to load the value on the data bus (PLD), and tell the SP register to increment* (SPI)

*Note: The SP register will be incremented after the PC register is loaded with the contents of the location pointed to by the SP register, i.e., the SP increment is overlapped with the fetch of the next instruction

" System control equations MSL = RUN.q&(S0 # S1&(LDA # STA # ADD # SUB # AND # RTS) # S2&JSR); MOE = S0 # S1&(LDA # ADD # SUB # AND # RTS); MWE = S1&STA # S2&JSR; ARS = START; PCC = RUN.q&S0; POA = S0; PLA = S3&JSR; POD = S2&JSR; PLD = S1&RTS; IRL = RUN.q&S0; IRA = S1&(LDA # STA # ADD # SUB # AND); AOE = S1&STA; ALE = RUN.q&S1&(LDA # ADD # SUB # AND); ALX = S1&(LDA # AND); ALY = S1&(SUB # AND); SPI = S1&RTS; SPD = S1&JSR; SPA = S1&RTS # S2&JSR; RST = S1&(LDA # STA # ADD # SUB # AND # RTS) # S3&JSR; END

Вам также может понравиться

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.От EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Оценок пока нет

- MOD 4-I Simple Computer - Bottom Up ImplementationДокумент11 страницMOD 4-I Simple Computer - Bottom Up ImplementationJohn DoeОценок пока нет

- Module-6 COMPUTER ARCHITECTUREДокумент25 страницModule-6 COMPUTER ARCHITECTUREpranaykumarghosh41Оценок пока нет

- StackДокумент4 страницыStackAbdul WahabОценок пока нет

- Central Processing Unit: Cpe 252: Computer Organization 1Документ30 страницCentral Processing Unit: Cpe 252: Computer Organization 1sulekhaisaacОценок пока нет

- Module 2 Bca CoaДокумент55 страницModule 2 Bca Coaafnanazir2004Оценок пока нет

- W03 CPU SimulatorДокумент13 страницW03 CPU SimulatorElsaday SimamoraОценок пока нет

- Lecture-31 6. Rcond: This Is A Conditional Return Statement. It Is Also A Part ofДокумент7 страницLecture-31 6. Rcond: This Is A Conditional Return Statement. It Is Also A Part ofWilliamОценок пока нет

- C-Code Software Routines For Using The SPI Interface On The MAX7456 On-Screen DisplayДокумент9 страницC-Code Software Routines For Using The SPI Interface On The MAX7456 On-Screen DisplayVinay Ashwath100% (2)

- SPI ProtocolДокумент8 страницSPI Protocolpraveenbc100% (2)

- General Laptop Power Supply Diagram (VALW Section of ADP+,+3V,+5V)Документ3 страницыGeneral Laptop Power Supply Diagram (VALW Section of ADP+,+3V,+5V)Leth ComputerRepair100% (2)

- SCS1315Документ98 страницSCS1315Sai KrishnaОценок пока нет

- Implementation of Serial Peripheral Interface (Spi) For Lpc2148 MicrocontrollerДокумент4 страницыImplementation of Serial Peripheral Interface (Spi) For Lpc2148 MicrocontrollerSanchit AgrawalОценок пока нет

- Arduino - Serial Peripheral InterfaceДокумент3 страницыArduino - Serial Peripheral Interfacewillingcoder.billionaireОценок пока нет

- cc2500 ConДокумент25 страницcc2500 Conprasad357Оценок пока нет

- UNIT-2: CPU OrganizationДокумент15 страницUNIT-2: CPU Organizationnidhish1802Оценок пока нет

- Laptop Voltage Requirement and Power Supply DiagramДокумент5 страницLaptop Voltage Requirement and Power Supply Diagrambong bernalbongОценок пока нет

- 8086 Assembler Tutorial For Beginners (Part 9)Документ1 страница8086 Assembler Tutorial For Beginners (Part 9)Ayman KattabОценок пока нет

- Csa Unit 3Документ8 страницCsa Unit 3deepОценок пока нет

- Stack OrganizationДокумент4 страницыStack OrganizationShyam VamsiОценок пока нет

- SP (Simple Processor) SpecificationДокумент4 страницыSP (Simple Processor) SpecificationrisirarocksОценок пока нет

- Co3 0Документ51 страницаCo3 0Gautam ChhabraОценок пока нет

- 6.coa Unit 2 Part 2Документ25 страниц6.coa Unit 2 Part 2my storiesОценок пока нет

- Pic 16f84a Pulse Counter - Yahoo! AnswersДокумент2 страницыPic 16f84a Pulse Counter - Yahoo! Answersanuragt_5Оценок пока нет

- Fetch-Decode-Execute CycleДокумент5 страницFetch-Decode-Execute CycleIzharSeizerОценок пока нет

- Cpu Tutorial 2Документ53 страницыCpu Tutorial 2rktiwary256034Оценок пока нет

- Unit - 2 Central Processing Unit TOPIC 1: General Register OrganizationДокумент13 страницUnit - 2 Central Processing Unit TOPIC 1: General Register OrganizationRam Prasad GudiwadaОценок пока нет

- Beginning FPGA Programming - Partie72Документ5 страницBeginning FPGA Programming - Partie72ali alilouОценок пока нет

- An Example Hardwired CPUДокумент29 страницAn Example Hardwired CPUMauro Ferreira De LimaОценок пока нет

- Mit Ocw Complex Digital Systems Lab1Документ6 страницMit Ocw Complex Digital Systems Lab1Monika YadavОценок пока нет

- Interrupts and Traps in Oberon-ARMДокумент3 страницыInterrupts and Traps in Oberon-ARMmqt99311zwoho.comОценок пока нет

- 08 CompOrgДокумент35 страниц08 CompOrgIke Mag-away GaamilОценок пока нет

- Unit 3 1.A) .Machine InstructionsДокумент13 страницUnit 3 1.A) .Machine InstructionsLovely VasanthОценок пока нет

- Sys BasconДокумент6 страницSys BasconLeonardo Rommel Escalante QuispeОценок пока нет

- UNIT III: Central Processing Unit: GeneralДокумент25 страницUNIT III: Central Processing Unit: GeneralGagandeep SinghОценок пока нет

- Etec 404Документ11 страницEtec 404Akhilesh ChaudhryОценок пока нет

- The Stack and SubroutinesДокумент28 страницThe Stack and Subroutinesuttam kumar sinhaОценок пока нет

- Topics - LC 3 - 2022Документ5 страницTopics - LC 3 - 2022Phước PhạmОценок пока нет

- (GOOD) SPI CommunicationsДокумент17 страниц(GOOD) SPI CommunicationsDuy Quang Nguyễn100% (1)

- Mic Module IVДокумент11 страницMic Module IVroshnibijuОценок пока нет

- Control BitsДокумент2 страницыControl BitsSri RamОценок пока нет

- McpuДокумент6 страницMcputpsa6668Оценок пока нет

- Lectures Section 3 ModifiedДокумент73 страницыLectures Section 3 ModifiedcoventryUkОценок пока нет

- Chapter 5Документ53 страницыChapter 5Yididiya TilahunОценок пока нет

- The Stack and SubroutinesДокумент2 страницыThe Stack and SubroutineszackОценок пока нет

- Block Diagram of Processor (Harvard)Документ48 страницBlock Diagram of Processor (Harvard)Nichita IonutОценок пока нет

- Lab Practical File: " Embedded System's "Документ17 страницLab Practical File: " Embedded System's "Saba WasimОценок пока нет

- Computer Architecture 3rd Edition by Moris Mano CH 08Документ43 страницыComputer Architecture 3rd Edition by Moris Mano CH 08Sadaf RasheedОценок пока нет

- Mod - Job Submission From CICSДокумент19 страницMod - Job Submission From CICSMainframe for everyone100% (2)

- Slides-Session 7,8 and 9Документ40 страницSlides-Session 7,8 and 9Gabbar SinghОценок пока нет

- Fundamentals of Processor Design: Using Figures From by Hamblen and FurmanДокумент35 страницFundamentals of Processor Design: Using Figures From by Hamblen and Furmanwilliamjamir2295Оценок пока нет

- 9 I2c-SpiДокумент40 страниц9 I2c-SpiTam PhamОценок пока нет

- CH 8a - The StackДокумент10 страницCH 8a - The Stackapi-237335979Оценок пока нет

- SapДокумент17 страницSap李德军Оценок пока нет

- Design Contest 2010 MentorДокумент27 страницDesign Contest 2010 MentorUjjwal KantОценок пока нет

- MAR Notes 2 - About 8051Документ6 страницMAR Notes 2 - About 8051YupniatsОценок пока нет

- Lab 10Документ5 страницLab 1015obaid.rehman20041Оценок пока нет

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationОт EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationОценок пока нет

- Conceptual Programming: Conceptual Programming: Learn Programming the old way!От EverandConceptual Programming: Conceptual Programming: Learn Programming the old way!Оценок пока нет

- Manfra - CH 6 - Quantum Mechanics IIДокумент32 страницыManfra - CH 6 - Quantum Mechanics IIJohn DoeОценок пока нет

- Cathode Ray Revisited: Wilhelm RöntgenДокумент12 страницCathode Ray Revisited: Wilhelm RöntgenJohn DoeОценок пока нет

- Purdue ECE 433 - Lecture 1Документ25 страницPurdue ECE 433 - Lecture 1John DoeОценок пока нет

- Hydrogen-Like Atoms: Energy LevelДокумент13 страницHydrogen-Like Atoms: Energy LevelJohn DoeОценок пока нет

- PHYS 342 - Lecture 18 Notes - F12Документ14 страницPHYS 342 - Lecture 18 Notes - F12John DoeОценок пока нет

- PHYS 342 - Lecture 1 Notes - F12Документ13 страницPHYS 342 - Lecture 1 Notes - F12John DoeОценок пока нет

- PHYS 342 - Lecture 3 Notes - F12Документ9 страницPHYS 342 - Lecture 3 Notes - F12John DoeОценок пока нет

- Iso 5852 SДокумент37 страницIso 5852 SGhasem A. JavidОценок пока нет

- CR95HFДокумент72 страницыCR95HFquemasda quiensoyОценок пока нет

- 8051 Interfacing LCD 16x2Документ14 страниц8051 Interfacing LCD 16x2Imran Shaukat100% (3)

- Design High Gain DC-DC Boost Converter With Coupling Inductor and Simulation in PsimДокумент8 страницDesign High Gain DC-DC Boost Converter With Coupling Inductor and Simulation in PsimInternational Journal of Research in Engineering and TechnologyОценок пока нет

- Service Manual: Multi Channel Av ReceiverДокумент90 страницService Manual: Multi Channel Av ReceiverRobson LuizОценок пока нет

- Back To Basics Vicor Power Design EbookДокумент50 страницBack To Basics Vicor Power Design Ebookmulleraf100% (1)

- Hard Disk Drive: TrainerДокумент19 страницHard Disk Drive: TraineramuljuneОценок пока нет

- LM4811 Dual 105mW Headphone Amplifier With Digital Volume Control and Shutdown ModeДокумент20 страницLM4811 Dual 105mW Headphone Amplifier With Digital Volume Control and Shutdown ModeBuga BuniciОценок пока нет

- Ah5f GaДокумент2 страницыAh5f GaNelson P. ColoОценок пока нет

- Battery Charger Range Technical Documentation en c2017 PDFДокумент24 страницыBattery Charger Range Technical Documentation en c2017 PDFAnonymous RcxX0FcОценок пока нет

- VX-2100 - 2200 VHF 2013 Ec061n90kДокумент86 страницVX-2100 - 2200 VHF 2013 Ec061n90kquinquinoОценок пока нет

- Chapter 7 Project Problem: Noise Equivalent Bandwidth: BackgroundДокумент4 страницыChapter 7 Project Problem: Noise Equivalent Bandwidth: BackgroundAndrew WagehОценок пока нет

- MN04020003EДокумент204 страницыMN04020003EElderJoaoОценок пока нет

- Dem 20487 Syh-LyДокумент14 страницDem 20487 Syh-LyPreda AndreiОценок пока нет

- Introduction To Computing:: Computer SystemsДокумент27 страницIntroduction To Computing:: Computer SystemsPhan Giang ChâuОценок пока нет

- Sharp lc60 70 80uq10kn893 Training DocumentДокумент99 страницSharp lc60 70 80uq10kn893 Training DocumentWee Chuan Poon100% (1)

- Analog Elektronik Ders Notları YTUДокумент50 страницAnalog Elektronik Ders Notları YTUAhmet DelenОценок пока нет

- Chapter 4: Memory Built in Chapter 4: Memory Built-In Self-Test Self TestДокумент52 страницыChapter 4: Memory Built in Chapter 4: Memory Built-In Self-Test Self TestPradeepRoyalОценок пока нет

- Op Amps - Solved ProblemsДокумент28 страницOp Amps - Solved ProblemsAaron Mueller86% (14)

- NAND Chip Mask ROM Mode Short LocationДокумент8 страницNAND Chip Mask ROM Mode Short LocationmrtuktukОценок пока нет

- Eet205 Analog Electronics, December 2021Документ3 страницыEet205 Analog Electronics, December 2021Midun RamkumarОценок пока нет

- The World's Most Popular DGPS Beacon Module: Key - 4 AdvantagesДокумент2 страницыThe World's Most Popular DGPS Beacon Module: Key - 4 AdvantagesAranОценок пока нет

- Previous GATE Questions On K Map, SOP and POS Expressions (1987 Till Date)Документ5 страницPrevious GATE Questions On K Map, SOP and POS Expressions (1987 Till Date)DHRUV CHAUHANОценок пока нет

- ATI FirePro V7800 DatasheetДокумент2 страницыATI FirePro V7800 Datasheetjbarboza2236Оценок пока нет

- Datasheet PDFДокумент4 страницыDatasheet PDFelkinОценок пока нет

- 1000 Watts Ups Circuit DiagramДокумент24 страницы1000 Watts Ups Circuit DiagramMuhammad Salman Khan100% (2)

- 8-Channel Electronic Volume With Input SelectorДокумент22 страницы8-Channel Electronic Volume With Input SelectorRADON electronicsОценок пока нет

- Medusa 4 TS 09 033Документ2 страницыMedusa 4 TS 09 033doantran2508Оценок пока нет

- FT 180a PDFДокумент60 страницFT 180a PDFFabian EtcheniqueОценок пока нет

- RN Atb002 Dismantle Telkomsel NTTДокумент2 страницыRN Atb002 Dismantle Telkomsel NTTSandy Vj TaneoОценок пока нет