Академический Документы

Профессиональный Документы

Культура Документы

Assignment 2 E5163 Sesi Jun 2011 Answer PDF

Загружено:

senyadnoireИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Assignment 2 E5163 Sesi Jun 2011 Answer PDF

Загружено:

senyadnoireАвторское право:

Доступные форматы

Department of Electrical Engineering Politeknik Port Dickson

PROGRAMME : DTK6-S1, DTK6-S2 CODE & COURSE NAME : E5163- INTEGRATEED CIRCUIT DESIGN TITLE : MOS Transistor Fabrication IC Design Methodology ASSIGNMENT :2 MATRIX NO. : NAME: DATE : 27 September 2011

I STRUCTIO : A SWER ALL QUESTIO S.

1. Explain the NMOS transistor fabrication process sequence based on wafer cross-section diagram shown in Figure 1.

Source Gate Drain Polysilicon SiO2

n+ p

n+ bulk Si

Figure 1 (12 marks, CLO2, JSP3.1, M)

2. Draw the physical structure of a Twin-tub CMOS transistor. (3 marks, CLO2, JSP3.2, L)

Department of Electrical Engineering Politeknik Port Dickson

PROGRAMME : DTK6-S1, DTK6-S2 CODE & COURSE NAME : E5163- INTEGRATEED CIRCUIT DESIGN TITLE : MOS Transistor Fabrication IC Design Methodology ASSIGNMENT :2 MATRIX NO. : NAME: DATE : 27 September 2011

I STRUCTIO : A SWER ALL QUESTIO S.

3. Explain the characteristic of a Twin-tub CMOS transistor. (3 marks, CLO2, JSP3.2, M)

** Any 3 related explanation.

(3 marks)

The starting material is a n+ or p+ substrate, with a lightly doped epitaxial layer (~1015/cm3, 10 -cm) on top. n-well and the p-well are formed in epitaxial layer. Suitable for high-performance chips. Since the substrate is lightly doped, there is less chance for latch-up because of the high resistivity.

4. What is the purpose of Well Tap and Substrate Tap in the physical structure of a CMOS inverter? (2 marks, CLO2, JSP3.3, L)

A P-type substrate "tap" is connected to VSS and an N-type n-well tap is connected to VDD to prevent Latchup. (2 marks)

5. Explain the parasitic capacitance problem that exists in CMOS transistor operation. (5 marks, CLO2, JSP3.3, M)

(2 marks) ** Any 3 related explanation. (3 marks) Parasitic capacitance is the unavoidable and usually unwanted capacitance that exists between Gate-Source and Get-Drain simply because of their proximity to each other. At low frequencies parasitic capacitance can usually be ignored, but in high frequency circuits it is a major problem. The parasitic capacitance between the base and collector of transistors and other active devices is the major factor limiting their high frequency performance. It could result in false switching in high frequency circuits.

Department of Electrical Engineering Politeknik Port Dickson

PROGRAMME : DTK6-S1, DTK6-S2 CODE & COURSE NAME : E5163- INTEGRATEED CIRCUIT DESIGN TITLE : MOS Transistor Fabrication IC Design Methodology ASSIGNMENT :2 MATRIX NO. : NAME: DATE : 27 September 2011

I STRUCTIO : A SWER ALL QUESTIO S.

6. Draw the physical structure of Silicon On Insulator (SOI). (3 marks, CLO2, JSP3.2, L)

(3 marks)

7. Explain the characteristic of Silicon on insulator (SOI) CMOS transistor. (3 marks, CLO2, JSP3.2, M)

Completely isolated nMOS and pMOS transistors side-by-side on an insulating substrate. higher integration density complete avoidance of the latch-up problem lower parasitic capacitances compared to n-well or twin-tub CMOS.

(5 marks, CLO2, JSP3.3, M)

8. Explain the latch-up problem that exists in CMOS transistor operation.

Latchup is a type of short circuit which can occur in an improperly designed circuit. It is an unintentional creation of a low resistance path between the VDD and GND triggering a parasitic structure which disrupts proper functioning of the part and possibly even leading to its destruction due to overcurrent. The parasitic structure is usually equivalent to a thyristor (or SCR), a PNPN structure which acts as a PNP and an NPN transistor stacked next to each other. During a latchup when one of the transistors is conducting, the other one begins conducting too. They both keep each other in saturation for as long as the structure is forward-biased and some current flows through it - which usually means until a power-down.

Department of Electrical Engineering Politeknik Port Dickson

PROGRAMME : DTK6-S1, DTK6-S2 CODE & COURSE NAME : E5163- INTEGRATEED CIRCUIT DESIGN TITLE : MOS Transistor Fabrication IC Design Methodology ASSIGNMENT :2 MATRIX NO. : NAME: DATE : 27 September 2011

I STRUCTIO : A SWER ALL QUESTIO S. A power cycle is required to correct this situation.

9. Define Application-Specific Integrated Circuit (ASICs). (2 marks, CLO3, JSP4.1, L)

Application Specific Integrated Circuit or ASIC is a chip that is custom designed for a specific application rather than a general-purpose chip such as a microprocessor. (2 marks)

10. Discuss the advantages and disadvantages of Specific-Custom IC over Standard IC. (6 marks, CLO3, JSP4.1, H)

i. Specific-custom IC have better performance, but they have higher manufacturing costs and lack the flexibility. If there is a change in the application, it is hard to reflect the change in the design. (3 marks) ii. Standard IC, on the other hand, are not optimized for a specific applications and hence do not provide satisfactory performance for most of the applications. (3 marks)

11. Compare the differences between Semi-Custom methodology and Full-Custom methodology. (6 marks, CLO3, JSP4.2, JSP4.3, H)

** Any 3 related answer for Semi-Custom. (3 marks) ** Any 3 related answer for Full-Custom. (3 marks) Semi-Custom Larger chip size. Less number of mask. Shorter design time. Poor performance. Full-Custom Smaller chip size. More number of mask. Longer design time. High performance.

12. Describe Standard Cell Library. (5 marks, CLO3, JSP4.5, L)

A Standard Cell Library is a collection of low-level logic functions such as AND, OR, INVERT, flipflops, latches, and buffers. These cells are realized as fixed-height, variable-width full-custom cells. The key aspect with these libraries is that they are of a fixed height, which enables them to be placed in rows, easing the process of automated digital layout. The cells are typically optimized full-custom layouts, which minimize delays and area.

Department of Electrical Engineering Politeknik Port Dickson

PROGRAMME : DTK6-S1, DTK6-S2 CODE & COURSE NAME : E5163- INTEGRATEED CIRCUIT DESIGN TITLE : MOS Transistor Fabrication IC Design Methodology ASSIGNMENT :2 MATRIX NO. : NAME: DATE : 27 September 2011

I STRUCTIO : A SWER ALL QUESTIO S.

13. Discuss the advantages and disadvantages of Standard cells methodology. (6 marks, CLO3, JSP4.5, H)

Advantages: (3 marks) 1. Short design turn-around time as the cells are predefined and need only to be laid out and connected. 2. The standard cell method allows each cell to be optimized individually. Thus, higher performance designs can be created, because each cell can be optimized for maximum speed and minimum area.

Disadvantages: (3 marks) 1. Wasted chip area will be high, the area occupied by the wiring channels can exceed 50% of the internal chip. However, this problem can be greatly reduced by using multiple metal layers in chip designs. 2. Since the cells are not prefabricated ahead of time, there is no savings in fabrication time.

14. Discuss at least 2 methods to increase the percentage of gate usage in gate array design. (4 marks, CLO3, JSP4.4, M)

(4 marks) i. Increase number of gates by increasing functionality. ii. Decrease number of available gates by providing just enough gates for interconnection.

15. Explain the advantages and disadvantages of full-custom methodology. (6 marks, CLO3, JSP4.2, M)

Advantages of Full-Custom Methodology: (3 marks) Improve performance Reduce power consumption Mix Analog and Digital Designs Design optimization through IC manufacturing process Development Tools support HDL and Schematic design approach Disadvantages of Full-Custom Methodology: Inflexible design Deployed systems can not be upgraded Mistakes in product development are costly Updates requires a redesign Complex and expensive development tools (3 marks)

Department of Electrical Engineering Politeknik Port Dickson

PROGRAMME : DTK6-S1, DTK6-S2 CODE & COURSE NAME : E5163- INTEGRATEED CIRCUIT DESIGN TITLE : MOS Transistor Fabrication IC Design Methodology ASSIGNMENT :2 MATRIX NO. : NAME: DATE : 27 September 2011

I STRUCTIO : A SWER ALL QUESTIO S.

16. Explain the gate-array design floor plan with aid of a diagram. (7 marks, CLO3, JSP4.4, M)

rows of uncommitted cells

routing channel

(3 marks) A gate-array (MPGAs) consists of transistors prefabricated on a wafer in the form of a regular 2-D array. Initially the transistors in an array are not connected to one another. In order to realize a circuit on a gate-array, metal connections must be placed using the usual process of masking (personalizing). (4 marks)

17. Describe the design methodology selection criteria. (5 marks, CLO3, JSP4.6, H) Methodology depends on: Type of chip Size of chip design time constraints Cost/performance Available tools

Вам также может понравиться

- Gain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipОт EverandGain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipОценок пока нет

- Assignment IcДокумент10 страницAssignment IcsenyadnoireОценок пока нет

- MOS Integrated Circuit DesignОт EverandMOS Integrated Circuit DesignE. WolfendaleОценок пока нет

- Pw1 Cmos Daniel f1070Документ9 страницPw1 Cmos Daniel f1070iskandardaniel0063Оценок пока нет

- Three Dimensional CMOS Devices and Integrated Circuits: JakubДокумент8 страницThree Dimensional CMOS Devices and Integrated Circuits: JakubGauri Shankar SinghОценок пока нет

- Design for High Performance, Low Power, and Reliable 3D Integrated CircuitsОт EverandDesign for High Performance, Low Power, and Reliable 3D Integrated CircuitsОценок пока нет

- Design and Analysis of Different Circuits Using DCVSL & Static CMOS TechniqueДокумент7 страницDesign and Analysis of Different Circuits Using DCVSL & Static CMOS TechniqueGRD JournalsОценок пока нет

- Cad Asic Extra QuestionДокумент18 страницCad Asic Extra QuestionDin_skyDОценок пока нет

- Model Exam StudentДокумент2 страницыModel Exam StudentSornagopal VijayaraghavanОценок пока нет

- Reviews: Nanoelectronics Era: Novel Device Technologies Enabling Systems On ChipsДокумент14 страницReviews: Nanoelectronics Era: Novel Device Technologies Enabling Systems On ChipsRajdeep BanerjeeОценок пока нет

- MicroelectronicsДокумент39 страницMicroelectronicsArun Av0% (1)

- 3-D Ics Seminar Report 2011-2012Документ29 страниц3-D Ics Seminar Report 2011-2012Jamsheer KpОценок пока нет

- D Ics Seminar Report 10Документ25 страницD Ics Seminar Report 10Deepti BalaОценок пока нет

- 3 DicsДокумент35 страниц3 DicsJnaresh NareshОценок пока нет

- Low Voltage Analog Circuit Design Techniques A TutorialДокумент17 страницLow Voltage Analog Circuit Design Techniques A TutorialRafael Rguez SОценок пока нет

- 3 - D ICsДокумент35 страниц3 - D ICsBibinMathewОценок пока нет

- Seminar Report 08Документ29 страницSeminar Report 08Mounikac40% (5)

- D ICsДокумент24 страницыD ICsKonara KiranОценок пока нет

- 3 - D ICsДокумент35 страниц3 - D ICsKhusi ArnavОценок пока нет

- Chenming-Hu ch7Документ32 страницыChenming-Hu ch7Dr Kavita KhareОценок пока нет

- 3 - D ICsДокумент31 страница3 - D ICsSudheesh VsОценок пока нет

- A200911 1003Документ6 страницA200911 1003polururamОценок пока нет

- 3 - D ICsДокумент35 страниц3 - D ICsSamhith ReddyОценок пока нет

- Imp 2Документ7 страницImp 2sohailasghar_tОценок пока нет

- Analytical Model For Surface Potential and Inversion Charge of Dual Material Double Gate Son MosfetДокумент5 страницAnalytical Model For Surface Potential and Inversion Charge of Dual Material Double Gate Son Mosfetanil kasotОценок пока нет

- 3-D ICsДокумент35 страниц3-D ICsNikitha GОценок пока нет

- Design Project 3 AssignmentДокумент4 страницыDesign Project 3 AssignmentHieu Nguyen TriОценок пока нет

- 3 - D ICsДокумент35 страниц3 - D ICsSano SanojОценок пока нет

- 3d ICs Full Seminar Report 2Документ31 страница3d ICs Full Seminar Report 2Shweta R Burli0% (1)

- Low Power VLSI Design Techniques A ReviewДокумент12 страницLow Power VLSI Design Techniques A Reviewvenkateshprasad1562812Оценок пока нет

- Cad PD AssignmentДокумент19 страницCad PD AssignmentRadhika KalawatОценок пока нет

- VLSI Fabrication and CharacterizationДокумент40 страницVLSI Fabrication and CharacterizationKarthik RamasamyОценок пока нет

- Low-Power VLSI Design Using Dynamic-Threshold LogicДокумент6 страницLow-Power VLSI Design Using Dynamic-Threshold LogicravindarsinghОценок пока нет

- Study and Analysis of Advanced 3D Multi-GateДокумент15 страницStudy and Analysis of Advanced 3D Multi-GateRaj sambhavОценок пока нет

- Design and AnalysisДокумент4 страницыDesign and Analysisbonat07Оценок пока нет

- Rahul.P (3 023 PD16EI) : Seminar Report ONДокумент13 страницRahul.P (3 023 PD16EI) : Seminar Report ONRahul PawarОценок пока нет

- Low Power and High Performance JK Flip - Flop Using 45 NM TechnologyДокумент5 страницLow Power and High Performance JK Flip - Flop Using 45 NM Technologyswetha sillveriОценок пока нет

- 2014 MR - Metal-Layer Capacitors in The 65 NM CMOS Process and The Application For Low-Leakage Power-Rail ESD Clamp CircuitДокумент7 страниц2014 MR - Metal-Layer Capacitors in The 65 NM CMOS Process and The Application For Low-Leakage Power-Rail ESD Clamp CircuitspaulsОценок пока нет

- Vlsi Design - Ec - 701 - Unit - IДокумент37 страницVlsi Design - Ec - 701 - Unit - Iangelcrystl4774Оценок пока нет

- Project Report On Integrated CircuitДокумент20 страницProject Report On Integrated CircuitSushil Kumar67% (6)

- Cmos Logic Families For Vlsi DesignДокумент12 страницCmos Logic Families For Vlsi DesignRishav YadavОценок пока нет

- CnuДокумент27 страницCnuMahesh BejgumОценок пока нет

- Extremly ScaledДокумент14 страницExtremly ScaledeleenaamohapatraОценок пока нет

- Low-Voltage High-Speed CML D-Latches in Nanometer CMOS TechnologiesДокумент12 страницLow-Voltage High-Speed CML D-Latches in Nanometer CMOS TechnologiesHemanthОценок пока нет

- Vision 2K11: "Trigate Transistors"Документ15 страницVision 2K11: "Trigate Transistors"Amruta PatilОценок пока нет

- SCE 100nmДокумент48 страницSCE 100nmGoogle acntОценок пока нет

- EC NotesДокумент2 страницыEC Noteshanumantha12Оценок пока нет

- Inverter LayoutДокумент22 страницыInverter LayoutPriyal PatelОценок пока нет

- P 103Документ7 страницP 103An HoaОценок пока нет

- Tutorial PADRE Simulation ToolsДокумент45 страницTutorial PADRE Simulation Toolsss626Оценок пока нет

- KN MishraДокумент2 страницыKN MishraKumaran Raj KОценок пока нет

- Low Power 6-Transistor Latch Design For Portable DevicesДокумент16 страницLow Power 6-Transistor Latch Design For Portable DevicesjayalakshmisnairОценок пока нет

- On PD-SOIДокумент27 страницOn PD-SOIpramodagarwal_nitrklОценок пока нет

- Double Gate MosfetДокумент23 страницыDouble Gate MosfetSoumyabrata DeОценок пока нет

- 279 E317 PDFДокумент6 страниц279 E317 PDFJubin JainОценок пока нет

- 3 D IcsДокумент15 страниц3 D IcsputtasatishОценок пока нет

- Impact of Gate Induced Drain Leakage On Overall Leakage of Submicrometer CMOS VLSI CircuitsДокумент10 страницImpact of Gate Induced Drain Leakage On Overall Leakage of Submicrometer CMOS VLSI Circuits275108006Оценок пока нет

- Assignment IcДокумент2 страницыAssignment IcsenyadnoireОценок пока нет

- VLSI Design IntroДокумент62 страницыVLSI Design IntroThuy TopОценок пока нет

- Importing Data Into MS Access With ODBCДокумент13 страницImporting Data Into MS Access With ODBCsenyadnoireОценок пока нет

- IcДокумент2 страницыIcsenyadnoireОценок пока нет

- IcДокумент2 страницыIcsenyadnoireОценок пока нет

- Industri DesignДокумент1 страницаIndustri DesignsenyadnoireОценок пока нет

- Monogatari SeriesДокумент1 страницаMonogatari SeriessenyadnoireОценок пока нет

- ProgrammingДокумент73 страницыProgrammingsenyadnoireОценок пока нет

- Monogatari SeriesДокумент1 страницаMonogatari SeriessenyadnoireОценок пока нет

- Friends by Manu MenonДокумент1 страницаFriends by Manu MenonsenyadnoireОценок пока нет

- Bab 1-1introДокумент5 страницBab 1-1introsenyadnoireОценок пока нет

- Mister MillionaireДокумент1 страницаMister MillionairesenyadnoireОценок пока нет

- Kamen No HanayomeДокумент1 страницаKamen No HanayomesenyadnoireОценок пока нет

- User Manual 22mt44dp-pzДокумент36 страницUser Manual 22mt44dp-pzVideoHi VizanteaОценок пока нет

- Decca TreeДокумент4 страницыDecca Treeiuridicaprima4Оценок пока нет

- Some Antenna and Propagation Fundamentals: March 2011Документ60 страницSome Antenna and Propagation Fundamentals: March 2011heruОценок пока нет

- Linear Link™: Installation, Operation and Maintenance ManualДокумент44 страницыLinear Link™: Installation, Operation and Maintenance ManualAlan Barros SallesОценок пока нет

- 742264Документ2 страницы742264Taposh Kumar BiswasОценок пока нет

- GE Renewal Parts: Contactor Model 17Cm53E10AДокумент3 страницыGE Renewal Parts: Contactor Model 17Cm53E10ARafael Dutil LucianaОценок пока нет

- Features: - 1 Watt CW - 26.5-40 GHZ - 20 V/M & 50 V/MДокумент2 страницыFeatures: - 1 Watt CW - 26.5-40 GHZ - 20 V/M & 50 V/Mraj1388Оценок пока нет

- ECE1007 Syllabus Opto - March 2019Документ3 страницыECE1007 Syllabus Opto - March 2019ASHUTOSH MOHAPATRA 18BLC1035Оценок пока нет

- HS-PX590 HS-PX997: Service ManualДокумент12 страницHS-PX590 HS-PX997: Service ManualSebastian Winged Neko KippОценок пока нет

- Igcse Physics c9 Prac Questions MSДокумент6 страницIgcse Physics c9 Prac Questions MShuxxiОценок пока нет

- 09072310301310Документ18 страниц09072310301310Walker BautistaОценок пока нет

- Ecodial 336Документ92 страницыEcodial 336trinhnhattienОценок пока нет

- Ecet321l - E1 - Single Stage Ce AmplifierДокумент9 страницEcet321l - E1 - Single Stage Ce AmplifierKenneth DomingoОценок пока нет

- Betaflight Tuning Blackbox 20200506Документ11 страницBetaflight Tuning Blackbox 20200506antozoneОценок пока нет

- Stricker FuseДокумент65 страницStricker FuseONILEDA1970Оценок пока нет

- DBV 200Документ36 страницDBV 200Cristian Villani SulezОценок пока нет

- 6.1 Sampling and Reconstruction of Analog Signals: Piyush Kumar 20104148901 G.E.C, KaimurДокумент9 страниц6.1 Sampling and Reconstruction of Analog Signals: Piyush Kumar 20104148901 G.E.C, KaimurEr VishuuuОценок пока нет

- Industrial Electronic ReportДокумент5 страницIndustrial Electronic ReportAkmal HazimОценок пока нет

- Bpy FluorescentДокумент3 страницыBpy FluorescentmegaОценок пока нет

- Canon 7161 Service ManuelДокумент346 страницCanon 7161 Service ManuelkopisanОценок пока нет

- Rekt 004 Day 5Документ60 страницRekt 004 Day 5Kish ShenoyОценок пока нет

- Intelligent Mobile ROBOT Navigation Technique Using RFID TechniqueДокумент29 страницIntelligent Mobile ROBOT Navigation Technique Using RFID TechniquenehakolheОценок пока нет

- Bankura MapДокумент27 страницBankura MapSUSOVAN BISWASОценок пока нет

- 5G RAN Feature Documentation 5G RAN2.1 - 07 20201229173029Документ54 страницы5G RAN Feature Documentation 5G RAN2.1 - 07 20201229173029juliosantanaОценок пока нет

- GB38031-2020EN Electric Vehiles Traction Battery Safety RequerimentsДокумент15 страницGB38031-2020EN Electric Vehiles Traction Battery Safety RequerimentsMarianoОценок пока нет

- 6 PTT Brush Holders Plug Sets Brush Holders MersenДокумент2 страницы6 PTT Brush Holders Plug Sets Brush Holders MersenIstvan MajorОценок пока нет

- Operation and Maintenance Instructions: Medipoint 26 Alarm System Local AlarmДокумент22 страницыOperation and Maintenance Instructions: Medipoint 26 Alarm System Local AlarmShoaib KhanОценок пока нет

- Specification For Motor Actuators For ValvesДокумент13 страницSpecification For Motor Actuators For ValvesDanish MohammedОценок пока нет

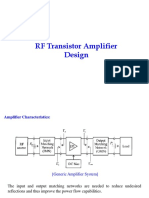

- Lecture 2 RF Amplifier DesignДокумент50 страницLecture 2 RF Amplifier DesignVenkata Pradeep SangepuОценок пока нет

- Basic Metal DetectionДокумент36 страницBasic Metal DetectionAnthony ProdeniantaОценок пока нет

- Hacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxОт EverandHacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxОценок пока нет

- Chip War: The Quest to Dominate the World's Most Critical TechnologyОт EverandChip War: The Quest to Dominate the World's Most Critical TechnologyРейтинг: 4.5 из 5 звезд4.5/5 (227)

- CompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)От EverandCompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)Рейтинг: 5 из 5 звезд5/5 (1)

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XОт EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XРейтинг: 3 из 5 звезд3/5 (2)

- Chip War: The Fight for the World's Most Critical TechnologyОт EverandChip War: The Fight for the World's Most Critical TechnologyРейтинг: 4.5 из 5 звезд4.5/5 (82)

- CompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)От EverandCompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)Рейтинг: 5 из 5 звезд5/5 (2)

- Amazon Web Services (AWS) Interview Questions and AnswersОт EverandAmazon Web Services (AWS) Interview Questions and AnswersРейтинг: 4.5 из 5 звезд4.5/5 (3)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102От EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Рейтинг: 5 из 5 звезд5/5 (2)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]От EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Рейтинг: 5 из 5 звезд5/5 (1)

- Programming with STM32: Getting Started with the Nucleo Board and C/C++От EverandProgramming with STM32: Getting Started with the Nucleo Board and C/C++Рейтинг: 3.5 из 5 звезд3.5/5 (3)

- How to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideОт EverandHow to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideРейтинг: 1 из 5 звезд1/5 (1)

- Amazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesОт EverandAmazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesОценок пока нет

- Windows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertОт EverandWindows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertРейтинг: 3.5 из 5 звезд3.5/5 (6)

- How To Market Mobile Apps: Your Step By Step Guide To Marketing Mobile AppsОт EverandHow To Market Mobile Apps: Your Step By Step Guide To Marketing Mobile AppsОценок пока нет

- Patterns in the Machine: A Software Engineering Guide to Embedded DevelopmentОт EverandPatterns in the Machine: A Software Engineering Guide to Embedded DevelopmentРейтинг: 5 из 5 звезд5/5 (1)

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsОт EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsРейтинг: 5 из 5 звезд5/5 (1)

- Raspberry Pi | 101: The Beginner’s Guide with Basics on Hardware, Software, Programming & ProjecОт EverandRaspberry Pi | 101: The Beginner’s Guide with Basics on Hardware, Software, Programming & ProjecОценок пока нет

- CompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102От EverandCompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Оценок пока нет

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-2-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1714737415?v=1)