Академический Документы

Профессиональный Документы

Культура Документы

DLC Question Bank

Загружено:

ecessecИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

DLC Question Bank

Загружено:

ecessecАвторское право:

Доступные форматы

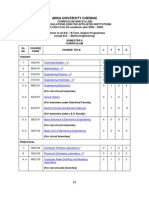

QUESTION BANK SUBJECT NAME: DIGITAL LOGIC CIRCUITS YEAR / SEM: II / IV UNIT I BOOLEAN ALGEBRA AND COMBINATIONAL CIRCUITS

PART-A (2 MARKS)

1. What is variable mapping? 2. Name the two canonical forms for Boolean algebra. 3. State the steps involved in Gray to binary conversion? 4. State De Morgan's theorem. 5. Reduce A'B'C' + A'BC' + A'BC 6. Prove that ABC + ABC' + AB'C + A'BC = AB + AC + BC 7. State the limitations of karnaugh map. 8. What is a full-adder? 9. What is Magnitude Comparator? 10. What is code conversion? 11. Give an application each for a mux and demux. 12. What is a priority encoder? 13. Implement the given function in 4:1 mux f= m(0,1,3,5,6) 14. Can a decoder function as a Demultiplexer? 15. What are prime-implicants?

PART-B 1. Obtain the minimum sop using QUINE- McCLUSKY method and verify using K-map F=m0+m2+m4+m8+m9+m10+m11+m12+m13 (16) 2. Reduce the following using tabulation method. (16) F=m2+m3+m4+m6+m7+m9+m11+m13. 3. Reduce the Boolean function using k-map technique and implement using gates f (w, x, y, z)= m (0,1,4,8,9,10) which has the dont cares condition d (w, x, y, z)= m (2,11). (16) 4. a) Design an 8421 to gray code converter. (8) b) Implement the Boolean function using 8:1 mux. (8) F (A, B, C, D) =ABD+ACD+BCD+ACD. 5. Design A Full Adder And A Full Subtractor. (16) 6. A combinational circuit is defined by the following three Boolean functions F1 = xyz+xz F2= xyz+xy F3= xyz+xy Design the circuit with a decoder and external gates. (16) 7. Simplify the following Boolean function by using Tabulation method F (w, x, y, z) =m (0, 1, 2, 8, 10, 11, 14, 15) (16) 8. Simplify the following Boolean functions by using KMap in SOP & POS. F (w, x, y, z) = m (1, 3, 4, 6, 9, 11, 12, 14) (16) 9. a) Design a 2 bit magnitude comparator. (8) b) Explain the operation of 4 to 10 decoder.

UNIT II SYNCHRONOUS SEQUENTIAL SIRCUITS PART-A (2 MARKS) 1. Write the characteristic equations for Jk and D Flip Flops. 2. How can a D flip flop be converted into T flip-flop? 3. What is meant by the term edge triggered? 4. How many ffs are required to design a mod-7 up down counter? 5. Define synchronous sequential circuit 6. Define flip flop 7. What is race around condition? 8. What is the difference between synchronous and asynchronous counter? 9. What is meant by modulus of a counter? 10. What is a state equation? PART B 1. A sequential circuit has 2D ffs A and B an input x and output y is specified by the following next state and output equations. A (t+1)= Ax + Bx B (t+1)= Ax Y= (A+B) x (i) Draw the logic diagram of the circuit. (ii) Derive the state table. (iii) Derive the state diagram. (16) 2. Design a mod-10 synchronous counter using Jk ff. write excitation table and state table. (16) 3. a)Write the excitation tables of SR, JK, D, and T Flip flops (8) b) Realize D and T flip flops using Jk flip flops (8) 4. Design a sequential circuit using JK flip-flop for the following state table [use state diagram] (16) 5. Design a counter with the following repeated binary sequence:0, 1, 2, 3, 4, 5, 6.use JK Flip-flop. (16)

UNIT III ASYNCHRONOUS SEQUENTIAL CIRCUIT PART-A (2 MARKS) 1. Distinguish between synchronous and asynchronous sequential circuits 2. What is an essential hazard and how to eliminate it? 3. What is meant by state assignment? 4. Define Asynchronous sequential circuit? 5. What is the significance of state assignment? 6. What is primitive flow chart? 7. What is fundamental mode? 8. What are the steps for the design of asynchronous sequential circuit? 9. Define merger graph. 10. When do race conditions occur?

PART B 1. Design an asynchronous sequential circuit that has 2 inputs x2 and x1, and one output z. the output is to remain 0 as long as an X1 is 0. The first change in x2 that occurs while x1 is 1 will cause z to be 1. Z is to remain 1 until x1 returns to 0. Construct a state diagram and flow table. Determine the output equations. (16) 2. Design a circuit with inputs A and B to give an output z=1 when AB=11 but only if A becomes 1 before B, by drawing total state diagram, primitive flow table and output map in which transient state is included. (16) 3. Obtain the primitive flow table for an asynchronous circuit that has 2 inputs x, y and output z. an output z=1, is to occur only during the input state xy=01 and then if and only if the input state xy=01 is preceded by the input sequence xy=01, 00, 10, 00, 10, 00 (16)

4. Design a circuit with input a and b to give an output z=1 when AB =11 but only if A becomes 1 before B, by drawing total state diagram, primitive flow table and output map in which transient state is included. (16) 5. Design a asynchronous sequential circuit with 2 inputs T and C. The output attains a value of 1 when T = 1 & c moves from 1 to 0. Otherwise the output is 0. (16) 6. Design an Asynchronous sequential circuit using SR latch with two inputs A and B and one output y. B is the control input which, when equal to 1, transfers the input A to output y. when B is 0, the output does not change, for any change in input.

UNIT-IV PROGRAMMABLE LOGIC DEVICS ,MEMORY AND LOGIC FAMILIES PART-A (2 MARKS) 1. Mention the classification of saturated bipolar logic families 2. What are the difference between PLA and PAL? 3. What is the major difference between ECL and TTL? 4. What are the types of TTL logic? 5. Define address and word: 6. What is programmable logic array? How it differs from ROM? 7. Explain EPROM. 8. Give the classification of PLDs. 9. Define Static RAM and dynamic RAM

PART B 1. a) Explain in detail about PLA with a specific example. (8) b) Explain with neat diagrams RAM architecture (8) 2. Implement the following function using PLA. A (x, y, z) = m (1, 2, 4, 6) B (x, y, z) = m (0, 1, 6, 7) C (x, y, z) = m (2, 6) (16) 3. Implement the following function using PAL. W (A, B, C, D) = m (2, 12, 13) X (A, B, C, D) = m (7, 8, 9, 10, 11, 12, 13, 14, 15) Y (A, B, C, D) = m (0, 2, 3, 4, 5, 6, 7, 8, 10, 11, 15) Z (A, B, C, D) = m (1, 2, 8, 12, 13) (16) 4. Discuss on the concept of working and applications of following memories. i) ROM ii) EPROM iii) PLA. (16) 5. i) A combinational circuit is defined by the functions. F1 (a, b, c) = m (3, 5, 6, 7) F2 (a, b, c) = m (0, 2, 4, 7) implement the circuit with a PLA. (8) ii) Write short notes on semiconductor memories (8) 6. a) compare the various digital logic families. (8) b) Write notes on FPGA. (8)

UNIT V VHDL PART-A (2 MARKS) 1. What do the acronyms VHDL and VHLSI stand for? 2. What are the advantages of using a hard ware description language? 3. What is VHDL? 4. What are the features of VHDL 5. Define entity 6. What do you meant by concurrent statement 7. Define VHDL package 8. What are the operates used in VHDL language 9. Give short notes on logic simulation and logic synthesis 10. What do you mean by test bench PART B 1. Write a HDL code for state machine to BCD to ex 3 codes Converter (16) 2. Write a behavioral VHDL description of the 4 bit counter (16) 3. (I) Write VHDL code for a full sub tractor using logic Equation (8) (II) Write a VHDL description of an S-R latch using a process (8) 4. Write a HDL code for 8:1 MUX using behavioral model (16) 5. Write the HDL description of the circuit specified by the Following Boolean equations (16) S = xy + x y C =xy 6. (I) Write an HDL data flow description of a 4 bit adder subtractor of Unsigned numbers use the conditional operator (8) (II) Write the HDL gate level description of the priority encoder (8) *****************************************

SREE SAKTHI ENGINERING COLLEGE

COIMBATORE - 641104

Вам также может понравиться

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- MS710 MS711 MS810 MS811 MS812 M5150 M5160 M5170 4063 SM PDFДокумент645 страницMS710 MS711 MS810 MS811 MS812 M5150 M5160 M5170 4063 SM PDFlftrevОценок пока нет

- DSP SamplingДокумент36 страницDSP Samplingin_visible100% (1)

- Lab Requirements of Ece: Infrastructure Requirement As Per Aicte NormsДокумент4 страницыLab Requirements of Ece: Infrastructure Requirement As Per Aicte NormsecessecОценок пока нет

- Electrical Circuit Lab ManualДокумент38 страницElectrical Circuit Lab Manualecessec67% (3)

- How To Add and Delete ONT On The OLT DeviceДокумент6 страницHow To Add and Delete ONT On The OLT DeviceElizabeth Rich100% (1)

- Digital Implementation of Sinusoidal Pulse Width Modulation GeneratorДокумент4 страницыDigital Implementation of Sinusoidal Pulse Width Modulation GeneratorecessecОценок пока нет

- SyllabusДокумент118 страницSyllabusecessecОценок пока нет

- Digital Implementation of Sinusoidal Pulse Width Modulation GeneratorДокумент4 страницыDigital Implementation of Sinusoidal Pulse Width Modulation GeneratorecessecОценок пока нет

- Hardware Implementation of A Digital Watermarking System For Video AuthenticationДокумент13 страницHardware Implementation of A Digital Watermarking System For Video Authenticationaasraj_saraОценок пока нет

- VLSI Implementation of A Low-Cost High-Quality Image Scaling ProcessorДокумент5 страницVLSI Implementation of A Low-Cost High-Quality Image Scaling ProcessorManish BansalОценок пока нет

- Hardware Implementation of A Digital Watermarking System For Video AuthenticationДокумент13 страницHardware Implementation of A Digital Watermarking System For Video Authenticationaasraj_saraОценок пока нет

- A High Performance Video Transform Engine by PDFДокумент10 страницA High Performance Video Transform Engine by PDFecessecОценок пока нет

- Adaptive Computationally Scalable Motion Estimation For The Hardware H.264AVC Encoder PDFДокумент11 страницAdaptive Computationally Scalable Motion Estimation For The Hardware H.264AVC Encoder PDFecessecОценок пока нет

- Jpeg 2000 PDFДокумент5 страницJpeg 2000 PDFecessecОценок пока нет

- Low Power Vlsi Question PaperДокумент2 страницыLow Power Vlsi Question Paperustadkrishna100% (3)

- Jpeg 2000 PDFДокумент5 страницJpeg 2000 PDFecessecОценок пока нет

- M.E. Degree Examination, April-May 201177907Документ2 страницыM.E. Degree Examination, April-May 201177907Joshua DuffyОценок пока нет

- DLC Question BankДокумент9 страницDLC Question BankecessecОценок пока нет

- Digital Logic Circuits Exam QuestionsДокумент3 страницыDigital Logic Circuits Exam QuestionsecessecОценок пока нет

- VHDL FirДокумент21 страницаVHDL FirSiva ChaitanyaОценок пока нет

- 2nd Sem - Anna UnivДокумент27 страниц2nd Sem - Anna UnivDeepak RamaswamyОценок пока нет

- Ec 2 Simulation Lab manuALДокумент56 страницEc 2 Simulation Lab manuALecessecОценок пока нет

- AnalogДокумент38 страницAnalogecessecОценок пока нет

- Solution Manual of Statistical Digital Signal Processing Modeling by MonsonHДокумент315 страницSolution Manual of Statistical Digital Signal Processing Modeling by MonsonHManuel Dominguez83% (29)

- Orcad Pspice 16Документ86 страницOrcad Pspice 16Hailin ArumigaОценок пока нет

- 2nd Sem - Anna UnivДокумент27 страниц2nd Sem - Anna UnivDeepak RamaswamyОценок пока нет

- Ec 2 Simulation Lab manuALДокумент56 страницEc 2 Simulation Lab manuALecessecОценок пока нет

- 2nd Sem - Anna UnivДокумент27 страниц2nd Sem - Anna UnivDeepak RamaswamyОценок пока нет

- Verilog Tutorial 3 - Kien 082009Документ16 страницVerilog Tutorial 3 - Kien 082009Trần Ngọc LâmОценок пока нет

- VST Mastering Tutorial - Professional mastering chain with native pluginsДокумент5 страницVST Mastering Tutorial - Professional mastering chain with native pluginsJose Rafael CentenoОценок пока нет

- Operation: USB Interface U1, U2, U3 and U4Документ5 страницOperation: USB Interface U1, U2, U3 and U4Mohammed MostefaiОценок пока нет

- SL-V28H US en-USДокумент8 страницSL-V28H US en-USJose J. VazquezОценок пока нет

- Department of Eee ProspectusДокумент5 страницDepartment of Eee ProspectusAnonymous 9lX3i3vОценок пока нет

- LMR-111D Data Sheet 4921240214 UKДокумент4 страницыLMR-111D Data Sheet 4921240214 UKCristian Camilo Arias RodriguezОценок пока нет

- Sup MotorolaДокумент18 страницSup MotorolaMario João MarioОценок пока нет

- RadWin - RW 2049 B350 PDFДокумент3 страницыRadWin - RW 2049 B350 PDFElfy PalmaОценок пока нет

- CMFB DesignДокумент4 страницыCMFB Designaminkhan83Оценок пока нет

- 12 Physics Exemplar Chapter 14Документ11 страниц12 Physics Exemplar Chapter 14Haarish KrishnamurthyОценок пока нет

- Information and Communication Technology by KhanДокумент48 страницInformation and Communication Technology by KhanKhanz TutoОценок пока нет

- 08-Electronics & Comm EnggДокумент47 страниц08-Electronics & Comm Enggraja2kumariОценок пока нет

- Snapdragon 625 Processor Product BriefДокумент2 страницыSnapdragon 625 Processor Product BriefvineetkrsinghОценок пока нет

- Avr4306 C4320 Protocol 4.6Документ26 страницAvr4306 C4320 Protocol 4.6fatrhinoОценок пока нет

- Ideacentre AIO 520-22IKU: F0D50094LDДокумент3 страницыIdeacentre AIO 520-22IKU: F0D50094LDklaus82Оценок пока нет

- Selected References: Ion ImplantationДокумент34 страницыSelected References: Ion Implantationmskumar_554Оценок пока нет

- AMOS, Antenna With Semicircular Radiation Diagram For 2.4 GHZДокумент22 страницыAMOS, Antenna With Semicircular Radiation Diagram For 2.4 GHZbudituxОценок пока нет

- Ata 23Документ35 страницAta 23Raby AbidiОценок пока нет

- MIT6Документ10 страницMIT6Ruru MartinОценок пока нет

- Passive Network SynthesisДокумент21 страницаPassive Network SynthesisSai Kyaw HtikeОценок пока нет

- GA-Gaming B8: User's ManualДокумент44 страницыGA-Gaming B8: User's ManualRommel LoayzaОценок пока нет

- Module 4 - Transformer TestingДокумент17 страницModule 4 - Transformer TestingldtonatoОценок пока нет

- Cooler Master Rs-700-Amba-d3 Ecos 2130 700w Report Rev 2Документ1 страницаCooler Master Rs-700-Amba-d3 Ecos 2130 700w Report Rev 2Aji Priambodo JatiОценок пока нет

- PC Based Robot Controlling Using Wireless Communication With ASK ModulationДокумент74 страницыPC Based Robot Controlling Using Wireless Communication With ASK ModulationSyam Kumar SОценок пока нет

- Exp - 8 PN JunctionДокумент3 страницыExp - 8 PN JunctionpooshkarrОценок пока нет

- Colpitts Oscillator Tutorial and Colpitts Design PDFДокумент1 страницаColpitts Oscillator Tutorial and Colpitts Design PDFyoudmeaОценок пока нет