Академический Документы

Профессиональный Документы

Культура Документы

Prob Resueltos T3

Загружено:

José Ángel Sanchez QuiñonesОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Prob Resueltos T3

Загружено:

José Ángel Sanchez QuiñonesАвторское право:

Доступные форматы

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

Ejercicio 1.

El circuito de la figura es un comparador binario de dos nmeros A (Ao, A1) y B (Bo, B1) de dos bits. Las salidas (M, m, I) toman el valor lgico "1" cuando A> B, A< B y A = B, respectivamente. Obten las funciones lgicas de cada salida y simplifcalas por Karnaugh.

Solucin.

La tabla de verdad ser: A 0 0 0 0 0 0 0 0 B 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 M 0 0 0 0 1 0 0 0 m 0 1 1 1 0 0 1 1 I 1 0 0 0 0 1 0 0 A 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 M 1 1 0 0 1 1 1 0 m 0 0 0 1 0 0 0 0 I 0 0 1 0 0 1 1 1

Las funciones cannicas sern:

Si completamos los mapas de Karnaugh tendremos:

AB CD

00

01

11

10

00 01 11 10

1 1

1 1

La funcin resultante para M:

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

AB CD

00

01

11

10

00 01 11 10 1 1 1 1 1 1

La funcin para m:

AB CD

00

01

11

10

00 01 11 10

1 1 1 1

Esta funcin lgica no se puede simplificar por Karnaugh, pero operando algebraicamente se obtienen las siguientes simplificaciones:

Que al implementar con cualquier tipo de puertas lgicas de dos entradas quedar:

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

Simblicamente:

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

Ejercicio 2.

Disee un circuito combinacional que realice la suma aritmtica de dos nmeros binarios, uno de un bit (A) y otro de dos bits (B1 B0), y cuyo resultado tambin est dado en binario (S1 S0).

Solucin.

La tabla de verdad sera: Entradas B1 B0 0 0 0 0 1 1 1 1 Las funciones cannicas seran: 0 0 1 1 0 0 1 1 A 0 1 0 1 0 1 0 1 Salidas S1 0 0 0 1 0 1 1 1 S0 0 1 1 0 1 0 0 1

Los mapas de Karnaugh sern:

AB C

00

01

11

10

0 1 1

1 1 1

Se pueden hacer tres bolsas de dos celdas con lo que la expresin quedar: La expresin no se puede simplificar por Karnaugh, pero utilizando mtodos algebraicos se obtiene:

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

Al implementar el circuito combinacional quedar:

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

Ejercicio 3.

La figura adjunta representa un comparador binario de dos nmeros (A y B), de dos bits cada uno. La salida toma el valor lgico 1 cuando se cumple que A B.

Se pide: a) Tabla de verdad. b) Funcin lgica simplificada. c) Circuito simplificado con puertas lgicas de dos entradas.

Solucin.

a) La tabla de verdad ser: A1 0 0 0 0 0 0 0 0 A0 0 0 0 0 1 1 1 1 B1 0 0 1 1 0 0 1 1 B0 0 1 0 1 0 1 0 1 S 0 0 0 0 1 0 0 0 A1 1 1 1 1 1 1 1 1 A0 0 0 0 0 1 1 1 1 B1 0 0 1 1 0 0 1 1 B0 0 1 0 1 0 1 0 1 S 1 1 0 0 1 1 1 0

La funcin cannica ser:

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

b) El mapa de Karnaugh ser:

A1A0 B1B0

00

01

11

10

00 01 11 10

1 1

1 1

Se puede hacer una bolsa de cuatro celdas y dos bolsas de dos celdas, por lo que la expresin quedar:

c) Que al implementarse con puertas bsicas de dos entradas quedar:

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

Ejercicio 4.

Un circuito combinacional consta de dos entradas de datos A y B, dos entradas de seleccin de operacin S1 y S0 y una salida Y de un solo bit. Funciona del siguiente modo con las seales S1 y S0, puede seleccionarse la funcin lgica Y, segn la siguiente tabla:

S1 0 0 1 1 Se pide: a) La tabla de verdad.

So 0 1 0 1

Y A+B AB A B

b) La funcin lgica simplificada mediante Karnaugh.

Solucin.

a) La tabla de verdad sera: A 0 0 0 0 0 0 0 0 B 0 0 0 0 1 1 1 1 S1 0 0 1 1 0 0 1 1 S0 0 1 0 1 0 1 0 1 Y 0 0 1 1 1 0 1 0 A1 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 S1 0 0 1 1 0 0 1 1 S0 0 1 0 1 0 1 0 1 Y 1 0 0 1 0 1 0 0

b) La funcin cannica sera:

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

El mapa de Karnaugh ser:

AB S1S0

00

01

11

10

00 01 11 10 1 1

1 1

1 1

Se pueden hacer tres bolsas de dos celdas y quedan dos celdas aisladas, por lo que la simplificacin podra dar una expresin como:

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

10

Ejercicio 5.

Un circuito digital tiene dos entradas de seal, E0 y E1, una entrada de seleccin, S, y una salida, F, siendo su funcionamiento el siguiente: si S = 0, F toma el mismo valor que E0; si S = 1, F toma el mismo valor que E1. a) Obtenga la tabla de verdad de F. b) Simplifquela por Karnaugh. c) Obtenga un circuito lgico que realice dicha funcin con el mnimo nmero de puertas lgicas.

Solucin.

a) La tabla de verdad ser:

Entradas E1 E0 0 0 0 0 1 1 1 1 La funcin cannica ser: b) El mapa de Karnaugh ser:

E1E0 S

Salida F 0 0 1 0 0 1 1 1

S 0 1 0 1 0 1 0 1

0 0 1 1 0 0 1 1

00

01

11

10

0 1

1 1 1

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

11

Se pueden hacer dos bolsas de dos celdas cada una, con lo que quedar la expresin:

c) Que implementado con cualquier tipo de puertas quedara:

d) Si queremos implementar el circuito con puertas NAND, negamos dos veces la expresin y aplicamos el teorema de DeMorgan a una de las dos negaciones, con lo que obtenemos la expresin:

Que una vez implementado quedara:

e) Si queremos implementar el circuito con puertas NOR, negamos dos veces cada uno de los dos productos y aplicamos el teorema de DeMorgan a una de las dos negaciones. Negamos dos veces toda la expresin y, con lo que obtenemos:

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

12

Que una vez implementado quedara:

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

13

Ejercicio 6.

Implementacin de funciones aritmticas. Sumador completo. Presenta tres entradas, dos correspondientes a los dos bits que se van a sumar y una tercera con el acarreo de la suma anterior. Y tiene dos salidas, el resultado de la suma y el acarreo producido.

Solucin

Su tabla de verdad ser: Entradas A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C-1 0 1 0 1 0 1 0 1 Salidas C 0 0 0 1 0 1 1 1 S 0 1 1 0 1 0 0 1

Sus funciones cannicas sern:

Que una vez simplificadas quedaran:

O bien:

Una vez implementado con puertas lgicas el sumador presentara cualquiera de los siguientes circuitos:

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

14

Observando la implementacin de la derecha, diremos: Para sumar dos bits, se emplea una puerta XOR. Para sumar tres bits, se le aplica una vez ms la puerta XOR al resultado El acarreo final ser un 1, cuando las dos entradas de la primera puerta XOR son 1, o cuando las dos entradas de la segunda puerta XOR son 1. Esto lo podemos conseguir con dos puertas AND en paralelo con ambas entradas, y sumando lgicamente con una puerta OR el resultado de ambas.

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

15

Ejercicio 7.

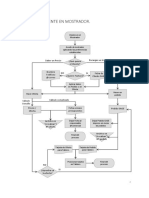

Obten la tabla de verdad y la funcin la cannica del circuito mostrado en la figura siguiente y simplifcala por el mtodo de Karnaugh

Solucin.

Para obtener la tabla de verdad debemos observar como se encuentran conectados los terminales del multiplexor y as obtendremos una tabla como sigue: A 0 0 0 0 0 0 0 0 B 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 S1 0 0 1 1 0 0 1 1 S0 0 1 0 1 0 1 0 1 0 0 0 0 Z Z 1 1 1 1 0 0 0 0 A 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 S1 0 0 1 1 0 0 1 1 S0 0 1 0 1 0 1 0 1 Z C C C C C+D C+D C+D C+D Z 0 0 1 1 0 1 1 1

b) La funcin cannica sera:

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

16

El mapa de Karnaugh ser:

AB CD

00

01

11

10

00 01 11 10

1 1 1 1 1 1 1 1 1

Se pueden hacer dos bolsas de cuatro celdas y una bolsa de dos celdas, por lo que la simplificacin podra dar una expresin como

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

17

Ejercicio 8.

Un proceso industrial responde a la siguiente tabla de verdad. Decimales Entradas C 0 1 2 3 4 5 6 7 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 A 0 1 0 1 0 1 0 1 Salida Y 0 1 0 1 1 0 0 1

Se desea implementar la funcin utilizando un decodificador.

Solucin.

La funcin cannica la obtenemos de la tabla de verdad:

Cada uno de los trminos de esta expresin corresponde con los nmeros decimales 1, 3, 4 y 7, y para configurar esa tabla de verdad solo se necesitan tres variables de entrada, como vamos a emplear un decodificador CI 7442, que tiene cuatro entradas, la de mayor peso la conectamos a masa, con lo que aseguramos un 0 lgico, y tomamos las salidas correspondientes a los decimales que hacen 1 la salida de la funcin, teniendo en cuenta que en la salida del decodificador, da niveles bajos, por lo que tenemos que construir la funcin por medio de puertas NAND, llevndolos a cada una de las entradas del CI 7420 que tiene dos puertas NAND de cuatro entradas, de las que emplearemos una. Por lo que el circuito una vez implementado quedar:

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

18

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

19

Ejercicio 9.

Empleando un multiplexor de ocho entradas de informacin y tres de seleccin, implementar el circuito lgico que responda a la funcin lgica:

Solucin.

Confeccionamos la siguiente tabla, donde se agrupan por columnas todas las posibles combinaciones de tres de las variables de entrada B, C y D, dejando en las filas las posibilidades de la variable que resta A. BCD 000 A 0 1 0 0 1 1 0 0 1 1 1 0 1 0 1 1 1 0 001 010 011 100 101 110 111

0 1

1 0

0 1

1 0 A A

1 0 A

Por tanto, la implementacin del circuito se consigue aplicando las variables B, C y D a las tres entradas de seleccin del multiplexor y conectando las entradas de los canales de la siguiente forma: Canales 0 y 3 conectado a 0. Canales 1, 3 y 6 conectado a 1. Canales 4, 5 y 7 a travs de un inversor a la variable A, ya que su valor es siempre el contrario del de dicha variable.

O bien todas las conexiones invertidas, si el multiplexor trabaja con lgica negativa, es decir: Canales 0 y 3 conectado a 1 (tensin de alimentacin +Vcc). Canales 1, 3 y 6 conectado a 0 (masa). Canales 4, 5 y 7 conectado a A.

Quedando el circuito como se muestra en la figura.

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

20

Ejercicio 10.

Realizar mediante puertas lgicas un decodificador de dos a cuatro lneas, con entradas en binario natural y salidas activas a nivel bajo. Si deseamos introducir un strobe que permita el funcionamiento del decodificador cuando este dicho strobe a nivel bajo, cmo se deber modificar el circuito?

Solucin

a) Sin Strobe

S0

E1 0 0 1 1

E0 0 1 0 1

S0 0 1 1 1

S1 1 0 1 1

S2 1 1 0 1

S3 1 1 1 0 S1 S2

S3

b) Con Strobe

E2 0 0 0 0 0 0 0 0

E1 0 0 1 1 0 0 1 1

E0 0 1 0 1 0 1 0 1

S0 0 1 1 1 1 1 1 1

S1 1 0 1 1 1 1 1 1

S2 1 1 0 1 1 1 1 1

S3 1 1 1 0 1 1 1 1

S3

S3 S0

S1

S2

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

21

Problema 11.

Implementar con puertas lgicas de cualquier tipo, de dos entradas, un codificador de 4 lneas a cdigo de exceso de 3 con prioridad a la entrada de mayor peso.

Solucin.

E2 0 0 1 S0 = 0 S1 = E1 E2 + E2

S2 = E 0 E1 E2 S3 = E 0 E1 E2 + E2

E1 0 1 X

E0 1 X X

S0 0 0 0

S1 0 1 1

S2 1 0 0

S3 1 0 1

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

22

Ejercicio 12.

Disear y montar mediante puertas lgicas un codificador de 4 lneas a cdigo exceso 3.

Solucin.

E3 0 0 0 1 E2 0 0 1 0 E1 0 1 0 0 E0 1 0 0 0 S0 0 0 0 0 S1 0 1 1 1 S2 1 0 0 1 S3 1 0 1 0

S0 = 0 S1 = E1 + E2 + E3 S2 = E0 + E3 S3 = E0 + E2

S1 S2 S3

Unidad 3. Control y Programacin de Sistemas Automticos. Problemas. Tema 3. Circuitos Combinacionales.

23

Ejercicio 13.

Realizar el circuito de una alarma en la que se muestra que sensor de los siete que componen la alarma se ha disparado. La indicacin se ha de mostrar en un display de 7 segmentos. Utilizar el codificador 74147. Como ejemplo de alarma, montar el circuito de tal manera que se dispare la alarma por el sensor numero 4.

Solucin

E0 1 0 X X X X X X X 1 1 E1 1 1 0 X X X X X X 1 1 E2 1 1 1 0 X X X X X 1 1 E3 1 1 1 1 0 X X X X 1 1 E4 1 1 1 1 1 0 X X X 1 1 E5 1 1 1 1 1 1 0 X X 1 1 E6 1 1 1 1 1 1 1 0 X 1 1 E7 1 1 1 1 1 1 1 1 0 1 1 E8 1 1 1 1 1 1 1 1 1 1 1 E9 1 1 1 1 1 1 1 1 1 1 1 D 1 1 1 1 1 1 1 1 1 1 1 C 1 1 1 1 1 0 0 0 0 1 1 B 1 1 1 0 0 1 1 0 0 1 1 A 1 1 0 1 0 1 0 1 0 1 1

Вам также может понравиться

- Ejercicios de Integrales de Línea, Superficie y VolumenОт EverandEjercicios de Integrales de Línea, Superficie y VolumenРейтинг: 4 из 5 звезд4/5 (2)

- Puertas LogicasДокумент13 страницPuertas LogicasturinatecnologiaОценок пока нет

- Guia Diseños Logicos - Intensivo 2013Документ40 страницGuia Diseños Logicos - Intensivo 2013Josea Arvelo33% (3)

- Ejercicios Puertas LógicasДокумент2 страницыEjercicios Puertas LógicasAlfonso Lopez AntonОценок пока нет

- Ejercicios U2 Circuitos DigitalesДокумент7 страницEjercicios U2 Circuitos Digitalesvaleria castañonОценок пока нет

- Problemas e DigitalДокумент8 страницProblemas e DigitalVictor PerezОценок пока нет

- Prob 2bach SELECTIVIDAD Logicabinaria ENUNCIADOSДокумент14 страницProb 2bach SELECTIVIDAD Logicabinaria ENUNCIADOSRaul100% (1)

- RELACIÓN DE PROBLEMAS Bloque Temático VДокумент3 страницыRELACIÓN DE PROBLEMAS Bloque Temático Veljesurodriguez888Оценок пока нет

- UTEL 6 ElectronicaДокумент9 страницUTEL 6 ElectronicaEduardoBenitoGarcia50% (2)

- Actividad 6 ElectronicaДокумент9 страницActividad 6 ElectronicaJonathan Chable Dionisio100% (1)

- Circuitos Digitales 1Документ12 страницCircuitos Digitales 1Circulo Es NivelОценок пока нет

- Ejercicios Electronica DigitalДокумент6 страницEjercicios Electronica DigitalJesus Ivan Herrera LopezОценок пока нет

- 4.2 - Logica CombinacionalДокумент20 страниц4.2 - Logica CombinacionalLex SchneiderОценок пока нет

- Puertas LogicasДокумент14 страницPuertas Logicasmglq100% (1)

- IDL2020 Pca2Документ7 страницIDL2020 Pca2Electro MotiveОценок пока нет

- Informe Previo N°2Документ10 страницInforme Previo N°2Jorge HuamanОценок пока нет

- 10) Sumador y ComparadorДокумент7 страниц10) Sumador y Comparadorjaja1978100% (1)

- 3.ED - Guia Actividades - 3Документ3 страницы3.ED - Guia Actividades - 3Luis GuerraОценок пока нет

- Problemas Resueltos Electronica DigitalДокумент7 страницProblemas Resueltos Electronica DigitalkazutoОценок пока нет

- Actividad Semana 6 ElectronicaДокумент9 страницActividad Semana 6 Electronicaalejandro michelОценок пока нет

- Guía 5-Sistemas DigitalesДокумент9 страницGuía 5-Sistemas DigitalesVictor MelaraОценок пока нет

- PAEUDigitalДокумент4 страницыPAEUDigitalfagonzalez1958Оценок пока нет

- Circuitos Lógicos Combiacioinales #15Документ6 страницCircuitos Lógicos Combiacioinales #15martinОценок пока нет

- Semana 5-WAДокумент33 страницыSemana 5-WAOscar ManriqueОценок пока нет

- Problem Ass DigДокумент107 страницProblem Ass DigYani Ivanov ManovОценок пока нет

- Algebra Booleana y Circuitos LógicosДокумент6 страницAlgebra Booleana y Circuitos Lógicosleandro ramirezОценок пока нет

- p3 sd1 p09Документ5 страницp3 sd1 p09Fernando GutierrezОценок пока нет

- Taller de Funcione Logicas y Algebra de BooleДокумент4 страницыTaller de Funcione Logicas y Algebra de BooleWill VillamilОценок пока нет

- Electronica Semana 6Документ9 страницElectronica Semana 6Cristian RangelОценок пока нет

- 4eso - Electrónica Digital 1Документ18 страниц4eso - Electrónica Digital 1Carlos Vargas RinconОценок пока нет

- Tarea 6 ElectronicaДокумент9 страницTarea 6 ElectronicaMartin GomezОценок пока нет

- Ejercicios de Puertas LogicasДокумент2 страницыEjercicios de Puertas LogicasCARMEN JULIANA GUERRERO SILVAОценок пока нет

- Ejercicios de Puertas LogicasДокумент2 страницыEjercicios de Puertas LogicasDiego SilveraОценок пока нет

- Ejercicios de Puertas LogicasДокумент2 страницыEjercicios de Puertas LogicasDaniel QuiaroОценок пока нет

- Ejercicios de Puertas LogicasДокумент2 страницыEjercicios de Puertas LogicasOmar CalapuchaОценок пока нет

- Ejercicios de Puertas LogicasДокумент2 страницыEjercicios de Puertas LogicasJuan Garay MonagoОценок пока нет

- Ejercicios de Puertas LogicasДокумент2 страницыEjercicios de Puertas LogicasJuan MejiaОценок пока нет

- Ejercicios de Puertas LogicasДокумент2 страницыEjercicios de Puertas LogicasRey ArturoОценок пока нет

- Ejercicios de Puertas LogicasДокумент2 страницыEjercicios de Puertas LogicasIsrael CruzОценок пока нет

- Ejercicios de Puertas LogicasДокумент2 страницыEjercicios de Puertas LogicasjoseОценок пока нет

- Ejercicios de Puertas LogicasДокумент2 страницыEjercicios de Puertas LogicasWhesner PaezОценок пока нет

- Ejercicios de Puertas LogicasДокумент2 страницыEjercicios de Puertas LogicasSamuel Torres100% (1)

- Ejercicios de Puertas LogicasДокумент2 страницыEjercicios de Puertas LogicasKELLY VALENTINA ALVARADO VEGAОценок пока нет

- Ejercicios de Puertas LogicasДокумент2 страницыEjercicios de Puertas LogicasDaniel LopezОценок пока нет

- Ejercicios de Puertas LogicasДокумент2 страницыEjercicios de Puertas LogicasLuis Santiago Castro JaimesОценок пока нет

- Ejercicios de Puertas LogicasДокумент2 страницыEjercicios de Puertas Logicaspatricio muñozОценок пока нет

- Ejercicios de Puertas LogicasДокумент2 страницыEjercicios de Puertas LogicasIsrrael SaraguroОценок пока нет

- 4 KarnaughДокумент15 страниц4 KarnaughRoberto CantoОценок пока нет

- Ejercicios Electronica DigitalДокумент13 страницEjercicios Electronica DigitaltecnoensenyamentОценок пока нет

- Ieee Algebra BooleanaДокумент6 страницIeee Algebra BooleanaNilsa Yohanna Niño HernandezОценок пока нет

- Puertas LógicasДокумент30 страницPuertas LógicasLuiz GarciaОценок пока нет

- Ejercicios de Puertas LogicasДокумент2 страницыEjercicios de Puertas LogicasmjmartintecnologiaОценок пока нет

- Taller 3 Electronica Algebra Booleana Usabana 2020 2Документ5 страницTaller 3 Electronica Algebra Booleana Usabana 2020 2Elian ArenasОценок пока нет

- Unidad III. Diseño de Sistemas CombinacionalesДокумент7 страницUnidad III. Diseño de Sistemas CombinacionalesJessica LeivaОценок пока нет

- Practica Alu 1 ByteДокумент12 страницPractica Alu 1 ByteDiego RuizОценок пока нет

- Arquitectura VerdeДокумент39 страницArquitectura VerdeArqque Garcia JessicaОценок пока нет

- KAIZENДокумент11 страницKAIZENIliana SanmartinОценок пока нет

- Temas Seleccionados de Refrigeración y Climatización 2018Документ220 страницTemas Seleccionados de Refrigeración y Climatización 2018EDINSON HERRERA VASQUEZОценок пока нет

- Relevamiento Equipos de Perforacion 2017Документ74 страницыRelevamiento Equipos de Perforacion 2017HM SPОценок пока нет

- Converter CodeДокумент19 страницConverter CodeseleneedithОценок пока нет

- Volkswagen Do BrasilДокумент22 страницыVolkswagen Do BrasilmjchipocoОценок пока нет

- Comparar 2 NumerosДокумент3 страницыComparar 2 Numerossergio hernan morenoОценок пока нет

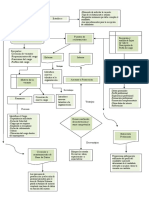

- FlujogramaДокумент1 страницаFlujogramalizethОценок пока нет

- Fut de TayacajaДокумент1 страницаFut de TayacajaEDDY JHON CHARCA CONZAОценок пока нет

- Actividad 1 ISO 31001Документ1 страницаActividad 1 ISO 31001ASESORIA SGSSTОценок пока нет

- PRUEBA DE COMPARACIÓN MÚLTIPLE IrisДокумент4 страницыPRUEBA DE COMPARACIÓN MÚLTIPLE IrisJohan TorresОценок пока нет

- Implante Auditivo de Tronco Cerebral en El Tratamiento de La Hipoacusia Sensorio NeuralДокумент7 страницImplante Auditivo de Tronco Cerebral en El Tratamiento de La Hipoacusia Sensorio NeuralDeisy Baeza OrtizОценок пока нет

- NPACKDДокумент21 страницаNPACKDcsalamancarОценок пока нет

- 2019-II MN216 Informe 4 Mecánica de Fluidos I FIM - UNIДокумент61 страница2019-II MN216 Informe 4 Mecánica de Fluidos I FIM - UNIALEXANDER EMANUEL ISIDRO OLLEROОценок пока нет

- Patricio Rey y Sus Redonditos de Ricota - Barba AzulДокумент2 страницыPatricio Rey y Sus Redonditos de Ricota - Barba AzulFacundo GiménezОценок пока нет

- Planta Concentradora y Manejo de Mena en Seco y HúmedoДокумент97 страницPlanta Concentradora y Manejo de Mena en Seco y HúmedoManuel PérezОценок пока нет

- Conocer Los Instrumentos Financieros InternacionalesДокумент6 страницConocer Los Instrumentos Financieros InternacionalesAlejandra VelasquezОценок пока нет

- Talleres Unillanos 2Документ10 страницTalleres Unillanos 2Andres HernandezОценок пока нет

- 1 - Guia de Laboratorio - Circuito Serie y ParaleloДокумент5 страниц1 - Guia de Laboratorio - Circuito Serie y ParaleloCheca DanielОценок пока нет

- Reci ClarДокумент6 страницReci ClarJessicaEsmeraldaRuizRomeroОценок пока нет

- Electroerosion ElectrodosДокумент12 страницElectroerosion ElectrodosAS PullaОценок пока нет

- Interruptor Automático Con 555 y Relé para Operar Dos Cámaras de VideoДокумент2 страницыInterruptor Automático Con 555 y Relé para Operar Dos Cámaras de VideoDIEGO LCОценок пока нет

- Atención Al Cliente en Mostrador Diagrama de Flujo y DescripciónДокумент2 страницыAtención Al Cliente en Mostrador Diagrama de Flujo y DescripciónMiguel Rodríguez Sancho0% (1)

- Trabajo de FerrocarrilesДокумент20 страницTrabajo de FerrocarrilesAztro Castillo0% (1)

- Resumen ElectrotecniaДокумент3 страницыResumen ElectrotecniaChuyoooОценок пока нет

- Problema Carta PsicrométricaДокумент3 страницыProblema Carta PsicrométricanelsonramzОценок пока нет

- Problemas SemiparabolicoДокумент5 страницProblemas SemiparabolicoLeandro Carhuchuco Josmell GenixОценок пока нет

- Actualizacion 1Документ2 страницыActualizacion 1Manuel Peña GonzalezОценок пока нет

- Decalaración de Impacto Ambiental ChoraДокумент61 страницаDecalaración de Impacto Ambiental ChoraRobert Ruiz VeraОценок пока нет

- Barra de ParalajeДокумент3 страницыBarra de Paralajeyaqueline310Оценок пока нет