Академический Документы

Профессиональный Документы

Культура Документы

Conduction Mechanisms in Thin-Film Accumulation-Mode P-Channel MOSFET's

Загружено:

Shubhra Deb Paul JoyОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Conduction Mechanisms in Thin-Film Accumulation-Mode P-Channel MOSFET's

Загружено:

Shubhra Deb Paul JoyАвторское право:

Доступные форматы

718

IEEE TRANSACTIONS ON ELECTRON DEVICES. VOL. 37. NO. 3. MARCH 1990

Conduction Mechanisms in Thin-Film AccumulationMode SO1 p-Channel MOSFETs

JEAN-PIERRE COLINGE,

MEMBER, IEEE

Abstract-A model has been developed to explain conduction mechanisms in thin-film accumulation-mode SO1 p-channel MOSFETs. It is found that, unlike that which occurs in thin-film fully depleted n-channel devices, there is little or no coupling between the front and back gates, unless the surface-state density is so high that the film remains depleted even when an accumulation channel is formed. The apparent front threshold shift is explained by back-gate modulation of a body current, flowing from the source to the drain. Indeed, the body of the device presents a p+-p--p+ structure whose conductivity is controlled by the depth of the depletion zones arising from the top and the bottom of the silicon film. The model is used to calculate drain current as a function of front- and back-gate bias as well as output characteristics.

back-gate bias must be explained by another mechanism than in n-channel devices. This apparent dependence can be explained by the back-gate dependence of the body current on back-gate bias. When a back-gate bias is applied, it modifies the value of the body current, which must be added to the accumulation current. This produces a shift of the total current in the device similar to that observed in n-channel devices, but which is caused by a totally different mechanism.

11. DEVICE MODELING A cross section of the device under investigation is given in Fig. l(a). The body of the device is doped with p-type impurities. Their concentration is typically on the order of 4 x 10l6 atoms/cm2. n+-polysilicon is used as gate material. When a zero bias is applied to the gate, the film is fully depleted due to both the presence of positive charges at the Si-Si02 interface and to that of the use of an n+-polysilicon gate. The gate material-silicon work function difference is given by

+Ms =

I. INTRODUCTION ODELING of thin-film fully depleted n-channel silicon-on-insulator transistors has been reported in the literature [l], [2]. Operation of the n-channel device is characterized by the presence of a depletion-charge sharing between the front gate and the back gate (mechanical support) which explains, among other things, the dependence of front threshold voltage on back-gate bias. In the case of a thin-film (100-nm) p-channel device, p-type doping of the body of the transistor must be used in order to obtain useful values of threshold voltage (around -0.7 V ) when a thin gate oxide (20 nm or less) and an n+-polysilicon gate is used [3]. When the device is turned OFF, the silicon film is fully depleted due to the presence of positive interface charges and to the negative value of the work function difference between the n+-polysilicon gate to the p-type body of the device [4]. When the device is turned ON,the film is no longer fully depleted and conduction occurs both in the body of the device and in a surface accumulation channel, unless the surface-state density is so high that the film remains depleted even when an accumulation channel is formed. In this case the transistor behavior follows general thin-film n-channel theory [ 11, [2] but accounting for the current flow in the p-accumulation channel, and it will not be treated here. Since there is little or no coupling between the front and back depletion zones when the device is turned ON and when the film is not fully depleted, the apparent dependence of front threshold voltage on

- E g / 2 - In ( N , / n i ) k T / q

Manuscript received February 21, 1989; revised September 5, 1989. The review of this paper was arranged by Associate Editor K . Saraswat. The author is with the Interuniversity Micro-Electronics Center, Kapeldreef 75, 3030 Leuven, Belgium. IEEE Log Number 8932794.

where ni is the intrinsic carrier concentration in silicon. When negative gate voltage is applied, the overall hole concentration in the silicon film is increased. Evolution of potential and hole concentration along the x direction can be found in [4]. Fig. l(b) presents a band curvature diagram for cases where the film is and is not fully depleted when accumulation occurs. Because the device contains no p-n junction, conduction occurs in the body of the device when the film is not fully depleted of carriers. In addition to this body current, an accumulation channel is created below the gate oxide-silicon interface when the gate voltage is smaller (more negative) than a given accumulation threshold voltage. If the doping in the film is low enough, and if the (positive) charge density is large enough, the film may still be fully depleted while an accumulation layer is formed at the silicon surface. For the sake of clarity, we will deal separately with the two current components, the accumulation current and the body current. = 0. Threshold of accumulation is reached when The gate voltage needed to accomplish this is given by

vh,acc

+MSI

Qoxl/Coxl

V@I

0018-9383/90/0300-07 18$0 1.00 0 1990 IEEE

COLINGE: CONDUCTION MECHANISMS IN p-CHANNEL MOSFETS

719

Back Gate (substrate)

non-depleted silicon below the channel. As far as this current component is concerned, similarity is found between the operation of this MOS device and that of a JFET (see, for example, [ 5 , pp. 248-2511. Conduction between the source and the drain occurs in the neutral (undepleted) part of the body. The width of this conduction path is modulated by the vertical extension of the depletion zones related to the front and the back gates. The front-gate depletion depth can be found by solving Poissons equation using the depletion approximation ~3~9 S x 2 = qN,/E,, (x)/ with 9 ( x ) being the potential in the x direction (in the depth of the semiconductor film), and Na the acceptor doping concentration. As long as there remains a portion of neutral silicon in the film (at a distance y from the source), the depth of the front-gate-related depletion region is given by

X d Y >=

E,,

--

c o xI

+ JGi/C;xl + 2Esi( ~

FRONT BACK FRONT BACK Fig. 1 . (a) Structure of the device under consideration. (b) Band curvature in the case of full (left) and partial (right) depletion when an accumulation channel is formed.

g l

vfii

- V(

y>)/qNa*

(3) Similarly, under the same conditions, the depth of the depletion zone arising from the back interface is given by

Xd2(y )

= -

2 %

cox2

JE:i/C:x2

where Vfil is the front flat-band voltage, Qoxlis the areal interface charge density at the front interface, and Coxlis the front oxide capacitance. This relationship assumes that the film body is neutral (not depleted) just under the surface. Throughout this paper, the subscripts 1 and 2 will be used to label parameters referring to the front (top) and back (bottom) interfaces, respectively. When the gate voltage Vg1 is lower (i.e., larger in absolute value) than the accumulation threshold voltage, the accumulation charge in the channel is given by

Qacc = -

+ 2%i(Vg2

- Vfi2 - V ( Y>)/qNa

[ 1/81 - V,I - V ( Y)] Cox,

where V ( y ) is the local potential along the channel ( y = = L at the drain junction). Using the gradual channel approximation (see, for example, [5, pp. 321-3271), one obtains the following expression for the current in the accumulation channel: W Iacc = ~cL,coxl[ vgl - ~ f i 1 ~ d s ~ i s / 2 ] ( 1) ( ) -

0 at the source junction and y

in the linear regime ( Vd, > VgI - V,), and

above saturation ( V,, < V,, - Vfil ). p, is the hole surface with mobility, which is equal to p s 0 / ( 1 + e( Vfil - Vgl)> pso being the zero-field surface mobility, and 0 being a field mobility reduction factor. The other current flowing from the source to the drain where teffis equal to t - Xd2,t being the silicon film thickis the body current, which appears if there is a portion of ness, and &, is the bulk hole mobility. Evidence of dif-

(4) If Xdl y ) ( Xd2(y ) is equal to or larger than t , the silicon film thickness, the film is locally fully depleted. A two-dimensional illustration of the distribution of space charges in the device can be obtained using a 2-D numerical device simulator, such as PISCES [ 6 ] . Fig. 2 presents a cross section of the device for the front gate, the back gate, and drain voltages of - 1.5, 0, and -3 V , respectively. Potential contours, from 0 to -3 V , per steps of 0.2 V , are -1so presented. In view of Fig. 2, and for the sake of simplicity, it will be assumed that the width of the back depletion region X d 2 is constant and given by (4) where V ( y ) is held constant and equal to V ( y = 0). This simplification introduces only a minor error in the evaluation of the current value, since the thickness of the buried oxide layer is typically significantly larger than those of both the front gate oxide and the silicon film. Indeed, it can be observed in Fig. 2 that the slope of the boundary between the depleted and the neutral zone is much softer for the back-side depletion zone than for the front depletion zone, where the boundary is almost vertical, considering the X and Y scales used in Fig. 2. The resistance of an elementary resistor in the body channel is given by

720

IEEE TRANSACTIONS ON ELECTRON DEVICES. VOL. 37. NO. 3. MARCH 1990

Gate (-1.5

v)

Distance (Microns)

Fig. 2. PISCES simulation of the device with front-gate, back-gate, source, and drain biases of -1.5. 0, 0. and - 3 V , respectively. The dotted line represents the boundary between the neutral and the depletion zone. The solid line represents potential contours (from 0 to - 3 V in -200-mV steps).

ferent bulk and surface mobility values has been reported in an experiment of Vu et al. in n+-n--n+ transistors [7], demonstrating the existence of both surface and bulk conduction mechanisms in this type of SO1 device. Using again the gradual channel approximation, and integrating dV = IdR from the source to the drain for the various operation modes of the device, and using (5) to find R and (3) to calculate &Ir one obtains the following expression:

r

tends all the way to the drain, etc. The following cases can be distinguished: 1) A = 0 when Vgl > Vfll Vdepl, i.e., when the film is fully depleted. Vdepl is the change in the front-gate volt= teff age with respect to flat band necessary to obtain near the source ( V ( y = 0 ) ) using (3). There is no accumulation channel (Fig. 3(a)). 2) A = teffVds when Vgl - Vfbl < 0 and Vgl - VFl 7 Vd, < 0 (Fig. 3(e)), i.e., when the front interface is in accumulation from the source to the drain. It is worth noting that the case where the film is fully depleted below the accumulation channel is not included here ( t e f f 0), = but it can be derived from n-channel theory when the device is in accumulation [l], [2]. 3)

&,

A =

(teff

+ csi/Coxl)

Vds

2

3 12

(6)

The integration of ( 6 ) from the source to the drain gives an expression in the form

W

]body = q N u p b

(Esi/Coxl)

-I- - (81

qNA

- fll

- Vd~)]

3 12

where A results from the integration of ( 6 ) and varies as a function of applied biases, depending on whether the film is fully depleted or not, whether the neutral zone ex-

when 0 < Vgl - VJbl < Vdepl and 0 < Vgl- Vfll - VdS < I/depl, i.e., when neither accumulation nor body channel pinchoff occur (Fig. 3(d)).

COLINGE: CONDUCTION MECHANISMS IN p-CHANNEL MOSFET'S

72 I

DEPLEED

NEUTRAL

when 0 < V,, - Vfll < V&pl and Vgl - Vfil - VAS< Vdepl,i.e., when the body channel is not pinched off and there is accumulation at the source end (Fig. 3(c)). 6)

A = leff(l/gl Vfll)

- (&ff

esi/coxl)

(Vdepl>

when 0 < V,, - Vfll < V&pl and V,, - Vfll - Vds > Vdepl,i.e., when the body channel is pinched off and there is accumulation at the source end (Fig. 2). Finally, the total drain current in the device is given by

Ids = Iacc

Ibody.

It is worth noting that this parallel association of the two current components is a simplification of a more complicated, but more complete, device behavior which would include the effect of carriers drifting from beyond the JFET channel pinchoff point toward the accumulation layer above it.

111. SIMULATION RESULTS

Fig. 4 presents the drain current in the device as a function of front-gate bias for different values back-gate voltage. Results of numerical simulation (PISCES) using the same parameters as in the analytical modeling are shown for comparison. The parameters used are: Qoxl / q = 5 X 10" cmP2, Q O x 2 / q 10" cm-2, toxl = 20 nm, tox2 = = 350 nm, t = 100 nm, Na = 4 x 1 0 l 6 atoms/cm2, W = 1 pm, L = 5 pm, Vds= -100 mV. The magnitude of the different components of the drain current are shown in Fig. 5. I,,,, Zbody, and Ids = I,,, + ]body are presented. The parameters are the same as in Fig. 4. It can be seen that I,,, is independent of the back-gate voltage (which is not surprising from (1) and (2)). The body current, on the other hand, is modulated by both front- and back-gate biases. It ranges between the values W of 0 when the film is fully depleted and - phqN,,tVl,, L when there is no depletion zone present. Fig. 6 shows the output characteristics of the same device, obtained by both the analytical model and numerical simulation (PISCES 11). Fig. 7 compares calculated and measured output characteristics of a SIMOX p-channel transistor for Vg2= 0 and -5 V. Details concerning device fabrication are described in [3]. The device width is 50 pm, and the gate length is 1.5 pm. The following parameters were used for both device fabrication and for simulation: toxl = 23 nm, tox2 = 350 nm, t = 100 nm, N , = 4 x loL6 cmP3. In

Fig. 3. Evolution of the depletion and accumulation layers for the different cases of integration of ( 6 ) . Please refer to the text for details.

when 0 < VgI - Vfll < Vdepland Vgl - Vfll - Vds > Vdepl, i.e., when the body channel is pinched off, but there is no accumulation at the source end nor full depletion of the film (Fig. 3(b)). 5)

A =

teff(vgl

VfiI>+

(teff

esi/Coxl)

(Vds -

V,, + VflI)

122

IEEE TRANSACTIONS ON ELECTRON DEVICES. VOL. 37. NO. 3. MARCH

700

1990

-:This model

vg2= -2

Vback = 0 V

v.

0 : PISCES

2 3 4 Vds (x -1 V)

(a)

Front gate voltage (V)

Fig. 4. Drain current as a function of gate voltage for different values of back-gate voltage. Drain voltage is - 100 mV. The solid line is analytical modeling, and the squares are the result of PISCES simulation. Parameters are given in the text.

600

1

3

400 200

n

-: accumulation current

vg2.1-2

v

0

+-+- +

2 3 4 Vds (x -1 V)

: body current :total current

v\ .

---

(b)

Fig. 7. Output characteristics of the device. Back-gate voltage is (a) 0 V and (b) -5 V. W / L = 50 pm/1.5 pm.

Front gate voltage (V)

Fig. 5 . Different drain current components as a function of gate voltage for different values of back-gate voltage. The drain voltage is - 100 mV. The solid line is analytical modeling, and the squares are the result of PISCES simulation. Parameters as in Fig. 4.

-~ 0

v g t r -3

:This model

2 5

E

101

0

-4

-3

-2

Dmln voltage (v)

Fig. 6. Output characteristics of a p-channel device. The solid line is analytical modeling, and the squares are the result of PISCES simulation. Parameters as in Fig. 4.

MOSFETs in which a neutral zone forms below the accumulation channel (which is the case if the oxide charge densities are not too large). Because the model is based on a simple gradual channel approximation, it does not account for two-dimensional short-channel effects. Since the width of the back-side depletion width is assumed to be constant as a function of y , and since back accumulation is not considered, the model is not equipped to describe large negative back-gate bias excursions. This can be done, however, by adding a third current component, the back accumulation current. Modulation of the width of the back depletion zone can also be calculated. This would impact on the number of possible values of the A parameter involved in the calculation of the body current. When the device is OFF, the film is fully depleted (as long as not too large negative back biases are used), and back-gate modulation can be obtained by adapting classical n-channel thin-film SO1 theory. In the ON case, back-gate modulation can occur, but it will influence only a portion of the body current, which is much smaller than the accumulation current when V,, is large.

V. CONCLUSION

addition, the following parameters were used in the model: Q,,,/q = 5 x 10 cmP2, Q,,,/q = 10 PI, = 240 cm2/Vs, ps0 = 200 cm2/Vs, and e = 0.12. IV. DISCUSSION This model shows the mechanism by which conduction takes place in thin-film accumulation-mode p-channel

ern-,,

This paper presents the conduction mechanisms involved in thin-film accumulation-mode SO1 p-channel transistors. It is shown that, in contrast to n-channel devices, little or no coupling arises between the front and back gates though space-charge sharing when the film is not fully depleted when the device is ON. Body current, similar to what occurs in a JFET, can be modulated, how-

COLINGE: CONDUCTION MECHANISMS IN p-CHANNEL MOSFETS

723 171 D. P. Vu, A . Chantre, D. Ronzani, and J . C . Pfister, Electrical characterization of beam-recrystallized SO1 structures using a depletionmode transistor, in MRS Symp. Proc. , Semiconductor-on-Insularor and Thin-Film Transistor Technology. vol. 53, 1986, pp. 357-361.

ever, by the applied front- and back-gate biases and causes a modulation of the total drain current. This gives rise to an apparent dependence of the front threshold voltage as a function of back-gate bias.

*

Jean-Pierre Colinge (M86) was born in Brussels, Belgium, in 1956. He received the Bachelors degree in philosophy, the Electrical Engineer degree, and the Ph.D. degree from the Universite Catholique de Louvain. Louvain-laNeuve, Belgium, in 1980, 1980, and 1984, respectively. From 1981 to 1985, he worked at the Centre National dEtudes des Telecommunications (CNET). Meylan, France, where he developed new silicon-on-insulator (Sol) and 3D integration technologies. From 1985 to 1988, he worked at the Hewlett-Packard Laboratories, Palo Alto, CA, where he was involved in SO1 CMOS and bulk bipolar technologies for high-speed digital applications. Since 1988, he has been with the Interuniversitair Microelektronica Centrum (IMEC), Leuven, Belgium, where he is involved in SO1 technology for ULSI and special device applications.

REFERENCES

H. K. Lim and J. G . Fossum, Current-voltage characteristics of thinfilm SO1 MOSFETs in strong inversion, IEEE Trans. Electron Devices, vol. ED-31, pp. 401-408, 1984. -, A charge-based large-signal model for thin-film SO1 MOSFETs, IEEE Trans. Electron Devices, vol. ED-32, pp. 446-457, 1985. J. P. Colinge and T. I. Kamins, CMOS circuits made in thin SIMOX films, Electron. Lett., vol. 23, pp. 1162-1 164, 1987. J. P. Colinge, Thin-film accumulation-mode p-channel SO1 MOSFETs, Electron. Lett., vol. 24, pp. 257-258, 1988. A. S. Grove, Physics and Technology ofSemiconductor Devices. New York: Wiley, 1967. M. R. Pinto, C . S . Rafferty, and R. W. Dutton, PISCES 11: Poisson and continuity equation solver, Stanford Univ. Tech. Rep., 1984.

Вам также может понравиться

- MOS Integrated Circuit DesignОт EverandMOS Integrated Circuit DesignE. WolfendaleОценок пока нет

- Analysis and Characterization of The Depletion-Mode IgfetДокумент10 страницAnalysis and Characterization of The Depletion-Mode Igfetbalaji_gawalwad9857Оценок пока нет

- Feynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterОт EverandFeynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterОценок пока нет

- ° Bogazici University PressДокумент8 страниц° Bogazici University PressaysevrimОценок пока нет

- Theory and Application of Field Effect TransistorsДокумент73 страницыTheory and Application of Field Effect TransistorsTiti GarconОценок пока нет

- HW 2Документ2 страницыHW 2b98154Оценок пока нет

- 540 130 PDFДокумент5 страниц540 130 PDFNava KrishnanОценок пока нет

- Nanocrystalline TFTДокумент3 страницыNanocrystalline TFTNavneet GuptaОценок пока нет

- SDTM 3 PDFДокумент6 страницSDTM 3 PDFGurwinder SinghОценок пока нет

- Scholar Search: A Simple Polysilicon Thin-Film Transistor SPICE ModelДокумент5 страницScholar Search: A Simple Polysilicon Thin-Film Transistor SPICE ModelBojan MilojevicОценок пока нет

- For In: Modeling Floating Body Effects Fully DepletedДокумент8 страницFor In: Modeling Floating Body Effects Fully DepletedAyash AshrafОценок пока нет

- Vlsi Final Notes Unit1Документ31 страницаVlsi Final Notes Unit1RohitParjapatОценок пока нет

- Ieee1998 p1554 Silc RiccoДокумент7 страницIeee1998 p1554 Silc RiccokurabyqldОценок пока нет

- 6 152J FT01 MOSCap01 PDFДокумент9 страниц6 152J FT01 MOSCap01 PDFAnonymous k50ZrVfОценок пока нет

- BSIM4 Gate Leakage Model Including Source-Drain PartitionДокумент4 страницыBSIM4 Gate Leakage Model Including Source-Drain PartitionalokjadhavОценок пока нет

- Physical Model of Lateral Pin Photodiode Gated by A Transparent Electrode Fabricated On Soi FilmДокумент6 страницPhysical Model of Lateral Pin Photodiode Gated by A Transparent Electrode Fabricated On Soi FilmBridget GwenОценок пока нет

- Switching Time in Junction Diodes and Junction TransistorsДокумент6 страницSwitching Time in Junction Diodes and Junction TransistorsHu JackОценок пока нет

- Use of 2G Coated Conductors For Efficient Shielding of DC Magnetic FieldsДокумент8 страницUse of 2G Coated Conductors For Efficient Shielding of DC Magnetic FieldsRomany AllamОценок пока нет

- VLSI Ut1Документ16 страницVLSI Ut1Naveen TimmarioОценок пока нет

- The Effect of The Inversion Channel at The Aln/Si Interface On The Vertical Breakdown Characteristics of Gan-Based DevicesДокумент7 страницThe Effect of The Inversion Channel at The Aln/Si Interface On The Vertical Breakdown Characteristics of Gan-Based DevicesA Mohan BabuОценок пока нет

- M B - P V C S G (CSG) Mosfet: Odeling of Uilt IN Otential Ariations OF Ylindrical Urrounding ATE SДокумент11 страницM B - P V C S G (CSG) Mosfet: Odeling of Uilt IN Otential Ariations OF Ylindrical Urrounding ATE SAnonymous e4UpOQEPОценок пока нет

- The Inverse-Narrow-Width Effect: Ieee Electron Device Letters, Vol. Edl-I, No. JULY 1986 419Документ3 страницыThe Inverse-Narrow-Width Effect: Ieee Electron Device Letters, Vol. Edl-I, No. JULY 1986 419Vijay Shankar PandeyОценок пока нет

- Analysis of An Aperture Coupled Micro StripДокумент8 страницAnalysis of An Aperture Coupled Micro StripYamtarОценок пока нет

- Analysis of The Gate-Source/Drain Capacitance Behavior of A Narrow-Channel FD SOI NMOS Device Considering The 3-D Fringing Capacitances Using 3-D SimulationДокумент5 страницAnalysis of The Gate-Source/Drain Capacitance Behavior of A Narrow-Channel FD SOI NMOS Device Considering The 3-D Fringing Capacitances Using 3-D SimulationSunil KumarОценок пока нет

- A Model For Avalanche Breakdown Calculation in Low-Voltage Trench Power MOSFET DevicesДокумент7 страницA Model For Avalanche Breakdown Calculation in Low-Voltage Trench Power MOSFET DevicesCazimir BostanОценок пока нет

- Module 5 V2 PDFДокумент82 страницыModule 5 V2 PDFhemanth.vishnu2002Оценок пока нет

- Two Dimensional Electron Gas, Quantum Wells & Semiconductor SuperlatticesДокумент41 страницаTwo Dimensional Electron Gas, Quantum Wells & Semiconductor SuperlatticesChang Jae LeeОценок пока нет

- M MMM M MMM MM MMMM MM MMMM M MM MM M MM MMДокумент19 страницM MMM M MMM MM MMMM MM MMMM M MM MM M MM MMpiezodocОценок пока нет

- Shielded Loop Aerials Rev 0Документ27 страницShielded Loop Aerials Rev 0jaynoweОценок пока нет

- Explicit Drain-Current Model of Graphene Field-Effect Transistors Targeting Analog and Radio-Frequency ApplicationsДокумент4 страницыExplicit Drain-Current Model of Graphene Field-Effect Transistors Targeting Analog and Radio-Frequency Applications9semОценок пока нет

- Microelectronic CircuitДокумент696 страницMicroelectronic CircuitImtiaz AhmedОценок пока нет

- COMSOL-Based Numerical Analysis of The Electric Field in PFM (Physics)Документ8 страницCOMSOL-Based Numerical Analysis of The Electric Field in PFM (Physics)carlos andres rosero zambranoОценок пока нет

- An Analytic Polysilicon Depletion Effect Model For: Mosfet'SДокумент3 страницыAn Analytic Polysilicon Depletion Effect Model For: Mosfet'SMohit GuptaОценок пока нет

- Physics of VLSI Devices (ECE-5018) Digital Assignment - II: M S G M S GДокумент6 страницPhysics of VLSI Devices (ECE-5018) Digital Assignment - II: M S G M S GShreyas RaoОценок пока нет

- Impedance Subsea CableДокумент6 страницImpedance Subsea Cableebene2Оценок пока нет

- Ultimate Load Capacity of Cable-Stayed Bridges by Ying Xii and J. S. Kuang, Z Member, ASCEДокумент9 страницUltimate Load Capacity of Cable-Stayed Bridges by Ying Xii and J. S. Kuang, Z Member, ASCEFrancisco FaggioniОценок пока нет

- A C O - C I L S S: Nalysis of Oplanar N HIP Nterconnects ON Ossy Emiconducting UbstrateДокумент5 страницA C O - C I L S S: Nalysis of Oplanar N HIP Nterconnects ON Ossy Emiconducting Ubstratesaleemnasir2k7154Оценок пока нет

- Two-Dimensional Simulation of A Device For Charge Transfer Operating at 77K: Transfer InefficiencyДокумент6 страницTwo-Dimensional Simulation of A Device For Charge Transfer Operating at 77K: Transfer InefficiencyIAEME PublicationОценок пока нет

- Characterization of Metallic-Particle Dynamics in Compressed SF - Insulated Systems Under Different Voltage StressesДокумент6 страницCharacterization of Metallic-Particle Dynamics in Compressed SF - Insulated Systems Under Different Voltage StressesItalo ChiarellaОценок пока нет

- A Memadmittance Systems Model For Thin Film Memory MaterialsДокумент4 страницыA Memadmittance Systems Model For Thin Film Memory MaterialsBlaise_Mouttet100% (1)

- COMSOL Scatterer On Substrate TutorialДокумент28 страницCOMSOL Scatterer On Substrate TutorialDyingUmbrellaОценок пока нет

- An Integrated Planar Patch Clamp System For Cell ElectrophysiologyДокумент4 страницыAn Integrated Planar Patch Clamp System For Cell ElectrophysiologySantosh PandeyОценок пока нет

- Passive Telemetry SensorДокумент7 страницPassive Telemetry SensorprincelylincolnОценок пока нет

- A Boundary Condition-Based Approach To The Modeling of Memristor Nano-StructuresДокумент14 страницA Boundary Condition-Based Approach To The Modeling of Memristor Nano-StructuresMohammed ElNeanaeiОценок пока нет

- FinFET Design and FabricationДокумент5 страницFinFET Design and FabricationbtanmayОценок пока нет

- AN211 FET Teory and PracticeДокумент12 страницAN211 FET Teory and PracticefabirznОценок пока нет

- Polythienylenevinylene Thin-Film Transistor With High Carrier MobilityДокумент4 страницыPolythienylenevinylene Thin-Film Transistor With High Carrier MobilityTianyu TangОценок пока нет

- Artikel Nomor 4Документ3 страницыArtikel Nomor 4Heny Yulia BudyantiОценок пока нет

- A New Validated Physically Based IGCT Model For Circuit Simulation of Snubberless and Series OperationДокумент7 страницA New Validated Physically Based IGCT Model For Circuit Simulation of Snubberless and Series Operationmipanduro7224Оценок пока нет

- Inductor Basic, J. LongДокумент4 страницыInductor Basic, J. LongAmitОценок пока нет

- Modelling Study of Coaxial Collinear Antenna Array PDFДокумент5 страницModelling Study of Coaxial Collinear Antenna Array PDFMar Cel100% (1)

- On OffДокумент4 страницыOn OffSilesiaОценок пока нет

- Gate Tunneling Current and Quantum Effects in Deep Scaled MosfetsДокумент5 страницGate Tunneling Current and Quantum Effects in Deep Scaled Mosfetsashishj1083Оценок пока нет

- AE72 - Microwave Theory & TechniquesДокумент16 страницAE72 - Microwave Theory & TechniquesKamal Singh Rathore100% (1)

- Electrical Study of Thin Film Al/N-Cds Schottky JunctionДокумент9 страницElectrical Study of Thin Film Al/N-Cds Schottky JunctionAnonymous cYpEVvoОценок пока нет

- 6B-2 (Invited) : Graphene Nanostructures For Device ApplicationsДокумент3 страницы6B-2 (Invited) : Graphene Nanostructures For Device Applications7semОценок пока нет

- Bias Dependent Attenuation of Coplanar Transmission Lines On SiliconДокумент4 страницыBias Dependent Attenuation of Coplanar Transmission Lines On SiliconEssam KhaterОценок пока нет

- Determinación Campo D KДокумент4 страницыDeterminación Campo D KJose Antonio MendezОценок пока нет

- A Simple Model For Quantisation Effects IN Heavily-Doped Silicon Mosfets at Inversion ConditionsДокумент4 страницыA Simple Model For Quantisation Effects IN Heavily-Doped Silicon Mosfets at Inversion ConditionsmodasshirОценок пока нет

- Progress in Electromagnetics Research C, Vol. 9, 171-182, 2009Документ12 страницProgress in Electromagnetics Research C, Vol. 9, 171-182, 2009thuantndtvt2883Оценок пока нет

- WMP EulaДокумент3 страницыWMP EulaMatache GabrielaОценок пока нет

- IJRER Final PaperДокумент3 страницыIJRER Final PaperShubhra Deb Paul JoyОценок пока нет

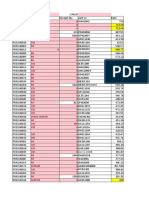

- HW MonitorДокумент50 страницHW MonitorShubhra Deb Paul JoyОценок пока нет

- WMP Firefox Plugin RelNotesДокумент2 страницыWMP Firefox Plugin RelNotesyonielteduardОценок пока нет

- Ebicycles Bicycle Sizing Chart Mountain BikesДокумент1 страницаEbicycles Bicycle Sizing Chart Mountain BikesShubhra Deb Paul JoyОценок пока нет

- IJRER Final PaperДокумент3 страницыIJRER Final PaperShubhra Deb Paul JoyОценок пока нет

- Change of Facade Pattern And: Facade Material For Energy Efficient Commercial Buildings in The Climatic Context ofДокумент3 страницыChange of Facade Pattern And: Facade Material For Energy Efficient Commercial Buildings in The Climatic Context ofShubhra Deb Paul JoyОценок пока нет

- New Text DocumentДокумент1 страницаNew Text DocumentShubhra Deb Paul JoyОценок пока нет

- International Journal of Renewable Energy Resources XДокумент5 страницInternational Journal of Renewable Energy Resources XShubhra Deb Paul JoyОценок пока нет

- HW MonitorДокумент50 страницHW MonitorShubhra Deb Paul JoyОценок пока нет

- International Journal of Renewable Energy Resources XДокумент5 страницInternational Journal of Renewable Energy Resources XShubhra Deb Paul JoyОценок пока нет

- International Journal of Renewable Energy Resources XДокумент5 страницInternational Journal of Renewable Energy Resources XShubhra Deb Paul JoyОценок пока нет

- International Journal of Renewable Energy Resources XДокумент5 страницInternational Journal of Renewable Energy Resources XShubhra Deb Paul JoyОценок пока нет

- New Text DocumentДокумент1 страницаNew Text DocumentShubhra Deb Paul JoyОценок пока нет

- AdmissionNotice 01Документ1 страницаAdmissionNotice 01Shubhra Deb Paul JoyОценок пока нет

- International Journal of Renewable Energy Resources XДокумент5 страницInternational Journal of Renewable Energy Resources XShubhra Deb Paul JoyОценок пока нет

- Read MeДокумент1 страницаRead MechickooooОценок пока нет

- InGaAs AlAsSb ReportДокумент9 страницInGaAs AlAsSb ReportShubhra Deb Paul JoyОценок пока нет

- AdmissionNotice 01Документ1 страницаAdmissionNotice 01Shubhra Deb Paul JoyОценок пока нет

- BUET Postgraduate Admission - HomeДокумент5 страницBUET Postgraduate Admission - HomeShubhra Deb Paul JoyОценок пока нет

- ABB MB3000 Versatile FT-IR Laboratory SpectrometerДокумент6 страницABB MB3000 Versatile FT-IR Laboratory SpectrometerShubhra Deb Paul JoyОценок пока нет

- BUET Postgraduate Admission - HomeДокумент5 страницBUET Postgraduate Admission - HomeShubhra Deb Paul JoyОценок пока нет

- IJRER Final PaperДокумент3 страницыIJRER Final PaperShubhra Deb Paul JoyОценок пока нет

- HW MonitorДокумент50 страницHW MonitorShubhra Deb Paul JoyОценок пока нет

- LicenseДокумент1 страницаLicenseShubhra Deb Paul JoyОценок пока нет

- Change of Facade Pattern andДокумент3 страницыChange of Facade Pattern andShubhra Deb Paul JoyОценок пока нет

- A 429769Документ13 страницA 429769Shubhra Deb Paul JoyОценок пока нет

- Detection of Greenhouse Gases Using The Photoacoustic SpectrosДокумент21 страницаDetection of Greenhouse Gases Using The Photoacoustic SpectrosShubhra Deb Paul JoyОценок пока нет

- IJRER Final PaperДокумент6 страницIJRER Final PaperShubhra Deb Paul JoyОценок пока нет

- WM KV Z Mnkvix E E 'VCK (Kvwimix/Cökvmb/A - ©) C 'I MV Vrkvi/ GŠWLK Cix Vi Zvwil I MGQ M PXДокумент2 страницыWM KV Z Mnkvix E E 'VCK (Kvwimix/Cökvmb/A - ©) C 'I MV Vrkvi/ GŠWLK Cix Vi Zvwil I MGQ M PXShubhra Deb Paul JoyОценок пока нет

- Alstom's ECO 100 PlatformДокумент23 страницыAlstom's ECO 100 Platformopzz_opzz100% (1)

- TDK Lambda ZWS30B 5 DatasheetДокумент2 страницыTDK Lambda ZWS30B 5 DatasheetSylvestre NguekengОценок пока нет

- InstallationInstructions - TNM I E 0041 - SDB670 Installation Guide - Issue 1.6Документ59 страницInstallationInstructions - TNM I E 0041 - SDB670 Installation Guide - Issue 1.6René CascoОценок пока нет

- How Do Variable Frequency Drives (VFDS) Work - or AC Drive Troubleshooting, Repair and ApplicationsДокумент11 страницHow Do Variable Frequency Drives (VFDS) Work - or AC Drive Troubleshooting, Repair and ApplicationsPandiselvan JeganathanОценок пока нет

- Upgrade Electrical Systems at Abqaiq Plants: Plan Elevation and General Arrangement Drawing For 111-091-MCC-003Документ6 страницUpgrade Electrical Systems at Abqaiq Plants: Plan Elevation and General Arrangement Drawing For 111-091-MCC-003Asad MaherОценок пока нет

- Computer Systems Servicing Learning Module K To 12Документ136 страницComputer Systems Servicing Learning Module K To 12Enzo IlabОценок пока нет

- MicPreamp Print PubДокумент2 страницыMicPreamp Print Pubapi-12922547100% (1)

- Cat. Vickers - Válvulas KBCG3Документ12 страницCat. Vickers - Válvulas KBCG3Elcio AzevedoОценок пока нет

- Paper DFR - Guide Transformadores PDFДокумент6 страницPaper DFR - Guide Transformadores PDFricsaguiОценок пока нет

- 4-Channel FM Radio System: Instruction ManualДокумент20 страниц4-Channel FM Radio System: Instruction ManualElton Marcel PadiaОценок пока нет

- Coleman 58032 Owners ManualДокумент12 страницColeman 58032 Owners Manual21st-Century-Goods.comОценок пока нет

- Ft-Oct 22 FinalДокумент79 страницFt-Oct 22 FinalOmkar Balasaheb MetkariОценок пока нет

- Watergen GEN L Spec 1Документ1 страницаWatergen GEN L Spec 1janeneveraОценок пока нет

- 74109Документ7 страниц74109Nur Hasana FОценок пока нет

- FRS Electrical Panel Spec EOIДокумент20 страницFRS Electrical Panel Spec EOITravis WoodОценок пока нет

- Ixys P-Channel Power Mosfets and Applications Abdus Sattar, Kyoung-Wook Seok, Ixan0064Документ14 страницIxys P-Channel Power Mosfets and Applications Abdus Sattar, Kyoung-Wook Seok, Ixan0064Kikuvi JohnОценок пока нет

- BASES Weidmuller PLUGSERIES OptocouplersДокумент4 страницыBASES Weidmuller PLUGSERIES OptocouplersFRANCISCO JOSE GARCIA IBAÑEZОценок пока нет

- GF-SAMXON Miniature Aluminum Electrolytic CapacitorsДокумент5 страницGF-SAMXON Miniature Aluminum Electrolytic CapacitorsIvan MarkovОценок пока нет

- Marshall Bass Amp dbs7200Документ5 страницMarshall Bass Amp dbs7200Dean LombardОценок пока нет

- Catalog - Loox (Iluminare Mobilier)Документ68 страницCatalog - Loox (Iluminare Mobilier)Paul AndreiОценок пока нет

- Science Activity Sheet: Quarter 2 - MELC 6 Week 8Документ9 страницScience Activity Sheet: Quarter 2 - MELC 6 Week 8Maribel Lebuna Cuello100% (1)

- LimiterДокумент2 страницыLimiterBoedi SetijoОценок пока нет

- Lec29 - 32 - FET Application PDFДокумент86 страницLec29 - 32 - FET Application PDFRichard ParkerОценок пока нет

- 7XG22 2RMLG Catalogue Sheet PDFДокумент12 страниц7XG22 2RMLG Catalogue Sheet PDFPontasОценок пока нет

- Paper-1 2012-17Документ39 страницPaper-1 2012-17ಶ್ರೀಕಾಂತ್ ತಿಪ್ಪೇರುದ್ರಪ್ಪОценок пока нет

- IPD3005C DatasheetДокумент3 страницыIPD3005C DatasheetAscenten TechnologiesОценок пока нет

- Underground Power Cable System PrinciplesДокумент4 страницыUnderground Power Cable System PrinciplesnooralhudОценок пока нет

- Nte2380 (N-CH) & Nte2381 (P-CH) Complementary Silicon Gate Mosfets Enhancement Mode, High Speed SwitchДокумент3 страницыNte2380 (N-CH) & Nte2381 (P-CH) Complementary Silicon Gate Mosfets Enhancement Mode, High Speed SwitchOdelis Castro PérezОценок пока нет

- Cat Transferswitchsircom enДокумент4 страницыCat Transferswitchsircom enWira Nur IndrawanОценок пока нет

- APT3200 Manual PDFДокумент46 страницAPT3200 Manual PDFMehmetОценок пока нет

- Practical Electrical Wiring: Residential, Farm, Commercial, and IndustrialОт EverandPractical Electrical Wiring: Residential, Farm, Commercial, and IndustrialРейтинг: 3.5 из 5 звезд3.5/5 (3)

- Conquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeОт EverandConquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeРейтинг: 4.5 из 5 звезд4.5/5 (9)

- Digital Filmmaking: The Ultimate Guide to Web Video Production for Beginners and Non-Professionals, Learn Useful Tips and Advice on How You Can Create, Film and Edit Your VideosОт EverandDigital Filmmaking: The Ultimate Guide to Web Video Production for Beginners and Non-Professionals, Learn Useful Tips and Advice on How You Can Create, Film and Edit Your VideosРейтинг: 5 из 5 звезд5/5 (1)

- Analog Design and Simulation Using OrCAD Capture and PSpiceОт EverandAnalog Design and Simulation Using OrCAD Capture and PSpiceОценок пока нет

- INCOSE Systems Engineering Handbook: A Guide for System Life Cycle Processes and ActivitiesОт EverandINCOSE Systems Engineering Handbook: A Guide for System Life Cycle Processes and ActivitiesРейтинг: 5 из 5 звезд5/5 (1)

- Programming the Raspberry Pi, Third Edition: Getting Started with PythonОт EverandProgramming the Raspberry Pi, Third Edition: Getting Started with PythonРейтинг: 5 из 5 звезд5/5 (2)

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionОт EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionРейтинг: 4.5 из 5 звезд4.5/5 (543)

- Hacking Electronics: An Illustrated DIY Guide for Makers and HobbyistsОт EverandHacking Electronics: An Illustrated DIY Guide for Makers and HobbyistsРейтинг: 3.5 из 5 звезд3.5/5 (2)

- Upcycled Technology: Clever Projects You Can Do With Your Discarded Tech (Tech gift)От EverandUpcycled Technology: Clever Projects You Can Do With Your Discarded Tech (Tech gift)Рейтинг: 4.5 из 5 звезд4.5/5 (2)

- The Phone Fix: The Brain-Focused Guide to Building Healthy Digital Habits and Breaking Bad OnesОт EverandThe Phone Fix: The Brain-Focused Guide to Building Healthy Digital Habits and Breaking Bad OnesРейтинг: 5 из 5 звезд5/5 (1)

- Wearable Sensors: Fundamentals, Implementation and ApplicationsОт EverandWearable Sensors: Fundamentals, Implementation and ApplicationsEdward SazonovОценок пока нет

- Practical Electronics for Inventors, Fourth EditionОт EverandPractical Electronics for Inventors, Fourth EditionРейтинг: 4 из 5 звезд4/5 (3)

- ARDUINO CODE: Mastering Arduino Programming for Embedded Systems (2024 Guide)От EverandARDUINO CODE: Mastering Arduino Programming for Embedded Systems (2024 Guide)Оценок пока нет

- Build Your Own Electric Vehicle, Third EditionОт EverandBuild Your Own Electric Vehicle, Third EditionРейтинг: 4.5 из 5 звезд4.5/5 (3)

- Understanding Automotive Electronics: An Engineering PerspectiveОт EverandUnderstanding Automotive Electronics: An Engineering PerspectiveРейтинг: 3.5 из 5 звезд3.5/5 (16)

- Teach Yourself Electricity and Electronics, 6th EditionОт EverandTeach Yourself Electricity and Electronics, 6th EditionРейтинг: 3.5 из 5 звезд3.5/5 (15)