Академический Документы

Профессиональный Документы

Культура Документы

CISC

Загружено:

sharingdocsАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

CISC

Загружено:

sharingdocsАвторское право:

Доступные форматы

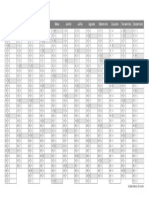

Pipeline

At o 386, os processadores da famlia x86 eram capazes de processar apenas uma instruo de cada vez. Uma instruo simples podia ser executada em apenas um ciclo de clock, enquanto instrues mais complexas demoravam vrios ciclos de clock para serem concludas. Seria mais ou menos como montar um carro de maneira artesanal, pea por pea. Para melhorar o desempenho do 486, a Intel resolveu usar o pipeline, uma tcnica inicialmente usada em processadores RISC, que consiste em dividir o processador em vrios estgios distintos. O 486, possui um pipeline de 5 nveis, ou seja, dividido em 5 estgios. Quando carregada uma nova instruo, ela primeiramente passa pelo primeiro estgio, que trabalha nela durante apenas um ciclo de clock, passando-a adiante para o segundo estgio. A instruo continua ento sendo processada sucessivamente pelo segundo, terceiro, quarto e quinto estgios do processador. A vantagem desta tcnica, que o primeiro estgio no precisa ficar esperando a instruo passar por todos os demais para carregar a prxima, e sim carregar uma nova instruo assim que se livra da primeira, ou seja, depois do primeiro pulso de clock. As instrues trafegam dentro do processador na ordem em que so processadas. Mesmo que a instruo j tenha sido processada ao passar pelo primeiro ou segundo estgio, ter que continuar seu caminho e passar por todos os demais. Se por acaso a instruo no tenha sido completada mesmo aps passar pelos 5, voltar para o primeiro e ser novamente processada, at que tenha sido concluda. Desta maneira, conseguimos que o processador seja capaz de processar simultaneamente, em um nico ciclo de clock, vrias instrues que normalmente demorariam vrios ciclos para serem processadas. Voltando ao exemplo do carro, seria como se trocssemos a produo artesanal por uma linha de produo, onde cada departamento cuida de uma parte da montagem, permitindo montar vrios carros simultaneamente. O uso dos 5 estgios de pipeline no 486 no chegava a multiplicar por cinco a performance do processador, na verdade a performance no chegava nem mesmo a dobrar, mas o ganho bem significativo. Os processadores atuais utilizam um nmero muito maior de estgios de pipeline. O Pentium II possui 10, o Athlon Thunderbird possui 12 e o Pentium 4 possui 20. No Pentium 4 por exemplo, cada estgio processa uma pequena parte da instruo, que s so concludas pelo ltimo estgio, a cada ciclo, cada um dos estgios passa a instruo para a frente e recebe uma nova. Cada instruo demora 20 ciclos para ser processada, mas em compensao so processadas 20 instrues ao mesmo tempo, em fila. Mais estgios permitem que o processador seja capaz de atingir frequncias mais altas, j que cada estgio far menos trabalho por ciclo, suportando mais ciclos por segundo, mas, por outro lado, o uso de muitos estgios pode prejudicar o desempenho do processador nas operaes de tomada de deciso, j que cada instruo demorar mais ciclos para ser concluda.

Fonte: http://www.hardware.com.br/termos/pipeline

Вам также может понравиться

- Guia Do Trabalho RemotoДокумент7 страницGuia Do Trabalho RemotosharingdocsОценок пока нет

- B078JWF7W9Документ1 страницаB078JWF7W9sharingdocsОценок пока нет

- Direito Administrativo Diferencas Praticas Entre Cargos Empregos e Funcoes PublicasДокумент44 страницыDireito Administrativo Diferencas Praticas Entre Cargos Empregos e Funcoes PublicasJeferson CardosoОценок пока нет

- Defensoria Pública Análise Institucional Capa - Miolo20191217100659Документ173 страницыDefensoria Pública Análise Institucional Capa - Miolo20191217100659sharingdocsОценок пока нет

- A Real Sobre o Sus - SuperДокумент5 страницA Real Sobre o Sus - SupersharingdocsОценок пока нет

- Calendario 2015Документ1 страницаCalendario 2015c1ceres1rodriguesОценок пока нет

- Dica para Manter Tênis BrancoДокумент2 страницыDica para Manter Tênis BrancosharingdocsОценок пока нет

- 20 Livros para Quem Estuda Comportamento Humano (Raridades)Документ13 страниц20 Livros para Quem Estuda Comportamento Humano (Raridades)sharingdocs100% (1)

- Municípios Com Eleitor Mais Conservador Têm Menos Políticas para Proteger Mulheres Da Violência, Mostra EstudoДокумент6 страницMunicípios Com Eleitor Mais Conservador Têm Menos Políticas para Proteger Mulheres Da Violência, Mostra EstudosharingdocsОценок пока нет

- EBOOK 50citações Pra Redacao PDFДокумент7 страницEBOOK 50citações Pra Redacao PDFGustavo OliveiraОценок пока нет

- 11 Truques Da Psicologia para Fazer Qualquer Um Gostar de Você - SuperДокумент13 страниц11 Truques Da Psicologia para Fazer Qualquer Um Gostar de Você - SupersharingdocsОценок пока нет

- 0 Paula Freire Analisa Rna para Entender Por Que Homens Reagem Pior À Covid-19 - SuperДокумент4 страницы0 Paula Freire Analisa Rna para Entender Por Que Homens Reagem Pior À Covid-19 - SupersharingdocsОценок пока нет

- 0 Paula Freire Analisa Rna para Entender Por Que Homens Reagem Pior À Covid-19 - SuperДокумент4 страницы0 Paula Freire Analisa Rna para Entender Por Que Homens Reagem Pior À Covid-19 - SupersharingdocsОценок пока нет

- MM Pascal WriteДокумент1 страницаMM Pascal WritesharingdocsОценок пока нет

- Operacoes FracoesДокумент62 страницыOperacoes FracoessharingdocsОценок пока нет

- Algoritmos EmailДокумент134 страницыAlgoritmos EmailsharingdocsОценок пока нет

- 21 StringsДокумент5 страниц21 StringssharingdocsОценок пока нет

- Amostra Algebra LinearДокумент47 страницAmostra Algebra LinearsharingdocsОценок пока нет

- Matematica PrecalculoДокумент84 страницыMatematica Precalculodwdaniel100% (2)

- Script para Cursor Com Texto CircularДокумент5 страницScript para Cursor Com Texto CircularsharingdocsОценок пока нет

- Função InjetoraДокумент2 страницыFunção InjetorasharingdocsОценок пока нет

- Tabela de Números RomanosДокумент9 страницTabela de Números RomanosClebson CarvalhoОценок пока нет

- Mudar o Buscador Padrão Do FirefoxДокумент1 страницаMudar o Buscador Padrão Do FirefoxsharingdocsОценок пока нет

- PT - 0034 7167 Reben 71 s4 1635Документ7 страницPT - 0034 7167 Reben 71 s4 1635licialmeidaОценок пока нет

- Projeto Ação Social InovartДокумент8 страницProjeto Ação Social InovartMary Jane DiasОценок пока нет

- TELP - Fatima Lourenco Fernando PDFДокумент14 страницTELP - Fatima Lourenco Fernando PDFBraimoОценок пока нет

- Aprendendo A Escrever Palavras Cursiva 2º AnoДокумент18 страницAprendendo A Escrever Palavras Cursiva 2º AnoGrasiela100% (1)

- Apol DidáticaДокумент18 страницApol DidáticaDiego Hernandez Gonçalves100% (1)

- Sap 1Документ1 страницаSap 1Computer Network100% (2)

- Lista de Classificação Definitiva - Assistente de Projetos Sociais - Caixa - AMPLAДокумент149 страницLista de Classificação Definitiva - Assistente de Projetos Sociais - Caixa - AMPLASTEFANI LEAL ALVESОценок пока нет

- My Teacher - Sam Crescent 71504Документ434 страницыMy Teacher - Sam Crescent 71504Maria Eduarda Silva SouzaОценок пока нет

- Ebook 5 PassosДокумент23 страницыEbook 5 PassosViviana PereiraОценок пока нет

- UFF SISU2022 2edicao Chamada2Документ113 страницUFF SISU2022 2edicao Chamada2Letícia MeloОценок пока нет

- Multiculturalismo e Multiculturalidade: Recorrências Discursivas Na Educação MusicalДокумент7 страницMulticulturalismo e Multiculturalidade: Recorrências Discursivas Na Educação MusicalCamilla BergamaschiОценок пока нет

- Universidade Federal Da Paraíba Centro de Educação Licenciatura em Pedagogia Área de Aprofundamento em Educação de Jovens E AdultosДокумент68 страницUniversidade Federal Da Paraíba Centro de Educação Licenciatura em Pedagogia Área de Aprofundamento em Educação de Jovens E Adultosluan ramos de barrosОценок пока нет

- Relatório Creches Janeiro 2023Документ44 страницыRelatório Creches Janeiro 2023Carlos GuedesОценок пока нет

- Questionário I - Educação InclusivaДокумент3 страницыQuestionário I - Educação InclusivaSolange Silva Azevedo0% (1)

- 1638 Consu Res. Regimento PPGESAДокумент22 страницы1638 Consu Res. Regimento PPGESATextos Filmicos Textos Escritos UNEBОценок пока нет

- JAVA ExerciciosДокумент21 страницаJAVA ExerciciosHelder100% (2)

- Educacao AmbientalДокумент21 страницаEducacao AmbientalpatriciacoordpedОценок пока нет

- Educação e SociedadeДокумент14 страницEducação e SociedadeFernanda LemosОценок пока нет

- MEBE 3 - Plano Estudos - 3300hДокумент2 страницыMEBE 3 - Plano Estudos - 3300hAna PatrícioОценок пока нет

- Gestao Processos Formativos Espacos Nao Escolares PDFДокумент61 страницаGestao Processos Formativos Espacos Nao Escolares PDFLeonardo FinelliОценок пока нет

- Biosseguranca de OGM - V1 PDFДокумент384 страницыBiosseguranca de OGM - V1 PDFLetícia Zambelli AmaralОценок пока нет

- Resenha - Determinismo Ambiental de RatzelДокумент2 страницыResenha - Determinismo Ambiental de RatzelRobson CarneiroОценок пока нет

- Art5 Pensamento Computacional Um Relato de Práticas Pedagógicas...Документ22 страницыArt5 Pensamento Computacional Um Relato de Práticas Pedagógicas...Renata Souza BarretoОценок пока нет

- Resoluo 010 IGE PesquisaДокумент10 страницResoluo 010 IGE PesquisaNascimento Passos de OliveiraОценок пока нет

- Trabalho de Matemática para As Férias de JulhoДокумент13 страницTrabalho de Matemática para As Férias de JulhoCristiane Restoy100% (2)

- AP1 2015 2 Gabarito PDAДокумент6 страницAP1 2015 2 Gabarito PDAPaula NovaesОценок пока нет

- Planejamento 2022 1º Bimestre 3 AnosДокумент4 страницыPlanejamento 2022 1º Bimestre 3 AnosGabriela Pereira0% (1)

- A Psicologia e o Indivíduo - Um Diálogo Entre Durkheim e EliasДокумент11 страницA Psicologia e o Indivíduo - Um Diálogo Entre Durkheim e EliasAllyf FerreiraОценок пока нет

- 1 - 5º.teste-10º.i - Versão 1Документ5 страниц1 - 5º.teste-10º.i - Versão 1Ana TimóteoОценок пока нет

- Dodf 111 13-06-2019 IntegraДокумент2 страницыDodf 111 13-06-2019 IntegraMetropolesОценок пока нет