Академический Документы

Профессиональный Документы

Культура Документы

ECE 18-760 FALL 2001 VLSI CAD: Logic To Layout

Загружено:

Kumar DeepakОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

ECE 18-760 FALL 2001 VLSI CAD: Logic To Layout

Загружено:

Kumar DeepakАвторское право:

Доступные форматы

Version 3.

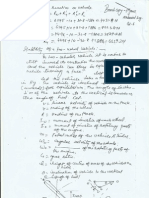

ECE 18-760 FALL 2001 VLSI CAD: Logic to Layout

Rob A. Rutenbar HH 3105 Lyz Knight Amit Singhee HH 3107 HH 3104 x8-3334 x8-5087 x8-6646 rutenbar@ece.cmu.edu lyz@ece.cmu.edu asinghee@ece.cmu.edu

FACULTY COURSE SECRETARY TEACHING ASSISTANT MEETING TIMES CLASS WEB PAGE PRE-REQUISITES

Tuesday, Thursday 12:30 - 2:20pm, HH B131

http://www.ece.cmu.edu/~ee760

Necessary Background 15-211, 15-212 18-240 Some exposure to VLSI ideas

Comments about Assumed Skills Basic CS data structures and algorithms, programming in C language, UNIX Basic digital design and verification, with combinational and sequential logic 18-321 or 18-322, or by permission

TEXTBOOKS

Synthesis and Optimization of Digital Circuits, McGraw-Hill, 1994, G. De Micheli. Also, extensive lecture notes will be provided. Graduate students and serious seniors interested in a broad exposure to the ideas behind the design of the algorithms inside VLSI CAD tools for logic and layout. Assignment 6 Homeworks Description Analysis & design of algorithms and small programs that illustrate core CAD ideas 3 Projects Programming assignments (JAVA/C++/UNIX) to build CAD tools 3 Paper reviews Analysis of topics from current CAD literature % of Grade 40% 45% 15%

INTENDED AUDIENCE

ASSIGNMENTS

WHAT 18-760 IS NOT

A circuits class. A design class where you mostly use other peoples CAD tools. Another class involving only mindless hacking (as opposed to thinking). Math-free, i.e., theres some discrete math in this class, and some continuous math. An applied algorithms class. A class where you get to look inside CAD tools and see what makes them work. A natural bridge between CE and CS applications and ideas. A class where you get to build (simplified chunks of) VLSI CAD tools. A good course for wouldbe CAD folks, or would-be VLSI designers, or folks just interested in nice algorithms that deal with 1s and 0s, graphs, time & waveforms, polygons.

WHAT 18-760 IS

TENTATIVE SYLLABUS (i.e., things may change...)

WEEK 1 8/28 8/30 WEEK 2 9/4 9/6 WEEK 3 9/11 9/13 WEEK 4 9/18 9/20 WEEK 5 9/25 9/27 WEEK 6 10/2 10/4 WEEK 7 10/9 10/11 WEEK 8 10/16 10/18 WEEK 9 10/23 10/25 WEEK 10 10/30 11/1 WEEK 11 11/6 11/8 WEEK 12 11/13 11/14 WEEK 13 11/20 11/22 WEEK 14 11/27 11/29 WEEK 15 12/4 12/6 WEEK 16 12/11 Introduction to CAD flow of ICs; Advanced Boolean Algebra Advanced Boolean Algebra, cont. Advanced Boolean Algebra, cont. JAVA Language Review Boolean Representation: BDDs Boolean Representation: BDDs, cont Boolean Representation: BDDs, cont Formal Verification: Finite State Machine Equiv Formal Verification: FSM Equivalence, continued 2-Level Logic Synthesis: ESPRESSO 2-Level Logic Synthesis: ESPRESSO, cont. Multilevel Logic Synthesis: Boolean Network Model Multilevel Logic Synthesis: Algebraic Division Project 2 Review Multilevel Logic Synthesis: Rectangle Covering Multilevel Logic Synthesis: Rectangle Covering, cont Multilevel Logic Synthesis: Role of Dont Cares Technology Mapping Component Placement for ASICs Component Placement for ASICs, cont Component Placement for ASICs, cont Component Routing for ASICs Project 3 Review Component Routing for ASICs, cont Static Timing Analysis. NO CLASS--THANKSGIVING BREAK Static Timing Analysis, cont. Electrical Delay Analysis RAR away; guest lecs RAR away; guest lec

HW

Proj Paper

hw1

hw2 Proj1

Pap1 hw3

note revised deadlines here

Proj2 hw4 Pap2

hw5 Proj3 Pap3

Geometric Data Structures for Analysis & Verification Geometric Data Structures, cont. Geometric Data Structures, cont. RAR away; guest lec

hw6

Вам также может понравиться

- 15 Highest Paying Companies For Software Engineers - The Times of IndiaДокумент13 страниц15 Highest Paying Companies For Software Engineers - The Times of IndiaKumar DeepakОценок пока нет

- Puzzle InternshalaДокумент10 страницPuzzle InternshalaKumar DeepakОценок пока нет

- Grocery and expense list April-MayДокумент5 страницGrocery and expense list April-MayKumar DeepakОценок пока нет

- Cognizant HiringДокумент2 страницыCognizant HiringKumar DeepakОценок пока нет

- Summer TRG Application Form 2013Документ2 страницыSummer TRG Application Form 2013Kumar DeepakОценок пока нет

- Thu 16-Apr Dahi 20Документ5 страницThu 16-Apr Dahi 20Kumar DeepakОценок пока нет

- BDL SyllabusElectronics EngineeringДокумент3 страницыBDL SyllabusElectronics EngineeringMurahari DanamОценок пока нет

- Flipkart refund declarationДокумент1 страницаFlipkart refund declarationKumar DeepakОценок пока нет

- NotificvhhjationДокумент10 страницNotificvhhjationsrinureddy217Оценок пока нет

- Bitcoin Manifesto - Satoshi NakamotoДокумент9 страницBitcoin Manifesto - Satoshi NakamotoJessica Vu100% (1)

- Data Conversion ArchitectureДокумент1 страницаData Conversion ArchitectureKumar DeepakОценок пока нет

- Managing StressДокумент22 страницыManaging StressKumar DeepakОценок пока нет

- A 1357706Документ12 страницA 1357706Kumar DeepakОценок пока нет

- NHPCДокумент2 страницыNHPCAbinash Kumar PuhanОценок пока нет

- Sanctioned Post Detail: Total No of Medical Teachers in 6 State Medical CollegesДокумент5 страницSanctioned Post Detail: Total No of Medical Teachers in 6 State Medical CollegesKumar DeepakОценок пока нет

- 8-Port 10/100Mbps Desktop Switch TL-SF1008DДокумент2 страницы8-Port 10/100Mbps Desktop Switch TL-SF1008DKumar DeepakОценок пока нет

- Electrostatics, Class 12th Cbse Physics FormulaeДокумент2 страницыElectrostatics, Class 12th Cbse Physics FormulaeJake TylerОценок пока нет

- Ec: Electronics and Communication Engineering: Duration: Three HoursДокумент24 страницыEc: Electronics and Communication Engineering: Duration: Three HoursKumar DeepakОценок пока нет

- 8-Port 10/100Mbps Desktop Switch TL-SF1008DДокумент2 страницы8-Port 10/100Mbps Desktop Switch TL-SF1008DKumar DeepakОценок пока нет

- Vedic MathsДокумент220 страницVedic Mathstargettutorials5740100% (7)

- Air India ECE Project ReportДокумент46 страницAir India ECE Project ReportManish KumarОценок пока нет

- Neha LemДокумент12 страницNeha LemKumar DeepakОценок пока нет

- Usb 232 Conv DatasheetДокумент2 страницыUsb 232 Conv DatasheetKumar DeepakОценок пока нет

- Maurice Nicoll The Mark PDFДокумент4 страницыMaurice Nicoll The Mark PDFErwin KroonОценок пока нет

- Syl v3 PDFДокумент2 страницыSyl v3 PDFKumar DeepakОценок пока нет

- Graphics CardДокумент3 страницыGraphics CardKumar DeepakОценок пока нет

- VHDL Basics: Distribution Restrictions and Disclaimer 1Документ5 страницVHDL Basics: Distribution Restrictions and Disclaimer 1Rishabh AggarwalОценок пока нет

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5783)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (119)