Академический Документы

Профессиональный Документы

Культура Документы

970126

Загружено:

gutic18Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

970126

Загружено:

gutic18Авторское право:

Доступные форматы

CIC IPN, Mxico

i

ndice

Pgina

Relacin de Tablas y Figuras iv

Resumen vii

Abstract viii

Introduccin

1

Captulo 1 Realizaciones Hardware de FLCs 5

1.1 Soluciones Ac tuales en la Realizac in de Sistemas de Control

Basados en Lgic a Difusa

6

1.1.1 Totalmente Software 7

1.1.2 Proc esador c on Instruc c iones Difusas Dedic adas 7

1.1.3 Proc esador Apoyado por un Coproc esador de Lgic a Difusa 8

1.1.4 Controlador de Lgic a Difusa Dedic ado 8

1.2 La Lgic a Difusa Aplic ada a los Sistemas de Control en

Realizac iones Hardware

9

1.2.1 Estruc tura del FLC Dedic ado 11

1.2.1.1 Interfaz de Fuzific ac in 12

1.2.1.2 Interfaz de Inferenc ia 13

1.2.1.3 Interfaz de Defuzific ac in 15

1.3 Princ ipales Realizac iones Hardware de FLCs 17

1.3.1 Clasific ac in de los FLCs Dedic ados 19

1.3.1.1 Controladores Dependientes de la Naturaleza de la Seal 20

2.3.1.2 Controladores Supeditados por la Estruc tura Interna 20

Captulo 2 Generalidades de las Tecnologas Programables 23

2.1 Fundamentos Teric os Sobre ASICs 24

2.2 ASIC Full Custom 25

2.3 ASIC Semi - Custom 25

2.4 ASIC Programable 26

2.4.1 Arquitec tura de los ASICs Programables: Simple y Avanzada 27

2.4.2 Disposic in de Programabilidad 28

2.4.3 Lgic a Programable 28

2.4.4 Tec nologas Programables 29

2.4.4.1 Fusibles 30

2.4.4.2 Programables por Msc ara 31

ndice

CIC IPN, Mxico

ii

Pgina

2.4.4.3 Antifusibles 31

2.4.4.4 RAM Esttic a 31

2.4.4.5 EPROM y EEPROM 32

2.5 Arquitec turas Avanzadas de los ASICs Programables 32

2.5.1 Arquitec tura FPGA 34

2.5.1.1 Granularidad de los FPGAs 36

2.5.1.2 Algunas Familias de FPGAs, Utilizadas en el Merc ado Ac tual 37

2.6 Metodologa de Diseo VLSI c on Herramientas CAD 42

2.7 Panorama General de los Lenguajes de Desc ripc in de Hardware 47

2.7.1 Elementos Bsic os de VHDL y Verilog 48

2.7.2 Niveles de Abstrac c in 50

Captulo 3 Modelado de FLCs, Utilizando HDLs 53

3.1 Esquema Bsic o del FLC Digital 54

3.1.1 Ejerc ic io de Aplic ac in: Controlador de Irrigac in 55

3.2 Aproximac in al Diseo de la Interfaz de Fuzific ac in 57

3.2.1 Estrategias Para el Clc ulo del Grado de Pertenenc ia 59

3.2.1.1 Estrategia 1: Algoritmo de los Puntos Extremos 59

3.2.1.2 Estrategia 2: Algoritmo del Punto Medio 61

3.2.2 Soluc iones Fuzific adoras de Proc esamiento Serie 62

3.2.2.1 Comparac in de las Estrategias Para el Clc ulo del Grado de

Pertenencia, Bajo el Modelo Serie

64

3.2.3 Soluc iones Fuzific adoras de Proc esamiento Paralelo 71

3.2.3.1 Diseo Individual de las Unidades Bsic as Fuzific adoras 72

3.2.4 Error en la Exac titud, Causado por el Trunc amiento 76

3.2.5 Valores Signados 78

3.3 Aproximac in al Diseo de la Interfaz de Inferenc ia 79

3.3.1 Interfaz de Inferenc ia c on Topologa Serie 80

3.3.2 Interfaz de Inferenc ia c on Topologa Paralela 81

3.4 Aproximac in al Diseo de la Interfaz de Defuzific ac in 85

3.4.1 Aproximac in Serie 85

3.4.2 Aproximac in Paralela 87

Captulo 4 Integracin de las Interfaces 93

4.1 Integrac in del FLC Digital 94

4.1.1 Integrac in del FLC c on Divisin Snc rona 96

4.1.2 Integrac in del FLC c on Divisin Asnc rona 97

4.1.3 Resultados de Sintetizac in 98

4.1.3.1 Implementac in 99

ndice

CIC IPN, Mxico

iii

Pgina

Captulo 5 Conclusiones y Trabajos a Futuro 101

5.1 Conc lusiones 102

5.2.1 Conc lusiones Espec fic as 102

5.2 Trabajos a Futuro 103

Bibliografa 104

Glosario de Trminos 109

Anexo A Documentacin de Cdigos 111

Anexo B Comprobacin Experimental 113

Anexo C Diagramas Esquemticos 116

CIC IPN, Mxico

iv

Relacin de Tablas y Figuras

Pgina

Captulo 1 Realizaciones Hardware de FLCs

Tabla 1.1 Soluciones en la realizacin de sistemas de control de lgica difusa 6

Tabla 1.2 Comparacin entre controladores 11

Tabla 1.3 Tipos de fuzificadores 13

Figura 1.1 Estructura bsica del controlador de lgica difusa dedicado 12

Figura 1.2 Controlador con modelo orientado a memoria 21

Figura 1.2 Controlador con modelo orientado a clculos 22

Captulo 2 Generalidades de las Tecnologas Programables

Tabla 2.1 Tecnologas programables, lgicas y usos 30

Tabla 2.2 Comparacin entre dispositivos de arquitectura avanzada 34

Tabla 2.3 Comparacin simple entre las diferentes familias de FPGAs de Xilinx 39

Tabla 2.4 Comparacin simple entre las diferentes familias de FPGAs de Altera 40

Tabla 2.5 Comparacin simple entre las diferentes familias de FPGAs de Actel 42

Tabla 2.6 Ambientes de desarrollo para FPGAs 43

Figura 2.1 Esquema bsico que muestra la arquitectura general, no detallada,

de un ASIC

24

Figura 2.2 Arquitectura simple y avanzada, de los ASICs programables 27

Figura 2.3 Clasificacin de los ASICs programables de acuerdo a su

disposicin de programacin

28

Figura 2.4 Derivacin MTP y OTP, de los ASICs programables 29

Figura 2.5 Arquitecturas no detalladas de un CPLD y un FPGA 33

Figura 2.6 Arquitectura demostrativa, no detallada, de un FPGA de Xilinx 35

Figura 2.7 Arquitectura de un FPGA XC4003E de Xilinx 38

Figura 2.8 Arquitectura de un FPGA FLEX8000 de Altera 40

Figura 2.9 Arquitectura de un FPGA ACT3 de Actel 41

Figura 2.10 Flujo de diseo para ASICs programables 44

Figura 2.11 Editor de diagramas esquemticos 45

Figura 2.12 Diseo bottom - up 51

Figura 2.13 Diseo top - down 52

Captulo 3 Modelado de FLCs, Utilizando HDLs

Tabla 3.1 Reglas de inferencia difusa para el controlador de irrigacin

propuesto

56

Tabla 3.2 Comparacin entre resultados de sintetizacin de los mdulos

resolutivos fuzificadores fuz_Tas1 y fuz_Tas2, bajo ambas estrategias de clculo

68

Tabla 3.3 Comparacin entre resultados de sintetizacin del mdulo resolutivo

fuzificador fuz_Tas3, bajo la estrategia de clculo 1

69

Tabla 3.3 Comparacin entre resultados de sintetizacin de los mdulos

resolutivos fuzificadores fuz_HTs1 y fuz_HTs2, bajo ambas estrategias de clculo

69

Tabla 3.5 Comparacin entre resultados de sntesis para Temperatura del Aire 75

Tabla 3.6 Comparacin entre resultados de sntesis para Humedad de la Tierra 76

Relacin de Tablas y Figuras

CIC IPN, Mxico

v

Pgina

Tabla 3.7 Reglas de inferencia difusas para el controlador de irrigacin, en

esquema matricial

79

Tabla 3.8 Resultados de sntesis de la interfaz de inferencia serie 81

Tabla 3.9 Comparacin entre resultados de sntesis del bloque bsico MIN 81

Tabla 3.10 Comparacin entre resultados de sntesis del bloque bsico MAX 83

Tabla 3.11 Sntesis comparativa de la inferencia con procesamiento paralelo 83

Tabla 3.12 Valores asumidos para la simulacin de la interfaz de inferencia 84

Tabla 3.13 Comparacin entre resultados de sntesis de la interfaz

defuzificadora serie con ambos tipos de mdulos de divisin

87

Tabla 3.14 Comparacin entre resultados de sntesis en la interfaz

defuzificadora paralela con ambos tipos de mdulos de divisin

92

Figura 3.1 Diagrama a bloques de un controlador convencional basado en

lgica difusa

54

Figura 3.2 Funciones de pertenencia para la variable Temperatura del Aire 55

Figura 3.3 Funciones de pertenencia para la variable Humedad de la Tierra 56

Figura 3.4 Funciones de pertenencia para defuzificar la variable de salida

Tiempo de Irrigacin

56

Figura 3.5 Modularizacin de la interfaz de fuzificacin 57

Figura 3.6 Funciones de pertenencia ms comunes 58

Figura 3.7 Conjunto reducido de funciones de pertenencia 58

Figura 3.8 Fuzificador triangular con pendientes diferentes 59

Figura 3.9 Mdulo resolutivo fuzificador, implementado bajo la estrategia 1 61

Figura 3. 10 Mdulo resolutivo fuzificador, implementado bajo la estrategia 2 62

Figura 3.11 Funciones de pertenencia traslapadas 63

Figura 3.12 Funcin de pertenencia trapezoidal 64

Figura 3.13 Mdulo resolutivo fuzificador, de procesamiento serie, para la

Temperatura del Aire

65

Figura 3.14 Resultados de simulacin para el fuzificador serie de la

Temperatura del Aire, estrategia 1

66

Figura 3.15 Resultados de simulacin para el fuzificador serie de la

Temperatura del Aire, estrategia 2

66

Figura 3.16 Comparacin grfica de los resultados obtenidos en la funcin de

pertenencia Fro, bajo las estrategias 1 y 2.

68

Figura 3.17 Mdulo resolutivo con memoria de datos externa 69

Figura 3.18 Mdulo resolutivo fuzificador de procesamiento serie para

Humedad de la Tierra

70

Figura 3.19 Resultados de simulacin para el fuzificador serie Humedad de la

Tierra, bajo la estrategia 1

70

Figura 3.20 Resultados de simulacin para el fuzificador serie Humedad de la

Tierra, bajo la estrategia 2

70

Figura 3.21 Topologa paralela del mdulo resolutivo Temperatura del Aire 71

Figura 3.22 Topologa paralela mxima Humedad de la Tierra 72

Figura 3.23 Funcin de pertenencia Fro de Temperatura del Aire 73

Figura 3.24 Resultados de simulacin para Fro bajo ambas estrategias 73

Figura 3.25 Funcin de pertenencia triangular con pendientes asimtricas 74

Figura 3.26 Resultados de simulacin para Fro, bajo la estrategia1, mejorando

la exactitud

78

Figura 3.27 Bloque MAX de cuatro entradas, implementado con bloques de

dos entradas

82

Relacin de Tablas y Figuras

CIC IPN, Mxico

vi

Pgina

Figura 3.28 Resultados de simulacin para la interfaz de inferencia 84

Figura 3.29 Abstraccin hardware de la interfaz defuzificadora serie 86

Figura 3.30 Interfaz defuzificadora con topologa paralela 88

Figura 3.30 Resultados de simulacin para la interfaz defuzificadora paralela

con un mdulo de divisin de restas sucesivas

90

Figura 3.31 Resultados de simulacin para la interfaz defuzificadora con un

mdulo de divisin de corrimientos constantes

92

Captulo 4 Integracin de las Interfaces

Tabla 4.1 Valores asumidos para la simulacin del FLC de irrigacin diseado 95

Tabla 4.2 Resultados de sintetizacin para el FLC diseado 98

Figura 4.1 Resultados de simulacin para el FLC diseado, con topologa

paralela y divisin mediante restas sucesivas en el defuzificador

96

Figura 4.2 Resultados de simulacin para el FLC diseado, con topologa

paralela y divisin mediante corrimientos constantes en el defuzificador

97

Figura 4.3 Resultados de simulacin para el FLC diseo, considerando seales

intermedias

98

Figura 4.4 Tarjeta de desarrollo XESSXC4010XL 99

Figura 4.5 Tarjeta con interfaces de entrada y de salida

CIC IPN, Mxico

109

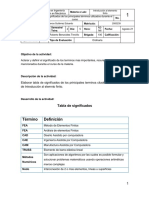

Glosario de Trminos

Controlador de Lgica Difusa.

Controlador que utiliza las tc nic as de la lgic a difusa para realizar su func in. En la literatura

espec ializada se les c onoc e c omo FLCs (Fuzzy Logic Controllers), c uya implementac in puede

ser a travs de hardware (analgic o, digital o hbrido) y/ o software.

Bsicamente, consta de tres interfac es que conservan la precedencia en la ejecucin del

prc eso: Fuzific ador, Inferenc ia y Defuzific ador.

Defuzificador.

El bloque defuzific ador genera su respuesta a partir de que la variable lingstic a difusa

resultante sale de la interfaz de inferenc ia. La interfaz de defuzific ac in, ser la enc argada de

generar el escalar que es el valor real que se entregar a la salida del controlador.

FPGA.

Field Programmable Gate Array Arreglo de Compuertas Programable en Campo. Es una

arquitec tura avanzada pertenec iente a los Circ uitos Integrados de Aplic ac in Espec fic a (ASICs)

programables. Consta de grandes c antidades de rec ursos no c omprometidos (mdulos lgic os e

interconexiones programables de tipo incremental) que pueden ser configurados por un usuario

final (programac in en c ampo). Solamente los FPGAs c on tec nologa SRAM son rec onfigurables.

Fuzificador.

La interfaz de fuzific ac in, asoc ia a c ada entrada su grado de pertenenc ia a un c onjunto difuso.

Este bloque toma los valores numric os, c onoc idos c omo valores frgiles (c risp) de las entradas

reales, que para el c aso del c ontrolador son esc alares, y les asigna un grado de pertenenc ia

respec to de una func in previamente definida heurstic amente por el experto humano,

generando en su salida valores difusos (fuzific ados). El universo de los valores se divide en

funciones de pertenencia a las cuales se identifica mediante etiquetas representativas de la

variable.

HDL.

Hardware Desc ription Language Lenguaje de Desc ripc in de Hardware. Es un lenguaje

utilizado para modelar la operac in func ional de una pieza de hardware (c irc uitos elec trnic os

y/ o sistemas c ompletos), en una forma textual.

En el c ontexto tec nolgic o mundial, los HDLs ms c omunes e importantes para alto modelado

son dos:, Verilog (Lgic a Verific able - Verify Logic ) y VHDL (VHSIC Hardware Desc ription

Language, donde el voc ablo VHSIC se refiere a Very High Speed Integrated Circ uit Circ uito

Integrado de Muy Alta Veloc idad). Ambos permiten disear de ac uerdo a ec uac iones, tablas de

verdad y diagrama de estados; su sintaxis es partic ular a c ada uno c on palabras reservadas

para indic ar al sintetizador el mtodo de diseo que se elija.

Glosario de Trminos

CIC IPN, Mxico

110

Inferencia.

La interfaz de inferenc ia c onsta de dos mdulos que interac tan entre s: la base de reglas

difusas y el mec anismo de inferenc ia. Una base de reglas difusas (Fuzzy Rules Base) c onsiste en

un c onjunto de reglas Si Entonc es (en ingls, If - Then) que modelan el func ionamiento del

sistema, por lo que el planteamiento c orrec to de la base de reglas de ac uerdo a la experienc ia

del operador humano, es factor fundamental para el comportamiento satisfac torio del

c ontrolador. Por lo mismo, a la base de reglas tambin se le c onoc e c omo Base del

Conoc imiento.

La mquina o mec anismo de inferenc ia difusa emplea la informac in almac enada en la base

de reglas difusas para determinar la func in de pertenenc ia de los antec edentes, el grado de

ac tivac in de las func iones de pertenenc ia del dominio de entrada, y de esta forma obtener la

func in de pertenenc ia de los c onsec uentes proporc ionando una nic a salida difusa.

Lgica Difusa.

Forma de razonamiento multivaluada que permite a valores intermedios ser definidos entre

valores convencionales (0 1). Este tipo de lgica est basado tradic ionalmente en reglas que

se determinan al azar dependiendo de la experienc ia de un operador humano; en vez de definir

un evento c omo 100% falso o verdadero, lo c onc ibe c omo parc ialmente falso o verdadero

otorgando a un evento grados de pertenenc ia, permitiendo as un manejo ms c onc reto y ms

lineal de situac iones.

Sntesis Lgica.

Es el equivalente a c ompilar un c digo esc rito en algn HDL, trabajando en herramientas de

diseo VLSI. El proceso genera un netlist (archivo de conexiones) que registra la descripc in de

las c eldas lgic as (primitivas) y sus c onexiones espec fic as, que c onforman un c irc uito modelado.

El formato de netlist ms utilizado es EDIF (Formato de Interc ambio de Diseo Elec trnic o -

Elec tronic Design Interc hange Format).

Tecnologas Programables.

Carac terstic as que c umple la c onstruc c in de dispositivos de lgic a programable, para permitir

la c onfigurac in o programac in. En el c aso de los FPGAs se c onsideran dos tec nologas

princ ipales: SRAM (Bit de RAM esttic a) para dispositivos rec onfigurables y Antifusibles para los no

rec onfigurables. Para algunos autores, tec nologas programables es todo el c ontexto del diseo

digital sobre FPGAs y CPLDs.

VLSI.

Very Large Sc ale Integrated Muy Alta Esc ala de Integrac in. Circ uitos integrados que

contienen entre mil y hasta cien millones de compuertas lgicas. Para algunos autores, VLSI

alcanza solamente cien mil compuertas, posteriormente c onsideran una esc ala ULSI (Ultra) para

los millones.

CIC IPN, Mxico

vii

Implementacin de un Controlador Difuso en un FPGA,

Utilizando Lenguajes de Descripcin de Hardware

Resumen

Este trabajo de tesis versa sobre el diseo e implementacin de controladores

digitales en FPGAs, cuya operacin est basada en lgica difusa. El estudio y la

realizacin electrnica del algoritmo seleccionado, permiti obtener soluciones

arquitecturales de proc esamiento serie y otras de proc esamiento paralelo, codificadas

en HDLs, que se adaptan a c ualquier aplic ac in.

Las aportac iones estn dirigidas al rea de las Tec nologas Programables, utilizando

herramientas de diseo VLSI CAD comerciales para sintetizar cdigos en Verilog y VHDL,

abarcando una de las lneas ms prometedoras de la electrnica digital

c ontempornea.

CIC IPN, Mxico

viii

Implementation of a Fuzzy Controller on FPGAs,

Using Hardware Description Languages

Abstract

This work of thesis deals with design and implementation of digital Fuzzy Logic

Controllers on FPGAs. The study and electronic implementation from selected algorithm,

allowed to obtain architectures with serie proc essing and one with parallel proc essing,

enc oded in HDLs, adaptables to any applic ation.

The contributions are directed towards Programmable Technologies with comercial

VLSI Design Tools to synthesize Verilog and VHDL c odes, embrac ing one promising line of

c ontemporary digital electronics.

CIC IPN, Mxico

1

Introduccin

Cuando un c ontrolador realiza su func in inc orporando las tc nic as de la Lgica

Difusa, se dice que es un Controlador de Lgica Difusa (FLC - Fuzzy Logic Controller). La

lgica difusa es una lgica multivaluada que ejecuta una serie de operaciones propias

y determinadas, estimadas como lingsticas, que se relacionan y proc esan de manera

similar a la forma en que lo hac e el c erebro humano, propic iando una soluc in a

problemas no lineales. Los mtodos y principios de este tipo de razonamiento en

partic ular, se enc uentran definidos en la teora matemtic a provista por los Conjuntos

Difusos (Fuzzy Sets) [1, 3, 4] .

La operatividad que evidencia el funcionamiento de un FLC, constituye una

aplicacin real y altamente demostrativa en el campo de la Inteligenc ia

Computac ional, mapeando el algoritmo involuc rado dentro de un FPGA (Field

Programmable Gate Array - Arreglo de Compuertas Programable en Campo). La

naturaleza de la arquitectura programable de estos dispositivos, as como los mtodos y

herramientas de diseo e implantacin fsica, favorecen la creacin de prototipos en

una sola pastilla de silic io

1

, a bajo costo, verstiles e inmediatos [2]. Los Lenguajes de

Desc ripcin de Hardware (HDLs Hardware Desc ription Languages), utilizados para

modelar la solucin, amplan el nivel del estudio al proponer ms elementos de

explorac in en el planteamiento original del c ontrolador, propic iando la

Automatizac in de la metodologa de diseo [18, 21, 33] .

La automatizacin del diseo sobre Tec nologas Programables es una rama del

c onoc imiento aplic ado, pertenec iente a la elec trnic a digital c ontempornea. Con la

estandarizacin en 1987 de VHDL como el primer lenguaje capaz de describir

hardware, el diseo de circuitos digitales de alta complejidad ha sido posible a un

coste razonable, permitiendo que el diseador alcance un gran nivel de abstraccin

utilizando herramientas comerciales o propias. Con la liberacin estandarizada de

Verilog en 1995, el diseo con HDLs se nutre an ms debido, entre otros aspectos, a la

fac ilidad sintc tic a en c omparac in a la propuesta por VHDL.

Los FLCs resultan ser materia de estudio constante y actual por parte de

investigadores en el mbito mundial; quienes buscan robustez, factibilidad y el

acrecentamiento en el desempeo de los controladores en trminos de la velocidad

de proc esamiento y la exactitud. La prioridad en este tipo de indagaciones recae en

1

Para algunos autores, esta tcnica es denominada SOC (System On Chip), haciendo alusin a que es posible integrar un sistema

completo en un solo circuito integrado.

Introduccin

CIC IPN, Mxico

2

enc ontrar el sentido de una realizac in elec trnic a que no est supeditada a utilizar los

dispositivos existentes c omerc ialmente sino a c rear prototipos propios, lo que admite el

anlisis de resultados y la optimizacin de los mismos [1, 2, 4, 5] . Los alcances no se

limitan, entonces, a sistemas de control, sino a toda la gama de ejerc ic ios

encaminados hacia los sistemas expertos y a la inteligencia artificial, bajo el rubro del

diseo en hardware digital.

Definicin del problema

Se han efectuado innumerables desarrollos de aplicacin especfica que

demuestran la factibilidad de la realizacin electrnica de FLCs en FPGAs,

obtenindose resultados ac eptables, los cuales se comentan debidamente en el

Captulo 1. La tendenc ia en este trabajo de tesis es formalizar un estudio detallado de

las bases prc tic as que definen la implementac in de un algoritmo de lgic a difusa,

de aplicacin completamente general. El mapeo de la solucin en el FPGA, infiere

arquitecturas que no slo competen al desempeo del controlador mismo, sino a la

optimizac in de resultados c on el propsito de reduc ir la c antidad de mdulos lgic os

en hardware utilizados del total disponible dentro del dispositivo.

La teora general del control de sistemas es muy basta, por lo que las aportaciones

originales suc intas de este doc umento no se enfoc an plenamente a la lnea del c ontrol

c omo tal, sino a la propia de la elec trnic a digital. El anlisis provisto est orientado a

las topologas de proc esamiento serie y paralelo, como arquitecturas ambiguas y

c lsicas del desarrollo digital de controladores, sin desvirtuar la importancia de la

correcta programacin en HDLs. La desc ripcin comportamental del controlador,

c odific ada en Verilog y VHDL, permite que el dominio de prc tic as y c onoc imientos,

sea ms general y accesible a cualquier nivel de estudio y bajo cualquier preferencia

sintc tic a.

Introduccin

CIC IPN, Mxico

3

Objetivo General

Disear un controlador digital basado en Lgica Difusa, c on arquitec tura adaptable

a c ualquier aplic ac in. Realizar la desc ripc in de su func ionamiento utilizando

Lenguajes de Descripcin de Hardware e implementarlo en un FPGA.

Objetivos Especficos

1. Plantear el marc o teric o del diseo de FLCs en FPGAs.

2. Demostrar que con un grupo reducido de topologas similares, es posible

resolver la mayora de los casos aplicables.

3. Detallar las soluc iones alternando desc ripc iones en VHDL y Verilog, c omo HDLs

princ ipales.

Justificaciones

No obstante que para la mayor parte de las aplicaciones resulta una soluc in

satisfactoria, un sistema implementado para trabajar va software con una

c omputadora como lazo primario de control

2

, presenta una velocidad de

proc esamiento lenta en comparacin a la de un desarrollo en hardware que cumpla

con el mismo propsito. Para sistemas muy complejos que requieren control en tiempo

real y precisan un nmero elevado de reglas de inferencia (refirindose al control de

lgica difusa) o cuando los sistemas a controlar tienen tiempos de respuesta muy

cortos, es obligatoria una realizacin en hardware [2, 6] .

El diseo de un controlador con arquitectura adaptable permite cubrir de manera

general cualquier aplicacin que infiera tcnicas de control difuso. En la mayora de los

casos, se aumenta considerablemente la cantidad de hardware para reducir el tiempo

de proc esamiento

3

, cuestin que no preocupa considerablemente, sin estimar la

2

A este tipo de sistema de control se le denomina Control Digital Directo (DDC Direct Digital Control). Tuvo sus inicios a la

par de la proliferacin de la PC.

3

Existen algoritmos matemticos que sirven para realizar la misma funcin. Por ejemplo, en los sumadores la funcin primordial

es la misma; sin embargo, en la configuracin de un sumador de 8 bits conectado en cascada, se tiene un nmero de compuertas

mucho menor que otro igual, pero en configuracin Carry Look - Ahead, el cual paraleliza las operaciones, aportando mayor

velocidad de procesamiento pero sacrificando espacio fsico.

Introduccin

CIC IPN, Mxico

4

optimizacin, dadas las caractersticas de un FPGA [18, 20] . Con la automatizacin del

diseo VLSI, la generacin de niveles lgicos envuelve alta inmunidad al ruido evitando

variaciones importantes en las caractersticas de los transistores involuc rados,

proveyendo un proc esamiento de datos exacto y confiable [23] .

La Ingeniera de Control establece el diseo de sistemas mediante cualquiera de las

tc nic as ya c onoc idas. El llamado Control Clsic o, su evoluc in hac ia el Control

Moderno y la c lara predisposic in al llamado Control Inteligente, enmarc an la

partic ipac in de la c ienc ia teric a en la mayora de las prc tic as en manejo de

proc esos sin importar el campo de diligencia. Las especificaciones de desempeo

4

determinadas para el sistema en particular sugieren el mtodo a utilizar para crear el

diseo [15] .

El c ontrol c lsic o y sus proc esamientos numric os basados en la teora matemtic a

diferenc ial, han sido una buena soluc in para la mayora de los sistemas que proponen

un comportamiento lineal, aunque los mtodos de diseo resultan muy complejos. Los

sistemas de control basados en lgica difusa han exhibido una mayor eficacia en

c uanto a su func ionamiento c omparndolos c on los c ontroladores c lsic os

5

,

especialmente cuando se destinan a proc esos no lineales difciles de modelar, y

c uando existe un manifiesto c onoc imiento heurstic o por parte del operador humano.

La tc nic a c lsic a no realiza ac tividades c ognosc itivas o proc esamiento de

informac in abstrac ta debido a la aplic ac in pura del c onoc imiento matemtic o y

plenamente comprobado, siendo la diferencia bsica entre el controlador con

tcnicas de lgica difusa y el controlador clsico [16] .

El Captulo 1 presenta el marco terico del diseo de controladores digitales de

lgica difusa, desc ribiendo las particularidades del trabajo sobre FPGAs. El Captulo 2,

abarc a la teora bsic a de las Tec nologas Programables en general, proporc ionando

una idea abstracta de la metodologa de diseo sugerida.

El terc er c aptulo, Captulo 3, desc ribe la metodologa y el desarrollo seguido para el

diseo individual de las interfac es difusas. En el Captulo 4 se muestra la integracin de

las interfac es para la implementac in c ompleta del c ontrolador, as c omo las pruebas

de func ionamiento. Finalmente, en el Captulo 5 se dan a conocer las conclusiones ms

representativas de este trabajo de tesis, generadas de los logros alc anzados. En este

mismo c aptulo se exponen los trabajos a futuro.

4

Bsicamente, en el Control Clsico las especificaciones de desempeo se pueden presentar en trminos de las caractersticas de

respuesta transitoria y/o las medidas de desempeo en el dominio de la frecuencia. En el Control Moderno, se presentan en

trminos de las variables de estado, a diferencia del Control Inteligente, donde se muestran como variables cognoscitivas.

5

Cuando se menciona a los controladores clsicos, se hace referencia a los controladores diseados mediante las tcnicas del

control clsico o del control moderno, que independientemente de la diferencia entre las tcnicas, ambas siguen siendo lgicas

bivaluadas.

CIC IPN, Mxico

5

Captulo 1

Realizaciones Hardware de FLCs

Contenido del Captulo

Los FLCs han sido ampliamente utilizados en una gran diversidad de aplicaciones,

existiendo una sustentable base terica que advierte las principales tendencias en su

realizacin electrnica digital.

En la investigacin previa concerniente a este documento, se obtuvieron una serie

de trabajos similares con respecto a la naturaleza de la lnea propuesta. La mayora de

estas aportaciones comprueban la factibilidad del diseo de FLCs sobre FPGAs,

limitndose solamente a la parte de la realizacin electrnica dirigida hacia una

aplic ac in en partic ular, ms no alternan c on la optimizac in de la soluc in y muc ho

menos proponen una arquitectura genrica.

En este captulo se presenta una revisin breve de la lgica difusa aplicada a los

sistemas de control, haciendo hincapi en los elementos ms importantes relacionados

con las realizaciones hardware (FLCs dedicados), y denotando el contexto sobre el

c ual se enc aminaron los esfuerzos de este trabajo de tesis (FLCs digitales). No se

pretende cubrir de manera detallada la teora difusa, por lo que se recomienda

auxiliarse de bibliografa especializada para una mayor acotacin de trminos.

Captulo !: Realizaciones Hardware de FLCs

CIC IPN, Mxico

6

1.1 Soluciones Actuales en la Realizacin de Sistemas

de Control Basados en Lgica Difusa

Ac tualmente existen excelentes referencias bibliogrficas en torno a la Lgica Difusa

encaminada a resolver problemas de Sistemas Expertos e Inteligenc ia Artific ial. Desde

1965, con la primera publicacin formal del trabajo realizado por Lofti A. Zadeh, la

lgica difusa comenz a tomar un auge muy particular no slo como una nueva

tc nic a de manipulac in matemtic a de eventos no lineales, sino c omo una

alternativa simple para reproduc ir un razonamiento humano.

No existe una estandarizacin de conceptos para determinar a ciencia cierta los

medios para concretar fsicamente un sistema de control de lgica difusa. La mayor

parte de los autores, coinciden en exponer una clasificacin basada en la estimacin

estruc tural del sistema de acuerdo a la participacin porcentual dedicada del

software y del hardware en la solucin provista [9, 10] .

Considerando el c riterio anterior, los sistemas de c ontrol en general que aplic an las

tc nic as de la lgic a difusa, se c lasific an en c uatro grupos dependientes de los

elementos con los que se construye el sistema: totalmente software, proc esador c on

instrucciones dedicadas al tratamiento de lgica difusa, proc esador apoyado por un

coproc esador especializado en lgica difusa y finalmente, c ontroladores difusos

dedicados; estos ltimos (en su naturaleza digital) son el elemento sustancial expuesto

en esta tesis y denotan realizac iones totalmente hardware. La tabla 1.1 muestra una

idea comparativa entre soluciones [2] .

Tabla 1.1: Soluciones en la realizacin de sistemas de control de lgica difusa.

Realizacin Caractersticas Principales

Totalmente Software Fc il y de bajo c osto. Veloc idad baja

Proc esador c on c onjunto de instruc c iones

dedic adas al tratamiento de operac iones

difusas

Mediana veloc idad de operac iones difusas y

c osto medio c onsiderable

Proc esador apoyado por un c oproc esador

c on instruc c iones difusos dedic adas

Alta veloc idad de operac iones difusas, c osto

moderado. El protoc olo de interc ambio de

informac in dific ulta el manejo de datos y la

generalidad

Controlador dedic ado al tratamiento de

operac iones difusas

Bajo, medio o alto c osto, dependiendo de la

experienc ia del diseador y de la

c omplejidad del c ontrolador. Poc a

generalidad, alta veloc idad. Soporte a

mltiples arquitec turas

Captulo !: Realizaciones Hardware de FLCs

CIC IPN, Mxico

7

1.1.1 Totalmente Software (Full Software)

Esta tendenc ia de realizac in indic a que a partir de una c omputadora personal y

ms a fondo, de cualquier proc esador de propsito general, se utiliza un lenguaje de

programacin formal para crear el sistema totalmente va software. Existe en el

mercado un respaldo muy respetable de herramientas que permiten crear sistemas

completos de manera simple e inmediata, que van desde las aplicaciones clsicas de

control hasta los sistemas expertos dedicados al manejo de bases de datos.

Existe en el mercado, software propietario que cumple con el apoyo a todas las

fases del desarrollo: diseo, simulacin, optimizacin, verificacin e implementac in.

Evidentemente los recursos de cmputo necesarios para implementar sistemas

mediante este mtodo son ms baratos e inmediatos que los de cualquiera de los

otros. La gran desventaja que tienen los sistemas creados bajo este concepto es que la

velocidad de proc esamiento es muy lenta, a causa de que se est utilizando un

proc esador de propsito general c uyo c onjunto de instruc c iones no inc luye algunas

dedicadas para las operaciones difusas, adems de que la programacin de eventos

es necesariamente serial

1

. El nmero de reglas de inferencia que pueden evaluarse en

determinada unidad de tiempo es caracterstica primordial para considerar el

desempeo de un sistema difuso. Aspecto por el cual, si se considera la posibilidad de

tener una cantidad muy grande de reglas difusas en un sistema full software, es

inminente que el tiempo de proc esamiento tambin ser muy grande debido a la

ejecuc in secuencial en la evaluacin de las reglas.

1.1.2 Procesador con Instrucciones Difusas Dedicadas

Este segundo concepto en las realizaciones, surge como una alternativa para

mejorar el desempeo de los sistemas full software. En ste, el conjunto de instrucciones

del proc esador de propsito general incluye algunas dedicadas para las operaciones

difusas. Las instrucciones incluidas en este caso fueron las clsicas MAX y MIN, c on la

intencin de desahogar un poco el grueso del proc esamiento cuando se evalan las

reglas difusas. An as, la ejecuc in sigue siendo prcticamente secuencial.

Es posible optar por la denominada programac in paralela, que aborda todo un

campo de estudio dentro de las aplicaciones software encaminadas a paralelizar

1

Con respecto al caso que se presenta de manera ms comn, recordando que puede haber programacin paralela basada en

recursos con arquitectura dispuesta para soportar este tipo de procesamiento.

Captulo !: Realizaciones Hardware de FLCs

CIC IPN, Mxico

8

proc esos; sin embargo, las tendencias evolutivas en la programacin de la inferencia

de las reglas difusas, no permiten un paralelismo va software

2

que permita evaluar de

manera independiente cada una de las reglas [14, 17] .

1.1.3 Procesador Apoyado por un Coprocesador de Lgica

Difusa

El coproc esador difuso es un dispositivo hardware que realiza operaciones difusas

especializadas y que trabaja bajo el mando de un proc esador de propsito general.

Esta aproximacin aumenta la velocidad del sistema, ya que algunas operaciones

como la evaluacin de las reglas y la comparacin entre tablas, son ejecutadas por el

coproc esador, quien a su vez entrega los resultados de su ejercicio al proc esador. El

inconveniente directo en este tipo de realizaciones, es que el sistema se encuentra

restringido por el nmero de entradas y salidas entre ambos dispositivos, requirindose

protoc olos de interc ambio de informac in y un sofistic ado c ontrol de sinc ronizac in;

razones suficientes para considerar que no se trata de una solucin ptima.

1.1.4 Controlador de Lgica Difusa Dedicado

Se trata de realizaciones hardware (c omerciales o no) de muy alta velocidad de

proc esamiento, pero con el inconveniente de ser casi totalmente de propsito

especfico para cada aplicacin. Los costos de investigacin y produccin suelen ser

relativamente altos, especialmente cuando se decide por una implementacin

analgic a, debido a que c onlleva al uso de metodologas distintas y ms c omplic adas

de desarrollo.

Como se ha venido mencionando a lo largo de este documento, el total de

entradas, salidas y el nmero de reglas que puede evaluar un dispositivo, son factores

que determinan el desempeo de un proc esador difuso. Tecnolgicamente hablando,

se dice que entre ms entradas y ms salidas se tengan, el procesador se vuelve ms

general aunque internamente las operaciones aumentan considerablemente, por lo

que la arquitectura y sus mecanismos de operacin matemtica, deben ser

2

Como se comentar posteriormente, en hardware es totalmente realizable.

Captulo !: Realizaciones Hardware de FLCs

CIC IPN, Mxico

9

cuidadosamente diseados para evitar que el desempeo se vea afectado

sacrificando velocidad por versatilidad.

Si se trata de utilizar microc ontroladores provenientes de fabricantes, se dispone de

software de soporte que crea el ensamblador para programarlos directamente

orientados al trabajo c on lgic a difusa (control ordinario o redes neuronales), tal y

como sucede con FuzzyTECH , NeuroFuzz y otros programas comerciales [1, 12] . El

funcionamiento de los microc ontroladores de propietario ms actuales (National

Semic onduc tor, SGS Thompson Mic roelec tronic s, Mitsubishi Elec tric Corporation, Texas

Instruments, Togai, Siemens, OmRom, entre otros), es aceptable en trminos de trabajo

definido ms no en generalidad, puesto que tienen un nmero restringido de entradas

y salidas, as como de reglas de inferencia, adems de que el proc esamiento en la

mayora de estos dispositivos es secuencial debido a su arquitectura diseada para

competir comercialmente buscando un punto intermedio entre costo y desempeo.

A nivel ms especializado es posible encontrar comercialmente software sofisticado

que permite modelar arquitecturas de lgica difusa automticamente sobre FPGAs

(FuzzyPL, FuzzyShell, entre otras). Estas herramientas generan cdigo en algn HDL

(Verilog o VHDL, principalmente) que modela la funcin de un controlador o de una

red neuronal, con los inconvenientes de que no optimizan el diseo, el nmero de

variables y reglas de inferencia est limitado, tienen pocas opciones en la forma de las

funciones de pertenencia y su precio es muy alto. Con la evoluc in de las soluciones en

software, estas herramientas sern motivo de anlisis consistente en el futuro.

1.2 La Lgica Difusa Aplicada a los Sistemas de

Control en Realizaciones Hardware

La lgic a en la c ual se apoya el c ontrol c lsic o define dos valores ac eptados y

restringidos que no c onc iben ninguna c onsiderac in intermedia: falso o verdadero [34] .

Estos a su vez, aplicados a diferentes contextos solamente cambian de nombre, pero

en esencia tienen el mismo sentido y aplican la misma norma: fro o c aliente, alto o

bajo, prendido o apagado, rpido o lento, 0 1. La Lgic a Booleana

3

no es suficiente

para analizar eventos de la vida real en la que se deben considerar valores

intermedios.

3

La lgica booleana es una forma de razonamiento propia de los sistemas bivaluados, ya que utiliza slo dos valores discretos

para representar sus operaciones.

Captulo !: Realizaciones Hardware de FLCs

CIC IPN, Mxico

10

En 1965, en la Universidad de California, Lofti A. Zadeh public el resultado de un

trabajo matemtic o al que titul Conjuntos Difusos (Fuzzy Sets), donde expone una

forma de razonamiento novedosa a la que nombr Lgica Difusa, que es bsicamente

una lgica multivaluada que permite a valores intermedios ser definidos entre valores

c onvenc ionales. Este tipo de lgic a est basado tradic ionalmente en reglas que se

determinan al azar dependiendo de la experiencia del operador humano. En otros

casos, se usan sistemas de determinacin y optimizacin de relaciones por medio de

algoritmos genticos o bien, redes neuronales [7, 8] .

La lgica difusa en vez de definir un evento como 100% falso o verdadero, lo

concibe como parcialmente falso o verdadero, es decir, otorga a un evento grados de

pertenencia (membresa), permitiendo as un manejo ms concreto de situaciones. El

grado de pertenencia de un elemento a un conjunto puede tener infinitos valores

dentro del rango [0, 1]. Por tanto, si x es el dominio (discreto o continuo) de todos los

elementos, un conjunto difuso cualquiera A est completamente definido por la

funcin de pertenencia

] 1 , 0 [ : x

A

(1.1)

donde ) (x

A

es el grado de pertenencia del elemento x al conjunto A.

Similarmente a la manera c omo se hac e extensible la teora c lsic a de c onjuntos

hac ia el c ampo de la lgic a bivaluada, es posible definir el c ampo de ac c in de la

lgica difusa y, en vez de hablar de grados de pertenencia de un conjunto, se habla

de grados de verdad de una proposicin lgica.

El funcionamiento del control se emula por medio de reglas en lenguaje aproximado

humano, que no son ms que expresiones formuladas c otidianamente que c ulminan

en una accin. As, el controlador de lgica difusa en capaz de evaluar el grado de

verdad de una proposicin lgica (premisa o antecedente) formulada a partir de las

variables de estado de un sistema y posteriormente inferir el grado de verdad de otra

proposic in utilizada c omo salida (c onc lusin o c onsec uente), cuyo valor ser reducido

a escalar, provocando una accin sobre el sistema bajo control.

La sistemtica de trasladar el conjunto experto de las reglas a una estrategia de

c ontrol, c on c onjuntos y lgic a difusa, se c onoc e c on el nombre de Control de Lgica

Difusa o simplemente Control Difuso (FLC Fuzzy Logic Controller). Esta innovativa

tecnologa mejora el diseo de sistemas convencionales por medio de Ingeniera

Experta

4

.

4

La Ingeniera Experta se basa en la experiencia humana. La forma en la que es operado un sistema cualquiera por un humano, se toma como gua

para sistemas independientes.

Captulo !: Realizaciones Hardware de FLCs

CIC IPN, Mxico

11

En la tabla 1.2, se puede observar una comparacin simple entre las principales

caractersticas del Controlador Clsic o y un FLC.

Tabla 1.2: Comparacin entre controladores.

Caracterstica Comparativa Controlador Clsico FLC

Diseo

A travs de modelo

matemtico y bajo tcnicas

conocidas. Baja flexibilidad

de diseo ante variables

mltiples

A travs de un modelo

heurstico. Alta flexibilidad

de diseo ante variables

mltiples

Respuesta

Depende de la

sintonizacin: clculo de las

constantes de Ganancia,

Reset y Rate

Depende de la base de

conocimiento (base de

reglas difusas)

Confiabilidad de respuesta a

cambios drsticos en las

condiciones de operacin

Baja

Alta (siempre y cuando la

base de conocimiento est

bien planteada)

Velocidad de procesamiento Aceptable

En funcin de la

arquitectura del controlador

Control no lineal

Es posible, aunque con

problemas tcitos y requiere

la ayuda de componentes

adicionales

Total

Robustez En casos limitados

Demasiada, debido a la

naturaleza del proceso

difuso

1.2.1 Estructura del FLC Dedicado

El diagrama a bloques de un controlador difuso dedicado se muestra en la figura

1.1. El sistema consta de cuatro mdulos bsicos: La interfaz de fuzificacin, un

mecanismo de inferencia que interacta con una base de reglas difusas (juntas,

forman la interfaz de inferencia) y la generacin de valores reales o interfaz de

defuzificacin. En el Captulo 3 de este trabajo de tesis, se comenta detalladamente el

diseo de cada interfaz, por lo que la revisin dada en esta seccin no revela

pormenores ms tcnicos.

Captulo !: Realizaciones Hardware de FLCs

CIC IPN, Mxico

12

Figura 1.1: Estructura bsica del controlador de lgica difusa dedicado.

1.2.1.1 Interfaz de Fuzificacin

La interfaz de fuzificacin, asoc ia a cada entrada su grado de pertenencia a un

c onjunto difuso. Este bloque toma los valores numric os, c onoc idos c omo valores

frgiles (c risp) de las entradas reales, que para el caso del controlador son escalares, y

les asigna un grado de pertenencia respecto de una funcin previamente definida

heursticamente por el experto humano, generando en su salida valores difusos

(fuzificados). El universo de los valores se divide en funciones de pertenencia a las

cuales se identifica mediante etiquetas representativas de la variable. Entre mayor es el

nmero de etiquetas, se tiene un grado mayor de resolucin. Las funciones de

pertenencia dan significado numrico a cada etiqueta e identifican el rango de

valores de entrada que corresponden a una etiqueta.

Las formas ms usuales de las funciones de pertenencia son cuatro: singleton,

gaussiano o c ampana, trapezoidal y triangular, los cuales se muestran en la tabla 1.3,

en donde x* representa un valor numrico real, A es un conjunto difuso que est

c ontenido en el c onjunto x, x

c

es el valor de x donde la funcin es mxima, es la

desviacin estndar y

A

(x) es la funcin de pertenencia o de membresa. En la

literatura especializada a estas formas grficas tambin se les conoce como

fuzificadores.

Captulo !: Realizaciones Hardware de FLCs

CIC IPN, Mxico

13

Tabla 1.3: Tipos de fuzificadores.

Tipo de

Fuzificador

Forma de la Funcin de

Pertenencia

Clculo del Grado de Pertenencia

Singleton

) (x

A

'

* , 0

* , 1

x x

x x

Gaussiano

) (x

A

2

2

2

) * (

c

x x

e

Trapezoidal

'

< <

,

_

< <

,

_

otro 0,

* si ,

*

1

* si ,

*

1

* si , 1

) (

d x c

c d

c x

b x a

a b

x b

c x b

x

A

Triangular

'

< <

< <

otro 0,

* si ,

*

1

* si ,

*

1

* si , 1

) (

b x x

x b

x x

x x a

a x

x x

x x

x

c

c

c

c

c

c

c

A

1.2.1.2 Interfaz de Inferencia

La interfaz de inferencia consta de dos mdulos que interactan entre s: la base de

reglas difusas y el mec anismo de inferenc ia (referirse a la figura 1.1).

1. Una base de reglas difusas (Fuzzy Rules Base) c onsiste en un c onjunto de reglas

Si Entonces (en ingls, If - Then) de la forma:

Si x

1

Es A

1

Y x

2

Es A

2

Y . . . x

n

Es A

n

Entonces z Es B (1.2)

Captulo !: Realizaciones Hardware de FLCs

CIC IPN, Mxico

14

donde A

n

y B, representan los valores lingsticos definidos por los conjuntos

difusos en el universo de disc urso. Las reglas modelan el funcionamiento del

sistema, por lo que el planteamiento correcto de la base de reglas de acuerdo

a la experiencia del operador humano, es factor fundamental para el

comportamiento satisfactorio del controlador. Por lo mismo, a la base de reglas

tambin se le conoce como Base del Conoc imiento.

La base de reglas debe cumplir las siguientes propiedades:

a. Completa. Para cualquier combinacin de valores de entrada se obtiene

un valor apropiado de salida. Se produc e el total cubrimiento del

espacio de entradas.

b. Consistente. No se presentan contradicciones. No existen dos reglas c on

idnticos antecedentes paro distintos consecuentes.

c. Continua. Reglas c ontiguas tienen func iones de pertenenc ia en los

c onsec uentes c on intersec c in nula.

2. La mquina o mec anismo de inferenc ia difusa emplea la informac in

almacenada en la base de reglas difusas para determinar la funcin de

pertenencia de los antecedentes, el grado de activacin de las funciones de

pertenencia del dominio de entrada, y de esta forma obtener la funcin de

pertenencia de los consecuentes proporcionando una nica salida difusa. Para

obtener la salida, la mquina de inferencia combina las diferentes reglas de

c omposic in de ac uerdo a lo estipulado en la teora de c onjuntos difusos. As, la

expresin Si x Es A Entonces z Es B, es abreviada AB, desc ribiendo una relacin

entre dos variables, lo que sugiere que esta regla puede ser definida como una

relacin R en el espac io entrada-salida AxB. Las dos principales formas de

obtencin de las funciones de pertenencia de los antecedentes y de

interpretacin de la sentencia de conexin, y/ o grado de activacin del

dominio de entradas, en la regla difusa AB son:

a. Mtodo del mnimo o de Mamdani. Se almacena en una relacin difusa

R donde se elige la funcin de pertenencia mnima:

R

(x,z) = min{

A

(x),

B

(z)} (1.3)

o bien,

A B = ( )

z x

B A

z x z x ) , /( ) ( ) ( (1.4)

Captulo !: Realizaciones Hardware de FLCs

CIC IPN, Mxico

15

b. Mtodo del produc to o de Larsen. Se almacena en una relacin difusa R,

que realiza el produc to de las funciones de pertenencia respectivas:

R

(x, z) =

A

(x)

B

(z) (1.5)

Ambas correlaciones aplican posteriormente el mtodo del Mximo, para

encontrar un valor resultante total para referenciar una sola funcin de

pertenencia del consecuente. El mtodo ms comnmente utilizado para

realizar la inferencia en hardware es el de Mamdani, debido a que es ms

simple construir unidades que realicen el mnimo y sucesivamente el mximo,

que multiplicadores dedicados. Por la naturaleza del proc eso realizado por el

mtodo Mamdani de inferencia, tambin es conocido simplemente c omo

mtodo MAX MIN.

1.2.1.3 Interfaz de Defuzificacin

El bloque defuzificador genera su respuesta a partir de que la variable lingstica

difusa resultante sale de la interfaz de inferencia. La interfaz de defuzificacin, ser la

encargada de generar el escalar que es el valor real que se entregar a la salida del

controlador.

Son varios los mtodos actuales para generar la salida escalar equivalente al

c onjunto difuso de inferenc ia. Tanto para un sistema difuso MISO (Entradas Mltiples,

Salida nic a) c omo para uno MIMO (Entradas Mltiples, Salidas Mltiples), los

razonamientos son anlogos c onsiderando que la inferenc ia se realiza mediante el

mtodo MAX MIN. As, los princ ipales mtodos de defuzific ac in ms aplic ados son:

1. Defuzificador del rea o Centro de Gravedad (COG). La variable Z* representa

la salida escalar y puede ser cualquier punto en la altura B (c onjunto difuso de

salida, proveniente de la inferenc ia). En la ecuacin 1.6 se muestra la relacin

matemtica que genera la salida escalar. En esta ecuacin

(Z) es la func in

de pertenencia, asoc iada al conjunto difuso de salida, resultante de aplicar el

mecanismo de inferencia al conjunto de reglas difusas.

Z* =

v

B

v

B

dZ Z

ZdZ Z

) (

) (

(1.6)

Captulo !: Realizaciones Hardware de FLCs

CIC IPN, Mxico

16

2. Defuzific ador del Promedio de Centros. En este defuzificador, tambin conocido

como Centro de Sumas, el valor escalar de la variable de salida Z* est

determinado por el promedio de los centros de los M c onjuntos difusos de salida

c on los pesos , siendo igual a la altura de los c onjuntos difusos

c orrespondientes. La ecuacin 1.7 exhibe la relac in matemtic a aplic able. A

su vez, este mtodo es el ms utilizado para la realizacin en hardware.

Z* =

n

1 i

_

Bi

n

1 i

1

_

Bi

) Z (

) Z (

(1.7)

3. Defuzific ador de Criterio del Mximo. La salida escalar es el valor numrico del

punto donde la funcin de pertenencia del conjunto difuso de la salida asume

su valor mximo. Si la altura B c ontiene un solo punto, se define Z* en forma

nica; si por el contrario contiene ms de un punto, se pueden especificar tres

defuzificadores de naturaleza diferente:

a. Defuzificador del Valor Ms Pequeo del Mximo. Este mtodo indic a

que se debe seleccionar como escalar Z* de salida, al menor valor

(primero) de la mayor funcin de pertenencia consecuente inferida.

b. Defuzificador del Valor Ms Grande del Mximo. Se debe seleccionar

como escalar Z* de salida, al mayor valor (primero) de la mayor funcin

de pertenencia consecuente inferida.

c. Defuzificador del Valor Promedio del Mximo. Esta aproximac in

requiere que se elija como escalar Z* de salida, el valor promedio de la

mayor func in de pertenenc ia c onsec uente inferida, tal y c omo lo

sugiere la ecuacin 1.8.

Z* =

) (

) (

B altura

B altura

dZ

ZdZ

(1.8)

Captulo !: Realizaciones Hardware de FLCs

CIC IPN, Mxico

17

1.3 Principales Realizaciones Hardware de FLCs

Los primeros trabajos enc aminados a vinc ular la lgic a difusa c on los diferentes

entornos de aplic ac in en c asos prc tic os, no nec esariamente sistemas de c ontrol,

surgieron en el momento en que la base terica de los Conjuntos Difusos fue

considerada sustentable por la comunidad tecnolgica y cientfica. En 1969, W.

Marinos de la Duke University, conduc e las primeras investigaciones sobre

implementac iones elec trnic as de la lgic a difusa. Las limitac iones c omunes de la

poca no desmerecieron la importancia prctica de la nueva tcnica, respetando

an en nuestros das las restric c iones en respuesta de los c omponentes adic ionales al

sistema; es decir, una situacin es crear dispositivos electrnicos rpidos que realicen el

proc esamiento y otra es que los elementos mecnicos presenten una respuesta

inmediata [3] .

En 1974, E. H. Mamdani present la primera aplicacin de la lgica difusa en un

sistema de control, resultando lo que se denomin Control Difuso (Fuzzy Control).

Mamdani plante la posibilidad de utilizar c omponentes disc retos c on la finalidad de

realizar un proc eso de inferencia manipulando valores de resistencias para variar

c orrientes, aportando una nueva tcnica para el tratamiento electrnico.

En 1985, Togai y Watanabe de AT & T Bell Laboratories, desarrollaron la primera

mquina de inferencia difusa, la cual fue construida sobre un circuito integrado VLSI

con una entrada y una salida de 4 bits. Este integrado ejecutaba hasta 250, 000 FRPS

5

(Fuzzy Rules Per Sec ond Reglas Difusas Por Segundo) sin defuzificacin

6

. Los alc anc es

se limitaron a sistemas de control muy bsicos ya que resolvan solamente funciones de

membresa triangulares clsicas, con un nmero muy reducido de reglas de inferencia,

as como topologas seriales basadas en un modelo de memoria de tabla de datos.

En 1986, los Hitachi Corporation Laboratories desarrollaron un controlador de lgica

difusa dedicado a ajustar la temperatura de un horno, cuyas caractersticas eran ms

generales que su predecesor, comenzando con un soporte mayor de entradas y reglas

de inferencia, pero restringido a una sola salida [2] .

T. Yamakawa, en 1987 present el primer controlador difuso completamente

analgic o en un c hip VLSI, integrando algunos c irc uitos dedic ados anlogos

bipolares. Internamente este proc esador exhibi por primera vez circuitos simples que

realizaban las func iones MAX y MIN, logrando velocidades de hasta un milln de FIPS

5

En el campo de los procesadores difusos, la principal caracterstica que diferencia las arquitecturas, es la velocidad en trminos

de las reglas difusas (FRPS) o de las inferencias (FIPS), evaluadas por segundo.

6

Si no hay defuzificacin, las salidas siguen siendo difusas, por lo que se tena la necesidad de estimar mediante un acoplamiento

independiente, algn mtodo para defuzificar los valores y encontrar las salidas reales.

Captulo !: Realizaciones Hardware de FLCs

CIC IPN, Mxico

18

(Fuzzy Inferences Per Second - Inferencias Difusas Por Segundo) y una unidad

defuzificadora basada en el mtodo del Centro de Gravedad (COG - Center Of

Gravity). Se tena la opcin de utilizar el controlador sin la unidad de defuzificacin,

obteniendo en este caso hasta 10 MFIPS.

En 1989, Togai y Watanabe, complementaron sus investigaciones en el campo del

diseo VLSI, presentado el primer controlador digital basado en lgica difusa c on

distribucin comercial, que no era totalmente adaptable a cualquier sistema, pero que

superaba por mucho la gama de aplicaciones y desempeo propuesto por los

antecesores. Este controlador adoptaba la suma lgic a de mnimos y el produc to

lgic o de mximos como operadores de unin y de interseccin respectivamente. Este

c irc uito integrado trabajaba a 36 MHz, y traduc a cerca de 580,000 FIPS, c on un

conjunto aceptable de aproximadamente 102 reglas de inferencia.

A la par de estos logros electrnicos, las herramientas de automatizacin de diseos,

refirindose especficamente a las propias de las tecnologas programables,

comenzaron el despunte hasta alcanzar niveles inimaginables. A partir de 1997

c omienza una serie de trabajos dirigidos hacia el control digital bajo mecanismos

inteligentes utilizando c omo base para el diseo del hardware, arreglos lgic os

programables y lenguajes de desc ripcin de hardware, tal y como lo demuestran los

siguientes artculos encontrados.

1. "Implementing Fuzzy Control Systems Using VHDL y Statecharts", es un artculo

escrito por Valentina Salapura y Volker Hamann, de la Technisc he Universitt

Wien de Austria [55]. Este doc umento aborda la implementac in de un sistema

de control difuso muy sencillo, pero que detalla una forma muy interesante de

atacar la problemtica y que es en s la misma idea de este trabajo de tesis:

separa los proc esos de fuzificacin, inferencia y defuzificacin, en tres bloques

independientes. El anlisis de la base de reglas del c ontrolador se realiza

utilizando Cartas de Estados (Statec harts). Todo el desarrollo se concreta

mediante VHDL (VHSIC HDL, Very High Speed Integrated Circuit HDL Circuito

Integrado de Muy Alta Velocidad modelado con HDL); la parte de la base de

reglas, se realiza primeramente en SPeeDCHART

7

para posteriormente utilizar el

sintetizador de VHDL y convertir todo a cdigo.

2. "The Programmable Fuzzy Logic Array", encontrado en Internet en la pgina

electrnica de Texas Instruments [56], es un artculo escrito por Philip Thrift del

Central Research Laboratories, Texas Instruments Incorporated. El doc umento

7

Se trata de una herramienta grfica que permite trazar diagramas de estados en mquinas de estados finitos. Tiene una interfaz

con VHDL - based logic Synthesis, que convierte los diagramas dibujados a cdigo VHDL.

Captulo !: Realizaciones Hardware de FLCs

CIC IPN, Mxico

19

desc ribe un dispositivo programable para lgic a difusa, el c ual c uenta c on su

propio ambiente de programacin.

El Arreglo de Lgica Difusa Programable (PFLA - Programmable Fuzzy Logic

Array), tal y como fue nombrado por su creador, produc e mapeos

multidimensionales no lineales implementando reglas de lgica difusa sobre una

arquitec tura de arreglos programable. Estudiando la informac in suministrada,

se encontraron varias desventajas: se trata de un dispositivo con recursos

comprometidos, como en el caso de un PLD, lo que restringe el diseo; por otra

parte, slo realiza la inferenc ia difusa manipulando las reglas lgic as, lo que

implicara redisear en base a mecanismos de control para que sirviera a

propsitos ms elaborados y generales. No c onsidera ni la fuzific ac in ni la

defuzificacin de las variables, pero exhibe una forma inteligente de resolver la

inferencia trazando un arreglo.

1.3.1 Clasificacin de los FLCs Dedicados

Por s mismo, el proc eso difuso es de c arc ter serial. Est demostrado que

mnimamente debe operar con una divisin de tres interfaces o mdulos que se

ejecutan de manera secuencial y que no cambian de orden: fuzificacin, Inferencia

(integrando la base de reglas y el mecanismo de inferencia) y defuzificacin. Cada

etapa depende de su predecesora; por ejemplo, no es posible evaluar las reglas de

inferencia si an no se ha realizado la fuzificacin de las variables. La optimizacin del

proc eso difuso no se encuentra en la forma de organizar la arquitectura en la

interconexin de las tres particiones bsicas, que como ya se advirti es invariable, sino

en la forma en que cada mdulo de la divisin funcional proc esa los datos respectivos.

Lo anterior dirige la disc usin a afirmar que no es posible paralelizar el proc eso

c ompleto (debido a la dependencia entre mdulos funcionales), pero s es posible

paralelizar las operaciones que cada uno de los mdulos realiza internamente, aspecto

que se comenta ms a detalle en el Captulo 3 de esta tesis.

La realizacin en hardware de los controladores difusos dedicados se clasifica en

dos grandes grupos: controladores dependientes de la naturaleza de la seal tratada y

controladores supeditados por la estruc tura fsic a interna. A c ontinuac in se inc luye

una breve explicacin de los elementos que caracterizan cada grupo.

Captulo !: Realizaciones Hardware de FLCs

CIC IPN, Mxico

20

1.3.1.1 Controladores Dependientes de la Naturaleza de la Seal Tratada

De acuerdo a la naturaleza de la seal que proc esan, los controladores pueden

c onstruirse mediante estrategias de hardware analgic o, digital, o un hbrido (mixto)

de ambos [2, 15] .

1. Analgic os. Si se parte de la idea de que un controlador (hablando en trminos

generales) recibe y entrega seales provenientes de un mundo analgico cuyo

c omportamiento es lineal y c ontinuo, no hay ms que rec onoc er que no hay

mejor proc esamiento que el realizado por componentes de la misma

naturaleza. Las realizaciones analgicas son muy eficientes en cuanto al rea

de silic io que oc upan, no nec esitan interfac es AD/ DA c on el mundo real y son

capaces de obtener muy buenos resultados cuando se realizan estruc turas de

proc esamiento paralelo

8

. Sin embargo, suelen tener un nmero reducido de

entradas, salidas y reglas difusas. Adems, la prec isin del c lc ulo analgic o

presenta limitaciones tecnolgicas como el desapareamiento entre transistores

y las variaciones de los parmetros del proc eso de fabricacin, por lo que son

muy sensibles al ruido y a las interferencias.

2. Digitales. Las realizaciones de este tipo son ms robustas (permiten ms

variables de entrada, salida y reglas difusas) y fc iles de disear, as mismo

presentan una programacin ms simple. En contraparte, oc upan ms rea de

silic io para realizar operac iones dedic adas c omo la multiplic ac in o la divisin y

requieren convertidores AD/ DA para comunicarse con el exterior.

3. Hbridos. La implementacin hbrida, utiliza las mejores propiedades de las dos

anteriores: utiliza elementos digitales para c ontrolar la c irc uitera analgic a, as

c omo para el almac enamiento de datos y utiliza elementos analgic os para

realizar los proc esamientos debidos. Las herramientas de diseo son ms

costosas y sofisticadas.

2.3.1.2 Controladores Supeditados por la Estructura Interna

Esta clasificacin de controladores, est enfocada directamente a las realizaciones

digitales e hbridas [2, 4] . En el contexto particular de este trabajo de tesis, se cataloga

como propia de la realizacin digital.

8

En la actualidad, el camino que persiguen los investigadores enfocados a las realizaciones analgicas, es mejorar el

procesamiento de la informacin. Existen dos derivaciones: utilizando amplificadores operacionales (modo tensin) y utilizando

amplificadores de transconductancia (modo corriente).

Captulo !: Realizaciones Hardware de FLCs

CIC IPN, Mxico

21

Las implementaciones pertenecientes a este grupo presentan arquitecturas basadas

en la forma interna en la que obtienen sus datos para comenzar las operaciones

especializadas: si provienen de tablas con valores de fuzificacin y defuzificacin

precalculados, o si se obtienen en el mismo instante con ayuda de unidades

aritmticas en hardware. En este sentido se tienen dos tipos de modelos a seguir:

Modelo Orientado a Memoria y Modelo Orientado a Clc ulos.

1. Modelo Orientado a Memoria. Tambin llamado Modelo de Obtenc in

Indirecta de Datos Difusos, presenta la particularidad de utilizar tablas

precalculadas de valores, almacenadas en una memoria que puede ser

externa o interna al controlador. Los datos pueden ser calculados directamente

por el diseador o como en la mayora de los casos (incluidas las versiones

comerciales) se utiliza un software que realiza los clculos y crea el ensamblador

que configura las caractersticas que cumplir el controlador de acuerdo a los

requerimientos propuestos por el diseador. La figura 1.2 esquematiza un

controlador orientado a memoria.

Figura 1.2: Controlador con modelo orientado a memoria.

La utilizacin de un dispositivo de memoria para almacenar las tablas

precalculadas implica el diseo de un controlador de memoria y a la vez de un

sistema de sinc ronizac in por c ic los para la obtenc in de c ada valor. La

velocidad de acceso para lectura y escritura, es una limitante fsica en este tipo

de modelos; aunado a que los datos se van obteniendo uno a uno a la vez.

Para sistemas mecnicos simples, este tipo de modelo es una buena opcin

dado que la gran mayora de los controladores difusos dedicados se disean de

acuerdo a esta orientacin, as el mercado actual contempla un soporte muy

importante en lo concerniente al software y dispositivos de propietario.

Captulo !: Realizaciones Hardware de FLCs

CIC IPN, Mxico

22

2. Modelo Orientado a Clc ulos. La figura 1.3 muestra un controlador de este tipo;

tambin se c onoc e c omo Modelo de Obtencin Directa de Datos Difusos y

tiene la caracterstica de utilizar unidades aritmticas construidas en software o

hardware

9

, que realizan el clculo a medida que se tiene un valor a proc esar.

La estimacin de las arquitecturas orientadas a este modelo necesitan de

algoritmos aritmticos ptimos en la implementacin de cada una de las

unidades de clculo. Este modelo no requiere de clculos previos y

especficamente es el tipo de orientacin que se utiliz en esta tesis.

Figura 1.3: Controlador con modelo orientado a clculos.

Resumen del Captulo

En este primer captulo, se present una revisin sucinta a la realizacin hardware de

los c ontroladores de lgic a difusa, planteando un marc o teric o sobre la lgic a difusa

enc aminada al c ontrol.

En el siguiente c aptulo, Captulo 2, se da una breve introduccin a las Tecnologas

Programables en general, c on la intenc in de analizar la tec nologa de implantac in

sugerida para el controlador.

9

La mayora de las bibliografas refirindose al Modelo Orientado a Clculos, tratan indiferentemente la implementacin de las

unidades aritmticas va software o hardware; sin embargo, de manera muy particular y de acuerdo al anlisis de acceso a

memoria, la implementacin de una unidad aritmtica en software nos conduce al caso de un modelo orientado a memoria ms

que a uno orientado a clculos.

CIC IPN, Mxico

23

Captulo 2

Generalidades de las Tecnologas Programables

Contenido del Captulo

El contexto de las Tecnologas Programables resulta primordial en soluciones que

infieren caractersticas configurables y reconfigurables, ya sea para optimizar un diseo

o para variar los parmetros del mismo. La realizac in de sistemas elec trnic os vertida

sobre FPGAs es todo un campo tecnolgic o en el diseo digital moderno.

En este apartado slo se desc ribe un panorama muy general sobre estas

tec nologas. Independientemente de su operatividad programable, un dispositivo de

esta naturaleza no deja de ser un circuito integrado, por lo que tambin existen otras

caractersticas que no se asumen a profundidad en esta seccin como son el retardo

de propagacin, la inmunidad al ruido y la disipacin de potencia.

El origen de este resumen es inherente al desarrollo del trabajo de tesis, debido a

que para considerar cumplidos los objetivos especficos planteados, es imprescindible

el hecho de conocer el marco teric o que envuelve el uso de estas herramientas para

aplicar correctamente la metodologa de diseo y crear soluciones no slo funcionales,

sino ptimas y genric as.

Captulo !: Tecnologas Programables

CIC IPN, Mxico

24

2.1 Fundamentos Tericos sobre ASICs

Un ASIC (Applic ation Spec ific Integrated Circ uit - Circ uito Integrado de Aplic ac in

Espec fic a) es un dispositivo terminal. Un diseo que ha sido probado y optimizado, se

manufac tura en una pastilla de silic io c uya operac in ser prefijada. Slo c ontiene las

interconexiones y elementos necesarios para realizar la funcin especfica deseada.

De manera general, un ASIC contiene dos elementos bsicos: Mdulos Lgic os e

Interconexiones (referirse a la figura 2.1). Los mdulos lgic os

1

(arreglos lgic os fijos o

bloques c onfigurables, dependiendo de la tec nologa del dispositivo programable)

c ontendrn una c onfigurac in elemental para generar una func in lgic a dada. Por

su parte, las interconexiones permiten el enlace entre mdulos lgicos bsicos para

crear mdulos ms complejos que realicen operaciones ms elaboradas, a esta

accin se le conoce como enrutado [18] .

Figura 2.1: Esquema bsico que muestra la arquitectura general, no detallada, de un ASIC.

Los ASICs se clasifican en tres grupos caractersticos: Full Custom (arquitec tura a la

medida), Semi - Custom (arquitec tura parc ialmente a la medida) y Programmables

(arquitec tura programable). La programac in, tanto para los ASIC Full Custom c omo

para los Semi Custom, se realiza direc tamente en fbric a. Los Programmables ASICs

pueden programarse por un usuario final, por lo que se dice que un ASIC de este tipo es

un dispositivo Programable en Campo. Posteriormente se comentar a detalle esta

particularidad.

1

Son conocidos como unidades bsicas de desarrollo, y son las encargadas de realizar las operaciones lgicas definidas por el

diseador.

Captulo !: Tecnologas Programables

CIC IPN, Mxico

25

2.2 ASIC Full - Custom

Para los ASIC Full Custom, los mdulos lgic os y los enrutamientos, se c onstruyen

hasta el ms mnimo detalle de distribucin de acuerdo a las especificaciones que el

usuario requiere para su diseo. Es decir, se crean mdulos y enrutamientos propios

para personalizar (Custom) o trazar a la medida un dispositivo, por lo que es necesario

manufacturar en fbrica.

De ac uerdo a la evoluc in no slo de tec nologas sino de c onc eptos, el ASIC Full

Custom, tradic ionalmente llamado MPGA (Mask programmable Gate Array - Arreglo

de Compuertas Programable por Mscara) consiste en una serie de transistores que

pueden conectarse entre s de acuerdo a los requerimientos del diseador, para crear

func iones lgic as simples o c omplejas. La personalizac in se realiza durante la

fabricacin del integrado especificando las interconexiones de metal. Esto significa

que para que un usuario emplee un MPGA existe un c osto industrial grande y el tiempo

de manufacturacin es generalmente de 12 semanas.

2.3 ASIC Semi - Custom

Los ASICs Semi Custom, tambin c onoc idos c omo ASICs Basados en Celdas

Estndar (Standard Cell Based ASICs), utilizan mdulos prediseados. Estos mdulos

se denominan Celdas Lgic as debido a la partic ularidad de su func in. El diseador se

limita a utilizar el recurso de las celdas preconstruidas colocndolas en el lugar que sea

necesario dentro del dispositivo de acuerdo a las especificaciones de su diseo. En este

tipo de ASICs, los fabricantes proporcionan un software que contiene una serie de

bibliotec as llamadas Bibliotec as de Celdas Estndar (Standard Cell Libraries) que

contienen los mdulos prediseados [19] .

La ac c in de utilizar Celdas Estndar prediseadas y plenamente probadas,

produc e un ahorro notorio de tiempo, dinero y sobre todo se evitan riesgos posteriores a

la realizac in elec trnic a. Las desventajas princ ipales radic an en el tiempo de

manufactura que tiene que ser realizada en fbrica (por lo general toma de 6 a 8

semanas) y en que en la mayora de las ocasiones, los fabricantes venden por

separado las celdas

2

que realizan func iones lgic as ms c omplejas.

2

La mayora de los fabricantes venden por separado mdulos a los que han denominado CORES y que son ms aplicados en el

diseo con ASICs Programables. Un CORE es un mdulo prediseado que implementa una funcin especfica que va desde un

simple multiplicador hasta un microprocesador completo, pasando por filtros e interfaces con bus PCI, entre otros.

Captulo !: Tecnologas Programables

CIC IPN, Mxico

26

Las interconexiones se realizan de manera personalizada, mediante lneas de unin

c onstruidas especficamente para conectar las celdas colocadas por el usuario en un

diseo partic ular, por lo que sus arquitec turas internas son parc ialmente a la medida:

una parte est definida por el fabricante (las celdas estndar y la manufacturacin) y

la otra est definida por el diseador (seleccin de las celdas, colocacin de las

mismas en el dispositivo y las Interconexiones entre ellas).

2.4 ASIC Programable

Los ASICs Programables (Programmables ASICs) c onoc idos tambin c omo ASICs

Basados en Arreglos de Compuertas (Gate Array Based ASICs, son las arquitec turas

ms representativas entre otras tantas existentes en el mercado actual y que

c onservan la c arac terstic a bsic a de programabilidad [18, 20] . Incluyen a los PLDs

(Programmable Logic Devic es Dispositivos Lgic os Programables), CPLDs (Complex

PLDs PLDs Complejos) y FPGAs (Field Programmable Gate Array Arreglo de

Compuertas Programable en Campo).

Estos ASICs c ontienen mdulos prediseados por el fabric ante (similares a las c eldas

estndar de los Semi Custom) que pueden ser enrutados por usuario. A la vez

permiten crear nuevos mdulos que pueden ser reutilizados. La ventaja inmediata est

en que los diseos pueden ser implementados en su totalidad, inc luyendo la

programacin, directamente en un mismo ambiente de desarrollo por el usuario final,

reduciendo el costo y el tiempo de diseo, no necesitando de una manufactura

terminal en fbrica. Debido a esta versatilidad en el diseo y a su aplicacin inmediata,

los ASICs Programables tambin son c onoc idos en la prc tic a c omo FPDs (Field

Programmables Devic es Dispositivos Programables en Campo) con una serie de

denominaciones comunes: FPLA (Field Programmable Logic Array Arreglo Lgico

Programable en Campo), FPA (Field Programmable Array Arreglo Programable en

Campo), etc tera.

Para asumir una mejor comprensin de los dispositivos, as como para cubrir el

objetivo de esta revisin, nos centraremos en el estudio de un ASIC Programable,

tratando c on tpic os de importanc ia general que c onforman el c ontexto del diseo

c on tec nologas programables: Tipos de Arquitec turas, Disposic in de Programac in,

Lgica Programable, y Tec nologas de Programac in.

Captulo !: Tecnologas Programables

CIC IPN, Mxico

27