Академический Документы

Профессиональный Документы

Культура Документы

Capitulo 1 msp430

Загружено:

Jr OlИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Capitulo 1 msp430

Загружено:

Jr OlАвторское право:

Доступные форматы

Chapter 1

SLAU144I December 2004 Revised January 2012

Introduction

This chapter describes the architecture of the MSP430.

Topic

...........................................................................................................................

Architecture ...................................................................................................... Flexible Clock System ........................................................................................ Embedded Emulation ......................................................................................... Address Space .................................................................................................. MSP430x2xx Family Enhancements .....................................................................

Page

1.1 1.2 1.3 1.4 1.5

26 26 27 27 29

SLAU144I December 2004 Revised January 2012 Submit Documentation Feedback

Introduction

25

Copyright 20042012, Texas Instruments Incorporated

Architecture

www.ti.com

1.1

Architecture

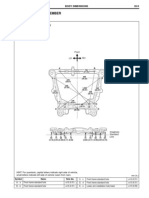

The MSP430 incorporates a 16-bit RISC CPU, peripherals, and a flexible clock system that interconnect using a von-Neumann common memory address bus (MAB) and memory data bus (MDB) (see Figure 1-1). Partnering a modern CPU with modular memory-mapped analog and digital peripherals, the MSP430 offers solutions for demanding mixed-signal applications. Key features of the MSP430x2xx family include: Ultralow-power architecture extends battery life 0.1 A RAM retention 0.8 A real-time clock mode 250 A/MIPS active High-performance analog ideal for precision measurement Comparator-gated timers for measuring resistive elements 16-bit RISC CPU enables new applications at a fraction of the code size. Large register file eliminates working file bottleneck Compact core design reduces power consumption and cost Optimized for modern high-level programming Only 27 core instructions and seven addressing modes Extensive vectored-interrupt capability In-system programmable Flash permits flexible code changes, field upgrades and data logging

Clock System

MCLK

ACLK SMCLK

Flash/ ROM

RAM

Peripheral

Peripheral

Peripheral

RISC CPU 16-Bit

JTAG/Debug

MAB 16-Bit

MDB 16-Bit

Bus Conv.

MDB 8-Bit

JTAG

ACLK SMCLK

Watchdog

Peripheral

Peripheral

Peripheral

Peripheral

Figure 1-1. MSP430 Architecture

1.2

Flexible Clock System

The clock system is designed specifically for battery-powered applications. A low-frequency auxiliary clock (ACLK) is driven directly from a common 32-kHz watch crystal. The ACLK can be used for a background real-time clock self wake-up function. An integrated high-speed digitally controlled oscillator (DCO) can source the master clock (MCLK) used by the CPU and high-speed peripherals. By design, the DCO is active and stable in less than 2 s at 1 MHz. MSP430-based solutions effectively use the high-performance 16-bit RISC CPU in very short bursts. Low-frequency auxiliary clock = Ultralow-power stand-by mode High-speed master clock = High performance signal processing

26

Introduction

Copyright 20042012, Texas Instruments Incorporated

SLAU144I December 2004 Revised January 2012 Submit Documentation Feedback

www.ti.com

Embedded Emulation

1.3

Embedded Emulation

Dedicated embedded emulation logic resides on the device itself and is accessed via JTAG using no additional system resources. The benefits of embedded emulation include: Unobtrusive development and debug with full-speed execution, breakpoints, and single-steps in an application are supported. Development is in-system subject to the same characteristics as the final application. Mixed-signal integrity is preserved and not subject to cabling interference.

1.4

Address Space

The MSP430 von-Neumann architecture has one address space shared with special function registers (SFRs), peripherals, RAM, and Flash/ROM memory as shown in Figure 1-2. See the device-specific data sheets for specific memory maps. Code access are always performed on even addresses. Data can be accessed as bytes or words. The addressable memory space is currently 128 KB.

Access 1FFFFh 10000h 0FFFFh 0FFE0h 0FFDFh Flash/ROM Word/Byte Interrupt Vector Table Word/Byte Flash/ROM Word/Byte

0200h 01FFh

RAM

Word/Byte

16-Bit Peripheral Modules 0100h 0FFh 010h 0Fh 0h 8-Bit Peripheral Modules Special Function Registers

Word

Byte

Byte

Figure 1-2. Memory Map

1.4.1 Flash/ROM

The start address of Flash/ROM depends on the amount of Flash/ROM present and varies by device. The end address for Flash/ROM is 0x0FFFF for devices with less that 60KB of Flash/ROM. Flash can be used for both code and data. Word or byte tables can be stored and used in Flash/ROM without the need to copy the tables to RAM before using them. The interrupt vector table is mapped into the upper 16 words of Flash/ROM address space, with the highest priority interrupt vector at the highest Flash/ROM word address (0x0FFFE).

SLAU144I December 2004 Revised January 2012 Submit Documentation Feedback

Introduction

27

Copyright 20042012, Texas Instruments Incorporated

Address Space

www.ti.com

1.4.2 RAM

RAM starts at 0200h. The end address of RAM depends on the amount of RAM present and varies by device. RAM can be used for both code and data.

1.4.3 Peripheral Modules

Peripheral modules are mapped into the address space. The address space from 0100 to 01FFh is reserved for 16-bit peripheral modules. These modules should be accessed with word instructions. If byte instructions are used, only even addresses are permissible, and the high byte of the result is always 0. The address space from 010h to 0FFh is reserved for 8-bit peripheral modules. These modules should be accessed with byte instructions. Read access of byte modules using word instructions results in unpredictable data in the high byte. If word data is written to a byte module only the low byte is written into the peripheral register, ignoring the high byte.

1.4.4 Special Function Registers (SFRs)

Some peripheral functions are configured in the SFRs. The SFRs are located in the lower 16 bytes of the address space, and are organized by byte. SFRs must be accessed using byte instructions only. See the device-specific data sheets for applicable SFR bits.

1.4.5 Memory Organization

Bytes are located at even or odd addresses. Words are only located at even addresses as shown in Figure 1-3. When using word instructions, only even addresses may be used. The low byte of a word is always an even address. The high byte is at the next odd address. For example, if a data word is located at address xxx4h, then the low byte of that data word is located at address xxx4h, and the high byte of that word is located at address xxx5h.

xxxAh 15 7 14 6 . . Bits . . . . Bits . . Byte Byte Word (High Byte) Word (Low Byte) 9 1 8 0 xxx9h xxx8h xxx7h xxx6h xxx5h xxx4h xxx3h

Figure 1-3. Bits, Bytes, and Words in a Byte-Organized Memory

28

Introduction

Copyright 20042012, Texas Instruments Incorporated

SLAU144I December 2004 Revised January 2012 Submit Documentation Feedback

www.ti.com

MSP430x2xx Family Enhancements

1.5

MSP430x2xx Family Enhancements

Table 1-1 highlights enhancements made to the MSP430x2xx family. The enhancements are discussed fully in the following chapters, or in the case of improved device parameters, shown in the device-specific data sheet. Table 1-1. MSP430x2xx Family Enhancements

Subject Reset Enhancement Brownout reset is included on all MSP430x2xx devices. PORIFG and RSTIFG flags have been added to IFG1 to indicate the cause of a reset. An instruction fetch from the address range 0x0000 - 0x01FF will reset the device. All MSP430x2xx devices integrate the Watchdog Timer+ module (WDT+). The WDT+ ensures the clock source for the timer is never disabled. The LFXT1 oscillator has selectable load capacitors in LF mode. The LFXT1 supports up to 16-MHz crystals in HF mode. The LFXT1 includes oscillator fault detection in LF mode. The XIN and XOUT pins are shared function pins on 20- and 28-pin devices. The external R OSCfeature of the DCO not supported on some devices. Software should not set the LSB of the BCSCTL2 register in this case. See the device-specific data sheet for details. The DCO operating frequency has been significantly increased. The DCO temperature stability has been significantly improved. The information memory has 4 segments of 64 bytes each. SegmentA is individually locked with the LOCKA bit. All information if protected from mass erase with the LOCKA bit. Segment erases can be interrupted by an interrupt. Flash updates can be aborted by an interrupt. Flash programming voltage has been lowered to 2.2 V Program/erase time has been reduced. Clock failure aborts a flash update.

Watchdog Timer

Basic Clock System

Flash Memory

Digital I/O

All ports have integrated pullup/pulldown resistors. P2.6 and P2.7 functions have been added to 20- and 28- pin devices. These are shared functions with XIN and XOUT. Software must not clear the P2SELx bits for these pins if crystal operation is required. Comparator_A has expanded input capability with a new input multiplexer. Typical LPM3 current consumption has been reduced almost 50% at 3 V. DCO startup time has been significantly reduced. The maximum operating frequency is 16 MHz at 3.3 V. An incorrect password causes a mass erase. BSL entry sequence is more robust to prevent accidental entry and erasure.

Comparator_A Low Power Operating frequency BSL

SLAU144I December 2004 Revised January 2012 Submit Documentation Feedback

Introduction

29

Copyright 20042012, Texas Instruments Incorporated

Вам также может понравиться

- Cannondale Super V and Super V Raven Owner'S ManualДокумент6 страницCannondale Super V and Super V Raven Owner'S ManualJVH1978Оценок пока нет

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- From To Load Details Cable Type Sizing For Short Circuit Sizing For Current Rating Voltage Drop CalculationДокумент36 страницFrom To Load Details Cable Type Sizing For Short Circuit Sizing For Current Rating Voltage Drop CalculationmagycОценок пока нет

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- B, RB EngineДокумент25 страницB, RB Enginemoparman175% (4)

- Retail Price List (01.07.2023) - For Website & General CirculationДокумент1 страницаRetail Price List (01.07.2023) - For Website & General CirculationBilal Cable dealerОценок пока нет

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- Antena Bibanda, OSJ146440Документ3 страницыAntena Bibanda, OSJ146440CarlosAgustoPinedaSanchezОценок пока нет

- T-MEET324LA Experiment No.7 Centrifugal Pump MEE31Документ11 страницT-MEET324LA Experiment No.7 Centrifugal Pump MEE31Paul Ryan GeneralОценок пока нет

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- Nad T743 GBДокумент32 страницыNad T743 GBemehranОценок пока нет

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Questions On DC Circuit - Electrical4uДокумент16 страницQuestions On DC Circuit - Electrical4udhineshp0% (2)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- Baker - 690981 PDFДокумент24 страницыBaker - 690981 PDFAsep SuhermanОценок пока нет

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- MAN B&W S70ME-C8.2-TII: Project Guide Electronically Controlled Twostroke EnginesДокумент387 страницMAN B&W S70ME-C8.2-TII: Project Guide Electronically Controlled Twostroke EnginesСлавик Мосин100% (1)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Week 5 ABS ESP TCS SystemsДокумент72 страницыWeek 5 ABS ESP TCS SystemsahmedaboshadyОценок пока нет

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- Smart Ato ManualДокумент6 страницSmart Ato ManualPerran TrevanОценок пока нет

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- Preventative Maintenance Guide For Mt3300 Mt3400 TwtaДокумент12 страницPreventative Maintenance Guide For Mt3300 Mt3400 Twtamohkal1168Оценок пока нет

- Price ListДокумент519 страницPrice Listabrar nurtata100% (1)

- Stafford - Presentation - PDFДокумент21 страницаStafford - Presentation - PDFdeepak kumarОценок пока нет

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- TSPL-1905 Technical Offer Dt.16.04.2022Документ4 страницыTSPL-1905 Technical Offer Dt.16.04.2022SECI 2020Оценок пока нет

- MAN 05 003 01 Service Manual MC 3 6Документ2 страницыMAN 05 003 01 Service Manual MC 3 6pabloОценок пока нет

- SM 3Документ539 страницSM 3Rizky Motor100% (1)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (345)

- 2008-2009 GM Magna Transfer Case Detailed Info, Bulletin # 1226Документ10 страниц2008-2009 GM Magna Transfer Case Detailed Info, Bulletin # 1226davidОценок пока нет

- Buck ConverterДокумент31 страницаBuck Converterbalak144Оценок пока нет

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- Proposal For An Advanced Embedded System Trainer ModuleДокумент3 страницыProposal For An Advanced Embedded System Trainer ModuleSolomon AkpanОценок пока нет

- Bike Frames For Sale - EbayДокумент1 страницаBike Frames For Sale - EbayamirsharifiОценок пока нет

- Firefly LED LightingДокумент6 страницFirefly LED Lightingkhraieric16Оценок пока нет

- Suspension Crossmember: Body Dimensions DI-9Документ1 страницаSuspension Crossmember: Body Dimensions DI-9diemnganОценок пока нет

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- BDX53C PDFДокумент5 страницBDX53C PDFonafetsОценок пока нет

- (JP120BC) Quotation of Horizontal Semi-Automatic Hydraulic Baler MachineДокумент4 страницы(JP120BC) Quotation of Horizontal Semi-Automatic Hydraulic Baler MachineEdwin Guerrero JachoОценок пока нет

- S10 Electric Power PackДокумент22 страницыS10 Electric Power PackAdolfo Badillo GálvezОценок пока нет

- Hino 700 Exhaust Brake-Engine Retarder WireingДокумент2 страницыHino 700 Exhaust Brake-Engine Retarder Wireingg.shien5150100% (1)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- Mercedes-Benz M254 Engine - Press ReleaseДокумент4 страницыMercedes-Benz M254 Engine - Press Releasefransiscus_282501842Оценок пока нет

- 315 D CaterpillarДокумент4 страницы315 D CaterpillarJose nildo lobato Mendes Mendes100% (1)