Академический Документы

Профессиональный Документы

Культура Документы

315Mhz Low-Power, +3V Superheterodyne Receiver: General Description Features

Загружено:

J Jesús Villanueva GarcíaИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

315Mhz Low-Power, +3V Superheterodyne Receiver: General Description Features

Загружено:

J Jesús Villanueva GarcíaАвторское право:

Доступные форматы

19-2135; Rev 1; 8/02

315MHz Low-Power, +3V Superheterodyne Receiver

General Description

The MAX1470 is a fully integrated low-power CMOS superheterodyne receiver for use with amplitude-shiftkeyed (ASK) data in the 315MHz band. With few required external components, and a low-current power-down mode, it is ideal for cost- and power-sensitive applications in the automotive and consumer markets. The chip consists of a 315MHz low-noise amplifier (LNA), an image rejection mixer, a fully integrated 315MHz phase-lock-loop (PLL), a 10.7MHz IF limiting amplifier stage with received-signal-strength indicator (RSSI) and an ASK demodulator, and analog baseband data-recovery circuitry. The MAX1470 is available in a 28-pin TSSOP package. o Built-In 53dB RF Image Rejection o -115dBm Receive Sensitivity* o 250s Startup Time o Low 5.5mA Operating Supply Current o 1.25A Low-Current Power-Down Mode for Efficient Power Cycling o 250MHz to 500MHz Operating Band (Image Rejection Optimized at 315MHz) o Integrated PLL with On-Board Voltage-Controlled Oscillator (VCO) and Loop Filter o Selectable IF Bandwidth Through External Filter o Complete Receive System from RF to Digital Data Out

*See Note 2, AC Electrical Characteristics.

Features

o Operates from a Single +3.0V to +3.6V Supply

MAX1470

Applications

Remote Keyless Entry Garage Door Openers Remote Controls Wireless Sensors Wireless Computer Peripherals Security Systems Toys Video Game Controllers Medical Systems

Ordering Information

PART MAX1470EUI TEMP RANGE -40C to +85C PIN-PACKAGE 28 TSSOP

Typical Application Circuit appears at end of data sheet. Pin Configuration appears at end of data sheet.

Functional Diagram

LNAOUT 6 MIXIN1 8 MIXIN2 9 MIXOUT 12 IFIN1 17 IFIN2 18 IF LIMITING AMPS LNA 0 Q

LNAIN

MAX1470

4

LNASRC

90 I DIVIDE BY 64

RSSI

DVDD

14

VCO DATA FILTER

AVDD

2,7 PHASE DETECTOR 13 CRYSTAL DRIVER SHUTDOWN DATA SLICER PEAK DETECTOR 1 XTAL1 28 XTAL2 27 PWRDN 25 DATAOUT 20 DSN 19 DSP 26 PDOUT 21 OPP LOOP FILTER

RDF2 100k

RDF1 100k

DGND

AGND

5,10

22 DF

________________________________________________________________ Maxim Integrated Products

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxims website at www.maxim-ic.com.

315MHz Low-Power, +3V Superheterodyne Receiver MAX1470

ABSOLUTE MAXIMUM RATINGS

AVDD to AGND ......................................................-0.3V to +4.0V DVDD to DGND......................................................-0.3V to +4.0V All Other Pins Referenced to AGND...........-0.3V to (VDD + 0.3V) Continuous Power Dissipation (TA = +70C) 28-Pin TSSOP (derate 13mW/C above +70C) .........1039mW Operating Temperature Range MAX1470EUI ...................................................-40C to +85C Storage Temperature Range .............................-60C to +150C Lead Temperature (soldering, 10s) .................................+300C

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

DC ELECTRICAL CHARACTERISTICS

(Typical Application Circuit, VDD = +3.0V to +3.6V, no RF signal applied, TA = -40C to +85C. Typical values are at VDD = +3.3V, TA = +25C, unless otherwise noted.) (Note 1)

PARAMETER Supply Voltage Supply Current Shutdown Supply Current PWRDN Voltage Input Low PWRDN Voltage Input High DATAOUT Voltage Output Low DATAOUT Voltage Output High SYMBOL VDD IDD ISHUTDOWN VIL VIH VOL VOH IDATAOUT = 100A IDATAOUT = -100A VDD 0.4 VDD 0.4 0.4 PWRDN = VDD PWRDN = GND CONDITIONS MIN 3.0 5.5 1.25 0.4 TYP MAX 3.6 UNITS V mA A V V V V

AC ELECTRICAL CHARACTERISTICS

(Typical Application Circuit, all RF inputs and outputs are referenced to 50, VDD = +3.3V, TA = +25C, fRFIN = 315MHz, unless otherwise noted.) (Note 1)

PARAMETER GENERAL CHARACTERISTICS Maximum Startup Time Maximum Receiver Input Level Minimum Receiver Input Level, 315MHz Minimum Receiver Input Level, 433.92MHz Receivers LOW-NOISE AMPLIFIER (LNA) Input Impedance 1dB Compression Point Input-Referred 3rd-Order Intercept LO Signal Feedthrough to Antenna Output Impedance S22LNA Normalized to 50 S11LNA P1dBLNA IIP3LNA Normalized to 50 (Note 3) 1 - j4 -22 -18 -95 0.12 j4.4 dBm dBm dBm fRFIN TON RFINMAX RFINMIN Time from PWRDN deasserting to valid data out Modulation depth 60dB Average carrier power level (Note 2) Peak power level (Note 2) Average carrier power level (Note 2) Peak power level (Note 2) 250 0 -115 -109 -110 -104 250 to 500 s dBm dBm dBm MHz SYMBOL CONDITIONS MIN TYP MAX UNITS

_______________________________________________________________________________________

315MHz Low-Power, +3V Superheterodyne Receiver

AC ELECTRICAL CHARACTERISTICS (continued)

(Typical Application Circuit, all RF inputs and outputs are referenced to 50, VDD = +3.3V, TA = +25C, fRFIN = 315MHz, unless otherwise noted.) (Note 1)

PARAMETER Noise Figure Power Gain MIXER Input Impedance Input-Referred 3rd-Order Intercept Output Impedance Image Rejection Noise Figure Conversion Gain Input Impedance Operating Frequency RSSI Linearity RSSI Dynamic Range RSSI Level DATA FILTER Maximum Bandwidth DATA SLICER Comparator Bandwidth Maximum Load Capacitance CRYSTAL OSCILLATOR Reference Frequency fREF 4.7547 MHz BWCMP CLOAD 100 10 kHz pF BWDF 100 kHz PRFIN < -120dBm PRFIN > -50dBm ZIN_IF fIF NFMIX 330 IF filter load S11MIX IIP3MIX ZOUT_MIX fRFIN = 315MHz, fRF_IMAGE = 293.6MHz (Note 4) fRFIN = 433.92MHz, fRF_IMAGE = 412.52MHz 40 Normalized to 50 0.25 j2.4 -18 330 53 39 16 13 330 10.7 1 65 1.2 2.0 dBm dB dB dB MHz dB dB V SYMBOL NFLNA CONDITIONS MIN TYP 2.0 16 MAX UNITS dB dB

MAX1470

INTERMEDIATE-FREQUENCY DEMODULATOR BLOCK

Note 1: Parts are production tested at TA = +25C; Min and Max values are guaranteed by design and characterization. Note 2: BER = 2E-3, Manchester encoded, data rate = 4kbps, IF bandwidth = 350kHz. Note 3: Input impedance is measured at the LNAIN pin. Note that the impedance includes the 15nH inductive degeneration connected from the LNASRC. Note 4: Guaranteed by production test.

_______________________________________________________________________________________

315MHz Low-Power, +3V Superheterodyne Receiver MAX1470

Typical Operating Characteristics

(VDD = +3.3V, TA = +25C, unless otherwise noted. Typical Application Circuit.)

SUPPLY CURRENT vs. SUPPLY VOLTAGE

MAX1470 toc01

BIT-ERROR RATE vs. AVERAGE RF INPUT POWER

MAX1470 toc02

RSSI vs. AVERAGE RF INPUT POWER

IF BANDWIDTH = 350kHz 2.0 1.8

MAX1470 toc03

6.1 5.9 SUPPLY CURRENT (mA) 5.7 5.5 5.3 5.1 4.9 4.7 2.7 2.9 3.1 3.3 3.5 SUPPLY VOLTAGE (V) TA = -40C TA = +25C TA = +85C

10

2.2

BIT-ERROR RATE (%)

RSSI (V) -120 -118 -116 -114

1.6 1.4 1.2

0.1 AVERAGE RF INPUT POWER (dBm)

1.0 -140 -120 -100 -80 -60 -40 -20 AVERAGE RF INPUT POWER (dBm)

RECEIVER SENSITIVITY vs. TEMPERATURE

MAX1470 toc04

IMAGE REJECTION vs. TEMPERATURE

MAX1470 toc05

SYSTEM GAIN vs. IF FREQUENCY

FROM RFIN TO MIXOUT fLO = 304.3MHz UPPER SIDEBAND SYSTEM GAIN (dB)

MAX1470 toc06

-116.0 AVERAGE RF INPUT POWER 1% BER IF BANDWIDTH = 350kHz -116.5

60

60 50 40 30 20 10 0 LOWER SIDEBAND 53dB IMAGE REJECTION

RECEIVER SENSITIVITY (dBm)

IMAGE REJECTION (dB)

55

-117.0

50

-117.5

-118.0 -40 -20 0 20 40 60 80 TEMPERATURE (C)

45 -40 -20 0 20 40 60 80 TEMPERATURE (C)

-10 0 10 20 30 IF FREQUENCY (MHz) 40

LNA GAIN vs. RF FREQUENCY

MAX1470 toc07

SUPPLY CURRENT vs. LO FREQUENCY

MAX1470 toc08

INPUT IMPEDANCE vs. INDUCTIVE DEGENERATION

70 60

REAL IMPEDANCE ()

MAX1470 toc09

30 LC TANK FILTER TUNED TO 315MHz 25 LNA GAIN (dB)

7.2 6.7 SUPPLY CURRENT (mA) 6.2 5.7 5.2 4.7

0 -50

50 40 30 20 10 0

REAL IMPEDANCE

-100 -150 -200 -250

20

15

IMAGINARY IMPEDANCE

-300 -350

10 250 275 300 325 350 375 RF FREQUENCY (MHz)

4.2 150 200 250 300 350 400 450 500 LO FREQUENCY (MHz)

10 INDUCTIVE DEGENERATION (nH)

100

_______________________________________________________________________________________

IMAGINARY IMPEDANCE ()

315MHz Low-Power, +3V Superheterodyne Receiver

Typical Operating Characteristics (continued)

(VDD = +3.3V, TA = +25C, unless otherwise noted. Typical Application Circuit.)

NORMALIZED IF GAIN vs. IF FREQUENCY

MAX1470 toc10

MAX1470

IMAGE REJECTION vs. RF FREQUENCY

MAX1470 toc11

5 3dB BANDWIDTH = 11.7MHz NORMALIZED IF GAIN (dB) 0

60

-5

IMAGE REJECTION (dB) 1 10 IF FREQUENCY (MHz) 100

50

40

-10

-15

30

-20

20 150 200 250 300 350 400 450 500 RF FREQUENCY (MHz)

S11 MAGNITUDE-LOG PLOT OF RFIN

MAX1470 toc12

S11 SMITH PLOT OF RFIN

MAX1470 toc13

0dB

315MHz

10dB/ div 315MHz, -29.5dB

50MHz

1GHz 50MHz 1GHz

_______________________________________________________________________________________

315MHz Low-Power, +3V Superheterodyne Receiver MAX1470

Pin Description

PIN 1 2, 7 3 4 5, 10 6 8 9 11, 15, 16, 23, 24 12 13 14 17 18 19 20 21 22 25 26 27 28 NAME XTAL1 AVDD LNAIN LNASRC AGND LNAOUT MIXIN1 MIXIN2 I.C. MIXOUT DGND DVDD IFIN1 IFIN2 DSP DSN OPP DF DATAOUT PDOUT PWRDN XTAL2 1st Crystal Input Positive Analog Supply Voltage for RF Sections. Decouple to AGND with 0.01F capacitors. Low-Noise Amplifier Input Low-Noise Amplifier Source. Connect inductor to ground to set LNA input impedance (see LowNoise Amplifier section). Analog Ground Low-Noise Amplifier Output 1st Differential Mixer Input. Must be AC-coupled to driving input. 2nd Differential Mixer Input. Must be AC-coupled to driving input. Internally Connected. Do not make connection to these pins. 330 Mixer Output Digital Ground Positive Digital Supply Voltage. Decouple to DGND with a 0.01F capacitor. 1st Differential Intermediate Frequency Limiter Amplifier Input 2nd Differential Intermediate Frequency Limiter Amplifier Input Positive Data Slicer Input Negative Data Slicer Input Noninverting Op Amp. Input for the Sallen-Key data filter. Data Filter Feedback Node. Input for the feedback of the Sallen-Key data filter. Digital Baseband Data Output Peak Detector Output Power-Down Select Input. Drive this pin with a logic low to shut down the IC. 2nd Crystal Input FUNCTION

Detailed Description

The MAX1470 CMOS superheterodyne receiver and a few external components provide the complete receive chain from the antenna to the digital output data. Depending on signal power and component selection, data rates as high as 100kbps can be achieved. The MAX1470 is designed to receive binary ASK data on a 315MHz carrier. ASK modulation uses a difference in amplitude of the carrier to represent logic 0 and logic 1 data.

and the LC tank network between the LNA output and the mixer inputs. The off-chip inductive degeneration is achieved by connecting an inductor from LNASRC to AGND. This inductor sets the real part of the input impedance at LNAIN, allowing for a more flexible match for low-input impedance such as a PC board trace antenna. A nominal value for this inductor with a 50 input impedance is 15nH, but is affected by PC board trace. See Typical Operating Characteristics for the relationship between the inductance and input impedance. The LC tank filter connected to LNAOUT comprises L1 and C9 (see Typical Applications Circuit). L1 and C9 values are selected to resonate at the RF input frequency of 315MHz. The resonant frequency is given by:

Low-Noise Amplifier

The LNA is a cascode amplifier with off-chip inductive degeneration that achieves approximately 16dB of power gain with a 2.0dB noise figure and an IIP3 of -18dBm. The gain and noise figure is dependent on both the antenna matching network at the LNA input,

_______________________________________________________________________________________

315MHz Low-Power, +3V Superheterodyne Receiver

= 1 2 L TOTAL CTOTAL To allow the smallest possible IF bandwidth (for best sensitivity), the tolerance of the reference must be minimized. The IF section presents a differential 330 load to provide matching for the off-chip ceramic filter. The internal five AC-coupled limiting amplifiers produce an overall gain of approximately 65dB, with a bandpass-filter-type response centered near the 10.7MHz IF frequency with a 3dB bandwidth of approximately 11.5MHz. The RSSI circuit demodulates the IF to baseband by producing a DC output proportional to the log of the IF signal level with a slope of approximately 15mV/dB (see Typical Operating Characteristics).

MAX1470

Intermediate Frequency

where: L TOTAL = L1+ LPARASITICS CTOTAL = C9 + CPARASITICS LPARASITICS and CPARASITICS include inductance and capacitance of the PC board traces, package pins, mixer input impedance, LNA output impedance, etc. These parasitics at high frequencies cannot be ignored and can have a dramatic effect on the tank filter center frequency. Lab experimentation should be done to optimize the center frequency of the tank.

Applications Information

Crystal Oscillator

The XTAL oscillator in the MAX1470 is designed to present a capacitance of approximately 3pF between XTAL1 and XTAL2. If a crystal designed to oscillate with a different load capacitance is used, the crystal is pulled away from its stated operating frequency, introducing an error in the reference frequency. Crystals designed to operate with higher differential load capacitance always pull the reference frequency higher. For example, a 4.7547MHz crystal designed to operate with a 10pF load capacitance oscillates at 4.7563MHz with the MAX1470, causing the receiver to be tuned to 315.1MHz rather than 315.0MHz, an error of about 100kHz, or 320ppm. In actuality, the oscillator pulls every crystal. The crystals natural frequency is really below its specified frequency, but when loaded with the specified load capacitance, the crystal is pulled and oscillates at its specified frequency. This pulling is already accounted for in the specification of the load capacitance. Additional pulling can be calculated if the electrical parameters of the crystal are known. The frequency pulling is given by: p = Cm 1 1 6 10 2 Ccase + Cload Ccase + Cspec

Mixer

A unique feature of the MAX1470 is the integrated image rejection of the mixer. This device was designed to eliminate the need for a costly front-end SAW filter for many applications. The advantage of not using a SAW filter is increased sensitivity, simplified antenna matching, less board space, and lower cost. The mixer cell is a pair of double-balanced mixers that perform an IQ downconversion of the 315MHz RF input to the 10.7MHz IF with low-side injection (i.e., fLO = fRF - fIF). The image rejection circuit then combines these signals to achieve ~50dB of image rejection over the full temperature range. Low-side injection is required due to the on-chip image-rejection architecture. The IF output is driven by a source-follower, biased to create a driving impedance of 330 to interface with an off-chip 330 ceramic IF filter. The voltage conversion gain driving a 330 load is approximately 13dB.

Phase-Lock Loop

The PLL block contains a phase detector, charge pump/integrated loop filter, VCO, asynchronous 64x clock divider, and crystal oscillator. This PLL does not require any external components. The quadrature VCO is centered at the nominal LO frequency of 304.3MHz. For an input RF frequency of 315MHz, a reference frequency of 4.7547MHz is needed for a 10.7MHz IF frequency (low-side injection is required). The relationship between the RF, IF, and reference frequencies is given by: fREF = (fRF - fIF) / 64

where: fp is the amount the crystal frequency is pulled in ppm. Cm is the motional capacitance of the crystal. Ccase is the case capacitance. Cspec is the specified load capacitance. Cload is the actual load capacitance.

_______________________________________________________________________________________

315MHz Low-Power, +3V Superheterodyne Receiver MAX1470

When the crystal is loaded as specified, i.e., Cload = Cspec, the frequency pulling equals zero.

Data Filter

The data filter is implemented as a 2nd-order lowpass Sallen-Key filter. The pole locations are set by the combination of two on-chip resistors and two external capacitors. Adjusting the value of the external capacitors changes the corner frequency to optimize for different data rates. The corner frequency should be set to approximately 1.5 times the fastest expected data rate from the transmitter. Keeping the corner frequency near the data rate rejects any noise at higher frequencies, resulting in an increase in receiver sensitivity. The configuration shown in Figure 1 can create a Butterworth or Bessel response. The Butterworth filter offers a very flat amplitude response in the passband and a roll-off rate of 40dB/decade for the two-pole filter. The Bessel filter has a linear phase response, which works well for filtering digital data. To calculate the value of C5 and C6, use the following equations along with the coefficients in Table 1: C5 = C6 =

MAX1470

RDF2 100k

RSSI RDF1 100k

19 DSP

21 OPP C6

22 DF C5

Figure 1. Sallen-Key Lowpass Data Filter

Choosing standard capacitor values changes C5 to 470pF and C6 to 220pF, as shown in the Typical Application Circuit.

Data Slicer

The purpose of the data slicer is to take the analog output of the data filter and convert it to a digital signal. This is achieved by using a comparator and comparing the analog input to a threshold voltage. The threshold voltage is set by the voltage on DSN, which is connected to the negative input of the data slicer comparator. The positive input is connected to the output of the data filter internally, and also the DSP pin for use with some data slicer configurations. The suggested data slicer configuration uses a resistor (R1) connected between DSN and DSP with a capacitor (C4) from DSN to DGND (Figure 2). This configuration averages the analog output of the filter and sets the threshold to approximately 50% of that amplitude. With this configuration, the threshold automatically adjusts as the analog signal varies, minimizing the possibility for errors in the digital data. The sizes of R1 and C4 affect how fast the threshold tracks the analog amplitude. Be sure to keep the corner frequency of the RC circuit lower than the lowest expected data rate. Note that a long string of zeros or ones can cause the threshold to drift. This configuration works best if a coding scheme, such as Manchester code, which has an equal number of zeros and ones, is used.

a 100k fc 4 100k fc

)( )( )

)( )( )

where fC is the desired 3dB corner frequency. For example, to choose a Butterworth filter response with a corner frequency of 5kHz: C5 = C6 =

(1.414)(100k)(3.14)(5kHz) (4)(100k)(3.14)(5kHz)

a 1.414 1.3617

1.000

450pF

1.414

225pF

Table 1. Coefficents to Calculate C5 and C6

FILTER TYPE Butterworth (Q = 0.707) Bessel (Q = 0.577) b 1.000 0.618

Peak Detector

The peak detector output (PDOUT), in conjunction with an external RC filter, creates a DC output voltage equal to the peak value of the data signal. The resistor provides a path for the capacitor to discharge, allowing the

_______________________________________________________________________________________

315MHz Low-Power, +3V Superheterodyne Receiver MAX1470

MAX1470

DATA FILTER DATA SLICER 25 DATA OUT C4 20 DSN R1 19 DSP

DATA SLICER

MAX1470

DATA FILTER

25 DATA OUT 47nF

20 DSN 25k

19 DSP 250k

26 PDOUT

47nF

Figure 2. Generating Data Slicer Threshold

Figure 3. Using PDOUT for Faster Startup

peak detector to dynamically follow peak changes of the data filter output voltage. For faster receiver startup, the circuit shown in Figure 3 can be used.

Layout Considerations

A properly designed PC board is an essential part of any RF/microwave circuit. On high-frequency inputs and outputs, use controlled-impedance lines and keep them as short as possible to minimize losses and radiation. At high frequencies, trace lengths that are approximately 1/20 the wavelength or longer become antennas. For example, a 2in trace at 315MHz can act as an antenna. Keeping the traces short also reduces parasitic inductance. Generally, 1in of a PC board trace adds about 20nH of parasitic inductance. The parasitic inductance can have a dramatic effect on the effective inductance. For example, a 0.5in trace connecting a 100nH inductor adds an extra 10nH of inductance or 10%. To reduce the parasitic inductance, use wider traces and a solid ground or power plane below the signal traces. Using a solid ground plane can reduce the parasitic inductance from approximately 20nH/in to 7nH/in. Also, use low-inductance connections to ground on all GND pins, and place decoupling capacitors close to all VDD connections.

433.92MHz Band

The MAX1470 can be configured to receive ASK modulated data with carrier frequency ranging from 250MHz to 500MHz. Only a small number of components need to be changed to retune the RF section to the desired RF frequency. Table 2 shows a list of changed components and their values for a 433.92MHz RF; all other components remain unchanged. The integrated image rejection of the MAX1470 is specifically designed to function with a 315MHz input frequency by attenuating any signal at 293.6MHz. The benefit of the on-chip image rejection is that an external SAW filter is not needed, reducing cost and the insertion loss associated with SAW filters. The image rejection cannot be retuned for different RF input frequencies and therefore is degraded. The image rejection at 433.92MHz is typically 39dB.

Table 2. Changed Component Values for 433.92MHz

COMPONENT C9 L1 L2 Y1 VALUE FOR 433MHz RF 1.0pF 15nH 56nH 6.6128MHz

Chip Information

TRANSISTOR COUNT: 1835 PROCESS: CMOS

Note: These values are affected by PC board layout. _______________________________________________________________________________________ 9

315MHz Low-Power, +3V Superheterodyne Receiver MAX1470

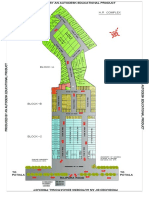

Typical Application Circuit

+3.3V Y1 4.7547MHz

C12 0.01F ANTENNA (RFIN) 1 XTAL1 XTAL2 28

2 C7 100pF L2 100nH 3 L3 15nH 4

AVDD

PWRDN 27

SHUTDOWN

LNAIN

PDOUT 26

LNASRC

DATAOUT 25

+3.3V

L1 27nH

AGND

I.C. 24 DATAOUT

6 C9 2.2pF C11 100pF 8 C2 0.01F 7

LNAOUT

I.C. 23

AVDD

MAX1470

DF 22

MIXIN1

OPP 21 C5 470pF

9 C10 220pF C8 100pF

MIXIN2

DSN 20

10 AGND

DSP 19

11 I.C.

IFIN2 18

C3 1500pF C6 220pF R1 5k C4 0.47F

12 MIXOUT

IFIN1 17

13 DGND

I.C. 16

14 DVDD C1 0.01F U1 10.7MHz

I.C. 15

10

______________________________________________________________________________________

315MHz Low-Power, +3V Superheterodyne Receiver

Pin Configuration

TOP VIEW

XTAL1 1 AVDD 2 LNAIN 3 LNASRC 4 AGND 5 LNAOUT 6 AVDD 7 MIXIN1 8 MIXIN2 9 AGND 10 I.C. 11 MIXOUT 12 DGND 13 DVDD 14 28 XTAL2 27 PWRDN 26 PDOUT 25 DATAOUT 24 I.C.

MAX1470

MAX1470

23 I.C. 22 DF 21 OPP 20 DSN 19 DSP 18 IFIN2 17 IFIN1 16 I.C. 15 I.C.

TSSOP

______________________________________________________________________________________

11

315MHz Low-Power, +3V Superheterodyne Receiver MAX1470

Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to www.maxim-ic.com/packages.)

TSSOP4.40mm.EPS

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

12 ____________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 2002 Maxim Integrated Products Printed USA is a registered trademark of Maxim Integrated Products.

Вам также может понравиться

- Spf5189z Data SheetДокумент11 страницSpf5189z Data SheetAparna BhardwajОценок пока нет

- 154XX, 354XX, 1034XXДокумент9 страниц154XX, 354XX, 1034XXmc_aeprОценок пока нет

- 40G QSFP+ PSM IR4 SOQP-3140-01 From SinovoДокумент16 страниц40G QSFP+ PSM IR4 SOQP-3140-01 From SinovomelissaОценок пока нет

- DataSheet Amplificador - RFPA0133DSДокумент9 страницDataSheet Amplificador - RFPA0133DSMariane Antonio de OliveiraОценок пока нет

- AD831-MIXER 200-500MHzДокумент17 страницAD831-MIXER 200-500MHzChelaru CosminОценок пока нет

- 4MSPS, 24-Bit Analog-to-Digital Converter: Features DescriptionДокумент37 страниц4MSPS, 24-Bit Analog-to-Digital Converter: Features DescriptionEric ChenОценок пока нет

- Features Descriptio: Lt5517 40Mhz To 900Mhz Quadrature DemodulatorДокумент12 страницFeatures Descriptio: Lt5517 40Mhz To 900Mhz Quadrature DemodulatorchunnumunnuОценок пока нет

- DatasheetДокумент8 страницDatasheetgijiskariaОценок пока нет

- TX2RX2 0202Документ15 страницTX2RX2 0202claudinei_verissimo8529Оценок пока нет

- SPF 5189zdsДокумент10 страницSPF 5189zdsAparna BhardwajОценок пока нет

- 300Mhz-To-450Mhz Low-Power, Crystal-Based Ask Transmitter: General Description FeaturesДокумент9 страниц300Mhz-To-450Mhz Low-Power, Crystal-Based Ask Transmitter: General Description FeaturesCostel DiaconuОценок пока нет

- Remote Control and Security Systems Hybrids - Ver.2: TelecontrolliДокумент37 страницRemote Control and Security Systems Hybrids - Ver.2: TelecontrolliSixto AgueroОценок пока нет

- Features Descriptio: Ltc1566-1 Low Noise 2.3Mhz Continuous Time Lowpass FilterДокумент8 страницFeatures Descriptio: Ltc1566-1 Low Noise 2.3Mhz Continuous Time Lowpass Filtergiapy0000Оценок пока нет

- 13.56Mhz Rfid Transceiver: (1) Ratp / Innovatron TechnologyДокумент25 страниц13.56Mhz Rfid Transceiver: (1) Ratp / Innovatron TechnologyorlandomaskОценок пока нет

- Ad6190 900 MHZ RF TransceiverДокумент9 страницAd6190 900 MHZ RF TransceivermgferreyraОценок пока нет

- Features Description: LTC2368-16 16-Bit, 1Msps, Pseudo-Differential Unipolar SAR ADC With 94.7dB SNRДокумент24 страницыFeatures Description: LTC2368-16 16-Bit, 1Msps, Pseudo-Differential Unipolar SAR ADC With 94.7dB SNRrotenolabsОценок пока нет

- 9-0-9 Step Down TransformerДокумент20 страниц9-0-9 Step Down TransformerSarthak JoshiОценок пока нет

- Receptor IR TSOP4836Документ7 страницReceptor IR TSOP4836damijoseОценок пока нет

- D7088 تكبيراشارةFM PDFДокумент9 страницD7088 تكبيراشارةFM PDFmzn_comОценок пока нет

- AD831Документ16 страницAD831Vicent Ortiz GonzalezОценок пока нет

- FДокумент24 страницыFrotenolabsОценок пока нет

- Max038 Generador de FuncionesДокумент17 страницMax038 Generador de FuncionesLuis Rodolfo Reyes JimenezОценок пока нет

- 3963 Sirenza-Microdevices SHF-0186K 01Документ4 страницы3963 Sirenza-Microdevices SHF-0186K 01TalОценок пока нет

- Dual-Band Gsm900/Dcs1800 Transmit: OUT OUTДокумент16 страницDual-Band Gsm900/Dcs1800 Transmit: OUT OUTBudi PrastyoОценок пока нет

- Radiometrix: UHF FM Data Transmitter and Receiver ModulesДокумент15 страницRadiometrix: UHF FM Data Transmitter and Receiver ModulesMehadi Alom ChoudhuryОценок пока нет

- RFM12BДокумент10 страницRFM12BLeonardo Gonzales JaraОценок пока нет

- CF750Документ9 страницCF750Shilpi VirmaniОценок пока нет

- RF & Microwave Discrete Low Power Transistors: FeaturesДокумент5 страницRF & Microwave Discrete Low Power Transistors: FeaturesMassimo MaestraleОценок пока нет

- Max 1472Документ9 страницMax 1472Eugenio J. MedinaОценок пока нет

- Paradise Datacom Mini-Redundant SSPA 209495 RevAДокумент8 страницParadise Datacom Mini-Redundant SSPA 209495 RevAarzeszutОценок пока нет

- DRF4432F20Документ6 страницDRF4432F20Ilie CristianОценок пока нет

- Cmos, 240 MHZ Triple 10-Bit High Speed Video Dac: 8C To +858C) 3 1200 at 100 HZ)Документ16 страницCmos, 240 MHZ Triple 10-Bit High Speed Video Dac: 8C To +858C) 3 1200 at 100 HZ)toilatoi2011Оценок пока нет

- OPA380 OPA2380: Features DescriptionДокумент23 страницыOPA380 OPA2380: Features DescriptionSunny SharmaОценок пока нет

- TSOP322.., TSOP324.., TSOP348.., TSOP344..: Vishay SemiconductorsДокумент7 страницTSOP322.., TSOP324.., TSOP348.., TSOP344..: Vishay SemiconductorsDiego SánchezОценок пока нет

- Rfpa3800 Data Sheet PDFДокумент12 страницRfpa3800 Data Sheet PDFmohamedОценок пока нет

- TLC 5540Документ18 страницTLC 5540EdgarJCОценок пока нет

- Nrf24l01 2.4ghz Wireless Transceiver Module ManualДокумент43 страницыNrf24l01 2.4ghz Wireless Transceiver Module ManualmuassegafОценок пока нет

- Product Features Product Description Functional Diagram: High Dynamic Range FETДокумент7 страницProduct Features Product Description Functional Diagram: High Dynamic Range FETVinod DawraОценок пока нет

- Features:: OFS-1303-20 Blank Without DDM X D With DDMДокумент6 страницFeatures:: OFS-1303-20 Blank Without DDM X D With DDMShaheel HawseeaОценок пока нет

- QUAD-BAND GSM850/EGSM900/DCS1800/ Pcs1900 Transmit Module: Package: Module 6.63mmx5.24mm1.0mmДокумент20 страницQUAD-BAND GSM850/EGSM900/DCS1800/ Pcs1900 Transmit Module: Package: Module 6.63mmx5.24mm1.0mmVasireddy AnudeepОценок пока нет

- Descriptio: FeaturesДокумент12 страницDescriptio: FeaturesgdfsndhgfdvhjzdОценок пока нет

- BTM182Документ6 страницBTM182jmsosanОценок пока нет

- 800 MHZ, 50 MW Current Feedback Amplifier:, G +2) Differential Phase ErrorДокумент16 страниц800 MHZ, 50 MW Current Feedback Amplifier:, G +2) Differential Phase Errorzef1Оценок пока нет

- Ads 7824Документ21 страницаAds 7824Andres Alberto Meza BrocheroОценок пока нет

- Cy520 Datasheet: 300M-450Mhz Ask ReceiverДокумент17 страницCy520 Datasheet: 300M-450Mhz Ask ReceiverMadhusudanan AshokОценок пока нет

- MRF6S18100Документ20 страницMRF6S18100Nguyen Van CuongОценок пока нет

- MAX038Документ17 страницMAX038Brane PetkoskiОценок пока нет

- SFP+ 10Gbps BiDi TX1270RX1330nm 40KMДокумент7 страницSFP+ 10Gbps BiDi TX1270RX1330nm 40KMpeng chenОценок пока нет

- Circuit Diagram of RC Transmitter and ReceiverДокумент6 страницCircuit Diagram of RC Transmitter and ReceivernicoletabytaxОценок пока нет

- 1.6 GHZ Differential Wideband Silicon Rfic Amplifier UPC2726TДокумент4 страницы1.6 GHZ Differential Wideband Silicon Rfic Amplifier UPC2726Tmancys2000Оценок пока нет

- ADF4110/ADF4111/ADF4112/ADF4113 RF PLL Frequency SynthesizersДокумент24 страницыADF4110/ADF4111/ADF4112/ADF4113 RF PLL Frequency SynthesizersMichael LiuОценок пока нет

- XGSW XX12 40D FДокумент9 страницXGSW XX12 40D FnelusabieОценок пока нет

- HPMX 3002Документ9 страницHPMX 3002sri kalyanОценок пока нет

- Ads 7825Документ21 страницаAds 7825geo888007Оценок пока нет

- DS8500Документ7 страницDS8500abdulmajeed_cetОценок пока нет

- 1915 LMM 40km WDMДокумент5 страниц1915 LMM 40km WDMwattanayimpearОценок пока нет

- FMT M - Fmtx1-Xxxx: Ransmitter OdulesДокумент6 страницFMT M - Fmtx1-Xxxx: Ransmitter Odulesinsomnium86Оценок пока нет

- MRF 5 S 9100 NДокумент16 страницMRF 5 S 9100 NpankajОценок пока нет

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsОт EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsОценок пока нет

- ATSC Digital Television Standard, Part 6 - Enhanced AC-3 Audio System CharacteristicsДокумент28 страницATSC Digital Television Standard, Part 6 - Enhanced AC-3 Audio System CharacteristicsJ Jesús Villanueva GarcíaОценок пока нет

- Vol1no2 3Документ9 страницVol1no2 3J Jesús Villanueva GarcíaОценок пока нет

- Epfl TH4771Документ157 страницEpfl TH4771J Jesús Villanueva GarcíaОценок пока нет

- ReadmefsdfДокумент1 страницаReadmefsdfalejandro_ledesma_15Оценок пока нет

- Math WorksДокумент53 страницыMath WorksJ Jesús Villanueva GarcíaОценок пока нет

- For (I 0 I 100 I++) (Suml Suml + - Mpy (A (I), B (I) ) Sumh Sumh + - Mpyh (A (I), B (I) ) ) Return (Suml + Sumh)Документ1 страницаFor (I 0 I 100 I++) (Suml Suml + - Mpy (A (I), B (I) ) Sumh Sumh + - Mpyh (A (I), B (I) ) ) Return (Suml + Sumh)J Jesús Villanueva GarcíaОценок пока нет

- Robert Gallager LDPC 1963Документ90 страницRobert Gallager LDPC 1963Thao ChipОценок пока нет

- Heat Equation Solution Using Fourier TransformДокумент2 страницыHeat Equation Solution Using Fourier TransformRakesh KamathОценок пока нет

- Bjorlin OAA 2004Документ3 страницыBjorlin OAA 2004J Jesús Villanueva GarcíaОценок пока нет

- Isc12 Opamppllsynth SLДокумент30 страницIsc12 Opamppllsynth SLJ Jesús Villanueva GarcíaОценок пока нет

- Information Theory and Statistics - A TutorialДокумент116 страницInformation Theory and Statistics - A Tutorialnmobin27100% (1)

- (2004) The Harris Corner DetectorДокумент2 страницы(2004) The Harris Corner DetectorJ Jesús Villanueva GarcíaОценок пока нет

- Algebraic Methods To Compute Mathieu Functions - FrenkelДокумент11 страницAlgebraic Methods To Compute Mathieu Functions - FrenkelJ Jesús Villanueva GarcíaОценок пока нет

- 16056876Документ6 страниц16056876J Jesús Villanueva GarcíaОценок пока нет

- Elg5163 PDCДокумент2 страницыElg5163 PDCJ Jesús Villanueva GarcíaОценок пока нет

- Optical Antennas: Palash Bharadwaj, Bradley Deutsch, and Lukas NovotnyДокумент46 страницOptical Antennas: Palash Bharadwaj, Bradley Deutsch, and Lukas NovotnyArmand Girard-NoyerОценок пока нет

- Radio Over Fiber Technology For Wireless AccessДокумент6 страницRadio Over Fiber Technology For Wireless AccessAnuj Pathak BallanОценок пока нет

- 194149Документ59 страниц194149J Jesús Villanueva GarcíaОценок пока нет

- Progress in Electromagnetics Research B, Vol. 44, 191-221, 2012Документ31 страницаProgress in Electromagnetics Research B, Vol. 44, 191-221, 2012J Jesús Villanueva GarcíaОценок пока нет

- Digital Signal Processing List of Transforms: Coursera - February 2013Документ2 страницыDigital Signal Processing List of Transforms: Coursera - February 2013Soumyajit DasОценок пока нет

- Numpy ReferenceДокумент1 413 страницNumpy Referencepagol_23_smhОценок пока нет

- 111Документ6 страниц111J Jesús Villanueva GarcíaОценок пока нет

- 205639Документ52 страницы205639J Jesús Villanueva GarcíaОценок пока нет

- TurboДокумент10 страницTurboAlireza MovahedianОценок пока нет

- On BCFW Shifts of Integrands and IntegralsДокумент43 страницыOn BCFW Shifts of Integrands and IntegralsJ Jesús Villanueva GarcíaОценок пока нет

- Twistor Theory of Higher-Dimensional Black Holes: Norman MetznerДокумент127 страницTwistor Theory of Higher-Dimensional Black Holes: Norman MetznerJ Jesús Villanueva GarcíaОценок пока нет

- Bello Orgaz GemaДокумент45 страницBello Orgaz GemaJ Jesús Villanueva GarcíaОценок пока нет

- Vol1no2 3Документ9 страницVol1no2 3J Jesús Villanueva GarcíaОценок пока нет

- 1203 5181Документ31 страница1203 5181J Jesús Villanueva GarcíaОценок пока нет

- Eee21 Probset4Документ4 страницыEee21 Probset4wafu017Оценок пока нет

- Tu 8200 Manual EnglishДокумент20 страницTu 8200 Manual EnglishZymaflor88% (8)

- MAG5000 Manual PDFДокумент98 страницMAG5000 Manual PDFphucОценок пока нет

- ProCash 2150xe PDFДокумент2 страницыProCash 2150xe PDFemrouz67% (3)

- RFSoC Evaluation Tool User GuideДокумент71 страницаRFSoC Evaluation Tool User GuideBismillah Nasir IshfaqОценок пока нет

- CMC Database Integrity Declaration (DID) CMCE 1510 03Документ1 страницаCMC Database Integrity Declaration (DID) CMCE 1510 03Mohd ShahОценок пока нет

- Toshiba Satellite E55 ZRMAA Compal LA-A481P Rev1.0 SchematicДокумент55 страницToshiba Satellite E55 ZRMAA Compal LA-A481P Rev1.0 SchematicdataОценок пока нет

- DC ServoДокумент17 страницDC ServoMuhammad Iqbal ZahidОценок пока нет

- TRIMA Service ManualДокумент52 страницыTRIMA Service ManualUku KukrusОценок пока нет

- Semester 1 - PPT'sДокумент237 страницSemester 1 - PPT'sSanjay GomastaОценок пока нет

- Substation Construction Project. Project ScheduleДокумент12 страницSubstation Construction Project. Project ScheduleBishnu Chapagai50% (2)

- Mri Devices Corporation: Technical ReportДокумент6 страницMri Devices Corporation: Technical ReportRogerio CastroОценок пока нет

- David EsseiniДокумент10 страницDavid Esseiniশুভ MitraОценок пока нет

- VTX A8 Specsheet - 5108391-00CДокумент3 страницыVTX A8 Specsheet - 5108391-00CIvan UzunovОценок пока нет

- Bridgewater HallДокумент4 страницыBridgewater HallHuzaifa J AhmedabadwalaОценок пока нет

- The Open Systems Interconnection (OSI) Model and Network ProtocolsДокумент148 страницThe Open Systems Interconnection (OSI) Model and Network Protocolswfidayu100% (1)

- Small Welder For Joining Nichrome and Nickel WiresДокумент7 страницSmall Welder For Joining Nichrome and Nickel WiresJulio_Cesar1981Оценок пока нет

- H.R Complex: Rajpura Road TO Patiala TO PatialaДокумент1 страницаH.R Complex: Rajpura Road TO Patiala TO Patialaprabhjeet singh antalОценок пока нет

- Pca 6003Документ1 страницаPca 6003drmnsyhОценок пока нет

- Wa0020.Документ16 страницWa0020.Giri DharanОценок пока нет

- MURS320T3G, SURS8320T3G, MURS340T3G, SURS8340T3G, MURS360T3G, SURS8360T3G Surface Mount Ultrafast Power RectifiersДокумент6 страницMURS320T3G, SURS8320T3G, MURS340T3G, SURS8340T3G, MURS360T3G, SURS8360T3G Surface Mount Ultrafast Power RectifiersBaskoro SutrisnoОценок пока нет

- Babu Banarasi Das National Institute of Technology and Management LucknowДокумент11 страницBabu Banarasi Das National Institute of Technology and Management LucknowPrajjwalKumarОценок пока нет

- Control SystemДокумент23 страницыControl SystemSudip BanikОценок пока нет

- Whirlpool ADG6550 IxДокумент17 страницWhirlpool ADG6550 Ixairwolf4226100% (1)

- Amted310010en WebДокумент120 страницAmted310010en WebMemo TipОценок пока нет

- Hall Effect PDFДокумент6 страницHall Effect PDFVenugopal Reddyvari0% (1)

- The Periodic TableДокумент123 страницыThe Periodic TableFatema KhatunОценок пока нет

- UT Dallas Syllabus For Ee3310.001.11s Taught by William Frensley (Frensley)Документ6 страницUT Dallas Syllabus For Ee3310.001.11s Taught by William Frensley (Frensley)UT Dallas Provost's Technology GroupОценок пока нет

- Intake System: Parts LocationДокумент7 страницIntake System: Parts LocationMenzie Peter RefolОценок пока нет