Академический Документы

Профессиональный Документы

Культура Документы

Solns 6

Загружено:

ramprakash_rampelliИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Solns 6

Загружено:

ramprakash_rampelliАвторское право:

Доступные форматы

6.

1)

Plot the magnitude and phase of vout (AC) in the following circuit, Fig. 6.20. Assume that the MOSFET was fabricated using the 50nm process (see Table 5.1) and is operating in strong inversion. Verify your answer with SPICE.

1mV (AC)

Sol: - From Fig. 6.20

250k 500mV

vout

W=L=100

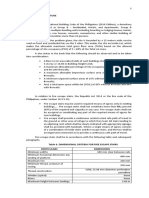

MOSFET is operating in strong inversion region and source, drain and body are connected to ground (body connection not shown). The device acts as MOSCAP, value of this capacitance can be calculated with the help of table 5.1 for 50nm process. C total = Cox WL = 25fF/m2 (10050nm) (10050nm) = 25fF/ m2 25 m2; C total = 625fF For 1mV AC input the circuit functions as low pass RC circuit with voltage divider equation given as : 1 j 2 fCtotal Vout = Vin R+ 1 j 2 fCtotal Vin = ; 1 + j 2 fRC total

Vout =

Vin 1 + (2 fRCtotal )

2

1 ; Vout = tan ( 2 fRCtotal )

3db frequency for this case will be

f3db =

1 1MHz thus simulating the circuit from 2 RCtotal

frequency of 1 kHz to 100MHz

In the above simulation plot we can see the RC response of the circuit. The magnitude plot is at approximately -60 db due to the fact that Vin taken as 1mV which will be equal to -60db. Also at the 1MHz the phase is approximately 45 and magnitude around -63db.

-Shantanu Gupta

Problem 6.2

Rupa Balan

If a MOSFET is used as a capacitor in the strong inversion region where the gate is one electrode and the source/drain is the other electrode, does the gate overlap of the source/drain change the capacitance? Why? What is the capacitance? Solution:- In the strong inversion region, the channel of electrons is formed below the gate oxide in case of NMOS shorting the drain and the source. Since source and drain of NMOS are shorted through channel of electrons, gate overlap of source/drain does not change the gate to source/drain capacitance. Capacitance between gate and source/drain =Cox=Cox. W. L. (scale)2 where W=Wdrawn and L=Ldrawn.

Problem 6.3

Krishna Duvvada

Repeat problem 6.2 when the MOSFET is operating in the accumulation region. Keep in mind that the question is not asking for the capacitance from gate to substrate. Solution:- When the MOSFET operates in the accumulation region, the gate overlap capacitance affects the capacitance from gate to source/drain. Here the drain and source is separated by the substrate which is the resistance. So the gate to drain/source capacitance is the overlap capacitance. Cgs = Cox. Ldiff. W (scale)2

Problem 6.4

Surendranath C Eruvuru

If the oxide thickness of a MOSFET is 40 Ao. What is Cox? Solution:- Cox = ox/Tox = (8.85 x 3.97 aF/m)/(40 x 10-10 m) = 8.784 fF/m2

KRISHNAMRAJU KURRA Problem 6.5. Repeat Ex: 6.5 to get a threshold voltage of 0.8V. Solution: Given Then Where VGS = VTHN and VSB = 1V

VS = - Vfp + VSB Vfp = -(KT/q) ln ( NA/ni) = -26 mV* ln [1015 (atoms/cm3) / 1.45* 1010 (atoms/cm3) ] = -290mV

We have =

Xd =

[2 si 2V fp + VSB / qN A

18 2 19

[2 11.7 8.85 10 (F / m ) ( 2 .29) + 1V / (1.6 10

= 1.43 m Qbo = q NA Xd

(C / atom ))1015 (atoms / cm3 )(cm3 / 1012 m3 )]

We have

= 1.6 10 19 (C / atom ) 1015 atoms / cm3 cm3 / 1012 m3 1.43 m = 229 aC/ m 2

)(

PROBLEM 6.6

Indira Priyadarshini.Vemula

Repeat Ex. 6.3 for a p-channel device with a well doping concentration of 1016 atoms/cm3? Solution: Given ND=1016 atom/cm3 =(2qsi ND)1/2/Cox =(2*1.6*10-19 C/atom*11.7*8.85 aF/um2*1016 atom/cm3 * cm3/1012 um2)1/2 1.75 fF/um2 =0.328V1/2

Problem 6.7

MESHACK P. APPIKATLA

What is the electrostatic potential of the oxide-semiconductor interface when VGS=VTHNO. Solution: It will be equal and opposite to the electrostatic potential of the substrate. Vs = -Vfp Where Vs is the electrostatic potential of the interface and Vfp is the electrostatic potential of the substrate.

Problem 6.8

Edward Kunz

Estimate the ion implant dose required to change the threshold voltage in Ex. 6.4 without Sodium contamination, to 0.8v. Solution: Using values from Ex. 6.4

VTHNO = 0.220v+ qN I = 0.8v C 'OX

C ' OX = 1.75 fF

m 2

atom 1.6*1019 C *N atom I 0.8v = 0.220v+ 1.75 fF 2 m N I = 1.115 * 1012 atoms 2 cm

q = 1.6 *10 19 C

Problem 6.9

Vinay Dindi

What happens to the threshold voltage in Problem 6.8 if sodium contamination of 100e9 sodium ions/cm2 is present at the oxide-semiconductor interface? Solution: Given Ni=100E+9 atoms/cm2=1000 atoms/um2 From E.q (6.22) and (6.23) and the results from Ex.6.4 Vthno= -220mv - qNs/C`ox + qNi/C`ox From Prob 6.8), we know 220mv + qNi/C`ox=0.8 So, Vthno with sodium contamination= 0.8 (1.6E-19*1000/1.75fF)= 0.7

Problem 6.10

Satish Dulam

How much charge (enhanced electrons) is available under the gate for conducting a drain current at the drain-channel interface when Vds = Vgs Vthn? Why? Assume the MOSFET is operating in strong inversion, Vgs > Vthn. Solution: In Strong inversion, the amount of charge present at any point in the channel is given by Eq 6.28. At the drain, V(y) is equal to Vds. Given that Vds is Vgs-Vthn. From Eq 6.28, the charge at the drain is zero. When the drain and source are held at ground and the gate voltage is greater than the Vthn, the MOS is already in strong inversion and the channel is uniform along the y-direction. As the drain voltage is increased, the positive voltage at the drain is removing the electrons from the inverted channel. When the drain voltage reaches (Vgs-Vthn), the net charge present at the drain is zero.

Problem 6.11 Show the details of the derivation for Eq. (6.33) for the PMOS device.

Rahul Mhatre

Solution: Since the device is a PMOS MOSFET, source and drain are p+ regions and the substrate is an nwell. Therefore, all the bulk is the most positive terminal and source is more positive than drain and gate. We follow the voltage convention of Figure 6.1 in the book. Also, the threshold for PMOS device (VTHP) is a negative quantity.

Consider the Figure 6.11, where VSG > |VTHP|, so that the surface under the oxide is inverted and VSD > 0, causing a drift current to flow from the source to the drain.

VBS

VSG Gate

VSD

Source FOX n+ p+ V(y) y p+

Drain

FOX

Body

y+dy

n-well

p-substrate

Figure 6.11 Calculation of large-signal behavior of the PMOS MOSFET in the triode region

V(y) is the channel voltage with respect to the source of the PMOS (a negative quantity) at a distance y away from the source. The potential difference between the Gate electrode and the channel is VSG V(y). The charge/unit area in the inversion layer is given by Qch = Cox. [VSG - V(y) ] Eq (6.1)

Charge Qb (holes) is present in the inversion layer from the application of the threshold voltage, VTHP, necessary for conduction between the drain and source. This charge is given by, Qb = Cox. |VTHP| Eq(6.2)

The total charge available in the channel, for conduction of a current between the source and the drain, is given by the difference between Equation (6.1) and Equation (6.2), which is QI(y)= Cox. [ VSG - V(y) - |VTHP|] where is the charge in the inverted channel. The differential resistance of the channel region with a length dy and a width W is given by, dR =( 1/ p QI(y) ) .dy/W Eq(6.4) Eq(6.3)

where p is the average hole mobility through the channel with units cm2/V.sec. The differential voltage drop across this differential resistance is given by dV(y) = ID . dR = ID . dy / (W p QI(y) ) Substituting Equation (6.) and rearranging ID . dy = W p Cox. [ VSG - V(y) - |VTHP|] . dV(y) We define the transconductance of the PMOS MOSFET as, KPp = p Cox = p ox / tox Eq(6.7) Eq(6.6) Eq(6.5)

The current can be found by integrating the left side of Equation (6.6) from source to drain, that is from 0 to L and the right side from 0 to VSD. This current flows from source to drain. This is as shown below: ID . 0L dy = W KPp 0 VSD [ VSG - V(y) - |VTHP|] . dV(y) ID = KPp (W/L) [ (VSG - |VTHP|) VSD (VSD2/ 2) ] for VSG>|VTHP| and VSDVSG - |VTHP| This current flows from Source to drain. Eq(6.8) Eq(6.9)

Problem 6.12

John Spratt

Using Eq. (6.35) estimate the small-signal channel resistance (the change in the drain current with changes in the drain-source voltage) of a MOSFET operating in the triode region (the resistance between the drain and source. Solution: Eq 6.35: ID=*[(Vgs-Vthn)Vds-Vds2/2]

r = Vds /ID = (Vds1- Vds2) / [(*[(Vgs-Vthn)*( Vds1)-( Vds1) 2/2]- *[(Vgs-Vthn)*( Vds2)-( Vds2)2/2]] = (Vds1- Vds2) / [(*[(Vgs-Vthn)*( Vds1- Vds2)-( Vds1)2/2+( Vds2)2/2]] =1 / [(*[(Vgs-Vthn)-( Vds1+ Vds2)/2]] r =1 / [*(Vgs-Vthn- Vds)]

Problem 6.13

Steve Bard

Question: Show, using Eqs. 6.33 and 6.37, that the parallel connection of MOSFETs shown in Fig. 5.18 behaves as a single MOSFET with a width equal to the sum of the individual MOSFETs widths.

Id D G Id1 Id2 Id3 Id4

Equivalent of Fig. 5.18 Solution: From Kirchoffs Current Law, we know that Id = Id1 + Id2 + Id3 + Id4. So if each MOSFET has the same KP, L, VGS, VDS and VTHN, equations 6.33 and 6.37 become:

2 W1 + W 2 + W 3 + W 4 VDS (VGS VTHN )VDS Id = KPn 2 L

for Eq. 6.33

Id = KPn

W1 + W 2 + W 3 + W 4 2 (VGS VTHN ) L

for Eq. 6.37

This shows that the total drain current, Id, is equal to a single MOSFET with a width equal to W1 + W2 + W3 + W4.

Problem 6.14

Shambhu Roy

Show that the bottom MOSFET. Fig 6.21. in a series connection of two MOSFETs cannot operate in the saturation region. Neglect the body effect. Hint: Show that M1 is always in either cutoff ( VGS1 < VTHN ) or triode ( V DS1` < VGS 1 VTHN ).

M2

W L1 + W Vds1 L1 -

Vgs2 Vgs1 M1

Solution:

For VGS1 < VTHN both MOSFETs are in the cutoff region. When VGS1 > VTHN V DS1 = VGS 1 VGS 2 Also V DS1 VGS 1 VTHN

VGS1 VGS 2 VGS1 VTHN VGS 2 < VTHN Which cannot be true, therefore if top MOSFET has to operate then the bottom MOSFET cannot be in Saturation.

Problem 6.15

Harish Reddy Singidi

Show that the series connection of MOSFETs shown in fig. 6.21 behaves as a single MOSFET with Twice the length of the individual MOSFETs. Again neglect the body effect. Solution: VD2 M2 VD2 VG W/L2 VG V1 W/(L1+L2) M1 W/L1

Assuming both MOSFETs are in triode region For M1 ID1 = ID ID1 = ID = KPn (W/L1) [(VG VTHN)V1- V12/2] (ID L1)/ (KPn W) = [(VG VTHN)V1- V12/2] As Both MOSFETs are in series i.e., ID1 = ID2 = ID For M2 ID2 = ID ID2 = ID = KPn (W/L2) [(VG V1 - VTHN)(VD2-V1) - (VD2-V1) 2/2] (ID L2)/ (KPn W) = [(VG V1 - VTHN)(VD2-V1) - (VD2-V1) 2/2] [(ID L1)/ (KPn W)] + [(ID L2)/ (KPn W)] = [(VG VTHN)V1- V12/2] + [(VG V1 - VTHN)(VD2-V1) (VD2-V1) 2/2] [(ID (L1+L2)/ (KPn W)] = [(VG VTHN) VD2 - (VD2) 2/2] This is the current from drain to source for a single MOSFET with length (L1+L2) If L1= L2 = L [(2ID L)/ (KPn W)] = [(VG VTHN) VD2 - (VD2) 2/2] ID = [(KPn W)/2L] [(VG VTHN) VD2 - (VD2) 2/2]

Вам также может понравиться

- BJT Diff AmplifierДокумент15 страницBJT Diff AmplifierAdrià Amézaga SàrriesОценок пока нет

- 688 (I) Hunter-Killer - User ManualДокумент115 страниц688 (I) Hunter-Killer - User ManualAndrea Rossi Patria100% (2)

- July 2014 GEARSДокумент76 страницJuly 2014 GEARSRodger BlandОценок пока нет

- Layers of The EarthДокумент26 страницLayers of The EarthLoo DrBrad100% (1)

- Dynamic Logic Circuits: Kang and Leblebicic, Chapter 9Документ34 страницыDynamic Logic Circuits: Kang and Leblebicic, Chapter 9Lovey SalujaОценок пока нет

- DP 900T00A ENU TrainerHandbookДокумент288 страницDP 900T00A ENU TrainerHandbookAndré baungatnerОценок пока нет

- Solns 9Документ66 страницSolns 9ramprakash_rampelliОценок пока нет

- Transient Thermal Conduction ExampleДокумент14 страницTransient Thermal Conduction ExampleDevendra BangarОценок пока нет

- DOST-ASTI Electric Manual PDFДокумент17 страницDOST-ASTI Electric Manual PDFJB NavarroОценок пока нет

- Neal Peres Da CostaДокумент507 страницNeal Peres Da CostaNoMoPoMo576100% (1)

- Chapter SixДокумент5 страницChapter Sixyunus memonОценок пока нет

- Layout 02Документ38 страницLayout 02Bulcea PaulОценок пока нет

- Voltage Reference 23Документ25 страницVoltage Reference 23api-3750190Оценок пока нет

- 4 Bit DacДокумент4 страницы4 Bit DacG Lokesh100% (1)

- Chap16-Analog Integrated CircuitsДокумент55 страницChap16-Analog Integrated CircuitsMạnh Cường TrầnОценок пока нет

- Solns - 1 CmosДокумент15 страницSolns - 1 Cmosramprakash_rampelliОценок пока нет

- Solns - 1 CmosДокумент15 страницSolns - 1 Cmosramprakash_rampelliОценок пока нет

- Solns 4Документ14 страницSolns 4ramprakash_rampelliОценок пока нет

- Solns 4Документ14 страницSolns 4ramprakash_rampelliОценок пока нет

- Cmos LayoutДокумент13 страницCmos LayoutshastryОценок пока нет

- Human Resource Development Multiple Choice Question (GuruKpo)Документ4 страницыHuman Resource Development Multiple Choice Question (GuruKpo)GuruKPO90% (20)

- Solucionario CAP 5 RAZAVIДокумент112 страницSolucionario CAP 5 RAZAVIBenjaminJimenezОценок пока нет

- A Research Paper On DormitoriesДокумент5 страницA Research Paper On DormitoriesNicholas Ivy EscaloОценок пока нет

- Gate Questions On MosfetДокумент16 страницGate Questions On MosfetEsakkiPonniah100% (1)

- Module 5Документ16 страницModule 5Raja ShekarОценок пока нет

- DC-DC ConverterДокумент24 страницыDC-DC ConverterkandularanjithОценок пока нет

- Solns 3cmosДокумент16 страницSolns 3cmosramprakash_rampelliОценок пока нет

- Solns 2cmosДокумент18 страницSolns 2cmosramprakash_rampelliОценок пока нет

- Solns 2cmosДокумент18 страницSolns 2cmosramprakash_rampelliОценок пока нет

- Solution:: C CEO E COДокумент19 страницSolution:: C CEO E COShiela Monique FajardoОценок пока нет

- Solns 29Документ102 страницыSolns 29ramprakash_rampelliОценок пока нет

- Solns 29Документ102 страницыSolns 29ramprakash_rampelliОценок пока нет

- Solns - 5 CmosДокумент12 страницSolns - 5 Cmosramprakash_rampelli100% (1)

- Sheet 3 - SolutionДокумент10 страницSheet 3 - SolutionMajid HelmyОценок пока нет

- Ler para CCIДокумент114 страницLer para CCIjonas1446Оценок пока нет

- Network Selected QuestionsДокумент13 страницNetwork Selected Questionsmisho_16100% (1)

- Amplifiers 21Документ57 страницAmplifiers 21api-3750190Оценок пока нет

- Basic VLSI SlidesДокумент91 страницаBasic VLSI SlidesDivya AhujaОценок пока нет

- Opamp 24Документ111 страницOpamp 24api-3750190Оценок пока нет

- Solns 22 DiffAmp BakerДокумент57 страницSolns 22 DiffAmp BakerHarry MadaanОценок пока нет

- Switch CapacitorДокумент90 страницSwitch CapacitorVaibhav Khurana100% (1)

- Chenming Hu Ch5Документ38 страницChenming Hu Ch5chhote19100% (1)

- VLSI Problems of Chapter 3Документ5 страницVLSI Problems of Chapter 3Ahsan MoinОценок пока нет

- Current Mirrors 20Документ45 страницCurrent Mirrors 20api-3750190Оценок пока нет

- Assignment 1Документ9 страницAssignment 1Taslima Rahman MiliОценок пока нет

- Mosfet SummaryДокумент1 страницаMosfet SummarybofshafiqueОценок пока нет

- ECE 4141-Experiment 3 - CMOS NAND Transistors Sizing Simulation Using PSPICEДокумент6 страницECE 4141-Experiment 3 - CMOS NAND Transistors Sizing Simulation Using PSPICEAnwar Zainuddin100% (2)

- Vlsi Lab 1Документ11 страницVlsi Lab 1Shawon karmokar JotyОценок пока нет

- Design and Analysis of Low Power Bandgap Voltage ReferenceДокумент8 страницDesign and Analysis of Low Power Bandgap Voltage ReferencePraveen Kumar ReddyОценок пока нет

- Rabaey Dig ElectronicsДокумент4 страницыRabaey Dig ElectronicsRahul AgarwalОценок пока нет

- Digital Electronics Lab ManualДокумент80 страницDigital Electronics Lab ManualRohitkumar RathodОценок пока нет

- PMOS, NMOS and CMOS Transmission Gate Characteristics.Документ13 страницPMOS, NMOS and CMOS Transmission Gate Characteristics.Prajwal KhairnarОценок пока нет

- ELEG312+Homework+ 6+solutionsДокумент16 страницELEG312+Homework+ 6+solutionsMạnh TuấnОценок пока нет

- Rail-To-Rail Input and Output AmplifiersДокумент71 страницаRail-To-Rail Input and Output AmplifiersassbassОценок пока нет

- Small Signal Model MOSFETДокумент8 страницSmall Signal Model MOSFETRAHUL100% (1)

- Solution Gates 2 SamplesДокумент9 страницSolution Gates 2 SamplesluqmansulymanОценок пока нет

- Mos Transistor TheoryДокумент144 страницыMos Transistor TheorymailtolokiОценок пока нет

- Vlsi Lab AssignmentДокумент5 страницVlsi Lab AssignmentRahul Saxena100% (1)

- Chap17 Frequency ResponseДокумент61 страницаChap17 Frequency ResponseMạnh Cường TrầnОценок пока нет

- Solns 6Документ13 страницSolns 6api-3750190Оценок пока нет

- Mosfet DC AnalysisДокумент13 страницMosfet DC AnalysiswaqarОценок пока нет

- Lecturenote3 MosfetchapterДокумент48 страницLecturenote3 MosfetchapterBayron Eduardo CentenoОценок пока нет

- ch4 2Документ15 страницch4 2Muhammed I'zwanОценок пока нет

- Lab3 ManualДокумент12 страницLab3 Manualdlat94Оценок пока нет

- 540 130 PDFДокумент5 страниц540 130 PDFNava KrishnanОценок пока нет

- Physics II Finals ReviewerДокумент6 страницPhysics II Finals ReviewerCarter SiyОценок пока нет

- Solution ECE-438, MOS Transistor: W V I K V V V V L Min (V - VДокумент10 страницSolution ECE-438, MOS Transistor: W V I K V V V V L Min (V - Vneeno2013Оценок пока нет

- ECE4762011 Lect14Документ46 страницECE4762011 Lect14selvan90Оценок пока нет

- TUGAS ELEKTRONIKA - Kelompok 2Документ11 страницTUGAS ELEKTRONIKA - Kelompok 2Christine SibaraniОценок пока нет

- Ee Lab ReportДокумент25 страницEe Lab Reportsamuel_r_butlerОценок пока нет

- Coulomb Blockade: Physics of Low Dimensional SemiconductorДокумент16 страницCoulomb Blockade: Physics of Low Dimensional Semiconductorabo_habeeb2003Оценок пока нет

- Planahead User Guide (Ug632)Документ1 страницаPlanahead User Guide (Ug632)ramprakash_rampelliОценок пока нет

- Cmos Inverter 11Документ16 страницCmos Inverter 11api-3750190Оценок пока нет

- Modelsim Se UserДокумент1 100 страницModelsim Se Userramprakash_rampelliОценок пока нет

- CMOS Fabrication: ... or What Lies Beneath..Документ47 страницCMOS Fabrication: ... or What Lies Beneath..ramprakash_rampelliОценок пока нет

- Iphone 14 Pro Max Inspired Preset by Rey Dhen - XMPДокумент3 страницыIphone 14 Pro Max Inspired Preset by Rey Dhen - XMPRizkia Raisa SafitriОценок пока нет

- Nguyen Ngoc-Phu's ResumeДокумент2 страницыNguyen Ngoc-Phu's ResumeNgoc Phu NguyenОценок пока нет

- Project Report: MES Dental College and HospitalДокумент28 страницProject Report: MES Dental College and HospitalAnurtha AnuОценок пока нет

- En 10143-1993Документ7 страницEn 10143-1993Eduardo TeixeiraОценок пока нет

- 2 Design Thinking - EN - pptx-ALVДокумент18 страниц2 Design Thinking - EN - pptx-ALVSalma Dhiya FauziyahОценок пока нет

- Piramal Revanta - Tower 3Документ13 страницPiramal Revanta - Tower 3bennymahaloОценок пока нет

- Al Kindi AssingmentДокумент9 страницAl Kindi AssingmentMuhammad Sirajuddin MazlanОценок пока нет

- Norm TMT PDFДокумент12 страницNorm TMT PDFGustavoОценок пока нет

- Theoretical Grammar of EnglishДокумент132 страницыTheoretical Grammar of EnglishMisarabbit NguyenОценок пока нет

- Tridium Europe DatasheetДокумент2 страницыTridium Europe DatasheetHoàngTrầnОценок пока нет

- 33392-01 Finegayan Water Tank KORANDO PDFДокумент3 страницы33392-01 Finegayan Water Tank KORANDO PDFShady RainОценок пока нет

- El Nido RW 33 Headwind 1120 + CLWДокумент2 страницыEl Nido RW 33 Headwind 1120 + CLWRanny LomibaoОценок пока нет

- Lifestyle Mentor. Sally & SusieДокумент2 страницыLifestyle Mentor. Sally & SusieLIYAN SHENОценок пока нет

- Teacher Empowerment As An Important Component of Job Satisfaction A Comparative Study of Teachers Perspectives in Al Farwaniya District KuwaitДокумент24 страницыTeacher Empowerment As An Important Component of Job Satisfaction A Comparative Study of Teachers Perspectives in Al Farwaniya District KuwaitAtique RahmanОценок пока нет

- Employment Under Dubai Electricity & Water AuthorityДокумент6 страницEmployment Under Dubai Electricity & Water AuthorityMominur Rahman ShohagОценок пока нет

- (LS 1 English, From The Division of Zamboanga Del SurДокумент17 страниц(LS 1 English, From The Division of Zamboanga Del SurKeara MhieОценок пока нет

- Differential Association Theory - Criminology Wiki - FANDOM Powered by WikiaДокумент1 страницаDifferential Association Theory - Criminology Wiki - FANDOM Powered by WikiaMorningstarAsifОценок пока нет

- Semantic SearchMonkeyДокумент39 страницSemantic SearchMonkeyPaul TarjanОценок пока нет

- Comparison of Plate Count Agar and R2A Medium For Enumeration of Heterotrophic Bacteria in Natural Mineral WaterДокумент4 страницыComparison of Plate Count Agar and R2A Medium For Enumeration of Heterotrophic Bacteria in Natural Mineral WaterSurendar KesavanОценок пока нет

- Job No. 25800: Quebrada Blanca Fase 2Документ1 страницаJob No. 25800: Quebrada Blanca Fase 2Benjamín Muñoz MuñozОценок пока нет

- Amanuel MekonnenДокумент125 страницAmanuel Mekonnenabata yohannesОценок пока нет

- MPDFДокумент10 страницMPDFshanmuganathan716Оценок пока нет