Академический Документы

Профессиональный Документы

Культура Документы

1845

Загружено:

aldoyenИсходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

1845

Загружено:

aldoyenАвторское право:

Доступные форматы

Copyright 2000

Rev. 1.4 4/00

F OR F U R T H E R I NF OR MAT I ON C A L L ( 7 1 4 ) 8 9 8 - 8 1 2 1

11861 WESTERN AVENUE, GARDEN GROVE, CA. 92841 1

C U R R E N T MO D E P WM C O N T R O L L E R

P R O D U C T I O N D A T A S H E E T

T H E I N F I N I T E P O W E R O F I N N O V A T I O N

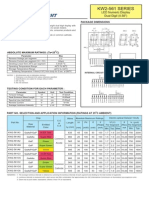

SG1844/SG1845 Series

LI N DOC #: 1844

DE S C RI PT I ON KE Y F E AT URE S

s OPTIMIZED FOR OFF-LINE CONTROL

s LOW START-UP CURRENT (<1mA)

s AUTOMATIC FEED FORWARD

COMPENSATION

s TRIMMED OSCILLATOR DISCHARGE

CURRENT

s PULSE-BY-PULSE CURRENT LIMITING

s ENHANCED LOAD RESPONSE

CHARACTERISTICS

s UNDER-VOLTAGE LOCKOUT WITH 6V

HYSTERESIS (SG1844 only)

s DOUBLE PULSE SUPPRESSION

s HIGH-CURRENT TOTEM-POLE OUTPUT

s INTERNALLY TRIMMED BANDGAP

REFERENCE

s 500kHz OPERATION

s UNDERVOLTAGE LOCKOUT

SG1844 - 16 volts

SG1845 - 8.4 volts

s LOW SHOOT-THROUGH CURRENT <75mA

OVER TEMPERATURE

The SG1844/45 family of control ICs

provides all the necessary features to

implement off-line fixed frequency,

current-mode switching power supplies

with a minimum number of external

components. Current-mode architecture

demonstrates improved line regulation,

improved load regulation, pulse-by-

pulse current limiting and inherent

protection of the power supply output

switch.

The bandgap reference is trimmed to

1% over temperature. Oscillator

discharge current is trimmed to less than

10%. The SG1844/45 has under-

voltage lockout, current-limiting circuitry

PRODUC T HI GHL I GHT

PAC KAGE ORDE R I NF ORMAT I ON

T

A

(C)

0 to 70

SG3844M SG3844N SG3844DM SG3844D SG3844Y SG3844J

SG3845M SG3845N SG3845DM SG3845D SG3845Y SG3845J

-25 to 85

SG2844M SG2844N SG2844DM SG2844D SG2844Y SG2844J

SG2845M SG2845N SG2845DM SG2845D SG2845Y SG2845J

-55 to 125

SG1844Y SG1844J SG1844L

SG1845Y SG1845J SG1845L

MIL-STD/883

SG1844Y/883B SG1844J/883B SG1844L/883B

SG1845Y/883B SG1845J/883B SG1845L/883B

DESC

SG1844Y/DESC SG1844J/DESC SG1844F/DESC SG1844L/DESC

SG1845Y/DESC SG1845J/DESC SG1845F/DESC SG1845L/DESC

TYPI CAL APPL I CAT I ON OF SG3844 I N A FLYBACK CONVERT ER

HIGH RELIABILITY FEATURES

s AVAILABLE TO MIL-STD-883B

s LINFINITY LEVEL "S" PROCESSING AVAILABLE

Note: All surface-mount packages are available in Tape & Reel.

and start-up current of less than 1mA.

The totem-pole output is optimized to

drive the gate of a power MOSFET. The

output is low in the off state to provide

direct interface to an N-channel device.

Both operate up to a maximum duty

cycle range of zero to <50% due to an

internal toggle flip-flop which blanks the

output off every other clock cycle.

The SG1844/45 is specified for

operation over the full military ambient

temperature range of -55C to 125C.

The SG2844/45 is specified for the

industrial range of -25C to 85C, and

the SG3844/45 is designed for the

commercial range of 0C to 70C.

Plastic DIP

8-pin

M

Plastic DIP

14-pin

N

Plastic SOIC

8-pin

DM

Plastic SOIC

14-pin

D

Ceramic DIP

8-pin

Y

Ceramic DIP

14-pin

J

Cer. Flatpack

10-pin

F

Ceramic LCC

20-pin

L

AC

INPUT

SG3844

R

ST

I

ST

V

CC

C U R R E N T - MO D E P WM C O N T R O L L E R

SG1844/SG1845 Series

P R O D U C T D A T A B O O K 1 9 9 6 / 1 9 9 7

Copyright 2000

Rev. 1.4 4/00

2

P R O D U C T I O N D A T A S H E E T

ABSOLUTE MAXIMUM RATINGS (Notes 1 & 2)

Supply Voltage (I

CC

< 30mA) ............................................................... Self Limiting

Supply Voltage (Low Impedance Source) ........................................................ 30V

Output Current (Peak) ....................................................................................... 1A

Output Current (Continuous) ....................................................................... 350mA

Output Energy (Capacitive Load) ....................................................................... 5J

Analog Inputs (Pins 2, 3) ................................................................. -0.3V to +6.3V

Error Amp Output Sink Current ..................................................................... 10mA

Operating Junction Temperature

Hermetic (J, Y, F, L Packages) ................................................................... 150C

Plastic (N, M, D, DM Packages) ................................................................ 150C

Storage Temperature Range.......................................................... -65C to +150C

Lead Temperature (Soldering, 10 Seconds) .................................................. 300C

PACKAGE PIN OUTS

V

REF

V

CC

OUT UT

GND

COM

V

FB

I

SENSE

R

T

/C

T

1 8

2 7

3 6

4 5

M & Y PACKAGE

(Top View)

DM PACKAGE

(Top View)

V

REF

V

CC

OUT UT

GND

COM

V

FB

I

SENSE

R

T

/C

T

1 8

2 7

3 6

4 5

V

REF

N.C.

V

CC

V

C

OUT UT

GND

WR GND

COM

N.C.

V

FB

N.C.

I

SENSE

N.C.

R

T

/C

T

1 14

2 13

3 12

4 11

5 10

6 9

7 8

D PACKAGE

(Top View)

M PACKAGE:

THERMAL RESISTANCE-JUNCTION TO AMBIENT,

JA

95C/W

N PACKAGE:

THERMAL RESISTANCE-JUNCTION TO AMBIENT,

JA

65C/W

DM PACKAGE:

THERMAL RESISTANCE-JUNCTION TO AMBIENT,

JA

165C/W

D PACKAGE:

THERMAL RESISTANCE-JUNCTION TO AMBIENT,

JA

120C/W

Y PACKAGE:

THERMAL RESISTANCE-JUNCTION TO AMBIENT,

JA

130C/W

J PACKAGE:

THERMAL RESISTANCE-JUNCTION TO AMBIENT,

JA

80C/W

F PACKAGE:

THERMAL RESISTANCE-JUNCTION TO CASE,

JC

80C/W

THERMAL RESISTANCE-JUNCTION TO AMBIENT,

JA

145C/W

L PACKAGE:

THERMAL RESISTANCE-JUNCTION TO CASE,

JC

35C/W

THERMAL RESISTANCE-JUNCTION TO AMBIENT,

JA

120C/W

Junction Temperature Calculation: T

J

= T

A

+ (P

D

x

JA

).

The

JA

numbers are guidelines for the thermal performance of the device/pc-board

system. All of the above assume no ambient airflow.

THERMAL DATA

Note 1. Exceeding these ratings could cause damage to the device.

Note 2. All voltages are with respect to Pin 5. All currents are positive into the specified

terminal.

1 14

2 13

3 12

4 11

5 10

6 9

7 8

J & N PACKAGE

(Top View)

COM

N.C.

V

FB

N.C.

I

SENSE

N.C.

R

T

/C

T

V

REF

N.C.

V

CC

V

C

OUT UT

GROUND

OWER GND

F PACKAGE

(Top View)

10.V

REF

9. V

CC

8. V

C

7. OUT UT

6. GND

1. COM

2. V

FB

3. I

SENSE

4. R

T

/C

T

5. OWER GND

1 10

2 9

3 8

4 7

5 6

L PACKAGE

(Top View)

3 2

4

5

6

7

8

9 11 10

1. N.C.

2. N.C.

3. COM .

4. N.C.

5. V

FB

6. N.C.

7. I

SENSE

8. R

T

/C

T

9. N.C.

10. N.C.

1 20 19

18

17

16

15

14

12 13

11. N.C.

12. WR GND

13. GND

14. N.C.

15. OUT UT

16. N.C.

17. V

C

18. V

CC

19. N.C.

20. V

REF

C U R R E N T - MO D E P WM C O N T R O L L E R

SG1844/SG1845 Series

P R O D U C T D A T A B O O K 1 9 9 6 / 1 9 9 7

3

Copyright 2000

Rev. 1.4 4/00

P R O D U C T I O N D A T A S H E E T

E L E C T RI C AL C HARAC T E RI S T I C S

(Unless otherwise specified, these specifications apply over the operating ambient temperatures for SG1844/SG1845 with -55C T

A

125C, SG2844/

SG2845 with -25C T

A

85C, SG3844/SG3845 with 0C T

A

70C, V

CC

= 15V (Note 7), R

T

= 10k, and C

T

= 3.3nF. Low duty cycle pulse testing

techniques are used which maintains junction and case temperatures equal to the ambient temperature.)

Reference Section

Parameter Symbol Test Conditions

Output Voltage T

J

= 25C, I

O

= 1mA

Line Regulation 12 V

IN

25V

Load Regulation 1 I

O

20mA

Temperature Stability (Note 4)

Total Output Variation (Note 4) Line, Load, Temp.

Output Noise Voltage (Note 4) V

N

10Hz f 10kHz, T

J

= 25C

Long Term Stability (Note 4) T

A

= 125C, 1000hrs

Output Short Circuit

SG3844/45

Units

Min. Typ. Max. Min. Typ. Max. Min. Typ. Max.

SG2844/45

4.95 5.00 5.05 4.95 5.00 5.05 4.90 5.00 5.10 V

6 20 6 20 6 20 mV

6 25 6 25 6 25 mV

0.2 0.4 0.2 0.4 0.2 0.4 mV/C

4.90 5.10 4.90 5.10 4.82 5.18 V

50 50 50 V

5 25 5 25 5 25 mV

-30 -100 -180 -30 -100 -180 -30 -100 -180 mA

Oscillator Section

Initial Accuracy (Note 8) T

J

= 25C

Voltage Stability 12V V

CC

25V

Temperature Stability (Note 4) T

MIN

T

A

T

MAX

Amplitude V

RT/CT

(Peak to Peak)

Discharge Current T

J

= 25C

T

MIN

T

A

T

MAX

Error Amp Section

Input Voltage V

COMP

= 2.5V

Input Bias Current

Open Loop Gain A

VOL

2 V

O

4V

Unity Gain Bandwidth (Note 4) T

J

= 25C

Power Supply Rejection Ratio PSRR 12 V

CC

25V

Output Sink Current V

VFB

= 2.7V, V

COMP

= 1.1V

Output Source Current V

VFB

= 2.3V, V

COMP

= 5V

V

OUT

High V

VFB

= 2.3V, R

L

= 15K to gnd

V

OUT

Low V

VFB

= 2.7V, R

L

= 15K to V

REF

SG1844/45

47 52 57 47 52 57 47 52 57 kHz

.02 1 0.2 1 0.2 1 %

5 5 5 %

1.7 1.7 1.7 V

7.8 8.3 9.1 7.5 8.4 9.3 7.5 8.4 9.3 mA

6.8 9.3 7.2 9.5 7.2 9.5 mA

2.45 2.50 2.55 2.45 2.50 2.55 2.42 2.50 2.58 V

-0.3 -1 -0.3 1 -0.3 -2 A

65 90 65 90 65 90 dB

0.7 1 0.7 1 0.7 1 MHz

60 70 60 70 60 70 dB

2 6 2 6 2 6 mA

-0.5 -0.8 -0.5 -0.8 -0.5 -0.8 mA

5 6 5 6 5 6 V

0.7 1.1 0.7 1.1 0.7 1.1 V

Supply Voltage Range

Output Current (Peak)

Output Current (Continuous)

Analog Inputs (Pin 2, Pin 3)

Error Amp Output Sink Current

Oscillator Frequency Range

Oscillator Timing Resistor R

T

Oscillator Timing Capacitor C

T

Operating Ambient Temperature Range:

SG1844/45

SG2844/45

SG3844/45

RE C OMME NDE D OPE RAT I NG C ONDI T I ONS (Note 3)

Parameter Symbol Units

Recommended Operating Conditions

Min. Typ. Max.

30 V

1 A

200 mA

0 2.6 V

5 mA

0.1 500 kHz

0.52 150 k

0.1 1.0 F

-55 125 C

-25 85 C

0 70 C

Note 3. Range over which the device is functional.

(El ect ri cal Charact eri s t i cs cont i nue next page. )

C U R R E N T - MO D E P WM C O N T R O L L E R

SG1844/SG1845 Series

P R O D U C T D A T A B O O K 1 9 9 6 / 1 9 9 7

Copyright 2000

Rev. 1.4 4/00

4

P R O D U C T I O N D A T A S H E E T

E L E C T RI C AL C HARAC T E RI S T I C S (Cont'd.)

Under-Voltage Lockout Section

Parameter Symbol Test Conditions

Start Threshold 1844

1845

Min. Operation Voltage After Turn-On 1844

1845

PWM Section

Maximum Duty Cycle

Minimum Duty Cycle

Power Consumption Section

Start-Up Current

Operating Supply Current V

FB

= V

ISENSE

= 0V

V

CC

Zener Voltage I

CC

= 25mA

Notes: 4. These parameters, although guaranteed, are not 100% tested in

production.

5. Parameter measured at trip point of latch with V

VFB

= 0.

SG3844/45

Units

Min. Typ. Max. Min. Typ. Max. Min. Typ. Max.

SG2844/45

15 16 17 15 16 17 14.5 16 17.5 V

7.8 8.4 9.0 7.8 8.4 9.0 7.8 8.4 9.0 V

9 10 11 9 10 11 8.5 10 11.5 V

7.0 7.6 8.3 7.0 7.6 8.2 7.0 7.6 8.2 V

SG1844/45

46 48 50 46 48 50 46 48 50 %

0 0 0 %

0.5 1 0.5 1 0.5 1 mA

11 17 11 17 11 17 mA

34 34 34 V

6. Gain defined as: A = ; 0 V

ISENSE

0.8V.

7. Adjust V

CC

above the start threshold before setting at 15V.

8. Output frequency equals one half of oscillator frequency.

Output Low Level I

SINK

= 20mA

I

SINK

= 200mA

Output High Level I

SOURCE

= 20mA

I

SOURCE

= 200mA

Rise Time (Note 4) T

J

= 25C, C

L

= 1nF

Fall Time (Note 4) T

J

= 25C, C

L

= 1nF

Current Sense Section

Gain (Notes 5 & 6)

Maximum Input Signal (Note 5) V

COMP

= 5V

Power Supply Rejection Ratio (Note 5) PSRR 12 V

CC

25V

Input Bias Current

Delay to Output (Note 4)

Output Section

2.85 3 3.15 2.85 3 3.15 2.85 3 3.15 V/V

0.9 1 1.1 0.9 1 1.1 0.9 1 1.1 V

70 70 70 dB

-2 -10 -2 -10 -2 -10 A

150 300 150 300 150 300 ns

0.1 0.4 0.1 0.4 0.1 0.4 V

1.5 2.2 1.5 2.2 1.5 2.2 V

13 13.5 13 13.5 13 13.5 V

12 13.5 12 13.5 12 13.5 V

50 150 50 150 50 150 ns

50 150 50 150 50 150 ns

V

COMP

V

ISENSE

C U R R E N T - MO D E P WM C O N T R O L L E R

SG1844/SG1845 Series

P R O D U C T D A T A B O O K 1 9 9 6 / 1 9 9 7

5

Copyright 2000

Rev. 1.4 4/00

P R O D U C T I O N D A T A S H E E T

BL OC K DI AGRAM

*

- V

CC

and V

C

are internally connected for 8-pin packages.

**

- POWER GROUND and GROUND are internally connected for 8-pin packages.

OSCILLATOR

S

R

INTERNAL

BIAS

S / R

5V

REF

PWM

LATCH

CURRENT SENSE

COMPARATOR

1V

R

2R

ERROR AMP

UVLO

34V

GROUND**

V

CC

*

R

T

/C

T

V

FB

T

COMP

CURRENT SENSE

POWER GROUND**

OUTPUT

V

C

*

V

REF

5.0V

50mA

16V (1844)

8.4 (1845)

6V (1844)

0.8V (1845)

2.5V

V

REF

GOOD LOGIC

C U R R E N T - MO D E P WM C O N T R O L L E R

SG1844/SG1845 Series

P R O D U C T D A T A B O O K 1 9 9 6 / 1 9 9 7

Copyright 2000

Rev. 1.4 4/00

6

P R O D U C T I O N D A T A S H E E T

GRAPH / CURVE INDEX

Characteristic Curves

FIGURE #

1. DROPOUT VOLTAGE vs. TEMPERATURE

2. OSCILLATOR TEMPERATURE STABILITY

3. CURRENT SENSE TO OUTPUT DELAY vs. TEMPERATURE

4. START-UP CURRENT vs. TEMPERATURE

5. REFERENCE VOLTAGE vs. TEMPERATURE

6. START-UP VOLTAGE THRESHOLD vs. TEMPERATURE

7. START-UP VOLTAGE THRESHOLD vs. TEMPERATURE

8. OSCILLATOR DISCHARGE CURRENT vs. TEMPERATURE

9. OUTPUT SATURATION VOLTAGE vs. OUTPUT CURRENT AND

TEMPERATURE (SINK TRANSISTOR)

10. CURRENT SENSE THRESHOLD vs. ERROR AMPLIFIER OUTPUT

11. OUTPUT SATURATION VOLTAGE vs. OUTPUT CURRENT AND

TEMPERATURE (SOURCE TRANSISTOR)

FIGURE INDEX

Application Information

FIGURE #

12. OSCILLATOR TIMING CIRCUIT

13. OSCILLATOR FREQUENCY vs. R

T

FOR VARIOUS C

T

Typical Applications Section

FIGURE #

14. CURRENT SENSE SPIKE SUPPRESSION

15. MOSFET PARASITIC OSCILLATIONS

16. BIPOLAR TRANSISTOR DRIVE

17. ISOLATED MOSFET DRIVE

18. ADJUSTABLE BUFFERED REDUCTION OF CLAMP LEVEL WITH

SOFTSTART

19. EXTERNAL DUTY CYCLE CLAMP AND MULTI-UNIT

SYNCHRONIZATION

20. OSCILLATOR CONNECTION

21. ERROR AMPLIFIER CONNECTION

C U R R E N T - MO D E P WM C O N T R O L L E R

SG1844/SG1845 Series

P R O D U C T D A T A B O O K 1 9 9 6 / 1 9 9 7

7

Copyright 2000

Rev. 1.4 4/00

P R O D U C T I O N D A T A S H E E T

C HARAC T E RI S T I C C URVE S

FIGURE 2. OSCILLATOR TEMPERATURE STABILITY

FIGURE 3. CURRENT SENSE TO OUTPUT DELAY vs.

TEMPERATURE

FIGURE 4. START-UP CURRENT vs. TEMPERATURE

FIGURE 1. DROPOUT VOLTAGE vs. TEMPERATURE

Junction Temperature - (C)

F

r

e

q

u

e

n

c

y

D

r

i

f

t

-

(

%

)

-10

-75 -50 -25 0 25 50 75 100 125

-8

-6

-4

-2

0 V

IN

= 15V

Duty Cycle = 50%

2

Junction Temperature - (C)

M

i

n

i

m

u

m

O

p

e

r

a

t

i

n

g

V

o

l

t

a

g

e

-

(

V

)

8.0

-75 -50 -25 0 25 50 75 100 125

8.4

8.8

9.2

9.6

10.0

SG1844

SG1845

Junction Temperature - (C)

C

u

r

r

e

n

t

S

e

n

s

e

D

e

l

a

y

-

(

n

S

)

120

-75 -50 -25 0 25 50 75 100 125

140

160

180

200

220

V

PIN3

= 1.1V

Junction Temperature - (C)

S

t

a

r

t

-

U

p

C

u

r

r

e

n

t

-

(

m

A

)

0.2

-75 -50 -25 0 25 50 75 100 125

0.3

0.4

0.5

0.6

0.7

SG1844

SG1845

C U R R E N T - MO D E P WM C O N T R O L L E R

SG1844/SG1845 Series

P R O D U C T D A T A B O O K 1 9 9 6 / 1 9 9 7

Copyright 2000

Rev. 1.4 4/00

8

P R O D U C T I O N D A T A S H E E T

C HARAC T E RI S T I C C URVE S

FIGURE 6. START-UP VOLTAGE THRESHOLD vs.

TEMPERATURE

FIGURE 7. START-UP VOLTAGE THRESHOLD vs.

TEMPERATURE

FIGURE 8. OSCILLATOR DISCHARGE CURRENT vs.

TEMPERATURE

FIGURE 5. REFERENCE VOLTAGE vs. TEMPERATURE

Junction Temperature - (C)

R

e

f

e

r

e

n

c

e

V

o

l

t

a

g

e

-

(

V

)

8.18

-75 -50 -25 0 25 50 75 100 125

SG1845

8.22

8.26

8.30

8.32

8.20

8.24

8.28

Junction Temperature - (C)

R

e

f

e

r

e

n

c

e

V

o

l

t

a

g

e

-

(

V

)

4.98

-75 -50 -25 0 25 50 75 100 125

V

CC

= 15V

4.99

5.00

5.01

5.02

Junction Temperature - (C)

S

t

a

r

t

U

p

V

o

l

t

a

g

e

-

(

V

)

16.00

-75 -50 -25 0 25 50 75 100 125

SG1844

16.02

16.04

16.06

16.08

15.98

Junction Temperature - (C)

O

s

c

i

l

l

a

t

o

r

D

i

s

c

h

a

r

g

e

C

u

r

r

e

n

t

-

(

m

A

)

7.4

-75 -50 -25 0 25 50 75 100 125

7.6

7.8

8.0

8.2

7.2

C U R R E N T - MO D E P WM C O N T R O L L E R

SG1844/SG1845 Series

P R O D U C T D A T A B O O K 1 9 9 6 / 1 9 9 7

9

Copyright 2000

Rev. 1.4 4/00

P R O D U C T I O N D A T A S H E E T

C HARAC T E RI S T I C C URVE S

FIGURE 10. CURRENT SENSE THRESHOLD vs.

ERROR AMPLIFIER OUTPUT

FIGURE 11. OUTPUT SATURATION VOLTAGE vs.

OUTPUT CURRENT & TEMPERATURE

FIGURE 9. OUTPUT SATURATION VOLTAGE vs.

OUTPUT CURRENT & TEMPERATURE

Error Amp Output Voltage - (V)

C

u

r

r

e

n

t

S

e

n

s

e

T

h

r

e

s

h

o

l

d

-

(

V

)

0.2

1.0 2.0 3.0 4.0 5.0

0.4

0.6

0.8

1.0

0

0.1

0.3

0.5

0.7

0.9

1

2

5

C

2

5

C

-

5

5

C

Output Current - (mA)

S

a

t

u

r

a

t

i

o

n

V

o

l

t

a

g

e

-

(

V

)

0.5

100 200 300 400 500

1.0

1.5

2.0

2.5

0

-5

5

C

+

2

5

C

+

1

2

5

C

V

IN

= 15V

Duty Cycle < 5%

Output Current - (mA)

S

a

t

u

r

a

t

i

o

n

V

o

l

t

a

g

e

-

(

V

)

1.0

100 200 300 400 500

2.0

3.0

4.0

0

V

IN

= 15V

Duty Cycle < 5%

-5

5

C

+

2

5

C

+

1

2

5

C

+

1

2

5

C

+

2

5

C

C U R R E N T - MO D E P WM C O N T R O L L E R

SG1844/SG1845 Series

P R O D U C T D A T A B O O K 1 9 9 6 / 1 9 9 7

Copyright 2000

Rev. 1.4 4/00

10

P R O D U C T I O N D A T A S H E E T

APPL I C AT I ON I NF ORMAT I ON

OSCILLATOR

The oscillator of the 1844/45 family of PWM's is programmed by

the external timing components (RT, CT) as shown in Figure 13.

FIGURE 12 OSCILLATOR TIMING CIRCUIT

V

REF

R

T

/C

T

GND

R

T

C

T

FIGURE 13 OSCILLATOR FREQUENCY vs. R

T

FOR VARIOUS C

T

100K

1K

100

10K

R

T

-

(

)

Oscillator Frequency - (Hz)

100K

1K 10K

1M

1

0

0

n

F

4

7

n

F

2

2

n

F

1

0

n

F

4

.

7

n

F

2

.

2

n

F

1

n

F

F where R

T

5k

1.86

R

T

C

T

C U R R E N T - MO D E P WM C O N T R O L L E R

SG1844/SG1845 Series

P R O D U C T D A T A B O O K 1 9 9 6 / 1 9 9 7

11

Copyright 2000

Rev. 1.4 4/00

P R O D U C T I O N D A T A S H E E T

T YPI C AL APPL I C AT I ON C I RC UI T S

FIGURE 17. ISOLATED MOSFET DRIVE FIGURE 16. BIPOLAR TRANSISTOR DRIVE

Current transformers can be used where isolation is required

between PWM and Primary ground. A drive transformer is then

necessary to interface the PWM output with the MOSFET.

The 1844/45 output stage can provide negative base current to

remove base charge of power transistor (Q

1

) for faster turn off. This

is accomplished by adding a capacitor (C

1

) in parallel with a resistor

(R

1

). The resistor (R

1

) is to limit the base current during turn on.

Pin numbers referenced are for 8-pin package and pin numbers in parenthesis are for 14-pin package.

FIGURE 14. CURRENT SENSE SPIKE SUPPRESSION FIGURE 15. MOSFET PARASITIC OSCILLATIONS

A resistor (R

1

) in series with the MOSFET gate reduce overshoot and

ringing caused by the MOSFET input capacitance and any inductance

in series with the gate drive. (Note: It is very important to have a

low inductance ground path to insure correct operation of the I.C.

This can be done by making the ground paths as short and as wide

as possible.)

The RC low-pass filter will eliminate the leading edge current spike

caused by parasitics of Power MOSFET.

V

CC

V

IN

7 (12)

7 (11)

6 (10)

5 (8)

3 (5)

R

C

R

S

Q1

I

PK

I

PK(MAX)

=

1.0V

R

S

SG1844/45

V

CC

V

IN

7 (12)

7 (11)

6 (10)

5 (8)

R

S

Q1

SG1844/45

3 (5)

R

1

SG1844/45

3 (5)

5 (8)

6 (10)

7 (11)

R

S

Q1

V

C1

C

1

R

1

R

2

V

IN

V

C

I

B

+

V

C

R

2

V

C1

R

1

||R

2

_

V

CC

V

IN

7 (12)

7 (11)

6 (10)

5 (8)

3 (5)

SG1844/45

Isolation

Boundary

C

R

R

S

N

S

N

P

Q1

V

GS

Waveforms

+

_

0

+

_

0

50% DC

25% DC

I

PK

=

V (PIN 1) - 1.4

3R

S

N

P

N

S

j

,

(

\

(

,

C U R R E N T - MO D E P WM C O N T R O L L E R

SG1844/SG1845 Series

P R O D U C T D A T A B O O K 1 9 9 6 / 1 9 9 7

Copyright 2000

Rev. 1.4 4/00

12

P R O D U C T I O N D A T A S H E E T

T YPI C AL APPL I C AT I ON C I RC UI T S (continued)

FIGURE 19. EXTERNAL DUTY CYCLE CLAMP AND

MULTI-UNIT SYNCHRONIZATION

FIGURE 18. ADJUSTABLE BUFFERED REDUCTION OF CLAMP LEVEL

WITH SOFTSTART

Precision duty cycle limiting for a duty cycle of <50%, as well as

synchronizing several 1844/45's is possible with the above circuitry.

Softstart and adjustable peak current can be done with the external

circuitry shown above.

I

PK

= Where: 0 V

1

1.0V t

SOFTSTART

= -ln1 - C

7 (12)

6 (10)

7 (11)

5 (8)

3 (5)

SG1844/45

V

CC

V

IN

Q1

R

S 5 (9)

8 (14)

4 (7)

2 (3)

1 (1)

2N2907

R

2

R

1

1

N

4

1

4

8

C

2

6

R

B

R

A

1

8 4

3

555

TIMER

4 (7)

5 (9)

8 (14)

SG1844/45

To other

SG1844/45

C

FIGURE 21. ERROR AMPLIFIER CONNECTION FIGURE 20. OSCILLATOR CONNECTION

7 (11)

6 (10)

5V

C

T

2.8V

1.1V

SG1844/45

Discharge

Current

I

d

= 8.2mA

R

T

1 (1)

R

F

R

i

2 (3)

R

F

10K

2.5V

SG1844/45

0.5mA

The oscillator is programmed by the values selected for the timing

components R

T

and C

T

. Refer to application information for

calculation of the component values.

Error amplifier is capable of sourcing and sinking current up to 0.5mA.

f =

(R

A

+ 2R

B

)C

1.44

f =

R

A

+ 2R

B

R

B

V

1

R

S

R

1

R

2

R

1

+R

2

1.43 - 0.23

1+

,

,

]

]

]

V

C

V

2

and V

1

= where: V

2

=

R

1

R

2

R

1

R

2

0.5

1+

R

1

R

2

This datasheet has been downloaded from:

www.DatasheetCatalog.com

Datasheets for electronic components.

Вам также может понравиться

- SG3842Документ14 страницSG3842sveta9733276100% (1)

- CA3059, CA3079: Description FeaturesДокумент12 страницCA3059, CA3079: Description FeaturesMiltongrimi GrimilОценок пока нет

- 74HC14Документ15 страниц74HC14Adilson LucaОценок пока нет

- SN75189NДокумент10 страницSN75189NJonatan Sovero BozaОценок пока нет

- HGTG12N60A4D, HGTP12N60A4D, HGT1S12N60A4DS: 600V, SMPS Series N-Channel IGBT With Anti-Parallel Hyperfast Diode FeaturesДокумент8 страницHGTG12N60A4D, HGTP12N60A4D, HGT1S12N60A4DS: 600V, SMPS Series N-Channel IGBT With Anti-Parallel Hyperfast Diode Featuresiulian_bОценок пока нет

- 7805TДокумент7 страниц7805TGoti TorcalОценок пока нет

- Precision Waveform Generator/Voltage Controlled Oscillator FeaturesДокумент12 страницPrecision Waveform Generator/Voltage Controlled Oscillator FeaturesCharles Tineo0% (1)

- Datasheet NE5532APДокумент10 страницDatasheet NE5532APMartín SayagoОценок пока нет

- 1.5A Low Dropout Regulator With Enable: Global Mixed-Mode Technology IncДокумент9 страниц1.5A Low Dropout Regulator With Enable: Global Mixed-Mode Technology IncImamОценок пока нет

- MC1489, MC1489A, SN55189, SN55189A, SN75189, SN75189A Quadruple Line ReceiversДокумент22 страницыMC1489, MC1489A, SN55189, SN55189A, SN75189, SN75189A Quadruple Line ReceiversDiego García MedinaОценок пока нет

- D D D D D: Description/ordering InformationДокумент14 страницD D D D D: Description/ordering InformationUma MageshwariОценок пока нет

- Gm2842a Gm3845aДокумент19 страницGm2842a Gm3845aMarcos ZielinskiОценок пока нет

- P 9 NC 60 FPДокумент9 страницP 9 NC 60 FPJulian PascuОценок пока нет

- Datasheet SN74HC04 - Hex InversorДокумент16 страницDatasheet SN74HC04 - Hex InversorPablo CarvalhoОценок пока нет

- Datasheet.... Schmitt TriggerДокумент22 страницыDatasheet.... Schmitt TriggerIc CruiseОценок пока нет

- Sn7414 Schmitt TriggerДокумент13 страницSn7414 Schmitt TriggerFaazil FairoozОценок пока нет

- SCRДокумент10 страницSCRHugo LopezОценок пока нет

- P 4 NK 80 ZДокумент18 страницP 4 NK 80 ZMalik Farhan ShabirОценок пока нет

- 74LS14Документ16 страниц74LS14Daniela S Arroba CОценок пока нет

- CA3189EДокумент8 страницCA3189EelektrovodaОценок пока нет

- D D D D D D D D D D: Description/ordering InformationДокумент21 страницаD D D D D D D D D D: Description/ordering InformationPalouОценок пока нет

- PT-76 Series Temperature Controller Operation Manual - B0Документ2 страницыPT-76 Series Temperature Controller Operation Manual - B0jowegОценок пока нет

- STW21NM50N MosfetДокумент16 страницSTW21NM50N MosfetrigowОценок пока нет

- Op 07 DДокумент6 страницOp 07 DShaun Dwyer Van HeerdenОценок пока нет

- P6NK90ZДокумент13 страницP6NK90ZVictor ChangОценок пока нет

- TGE 5, TGE 5-Ex, TGM 5, TGM 5-Ex, TGU 5, TGU 5-Ex: Transmitter For Angular PositionДокумент10 страницTGE 5, TGE 5-Ex, TGM 5, TGM 5-Ex, TGU 5, TGU 5-Ex: Transmitter For Angular Positionvinodk335Оценок пока нет

- 2 N 6344Документ8 страниц2 N 6344lgrome73Оценок пока нет

- 8008fa - 72V Regulator PDFДокумент16 страниц8008fa - 72V Regulator PDFKaan GünayОценок пока нет

- UC3825ADWДокумент15 страницUC3825ADWmichaelliu123456Оценок пока нет

- C106MGДокумент6 страницC106MGCesar VeraОценок пока нет

- KW2-561 SERIES: Description: Package DimensionsДокумент1 страницаKW2-561 SERIES: Description: Package DimensionsValdivia FranciscoОценок пока нет

- STP6NA80 Stp6Na80Fi: N - Channel Enhancement Mode Fast Power Mos TransistorДокумент11 страницSTP6NA80 Stp6Na80Fi: N - Channel Enhancement Mode Fast Power Mos Transistorz01loОценок пока нет

- Fet 60NF06Документ9 страницFet 60NF06Anh Nguyễn HoàngОценок пока нет

- Mac 15Документ9 страницMac 15wolfgang39Оценок пока нет

- SANYO Semiconductor Specifications and STK404-120N-E Audio ICДокумент11 страницSANYO Semiconductor Specifications and STK404-120N-E Audio ICgapjgОценок пока нет

- STP55NE06 STP55NE06FP: N - Channel Enhancement Mode " Single Feature Size " Power MosfetДокумент9 страницSTP55NE06 STP55NE06FP: N - Channel Enhancement Mode " Single Feature Size " Power MosfetLiliana Nadia MarchisОценок пока нет

- Stp7Nk80Z - Stp7Nk80Zfp STB7NK80Z - STB7NK80Z-1Документ18 страницStp7Nk80Z - Stp7Nk80Zfp STB7NK80Z - STB7NK80Z-1queequeg73Оценок пока нет

- Adl Ap4g3Документ100 страницAdl Ap4g3Catia Santoro100% (1)

- 4 Ca741 (Harris)Документ5 страниц4 Ca741 (Harris)Ricardo Teixeira de AbreuОценок пока нет

- DatasheetДокумент1 страницаDatasheetMateus RibeiroОценок пока нет

- AD829AQ-High Speed Video OpampДокумент13 страницAD829AQ-High Speed Video OpamphariharanccetОценок пока нет

- CA3059Документ13 страницCA3059Luis Miguel BarrenoОценок пока нет

- Data SheetДокумент11 страницData SheetelgarinenseОценок пока нет

- 556 DatasheetДокумент8 страниц556 DatasheetDaniela Cardenas LuboОценок пока нет

- S108T02 Series S208T02 Series: I (RMS) 8A, Zero Cross Type Low Profile SIP 4pin Triac Output SSRДокумент13 страницS108T02 Series S208T02 Series: I (RMS) 8A, Zero Cross Type Low Profile SIP 4pin Triac Output SSRmplokijuhyОценок пока нет

- SMAJДокумент5 страницSMAJStu DentОценок пока нет

- SG3524Документ9 страницSG3524gettinОценок пока нет

- 2N6073A DatasheetДокумент8 страниц2N6073A DatasheetJulia VidallОценок пока нет

- EX 1673 2 - DPtransmitterДокумент12 страницEX 1673 2 - DPtransmitterCerveza FlotaОценок пока нет

- D D D D D D D: SN54HC574, SN74HC574 Octal Edge-Triggered D-Type Flip-Flops With 3-State OutputsДокумент16 страницD D D D D D D: SN54HC574, SN74HC574 Octal Edge-Triggered D-Type Flip-Flops With 3-State OutputsJADERSONОценок пока нет

- AD780Документ10 страницAD780game___overОценок пока нет

- SG3524Документ19 страницSG3524Gabriel CamargoОценок пока нет

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsОт EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsОценок пока нет

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Оценок пока нет

- 110 Waveform Generator Projects for the Home ConstructorОт Everand110 Waveform Generator Projects for the Home ConstructorРейтинг: 4 из 5 звезд4/5 (1)