Академический Документы

Профессиональный Документы

Культура Документы

6.012 ST13 Design Project

Загружено:

arthur5689791Исходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

6.012 ST13 Design Project

Загружено:

arthur5689791Авторское право:

Доступные форматы

6.

012

Microelectronic Devices and Circuits

Optical Receiver Design Project

Assigned Out: Wednesday, April 24, 2013 Due: Friday, May 10, 2013

Spring 2013

1. Introduction In this project, you are going to design an optical receiver for laser pulses sent over an optical fiber by a transmitter as part of a data communication channel. In the fiber optic system, a transmitter encodes the data as IR laser pulses and transmits the pulses over a long optical fiber. At the other end of the optical receiver detects the attenuated optical signal, transduces it to an electrical signal and then amplifies electrical signal to digital levels. For simplicity we shall assume that the data transmitted is encoded into a 4-bit word. The transmitter sends these words using infra-red pulses, four pulses per word, or one pulse per bit. The bit rate is 10 MHz. Your task is to design the receiver to detect IR signals sent by the transmitter and convert them back into digital bits. To make things more interesting, the words transmitted are actually encrypted. In order to get the correct word at the output, you need to perform a NOR function of the detected word with the encryption key, 1101. Finally, your design needs to be able to drive a load capacitor of 1pF. A 1.5m CMOS process is available for this design. You can download the model file from the course website under the link Project. The relevant parameters are the SPICE Level I parameters such as VTO, UO, TOX (or COX), CGDO, CJSW, CJ, PB, MJ, MJSW, etc. Note that 1.5 m CMOS process means Lmin = 1.5 m and in most instances means minimum LG = Lmin and minimum Ldiff = 2Lmin. How does IR receiver work? The functional blocks of the IR optical receiver are shown in Figure 1. The photodiode receives the IR signal and converts IR pulses into current pulses as shown in Figure 2. This current signal will vary depending on the distance between the IR transmitter and the receiver. The current is converted to voltage by an input stage and the resulting voltage signal is passed through a gain stage in which the voltage signal is amplified to a sufficient level to drive a decoder logic. The last stage of the gain stage(s) serves essentially as an analog to digital converter. After the signal is decoded it is used to drive another chip which is represented by the load capacitance. 2. Design Specifications 1.5m CMOS process, with a supply voltage VDD=5V Frequency fTX=10 MHz (bit rate) Maximum power consumption Pdc=7.5mW Maximum total propagation delay td= tPHL +tPLH=50ns Load capacitor CL=1pF High output (bit 1) voltage VH>4.9V, and low output (bit 0) voltage VL<0.1V

6.012-ST13-CircuitDesignProject-01.doc

Circuit Design Project

Page 1 of 5

3. Design process

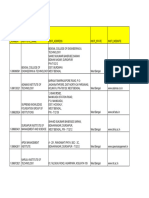

Figure 1: Block Diagram

The project can be divided into four parts as shown in the block diagram in Figure 1.

Signal source: A reverse biased photo diode is used to detect the IR signal. The current on this photo diode provides the input for your design. The diode can be represented by an ideal current source in parallel with a 1pF parasitic capacitor as shown in Figure 2. The diode current has a peak current of 10A when detecting the bit 1, and 0 when detecting the bit 0. Although the laser diode in the optical transmitter produces a large square wave pulse at the end of the fiber, dispersion and loss make the diode current, is, appear sinusoidal. This current is guaranteed to have a peak of about 10 A.

Photons

A

1pF

A

is

is 10A

100 200 Time (ns)

300

400

B

Photo Diode

B

Circuit Model

Figure 2: Photo Diode Signal Source

Example: detecting 1011

Input stage: Usually, it is easier to amplify voltages than currents. In addition, your design needs to drive a logic gate. Therefore, the input signal, in the form of the current on the photo diode, needs to be converted into voltage. This conversion can be accomplished by a trans-impedance amplifier (TIA) (it is also referred to as trans-resistance amplifiers). TIAs usually have small input impedance and large output resistance. Hint: which of the transistor configurations (common-gate, common-source ) fit this description?

6.012-ST13-CircuitDesignProject-01.doc

Circuit Design Project

Page 2 of 5

Gain stage(s): Additional gain stage(s) might be necessary to amplify the input signal enough to drive the decoding logic. Keep in mind that these gain stages are voltage amplifiers and the last of these stages essentially converts the analog signal to digital signal by clipping the analog signal, hence the last of the gain stages is often called a saturating (or limiting) amplifier. [See lecture 18 notes that introduces amplifiers]. You are free to choose the topologies as well as biasing circuits for these amplifiers. Decoding Logic: A NOR gate provides the decoding logic and it drives an output buffer. The two inputs of this NOR gate are the encryption key 1101, and the detected word from the infra-red signal. The key 1101 can be represented by an ideal piecewise linear voltage source. Output stage: A buffer driving a 1pF load capacitor provides the output. The 1pF load capacitor presents a design challenge. In order to satisfy the time delay requirement, you will need a reasonably sized output buffer to drive the 1pF load. However, a large output buffer has two drawbacks. First, it consumes more power. Second, since it is the load to the decoding logic, it directly affects the power consumption as well as time delay of the decoding stage. It is possible to size the output buffer such that it can drive the 1pF load capacitor directly and still satisfy both the power consumption and time delay requirement. However, you might find it easier to insert another sized buffer stage between the decoding logic and the 1pF load capacitor (Read Section 13.5.3 of Howe and Sodini).

4. Design Approach You are encouraged to approach the design using hand-calculations. Use the NMOS & PMOS parameters in the SPICE model file. You should only use HSPICE after you have chosen topologies and determined all the component values. The results from HSPICE help you with verifying your prediction from handcalculation, and final tweaking to meet all the specifications. You are strongly encouraged to present your rough hand calculations and design approach to the instructors for feedback during office hours.

5. Schedule As in most technical design problems, time is not an infinite resource and it often has an effect on the overall cost. Furthermore, time to market determines very much the success of products. With this in mind we suggest that you follow the schedule outlined below with individual milestones and deliverables which will be turned in.. The first milestone is the topological design outlining the circuit elements (transistors and passive elements) that comprise each of the stages in the block diagram (a) transimpedance amplifier (TIA), (b) gain stages including the limiting amplifier, (c) the NOR gate for the decoding logic and (d) output driver. This could be done without the bias

6.012-ST13-CircuitDesignProject-01.doc

Circuit Design Project

Page 3 of 5

circuits but the schematic of the bias circuit should be specified. This should be completed and a copy turned in by Thursday, May 2, 2013 at 5:00 PM or earlier. Remember to retain a copy for later use. Our objective is to make sure you are on schedule. The second milestone is the completion of design based on hand calculation including (a) bias circuits, (b) transistor sizes for each block & values of passive elements comprising each block, (c) performance of each block and overall transceiver performance. This should be completed by Monday, May 6, 2013 by 5:00 PM or earlier. Please turn-in a copy of your calculations but remember to retain a copy for later use. Our objective is to make sure you are on schedule. The third milestone is simulation of your device using SPICE and adjustment of parameters to improve performance. This should be completed by Thursday, May 9, 2013 at 5:00 PM or earlier but no report is due. The final milestone and your final deliverable is the report which is due on Friday, May 10, 2013 at 5:00 PM by electronic submission if possible.

6. Report You are expected to submit a complete report. Your report must describe your design in a clear, concise, and complete manner. The report should include the following parts: Circuit schematic (maximum 1 page). Neatly draw your final circuit, labeling all the component names, size and values. Make sure to indicate all the dc bias conditions (dc voltage of all nodes, and dc current of all components) Approach (maximum 2 pages) Explain your design approach and topology selections. For each stage (TIA, voltage amplifier, decoding logic, output), discuss the design tradeoffs that you discovered. Final HSPICE input file (maximum 1 page) You should remove all the model parameter lines from the printout. Hand in only the circuit description and simulation portion. HSPICE output Plots (maximum 1 page) Include the transient analysis plot of the output. Please mark the time delays (tPHL and tPLH). Hand Calculations (maximum 3 pages) If you turned in your hand calculations earlier, you do not need to turn in another one if there are no significant changes NB: Please be prepared to demonstrate that your circuit simulation works. The TAs may ask you to load the SPICE deck and run the simulation on Friday, May 10, 2013 (Due Date). The interim reports will only be graded when the final report is graded.

6.012-ST13-CircuitDesignProject-01.doc

Circuit Design Project

Page 4 of 5

POLICY FOR ACADEMIC CONDUCT

The homework and design problems in 6.012 are prepared with the aim of complementing lectures and recitations and are designed to reinforce important concepts and material. Working on the problem sets and design problems is extremely effective in assuring your command of the course material. In order to encourage you to do the homework and design problems in a timely manner, a significant fraction of the final grade will be based on your performance in these exercises. This brings up important ethical questions to the foreground. Our judgment is that allowing and encouraging collaboration with fellow students best serve the primary learning purpose of homework and design problems. After all, modern engineering is almost exclusively a team effort. However, fairness requires us to be able to assess your own contribution. This also provides you with feedback that helps you learn better. Towards this goal, below are the rules for academic conduct in 6.012 this semester: You are allowed and encouraged to work with fellow students on homework and design problems. All parties must acknowledge collaborations or discussions in writing in the assignment. You must work out the entire assignment. The written material that you hand in must be your own work.

The policy of academic conduct outlined in this handout is intended to help you make the most out of 6.012 by freely working with your classmates and any material you may find useful. If you have any doubts as to what constitutes ethical or unethical behavior, please contact any member of the staff. Violations to this policy will be handled with the maximum severity allowed by the Institute's Rules and Regulations regarding academic honesty as outlined on the web at http://web.mit.edu/discipline/academic.html.

6.012-ST13-CircuitDesignProject-01.doc

Circuit Design Project

Page 5 of 5

Вам также может понравиться

- DeliciousDoughnuts Eguide PDFДокумент35 страницDeliciousDoughnuts Eguide PDFSofi Cherny83% (6)

- RS232 CommunicationsДокумент37 страницRS232 CommunicationsNoor Kareem100% (1)

- Lab 2 - myRIO Analog Basics PDFДокумент6 страницLab 2 - myRIO Analog Basics PDFguigo170_321273986Оценок пока нет

- Impact of Pantawid Pamilyang Pilipino Program On EducationДокумент10 страницImpact of Pantawid Pamilyang Pilipino Program On EducationEllyssa Erika MabayagОценок пока нет

- Patrick Meyer Reliability Understanding Statistics 2010Документ160 страницPatrick Meyer Reliability Understanding Statistics 2010jcgueinj100% (1)

- Prototyping and Measurements For A Lifi SystemДокумент5 страницPrototyping and Measurements For A Lifi SystemSumit BansalОценок пока нет

- DPScope SE Design Description PDFДокумент11 страницDPScope SE Design Description PDFingenierognvОценок пока нет

- Lab BookДокумент70 страницLab Bookअमरेश झाОценок пока нет

- Apparatus:: AIM: Acquire The Knowledge of Output Devices Like CRO and DSO For Observing OutputДокумент5 страницApparatus:: AIM: Acquire The Knowledge of Output Devices Like CRO and DSO For Observing OutputAdwait BorikarОценок пока нет

- VHDL & Optical Fiber Lab: L Ab ManualДокумент29 страницVHDL & Optical Fiber Lab: L Ab ManualR arnaldОценок пока нет

- 37 - Myoelectrically Controlled Robotic ArmДокумент37 страниц37 - Myoelectrically Controlled Robotic ArmKARTHIK S SОценок пока нет

- PLL DividerДокумент6 страницPLL Divider081270Оценок пока нет

- TI Data Converter GuideДокумент16 страницTI Data Converter GuideDavid PostonОценок пока нет

- Computer-Based Project in VLSI Design Co 3/7Документ14 страницComputer-Based Project in VLSI Design Co 3/7Naresh LakhaniОценок пока нет

- Tutorial 3: Entering The World of GNU Software RadioДокумент5 страницTutorial 3: Entering The World of GNU Software RadioNahum SetuОценок пока нет

- IR Sensor Based Distance Measurement SystemДокумент5 страницIR Sensor Based Distance Measurement SystemRajkeen ChamanshaikhОценок пока нет

- Ofc Lab Manual 2Документ21 страницаOfc Lab Manual 2Shobhit JainОценок пока нет

- 4 Channel RF Remote Control DeviceДокумент90 страниц4 Channel RF Remote Control Devicepinku3Оценок пока нет

- The Development of The Digital Oscilloscope Based On FPGA PDFДокумент8 страницThe Development of The Digital Oscilloscope Based On FPGA PDFivy_publisherОценок пока нет

- Embedded Radar SignalprocessingДокумент3 страницыEmbedded Radar SignalprocessingManikantaReddyОценок пока нет

- RealDigital Module 8Документ7 страницRealDigital Module 8Sidney O. EbotОценок пока нет

- Digital Communications Lab: List of ExperimentsДокумент50 страницDigital Communications Lab: List of ExperimentsNeel SarkarОценок пока нет

- AO Proximity Security SystemДокумент31 страницаAO Proximity Security SystemSana UllahОценок пока нет

- Final Doc 2Документ49 страницFinal Doc 2Alekhya Alex100% (1)

- Implementation of A Fiberoptic Transceiver: ObjectivesДокумент33 страницыImplementation of A Fiberoptic Transceiver: Objectivesanasardi93Оценок пока нет

- EDN Design Ideas 2006Документ142 страницыEDN Design Ideas 2006chag1956100% (1)

- Talking Volt MeterДокумент9 страницTalking Volt Meterudita10Оценок пока нет

- Research PaperДокумент8 страницResearch PaperinfydiptiОценок пока нет

- 4fsk DemodДокумент4 страницы4fsk DemodavionionОценок пока нет

- Final Project Report E3390 Electronic Circuits Design Lab RFID Access Control SystemДокумент28 страницFinal Project Report E3390 Electronic Circuits Design Lab RFID Access Control Systemshanx77Оценок пока нет

- AmДокумент8 страницAmLisa TorresОценок пока нет

- RPM Measurement (Tachometer)Документ10 страницRPM Measurement (Tachometer)19E45A0229 SDESEEEОценок пока нет

- Design and Simulation of 1-Bit Sigma-Delta ADC Using Ngspice ToolДокумент5 страницDesign and Simulation of 1-Bit Sigma-Delta ADC Using Ngspice ToolIjarcsee JournalОценок пока нет

- Term Paper EEL (201) : Clock and Data Recovery CircuitsДокумент4 страницыTerm Paper EEL (201) : Clock and Data Recovery CircuitsGaurav NavalОценок пока нет

- Procedure - AC Circuits and Signal Modulation - W20Документ6 страницProcedure - AC Circuits and Signal Modulation - W20ChocoОценок пока нет

- Paper Presentation On Detection by RADAR byДокумент4 страницыPaper Presentation On Detection by RADAR byJanmayjay SwetankОценок пока нет

- Isscc2022 000016CLДокумент17 страницIsscc2022 000016CLdashuai huaОценок пока нет

- An Efficient Cordic Processor For Complex Digital Phase Locked LoopДокумент7 страницAn Efficient Cordic Processor For Complex Digital Phase Locked LoopInternational Journal of Application or Innovation in Engineering & ManagementОценок пока нет

- EE 310 Electronic Circuit Design I Experiment 8 Op Amp Design ProjectДокумент4 страницыEE 310 Electronic Circuit Design I Experiment 8 Op Amp Design ProjectZulqarnain KhanОценок пока нет

- Design and Analysis of A Low Power Passive UHF RFID Transponder ICДокумент6 страницDesign and Analysis of A Low Power Passive UHF RFID Transponder ICAli ErenОценок пока нет

- EE 230 - Analog Circuits Lab - 2021-22/I (Autumn) Experiment 1: Familiarization With NGSPICE Circuit Simulator and Lab EquipmentДокумент7 страницEE 230 - Analog Circuits Lab - 2021-22/I (Autumn) Experiment 1: Familiarization With NGSPICE Circuit Simulator and Lab EquipmentTanmay JainОценок пока нет

- Sample Questions: Chapter One: Digital Building BlocksДокумент4 страницыSample Questions: Chapter One: Digital Building BlocksDonnОценок пока нет

- DAC CompleteДокумент9 страницDAC CompleteNashrul HaqОценок пока нет

- Simple FSKДокумент6 страницSimple FSKFaten AliОценок пока нет

- Decoder2001 Armatur HorowitzДокумент10 страницDecoder2001 Armatur HorowitzNK NKОценок пока нет

- A Low Power, and Low Signal 5-Bit 25msamples/s Pipelined ADC For Monolithic Active PixelsДокумент5 страницA Low Power, and Low Signal 5-Bit 25msamples/s Pipelined ADC For Monolithic Active Pixelstajmjcet_123Оценок пока нет

- Traffic Light Control SystemДокумент12 страницTraffic Light Control SystemVinay ReddyОценок пока нет

- DQPSK ModulationДокумент14 страницDQPSK Modulationkrishnak_ece7077Оценок пока нет

- Opamp Baed Line Follower RobotДокумент9 страницOpamp Baed Line Follower RobotboresharvariОценок пока нет

- DSP Techniques For Radio AmateursДокумент32 страницыDSP Techniques For Radio AmateursbaymanОценок пока нет

- Exploring GNU RadioДокумент10 страницExploring GNU RadioSudharssun Subramanian0% (1)

- Integrator Circuits: 7.0.1 ReadingДокумент5 страницIntegrator Circuits: 7.0.1 Readingnaveenkv10_105528408Оценок пока нет

- Implementation of Digital QPSK Modulator by Using VHDL / MatlabДокумент5 страницImplementation of Digital QPSK Modulator by Using VHDL / Matlabblesson123Оценок пока нет

- C CCC CCC C CC C CДокумент6 страницC CCC CCC C CC C CMd Rizwan AhmadОценок пока нет

- AP0107 Impedance-Controlled RoutingДокумент6 страницAP0107 Impedance-Controlled RoutingdrakenhavenОценок пока нет

- DC Lab 2018 HandoutsДокумент22 страницыDC Lab 2018 HandoutssruthyОценок пока нет

- Construction of Microcontroller Based Digital Voltmeter: Md. Imran Hossain Jony, Md. Moshiur RahmanДокумент4 страницыConstruction of Microcontroller Based Digital Voltmeter: Md. Imran Hossain Jony, Md. Moshiur Rahmanshiva kumarОценок пока нет

- This Set of 8051 MicroДокумент21 страницаThis Set of 8051 MicroSonaliОценок пока нет

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsОт EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsОценок пока нет

- BSC HTM - TourismДокумент4 страницыBSC HTM - Tourismjaydaman08Оценок пока нет

- Head Coverings BookДокумент86 страницHead Coverings BookRichu RosarioОценок пока нет

- Global Divides: The North and The South: National University Sports AcademyДокумент32 страницыGlobal Divides: The North and The South: National University Sports AcademyYassi CurtisОценок пока нет

- BrochureДокумент3 страницыBrochureapi-400730798Оценок пока нет

- Radon-222 Exhalation From Danish Building Material PDFДокумент63 страницыRadon-222 Exhalation From Danish Building Material PDFdanpalaciosОценок пока нет

- MultiLoadII Mobile Quick Start PDFДокумент10 страницMultiLoadII Mobile Quick Start PDFAndrés ColmenaresОценок пока нет

- The Covenant Taken From The Sons of Adam Is The FitrahДокумент10 страницThe Covenant Taken From The Sons of Adam Is The FitrahTyler FranklinОценок пока нет

- PDF Chapter 5 The Expenditure Cycle Part I Summary - CompressДокумент5 страницPDF Chapter 5 The Expenditure Cycle Part I Summary - CompressCassiopeia Cashmere GodheidОценок пока нет

- W25509 PDF EngДокумент11 страницW25509 PDF EngNidhi SinghОценок пока нет

- Dermatology Skin in Systemic DiseaseДокумент47 страницDermatology Skin in Systemic DiseaseNariska CooperОценок пока нет

- Cisco UCS Adapter TroubleshootingДокумент90 страницCisco UCS Adapter TroubleshootingShahulОценок пока нет

- QSP 04bДокумент35 страницQSP 04bakrastogi94843Оценок пока нет

- SweetenersДокумент23 страницыSweetenersNur AfifahОценок пока нет

- WBДокумент59 страницWBsahil.singhОценок пока нет

- Bullshit System v0.5Документ40 страницBullshit System v0.5ZolaniusОценок пока нет

- Prevention of Waterborne DiseasesДокумент2 страницыPrevention of Waterborne DiseasesRixin JamtshoОценок пока нет

- KsДокумент5 страницKsnurlatifahОценок пока нет

- PresentationДокумент27 страницPresentationMenuka WatankachhiОценок пока нет

- SachinДокумент3 страницыSachinMahendraОценок пока нет

- 20-Admission of PatientДокумент3 страницы20-Admission of Patientakositabon100% (1)

- 2022 Mable Parker Mclean Scholarship ApplicationДокумент2 страницы2022 Mable Parker Mclean Scholarship Applicationapi-444959661Оценок пока нет

- Cisco BGP ASPATH FilterДокумент115 страницCisco BGP ASPATH FilterHalison SantosОценок пока нет

- Application Form InnofundДокумент13 страницApplication Form InnofundharavinthanОценок пока нет

- Jackson V AEGLive - May 10 Transcripts, of Karen Faye-Michael Jackson - Make-up/HairДокумент65 страницJackson V AEGLive - May 10 Transcripts, of Karen Faye-Michael Jackson - Make-up/HairTeamMichael100% (2)

- DBMS Lab ManualДокумент57 страницDBMS Lab ManualNarendh SubramanianОценок пока нет

- 50114a Isolemfi 50114a MonoДокумент2 страницы50114a Isolemfi 50114a MonoUsama AwadОценок пока нет

- MMS - IMCOST (RANJAN) Managing Early Growth of Business and New Venture ExpansionДокумент13 страницMMS - IMCOST (RANJAN) Managing Early Growth of Business and New Venture ExpansionDhananjay Parshuram SawantОценок пока нет