Академический Документы

Профессиональный Документы

Культура Документы

Viper22a Equivalent PDF

Загружено:

Xande Nane SilveiraИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Viper22a Equivalent PDF

Загружено:

Xande Nane SilveiraАвторское право:

Доступные форматы

AN1715 - APPLICATION NOTE

VIPower: SMPS Solutions for Power Line Modem Application with VIPerX2A

F. Cacciotto - F. Gennaro - M. Sciortino

1. ABSTRACT This application note investigates about possible power supply solutions based on VIPerX2A family, realized in order to power a Power Line Modem System (PLMS). As a starting point, the power supplies have been designed and developed according to the specifications for a complete PLMS based on ST7538 (by STMicroelectronics), but other diffused PLMS can be suitably supplied.

2. INTRODUCTION The growth of the automation system in home appliance has brought the development of systems able to exchange information using the electrical network as a communication medium. As a result, there is no need to install extra control cable and all the system components can be connected to the network by plugging them in a wall socket. These virtual networks also improve the flexibility and the expansibility of the system, since new devices can be instantly connected to the system by means of a wall socket. New dedicated modem integrated circuits have been developed in order to make these applications feasible. A typical PLMS is shown in figure 1. The Power Line Modem (PLM) is a half duplex asynchronous FSK modem with a carrier frequency complying with Europes CENELEC EN50065 standard, which specifies the use of carrier frequencies from 125kHz to 140kHz for home automation and US FCC regulations, which specifies the use of carrier frequencies lower than 450kHz. The Power Line Interface (PLI) connects the PLM to the power lines. It consists in a line driver, which amplifies the Analog Transmit Output signal (ATO) from the PLM and a line interface, which adapts the line driver to the power line and insulates the PLMS from the electrical network. Some PLMs directly integrate the line interface on the chip. The PLI has the following functions: - TX Mode: amplifies and filters the transmit signal from the ATO; - RX Mode: provides received signal from power lines to the Receive Analog Input (RAI). The PLM is connected to a microcontroller or to a Personal Computer (through the RS232 driver interface), in order to build a home LAN, where each device is able to use any information required whether it is local (washing machine) or remote (remote control system). In the previous typical application, the power supply has to be able to provide a single output. 3. VIPerX2A DESCRIPTION The VIPerX2A family is a range of smart power devices with current mode PWM controller, start-up circuit and protections integrated in a monolithic chip using VIPower M0 Technology.

May 2003

1/16

AN1715 - APPLICATION NOTE

Figure 1: Power Line Modem: System configuration

Mains 50/60 Hz

PLMS

PLMS

Switch Mode Power Supply

+10V

+5V +5V DV CC AV CC

+5V LDO Regulator

Washing machine

Remote Control System

Power Line Modem

Power Driver Analog Front End

Line interface

Power Line Modem System (PLMS)

The VIPerX2A family includes: - VIPer12A, with a 0.4A peak drain current limitation and 730V breakdown voltage; - VIPer22A, with a 0.7A peak drain current limitation and 730V breakdown voltage. The switching frequency is internally fixed at 60kHz by the integrated oscillator of the VIPerX2A. The internal control circuit offers the following benefits: - Large input voltage range on the VDD pin accommodates changes in auxiliary supply voltage; - Automatic burst mode in low load condition; - Overtemperature, overcurrent and overvoltage protection with auto-restart. The internal current mode structure is shown in figure 2. The feedback pin (FB pin) is sensitive to current and controls the operation of the device. The Power MOSFET delivers a sense current IS which is proportional to the drain current ID. R2 receives this current and the current coming from the FB pin. The voltage across R2 is then compared to a fixed reference voltage of 0.23 V.

2/16

AN1715 - APPLICATION NOTE

Figure 2: VIPerX2A current internal structure

DRAIN

60kHz Oscillator

S ID

+VDD

PWM Q LATCH

R

Secondary feedback 0.23V

IFB 1k R1 230 R2

IS

FB

SOURCE

The mosfet is switched off when the following condition is reached:

R 2 (I S + I FB ) = 0.23V

Using the current sense ratio of the mosfet, GID and considering (1), ID is given by:

0.23V I D = G ID I S = G ID I FB R 2

(1)

(2)

The FB pin is commonly driven by the emitter of an optocoupler but a discrete BJT or a zener diode can also be used, behaving as a current source. This current is filtered by a small capacitor C to guarantee the feedback stability. It is necessary to keep this capacitor very close to the FB pin, to avoid high frequency instability on the compensation loop. For low drain currents, (2) applies as long as IFB<IFBsd, where IFBsd is an internal threshold of the VIPerX2A. If IFB exceeds this threshold, the device will stop switching. When the output load is decreased and the regulation loop increases the FB current to reach the IFBsd threshold, the device enters burst mode operation by skipping switching cycles and, consequently, reducing the average switching frequency. This is achieved when the power drained by the load goes below:

POUT =

(V

IN DC(min)

t ON(min) )

2L

f SW

(3)

This feature is especially important when the converter is lightly loaded, in order to have very low input power consumption.

3/16

AN1715 - APPLICATION NOTE

4. POWER SUPPLY DESCRIPTION AND DESIGN The SMPS specifications are listed in table 1. Table 1: SMPS specifications.

Input Voltage VOUT IOUT(min) IOUT(max) 185VAC 265VAC 10V 25% 23mA in RX mode 480mA in TX mode

Due to the low power related to the RX mode, as low as possible switching frequency can be chosen, in order to have higher order harmonics in the carrier frequency band. The only way to reduce the switching frequency is to optimise the burst mode operation. 4.1. Clamp Design The drain voltage needs to be clamped in order to prevent voltage spikes, due to leakage inductance, from exceeding the breakdown voltage of the device (730V minimum). The most used solution is the RCD clamp, as shown in figure 3a. This is a very simple and cheap solution, but it impacts on the efficiency even at no load condition. If the standby efficiency is important, a zener clamp is recommended, as shown in figure 3b. However such a solution gives higher power dissipation at full load, even if the clamp voltage is exactly defined. Figure 3: Clamp circuit topology: (a) RCD clamp and (b) Zener clamp

RCD CLAMP . R C +

ZENER CLAMP .

Dz +

(a)

(b)

The capacitor value is calculated in order to charge it with the energy from the leakage inductance and must ensure that the maximum VSPIKE is never exceeded, thus from energy balance consideration, the minimum capacitance value is:

L LK I 2 DLIM 2 (VSPIKE + VR ) 2 VR

(4)

4/16

AN1715 - APPLICATION NOTE

In order to have a proper operation of the clamp, the minimum value of resistance is:

1 VSPIKE f SW C ln 1 + V R

(5)

Its power rating will be:

PR =

2 VR 1 + L LK I 2 f SW DLIM R 2

(6)

For a zener clamp, the zener voltage should be:

VZ = VR + VSPIKE

with a power capability equal to:

(7)

PZ =

VZ 1 L LK I 2 f SW DLIM 2 VZ VR

(8)

5. APPLICATION DESCRIPTION In this chapter, two solutions are presented in order to power a typical PLMS in both isolated and non isolated applications. The first configuration is typical in home automation systems and the last is suitable for many industrial applications. The regulation is obtained by means of a zener diode in either solution, considering the high output voltage tolerance for this application. The transformer has been designed with lower primary inductance compared to a typical 5W application. This enables the device to work in burst mode during RX condition, reducing the average switching frequency. 5.1. Isolated Solution The first proposed solution regards the isolated Flyback topology with a single input rectifier diode and an input C-L-C filter. Such a filter provides both DC voltage stabilization and EMI filtering. In the considered application, the transformer has a secondary winding with galvanic insulation and an auxiliary winding to supply the VIPer. In table 2 the transformer specifications are listed and the converter schematic is shown in figure 4. Table 2: Isolated transformer specifications

Core geometry Core material BSAT Air Gap Primary Inductance Leakage Inductance Primary Winding Auxiliary Winding Output Winding E13/7/14 N27 or equivalent 380mT 0.24mm 1.8mH 54H 166 turns 52 turns 22 turns

5/16

AN1715 - APPLICATION NOTE

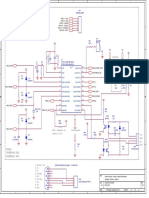

The converter has been tested in several load conditions and in the whole input voltage range, i.e. from 185VAC to 265VAC. Load and line regulation results are shown in figure 5 and figure 6 respectively. The efficiency measurement has been done using a DC power source and an amperometer, in order to have a higher accuracy than in AC measurements: the results are shown in figure 7. In all the considered operating conditions, the converter meets the specifications given in table 1. Figure 4: Isolated Flyback converter

R-fuse AC IN 10

D1 1N4007

L1 470uH R1 1.2k R2 150k STTH106 D2 D3 BAS21 C5 100pF

TF1

BYW100-200 D4

L2 22uH

+10V

C6 470uF

C7 47uF

GND OUT + C1 4.7uF + C2 4.7uF

VDD DRAIN

R4 220

+ C3 10uF

FB

CONTROL

OPT PC817

SOURCE

VIPer12A DZ1 8.2V

C4 47nF AC IN

C8 2.2nF-2kV/Y2

Figure 5: Load Regulation

9.8

185V 220V 265V

9.6

9.4

VOUT (V)

9.2

9.0

8.8 0 100 200 300 400 500

IOUT (mA)

6/16

AN1715 - APPLICATION NOTE

Figure 6: Line Regulation

10,0

Rx Mode Full load

9,5

VOUT (V)

9,0 8,5 180

200

220

240

260

280

VINAC(V)

Figure 7: Efficiency Vs. output current

100

185V 230V 265V

90

80

Efficiency (%)

70

60

50

40 0 100 200 300 400 500

IOUT (mA)

In figures. 8, 9 and 10 typical waveforms in RX mode and full load are shown: it is important to point out that, in RX Mode, the converter works in burst mode, limiting the maximum switching frequency to 30kHz. The startup transient is shown in figure 11. The maximum drain voltage has been measured under worstcase operations, i.e. start-up at VIN=265VAC and full load. The maximum measured value is 594V, as shown in figure 11(b) and the output voltage ripple at full load and VIN=230VAC is shown in figure 12.

7/16

AN1715 - APPLICATION NOTE

Figure 8: Typical waveforms at 185VAC: (a) RX mode and (b) Full load

Ch1 Freq 29.41kHz Ch1 Freq 14.65kHz Ch1 Max 376V Ch2 Max 140mA (a)

Ch1 Freq 58.40kHz Ch1 Max 444V Ch2 Max 304mA (b)

Figure 9: Typical waveforms at 230VAC: (a) RX mode and (b) Full load

Ch1 Freq 29.41kHz Ch1 Freq 14.67kHz Ch1 Max 444V Ch2 Max 156mA (a)

Ch1 Freq 58.19kHz Ch1 Max 504V Ch2 Max 296mA (b)

8/16

AN1715 - APPLICATION NOTE

Figure 10: Typical waveforms at 265VAC: (a) RX mode and (b) Full load

Ch1 Freq 29.41kHz Ch1 Freq 14.65kHz Ch1 Max 500V Ch2 Max 164mA (a)

Ch1 Freq 58.22kHz Ch1 Max 560V Ch2 Max 296mA (b)

Figure 11: (a) Start up time at 230VAC and (b) VDS during start-up at 265VAC at full load

VDD

VOUT VDS

Ch1 Max 524V Ch2 Max 17.1V Ch3 Max 9.2V

Ch1 Freq 59.74kHz Ch1 Max 594V

(a)

(b)

9/16

AN1715 - APPLICATION NOTE

Figure 12: Output voltage ripple at 230VAC and full load

5.2. Non Isolated Flyback Description For non-isolated applications, the following solution can be used. The transformer specifications are the previous ones, but galvanic insulation and auxiliary winding are not required. The converter schematic is shown in figure 13. The VDD voltage is provided rectifying the transformer output voltage. This allows to have a supply voltage higher of 0.8V (forward voltage drop on D4), avoiding a VDD lower than VDDoff(MAX)=9V. Figure 13: Non isolated Flyback converter

R2 AC IN 1k R1 10 D1 1N4007 L1 470uH DZ1 9.1V D2 1N4148 D3 STTH106 + C3 10uF GND OUT BYW100-200 D4 R2 150k C5 100pF C6 470uF + C7 47uF + L2 22uH +10V

TF1

C1 4.7uF 400V

+ C2 4.7uF 400V

VIPer12A

VDD DRAIN

FB C4 10nF AC IN

CONTRO L

SOURCE

10/16

AN1715 - APPLICATION NOTE

Load and line regulation results are shown in figures 14 and 15 respectively, while the efficiency is shown in Figure 16. The converter shows good performance concerning the output voltage regulation, with efficiency higher than 75% at full load. Figure 14: Load Regulation

10,6

185V 220V 265V

10,4

10,2

VOUT (V)

10,0

9,8

9,6 0 100 200 300 400 500

IOUT (mA)

Figure 15: Line Regulation

11,0

Rx Mode Full load

10,5

VOUT (V)

10,0

9,5

9,0 180

200

220

240

260

280

VINAC (V)

11/16

AN1715 - APPLICATION NOTE

Figure 16: Efficiency Vs. output current

100

185V 230V 265V

90

80

Efficiency (%)

70

60

50

40 0 100 200 300 400 500

IOUT (mA)

In figures 17, 18 and 19 typical waveforms in RX mode and full load are shown: even in this case, in RX Mode, the converter works in burst mode, with a maximum switching frequency of 30kHz. The startup transient is shown in figure 20. The maximum drain voltage has been measured under worstcase operations, i.e. start-up @VIN=265VAC and full load. The maximum measured value is 612V, as shown in figure 20(b) and the output voltage ripple at full load and VIN=230VAC is shown in figure 21. Figure 17: Typical waveforms at 185VAC: (a) RX and (b) Full load

Ch1 Freq 19.84kHz Ch1 Freq 29.33kHz Ch1 Max 380V Ch2 Max 112mA

12/16

Ch1 Freq 58.47kHz Ch1 Max 454V Ch2 Max 312mA (a) (b)

AN1715 - APPLICATION NOTE

Figure 18: Typical waveforms at 230VAC: (a) RX mode and (b) Full load

Ch1 Freq 29.07kHz Ch1 Freq 19.52kHz Ch1 Max 456V Ch2 Max 128mA (a)

Ch1 Freq 58.23kHz Ch1 Max 518V Ch2 Max 304mA (b)

Figure 19: Typical waveforms at 265VAC: (a) RX mode and (b) Full load

Ch1 Freq 29.76kHz Ch1 Freq 14.67kHz Ch1 Max 512V Ch2 Max 128mA (a)

Ch1 Freq 58.11kHz Ch1 Max 570V Ch2 Max 304mA (b)

13/16

AN1715 - APPLICATION NOTE

Figure 20: (a) Start up time at 230VAC and (b) VDS during start-up at 265VAC at full load

VDD

VOUT VDS

Ch1 Max 548V Ch2 Max 15.2V Ch3 Max 10.3V (a)

Ch1 Freq 60.11kHz Ch1 Max 612V (b)

Figure 21: Output voltage ripple at 230VAC and full load

7. SPECTRUM FREQUENCY COMPARISON If lower switching frequency is required during RX mode due to interference issues, the primary inductance of the transformer has to be reduced down to 800H, resulting in a higher drain peak current. This imposes a higher drain current capability device such as the VIPer22A, whose minimum peak drain current is of 560mA. In figure 22 the comparison between the solutions with VIPer12A and VIPer22A is shown: it is important

14/16

AN1715 - APPLICATION NOTE

to point out that, due to the lower primary inductance, the converter with VIPer22A in burst mode works with a lower average switching frequency respect to the solution using VIPer12A, but with a higher peak drain current. The harmonic current spectra for the two converters are shown in figure 23 and 24 respectively. It is possible to note that, in the frequency range up to 200kHz, the current harmonics amplitudes in the VIPer22A converter are lower than VIPer12A converter. This can give less interference issues when the PLMS works in RX mode. Figure 22: Typical waveforms at 185VAC in RX Mode: (a) with VIPer12A and (b) with VIPer22A

Ch1 Freq 19.84kHz Ch1 Freq 29.33kHz Ch1 Max 380V Ch2 Max 112mA (a) Figure 23: Harmonic current spectrum with VIPer12A

25

Ch1 Freq 14.79kHz Ch1 Freq 19.70kHz Ch1 Max 334V Ch2 Max 269mA (b)

VIPer12A

20

Amplitude (mA)

15

10

100

200

300

400

500

Frequency (kHz)

15/16

AN1715 - APPLICATION NOTE

Figure 24: Harmonic current spectrum with VIPer22A

25

VIPer22A

20

Amplitude (mA)

15

10

0 0 100 200 300 400 500

Frequency (kHz)

8. CONCLUSION Two solutions have been introduced in order to power a PLMS based on ST7538 chip specifications. The power supplies have been designed and developed using the VIPower device VIPer12A, since it represents the device of choice for the considered output power level in terms of performance and price. The main result of this investigation is that the proposed power supply performs well in terms of line and load regulation, working in burst mode when the PLMS works in RX mode, thus reducing the maximum switching frequency to 30kHz. Using VIPer22A it is possible to reduce the average burst switching frequency to 19KHz, since a transformer with a lower primary inductance than VIPer12A converter can be chosen. Even if this device is more expensive compared to VIPer12A, the performance in terms of frequency reduction will be improved and, consequently, the interference with the PLMS will be reduced.

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may results from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics. The ST logo is a trademark of STMicroelectronics 2003 STMicroelectronics - Printed in ITALY- All Rights Reserved. STMicroelectronics GROUP OF COMPANIES Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A. http://www.st.com

16/16

Вам также может понравиться

- Project Report Speed Control of Induction MotorДокумент47 страницProject Report Speed Control of Induction Motorsrajaprojects0% (1)

- Pe 194802B Philips Manual DatasheetДокумент14 страницPe 194802B Philips Manual DatasheetMárcio FernandesОценок пока нет

- Kirisun PT8100-Service-ManualДокумент35 страницKirisun PT8100-Service-ManualRobertino100% (1)

- DSE9701 & DSE9702: Vertical 5 Amp Battery ChargersДокумент2 страницыDSE9701 & DSE9702: Vertical 5 Amp Battery Chargersasuhuane100% (1)

- Aoc E936swa Service ManualДокумент51 страницаAoc E936swa Service ManualClaudio Robson TobiasОценок пока нет

- Manual Relé GEДокумент16 страницManual Relé GEPablo Briceño NavarroОценок пока нет

- SKIIP09NAC125IT45Документ1 страницаSKIIP09NAC125IT45Charoon SuriyawichitwongОценок пока нет

- LG Bh9520twДокумент147 страницLG Bh9520twdanielradu27100% (1)

- LG 47lm6400Документ156 страницLG 47lm6400Boniface AsuvaОценок пока нет

- Sp431 High Voltage Adjustable Precision Shunt RegulatorsДокумент11 страницSp431 High Voltage Adjustable Precision Shunt Regulatorsagmnm1962Оценок пока нет

- SEKO Kompact PDFДокумент4 страницыSEKO Kompact PDFRuber TorresОценок пока нет

- MR MESSKO - Digital Thermometer EPT202Документ4 страницыMR MESSKO - Digital Thermometer EPT202OpscenarJMD100% (1)

- BA5927SДокумент10 страницBA5927SHugo VelozОценок пока нет

- Data SheetДокумент16 страницData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣОценок пока нет

- Compair Manual 312278518500Документ13 страницCompair Manual 312278518500zeewox100% (1)

- Datasheet Rele General ElectricДокумент45 страницDatasheet Rele General Electriclfierro_2Оценок пока нет

- Multilin f650Документ533 страницыMultilin f650๖ۣۜLUÂN ๖ۣۜNGUYỄN 卍Оценок пока нет

- Semp Toshiba Manual de Servico PDFДокумент49 страницSemp Toshiba Manual de Servico PDFAnildo Eldivar De Oliveira SarmentoОценок пока нет

- Samsung 633nw Ls16cmy SCHДокумент10 страницSamsung 633nw Ls16cmy SCHrenanОценок пока нет

- EVS XT3 ManualДокумент201 страницаEVS XT3 ManualnickgnatОценок пока нет

- D 450Документ6 страницD 450Jose Benavides100% (1)

- UPS700 657Документ6 страницUPS700 657Marcio Antonio MachadoОценок пока нет

- Preliminary: Fagor Automation, S.CoopДокумент32 страницыPreliminary: Fagor Automation, S.CoopRogério PereiraОценок пока нет

- Dokumen - Tips Simoreg K 6ra22 Analog Chassis Converters Siemens Ramp Downtimesareadjust AbleviaapotentiometertheДокумент64 страницыDokumen - Tips Simoreg K 6ra22 Analog Chassis Converters Siemens Ramp Downtimesareadjust Ableviaapotentiometertheomar tlebОценок пока нет

- WEG CFW 11 Variable Speed Drives1Документ32 страницыWEG CFW 11 Variable Speed Drives1Marco PosadaОценок пока нет

- Esquema La-E993pДокумент78 страницEsquema La-E993pc4rl0slinuxОценок пока нет

- PTM-6V English v1.00Документ14 страницPTM-6V English v1.00Mohd SamirОценок пока нет

- Manual de Variador de Velocidad WEG VECTORДокумент32 страницыManual de Variador de Velocidad WEG VECTORSamuel Miranda PintoОценок пока нет

- Omron CablesДокумент13 страницOmron CablescomantonioОценок пока нет

- SPECS UPS Link ProtocolДокумент37 страницSPECS UPS Link Protocolindians jonesОценок пока нет

- 5V DC To 48V DC Converter For Phantom Power SuppliesДокумент3 страницы5V DC To 48V DC Converter For Phantom Power SuppliesHasan AlatasОценок пока нет

- Samsung Bn44-00369a PDFДокумент2 страницыSamsung Bn44-00369a PDFAnalia Grilli100% (1)

- Modular PLC XC-CPU201-... (-XV) XC-CPU202-... - XV: User ManualДокумент156 страницModular PLC XC-CPU201-... (-XV) XC-CPU202-... - XV: User ManualIonel RacaruОценок пока нет

- Sirius10 120Документ40 страницSirius10 120Nicoleta Sima67% (3)

- 35N06 PDFДокумент4 страницы35N06 PDFMy LifeОценок пока нет

- Termistor NTC Mf73t-1Документ4 страницыTermistor NTC Mf73t-1Tatys SoleОценок пока нет

- EM 231 TC 8AI eДокумент4 страницыEM 231 TC 8AI eJaime Saldias0% (1)

- Celdas de CargasДокумент120 страницCeldas de CargasRafael RogelОценок пока нет

- Washer Extractors: W4130S, W4180S, W4250SДокумент2 страницыWasher Extractors: W4130S, W4180S, W4250SHanif Harun100% (1)

- Discontinued Belimo Products Valve Actuators-1 PDFДокумент2 страницыDiscontinued Belimo Products Valve Actuators-1 PDFJasonОценок пока нет

- My Graduation Project Final ReportДокумент66 страницMy Graduation Project Final Reportsiva129Оценок пока нет

- Flowpet 5GДокумент56 страницFlowpet 5GOoi Ban JuanОценок пока нет

- Danfoss VLT 6000 SeriesДокумент3 страницыDanfoss VLT 6000 SeriesnansusanОценок пока нет

- Voltage Transducer LV 25-400 400 VДокумент3 страницыVoltage Transducer LV 25-400 400 Vtichtruong77Оценок пока нет

- Smi2000hd enДокумент4 страницыSmi2000hd enTran Hong HiepОценок пока нет

- VIRDI AC5000 Installation GuideДокумент20 страницVIRDI AC5000 Installation Guidecarlos sousaОценок пока нет

- Semikron Datasheet Skiip 25ac126v1 25230090Документ4 страницыSemikron Datasheet Skiip 25ac126v1 25230090elias100% (1)

- Ic 693 Cpu 313Документ5 страницIc 693 Cpu 313mubashersaeedОценок пока нет

- B43876S9478M 1 - Ed5Документ3 страницыB43876S9478M 1 - Ed5Mauricio BaronОценок пока нет

- Jj-Crc-I11 Userguide: Z Frequency 433.92Mhz Z Indicator Light Blue Led Z Working Voltage DC 12VДокумент1 страницаJj-Crc-I11 Userguide: Z Frequency 433.92Mhz Z Indicator Light Blue Led Z Working Voltage DC 12VMishaCvele100% (1)

- Esq Nobreak T0319500 Net SensationДокумент1 страницаEsq Nobreak T0319500 Net SensationrenanОценок пока нет

- Datasheet LD7523 PDFДокумент18 страницDatasheet LD7523 PDFIvica ConićОценок пока нет

- Maquina de Instrumentação PDFДокумент4 страницыMaquina de Instrumentação PDFhecirlene vieiraОценок пока нет

- AT90S8535 Programmer: Suitable For In-System UseДокумент3 страницыAT90S8535 Programmer: Suitable For In-System UseTariq ZuhlufОценок пока нет

- Aoz1212ai PDFДокумент18 страницAoz1212ai PDF060279Оценок пока нет

- Acopos PDFДокумент19 страницAcopos PDFHoàng Mỹ NguyễnОценок пока нет

- Siemens Micromaster Eco ManualДокумент181 страницаSiemens Micromaster Eco ManualMohammad Imtiaz ChowdhuryОценок пока нет

- Viper 100 AДокумент31 страницаViper 100 AvasilesicoeОценок пока нет

- VIPower: 10W POWER SMPS USING VIPer22A FOR AIR-CONDITIONER APPLICATIONДокумент8 страницVIPower: 10W POWER SMPS USING VIPer22A FOR AIR-CONDITIONER APPLICATIONLullaby summerОценок пока нет

- AND8241/D A 5.0 V/2.0 A Standby Power Supply For INTEL Compliant ATX ApplicationsДокумент16 страницAND8241/D A 5.0 V/2.0 A Standby Power Supply For INTEL Compliant ATX ApplicationsJonatan LunaОценок пока нет

- Äñ Æ÷Éè Æ Ó ©Документ6 страницÄñ Æ÷Éè Æ Ó ©Rachel RowlandОценок пока нет

- Onsm S A0013274851 1Документ6 страницOnsm S A0013274851 1Santhosh H AОценок пока нет

- SMPS and Linear Power Supply ComparisonДокумент5 страницSMPS and Linear Power Supply ComparisonSusan BowenОценок пока нет

- NTC 220 - 50 Manual Rev00Документ57 страницNTC 220 - 50 Manual Rev00Xuân NHОценок пока нет

- Isolated Zeta Converter: Principle of Operation and Design in Continuous Conduction ModeДокумент10 страницIsolated Zeta Converter: Principle of Operation and Design in Continuous Conduction ModejhntfghkmОценок пока нет

- Lab Gruppen Lab 1300c Manual de UsuarioДокумент12 страницLab Gruppen Lab 1300c Manual de UsuarioAndoniainaRakotoarimananaОценок пока нет

- PsbookДокумент171 страницаPsbookGovinda RajОценок пока нет

- ONSemi-Developing A 25-kW SiC-Based Fast DC Charger Solution Overview4Документ16 страницONSemi-Developing A 25-kW SiC-Based Fast DC Charger Solution Overview4133514Оценок пока нет

- Smps TДокумент1 страницаSmps Tv5groupОценок пока нет

- AN4134 Designing Forward SmpsДокумент14 страницAN4134 Designing Forward SmpsGrzegorz WegnerОценок пока нет

- Fa5553/5547 Series of PWM Control Power Supply Ics With Multi-Functionality and Low Standby PowerДокумент6 страницFa5553/5547 Series of PWM Control Power Supply Ics With Multi-Functionality and Low Standby PowerCesar AzcargortaОценок пока нет

- Project On Accounts ReceivableДокумент61 страницаProject On Accounts ReceivableNilesh JhaОценок пока нет

- ETS1201 Series Fixed Wireless Terminal Maintenance ManualДокумент34 страницыETS1201 Series Fixed Wireless Terminal Maintenance ManualRumesha TharindiОценок пока нет

- Improved Modulation Strategy Using Dual Phase Shift Modulation For Active Commutated Current-Fed Dual Active BridgeДокумент4 страницыImproved Modulation Strategy Using Dual Phase Shift Modulation For Active Commutated Current-Fed Dual Active BridgeBrightworld ProjectsОценок пока нет

- Printed On Recycled PaperДокумент11 страницPrinted On Recycled PaperVictor SampaОценок пока нет

- PROWATCHER Power Supply PricelistДокумент12 страницPROWATCHER Power Supply PricelistRAMJETОценок пока нет

- Dap011 DДокумент24 страницыDap011 Dsontuyet82Оценок пока нет

- DAVR Training ManualДокумент66 страницDAVR Training ManualAhemad100% (1)

- USB3 Accelerator Module DatasheetДокумент22 страницыUSB3 Accelerator Module DatasheetSourabh SaikiaОценок пока нет

- T3000 Thermal Power SupplyДокумент44 страницыT3000 Thermal Power Supplyronal552Оценок пока нет

- ΠαλμοτροφοδοτικάДокумент14 страницΠαλμοτροφοδοτικάVasilis ChrimatopoulosОценок пока нет

- Naka RegДокумент454 страницыNaka RegRoshan RivaldgeОценок пока нет

- Literature Review of D ProjectДокумент17 страницLiterature Review of D ProjectPhani Kiran100% (1)

- Automotive Electronics SolutionsДокумент36 страницAutomotive Electronics Solutionssorteabhay6877Оценок пока нет

- AI Based Controller For Three Phase Three Level, Soft Switched, Phase Shift PWM DC To DC Converter For High Power ApplicationДокумент7 страницAI Based Controller For Three Phase Three Level, Soft Switched, Phase Shift PWM DC To DC Converter For High Power ApplicationJyothiPunemОценок пока нет

- (3L) Single-Phase Three-Level Boost Power Factor Correction ConverterДокумент6 страниц(3L) Single-Phase Three-Level Boost Power Factor Correction ConverterQuickerManОценок пока нет

- SDA10-4850DC Iron Lithium Battery Integrated System enДокумент2 страницыSDA10-4850DC Iron Lithium Battery Integrated System enFrancisco TorrealbaОценок пока нет

- Vestel DVD 6000Документ19 страницVestel DVD 6000tlw72Оценок пока нет

- Viper 100Документ8 страницViper 100SeanОценок пока нет