Академический Документы

Профессиональный Документы

Культура Документы

EE 244 Tutorial For Programming The BASYS

Загружено:

Flo87Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

EE 244 Tutorial For Programming The BASYS

Загружено:

Flo87Авторское право:

Доступные форматы

EE 244 Tutorial for programming the BASYS-2 FPGA board Hello there and welcome to the basic tutorial

on how to program the BASYS-2 board for your EE 244 class. Using this board and the following examples, this will allow you to upload your own Verilog code into the FPGA in order to assist in learning digital logic. In order to program the BASYS-2 FPGA, two software packages will be required. The first is a Free Webpack available from Xilinx. The link to download the free software is listed below: http://www.xilinx.com/products/design-tools/ise-design-suite/ise-webpack.htm The second software is for uploading and downloading the program, register data and I/O to and from the FPGA. The Adept software is specifically configured for the BASYS-2 FPGA boards, complete with auto-detection of the FPGA when plugged in via USB port, test verification for board functionality, and I/O. The software can be downloaded from the link below: http://www.digilentinc.com/Products/Detail.cfm?NavPath=2,66,828&Prod=ADEPT2 For the board to work properly to display the results of the formula, the code to program the FPGA will be distributed to you for uploading to the FPGA and for the demonstration of Boolean Logic such as gates and a simple calculator. Sample code will be available for you to download. The files will be made available via USB drive. So a USB drive or laptop is recommended for you to obtain the files necessary for the FPGA. The modules are as follows for the following modules for loading into the FPGA: Calculator_bit: A 1-bit calculator (simple add and subtract) Calculator_vNR: 2-bit calculator Calculator_vR: 4-bit calculator DecoderH: high-enabled (1) decoder DecoderL: low-enabled (0) decoder Gate_A: AND gate Gate_B: OR gate Gate_C: XOR gate Gate_D: NAND gate Gate_E: NOR gate Gate_F: Invete (NOT) gate

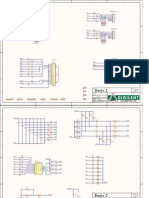

Below is a diagram of the development flow for programming in the BASYS-2 FPGA. Please follow the steps in order to program your own BASYS-2 FPGA properly.

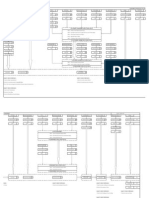

Guidelines for Installation of Software Programs and how to test syntax, compile, generate necessary files and upload to the BASYS-2 FPGA The contents of the DVD disc are as follows: Xilinx SDK 12.4 ISE Webpack (will be suitable for generating bit files), Diligent Adept 2.2 software (for uploading to the BASYS-2 FPGA development board), and Xilinx License for the ISE webpack (for installation on one machine). The files will be shown in a picture below:

Pictured: Files on the DVD. Xilinx ISE 12.4, and Diligent Adept 2.2. Please follow the instructions below to install both the ISE and FPGA uploading software to your machine (Windows based installation below): 1. Click on the Xilinx folder, and run the Xilinx setup (which will have the Xilinx logo and be titled xsetup.exe). The setup.exe file will be at the bottom of the folder as pictured below:

Pictured: Setup.exe highlighted for installing the Xilinx ISE 12.4 software 2. Follow the setup wizard for the installation of the Xilinx ISE webpack software. Once the file is clicked (setup.exe), the following screen will appear:

Pictured: Beginning of Setup for installation of the Xilinx ISE 12.4 program.

3. Accept the terms of the license agreement by clicking the box that states I accept the terms of this software license. Once this is done, the Next button will be available to continue the installation. There will be two (2) license agreement screens to progress through, pictured below:

Pictured: License Agreement and Necessary Buttons (1)

Pictured: License Agreement (2).

4. The next screen will allow you to choose which edition of the Xilinx ISE to install. Please select ISE Webpack from the list of available choices, as pictured below:

Pictured: Edition Choice Window. This will also calculate the amount of disk space the installation will require for your PC. Please make sure the necessary disk space is available on your PC. Once this is done, please click the Next button. 5. Next will be the installation options for the software. Please make sure all options are selected as shown below:

Pictured above: Select Installation Options Once this is done, please click the Next button. 6. After, the Select Destination Directory will appear. The default directory the software will install will be C:\Xilinx\12.4, as shown below:

Pictured Above: Select Destination Directory If you have a previous edition of the software installed, the software will import all necessary files into this version. Please click the Next button.

7. The Options Summary will be displayed summarizing all of the options and functions that were clicked or checked during the setup process. Shown below:

Pictured: Options Summary. To begin the installation of the ISE, please click the Install button. Installation of the Xiline 12.4 ISE will begin. During the installation, a progress bar highlighting the files being installed and the percentage of installation will appear, like so:

Pictured: Installation Progres Screen.

Note: Installation of the software will occur at a fast speed if installed from the Hard Disk Drive (HDD). Please copy the contents of the DVD to your Desktop if you desire to do so. 8. The next step in the installation process will be the WinPCap Ethernet Hardware CoSimulation. This will install the Ethernet drivers for co-simulation for the ISE. Screen shot shown below:

Pictured: WinPcap software installation. Please click the Next button to begin the WinPcap installation process (as part of the Xilinx ISE installation). 9. The Setup Wizard will begin for the WinPcap software, shown below:

Pictured: Setup Wizard for the WinPcap software. Please click the Nextbutton. 10. The License Agreement for the WinPCap software will appear, shown below:

Pictured: License Agreement for PCap. Click the I Agree button to proceed with the installation.

11. The Installation Options window will appear with the option to Automatically Start the WinPcap Driver at Boot Time option selected. Please make sure this option is selected and press the Install button, as shown below:

12. The installation will commence (should take no longer than 1 minute, but your installation time may vary). Once the installation is finished, the following screen will appear:

Pictured: Completed installation for WinPcap.

Click the Finish button to complete the WinPcap installation and continue on with the Xilinx ISE installation. 13. Once this is done, the Xilinx ISE installation will be finished and two windows will appear. One of these windows will be the Jungo Device Driver software. Screen shot of window shown below:

Pictured: Screen shot of Jungo driver installation request. Click the Install button to complete the device driver installation for the ISE. Another window will need to be completed for this tobe complete, which is the Xilinx License Configuration Manager window, shown below:

Pictured: Xilinx License Configuration Manager window Please select the Locate Existing License option in this window and then click the Next button. This will allow you to locate the Xilinx License file (Xilinx.lic) that is present on the DVD. 14. The next window will be under the Manage Xilnx License tab under the Xilinx License Configuration Window, as shown below:

Pictured: The Manage Xilinx License tab under the Xilinx License Configuration Manager.

Press the Copy License button in the upper left of the window. A window will open so that the file can be located. To locate the file on the DVD, please select the DVD drive from your window, like shown below:

Pictured: The window showing the DVD drive where the DVD containing the Xilinx.lic file is located (highlighted in picture above). Once the Xilinx.lic file is highlighted, click the Open button on the window in the lower right as shown above. This will activate the license for the ISE Webpack. If successful, the following window will appear:

Pictured: Successful installation of the ISE webpack license (located on the DVD). Once this is finish, click the OK button. After the license is successfully installed, click the Close button on the Xilinx License Configuration Manager. 15. This concludes the installation of the Xilinx ISE software package and is now available for use. If successful, the screen show below should appear:

Pictured: Successful finished installation of the Xilinx ISE Webpack software. Please click the Finish button to complete the installation.

THIS CONCLUDES THE INSTALLATION OF THE XILINX 12.4 ISE WEBPACK software.

Next will be the installation of the Diligent Adept software to load your .bit files for the BASYS-2 FPGA. Please follow the instructions below: 1. Click on the diligent_adept_system_v2.9.4.exe software application. This will start the setup wizard for the software package. The software is located in the DVD as shown below:

Pictured: Diligent Adept Software 2.9.4 (highlighted in window) Double click on the highlighted file to begin the installation. 2. The Setup Wizard will begin the installation process. The window will be shown below:

Pictured: Diligent Adept Setup Wizard. Please click the Next button. 3. The License Agreement will appear in the next window, as shown below:

Pictured: License Agreement for the Diligent Adept Software. Please click the I Agree button to continue the installation. 4. The next window will be the Choose Components for the installation of the software components, as shown below:

Pictured: Choose Components Window for Diligent Adept Software. It will show the necessary space required for the software to be installed in the lower left hand corner (shown above). Please make sure the necessary space is available on the hard disk drive (HDD). Make sure the Adept Runtime 2.9.4 and Adept Application 2.9.4 options are checked (as shown above). Then once this is complete, click the Next button. For the components to install, please install the Adept Runtime and Adept Application). 5. Shortcuts are optional if you desire. If you would like to have them installed, please chek the box shown below marked Create Quick Launch Shortcuts?, ad shown below:

Pictured: Create Quick Launch Shortcuts option for Setup. Please click the Next button. 6. The Choose Install Location window will appear next, as shown below:

It will also display the required and free space available to install the software. To proceed with the installation (provided the required space for installation is available), click the Install button. The installation of the Diligent Adept Software will begin.

7. The installation process will begin. The progress window for the installation will appear, like below:

Pictured: Installation for the Diligent Adept software progress bar. 8. Once the installation is complete the following window will appear:

Pictured: Completed Diligent Adept software installation. Please click the Next button.

9. The window Completing the Diligent Adept Setup Wizard will appear as shown below:

If you would like to run the Adpt software at this time, and open the Readme file for use of this software, leave the boxes checked (as shown above). If not, deselect these options. Please click the Finish button. This completes the installation of the Diligent Adept software. Below are the steps to generate the necessary .bit files for uploading your work to the BASYS-2 FPGA development boards. 1. Open the ISE webpack (specifically the ISE Design Tools Folder -> Project Navigator). The window shown below will show where the program is located:

Pictured: Location of the Project Navigator program for the Xilinx ISE 12.4 suite. 2. Once the project Navigator is opened, please select New project. The new project window will appear. The Project Navigator is shown below:

Pictured: Project Navigator in the Xilinx ISE 12.4

3. Once the Project Navigator is loaded and ready, click the New project button. A window will appear with the title Create New Project. At this point, please type in the name of the project, as shown below with the Test name:

Pictured: Creation of the New Project window for the Project Navigator. Please leave the top-level source module as HDL. Once this is complete, click the Next button. 4. The Next Window that will appear will be Project Settings. For the BASYS2 FPGA development board, please select the following options: Family: Spartan3E Device: XC3S100E Package: CP132 If done correctly, the window should appear as shown below:

If the settings are correct as detailed above picture, please click the Next button. 5. The Window for the Project Summary will appear. Please review the project summary for the correct settings. The window should appear as below:

Pictured: Project Summary for the Project Navigator Once this is done click the Finish button. This will conclude setting up your project.

Now the next step is to generate the Verilog (.v) file for your project. 1. Create a new file, and select Text File. Then click OK. A screen shot shown below for generating the text file:

2. Follow the design ideology as demonstrated, and finish the coding for the project. 3. Once this is done, SAVE the program. This will convert the text file into a .v file for your project. Screen shot provided below:

Picture: Saving projects for .v file generation in the Project Manager

4. Once this is done, right-click the hierarchy window and select Add Source. Once this is done, you can add your .v file to your project. The screen shot below will highlight the Add Source option:

Pictured: Add Source option for attaching source files to the Project. Once this is done, the Project Navigator will check the .v file for errors. The window for this procedure will be shown as such.

Pictured: Checking .v files for adding source files.

If successful and no errors occur, a green check mark will appear next to the files and then the files will be available to be added to the project. Once this is complete, click the OK button. 5. Now the addition of another file will be done. This file will be called k_map.ucf, which will configure the FPGA pins on the development board accordingly for the project. They will be added in a similar manner to the main project file. Right click under the Hierachy window and select Add Source. The file is highlighted in the screen shot below:

Pictured: Adding the k_map_ucf file for the project. Once the file is selected, press the Open button, and the configuration file for the BASYS2 board will be added to the projet. This file is necessary for the FPGA to execute the project properly. PLEASE DO NOT FORGET IT! 6. Once this is done, a project report will be generated. More options wil be available as well. One of these options will be to generate the necessary files. A window highlighting the Synthesize, Implement Design and Generate Programming File options are shown below:

Click the Synthesize tab under the Process menu. This will synthesize your project and check for errors in your code. Please make sure the project code is correct and free of errors. 7. Once the above is finish, click the Implement Design tab. This will allow the Project Manager to compile your code and implement the design specified by the Verilog (.v) code. 8. Next, click the Generate Programming File. This will generate the.bit (compiled) files for the specified FPGA board for the project. 9. Save the generated .bit files. These files will be the files to be uploaded to the FPGA development board. Now start the Diligent Adept software for the BASYS2FPGA development board 1. Connect the BASYS2 FPGA development board to your PC using the supplied USB cable and turn the FPGA development board in the ON position. It will be lit up as shown below:

Pictured: Connected the Basys2 FPGA development board. 2. Run the Adept software. The software will auto-detect the FPGA. Once detected the FPGA will be listed under the Config tab as shown below:

Pictured: Basys-2 Adept Software window. 3. To upload your file, click the Browse button, and locate the .bit file you would like to upload to the FPGA. Once this file is selected, the file will be available in the drop-down menu next to the Browse button. Screen shot shown below:

Pictured: Browsing for the .bit file to be uploaded to the BASYS2 FPGA development board.

4. The option to use the CCLK instead of the JTAG CLK will appear for the configuration window as shown below:

Pictured: CCLK and JTAG CLK window. Please choose Yes for the CCLK association for the .bit files. The .bit files will then be ready to be loaded into the FPGA. 5. Once the file is selected, press the Program button. This will program the FPGA with the designed code from the project. Also please choose Yes for the CCLK association. A screen shot shown below will show a successful programming of the FPGA:

6. Test the FPGA input switches, LEDs, etc. to verify your code. This concludes how to upload the code to the FPGA.

Вам также может понравиться

- Before You Plug Into Your PC You Must Read This!Документ2 страницыBefore You Plug Into Your PC You Must Read This!Airkid Discomovil JesusОценок пока нет

- WinXP Installation CD Slipstream For Ebox-3300Документ16 страницWinXP Installation CD Slipstream For Ebox-3300shahulpdvОценок пока нет

- 8051 Development BoardДокумент11 страниц8051 Development BoardراجيرحمةربهОценок пока нет

- EasyScopeX Install GuideДокумент12 страницEasyScopeX Install GuideviyikitoОценок пока нет

- Safe Install Instructions PDFДокумент2 страницыSafe Install Instructions PDFSara BookerОценок пока нет

- Wireless Network Card Installation Guide: System RequirementsДокумент2 страницыWireless Network Card Installation Guide: System RequirementsAvinash McaОценок пока нет

- VIDEO 2 PC - Driver Installation Instructions PDFДокумент2 страницыVIDEO 2 PC - Driver Installation Instructions PDFeduinnОценок пока нет

- SQL Ledger InstalationДокумент35 страницSQL Ledger Instalationjohn irsyamОценок пока нет

- Allen BradleyДокумент67 страницAllen BradleyNorasad Rafiq Lim SaariОценок пока нет

- Etabs Install InstructionsДокумент2 страницыEtabs Install InstructionsLeonel AguilarОценок пока нет

- DSEA Technical Note: #040: Updated HQ RIP Plug-In InstallerДокумент4 страницыDSEA Technical Note: #040: Updated HQ RIP Plug-In InstallerodelaineОценок пока нет

- FirmwareДокумент4 страницыFirmwareOctavio Cotillo LubiánОценок пока нет

- Elastix Installation v1.3.2Документ16 страницElastix Installation v1.3.2Juan David García JaimeОценок пока нет

- SAP GUI Installation Guide: Step 1: Download The SAP GUI 7.10 From The Link BelowДокумент8 страницSAP GUI Installation Guide: Step 1: Download The SAP GUI 7.10 From The Link BelowJose ThomasОценок пока нет

- Oracle Applications 11.5.10.2 InstallationДокумент17 страницOracle Applications 11.5.10.2 InstallationBalvinder SinghОценок пока нет

- Vsat Installation Guide ConnexstarДокумент45 страницVsat Installation Guide ConnexstarDanny FernandoОценок пока нет

- How To Install Software and DriversДокумент7 страницHow To Install Software and DriversMohamed Elfatih FaragОценок пока нет

- Emeraude InstallationДокумент8 страницEmeraude InstallationMuntadher MejthabОценок пока нет

- Install EngSolutions RCB V9Документ2 страницыInstall EngSolutions RCB V9Miller UrregoОценок пока нет

- Installation and Usage Guide of The New Generic USB DAC Driver For FiiO PlayersДокумент16 страницInstallation and Usage Guide of The New Generic USB DAC Driver For FiiO PlayersArmando SgabeiОценок пока нет

- GoldenGate Server Setup for Oracle 11gДокумент55 страницGoldenGate Server Setup for Oracle 11gNainika KedarisettiОценок пока нет

- Apis Iq Software Installation v70 enДокумент17 страницApis Iq Software Installation v70 enЕвгений БульбаОценок пока нет

- Leica Install GuideДокумент24 страницыLeica Install GuideTony MackleyОценок пока нет

- Asterisk Installation on Debian 7Документ17 страницAsterisk Installation on Debian 7DanarОценок пока нет

- Program USB Controller BoardДокумент15 страницProgram USB Controller Boardxinuxnt256Оценок пока нет

- Install InstructionДокумент3 страницыInstall InstructionDaniel RosembergОценок пока нет

- Install ETABS Version 9 softwareДокумент2 страницыInstall ETABS Version 9 softwareVictor MazaОценок пока нет

- Sap Install InstructionsДокумент2 страницыSap Install InstructionsSelcuk ZenginОценок пока нет

- WinPIC800programmerUserGuide Include877a Aug09Документ2 страницыWinPIC800programmerUserGuide Include877a Aug09Murali Krishna GbОценок пока нет

- Sneak Circuit Analysis Tool (SCAT) Version 5.3 Installation GuideДокумент14 страницSneak Circuit Analysis Tool (SCAT) Version 5.3 Installation GuideBastra Amirul MadjidОценок пока нет

- TNG UPDATE InstructionsДокумент10 страницTNG UPDATE InstructionsDiogo Alexandre Crivelari CrivelОценок пока нет

- Pxe Wds Server Setup SopДокумент45 страницPxe Wds Server Setup SopAlexandru CureaОценок пока нет

- Ideapad Hard Disk Drive Firmware Update Utility GuideДокумент2 страницыIdeapad Hard Disk Drive Firmware Update Utility Guidetushar patelОценок пока нет

- Make Your Own Customized WindowsXPДокумент32 страницыMake Your Own Customized WindowsXPAmit SonyОценок пока нет

- ReadmeДокумент9 страницReadmeArnab ChakrabartiОценок пока нет

- Descarga, Instalación y Activación de Licencia de TIA Portal V11Документ11 страницDescarga, Instalación y Activación de Licencia de TIA Portal V11Jorge SouzaОценок пока нет

- Install FarineHPI 1.0 ManualДокумент8 страницInstall FarineHPI 1.0 Manualsina20795Оценок пока нет

- ENSC 351 software installation guideДокумент9 страницENSC 351 software installation guidea bОценок пока нет

- Survival Guide For FPGA and Verilog Labs: HOW TO INSTALL XILINX (Already Installed in ECE Lab)Документ23 страницыSurvival Guide For FPGA and Verilog Labs: HOW TO INSTALL XILINX (Already Installed in ECE Lab)saket512Оценок пока нет

- Installation Guide 16.6Документ10 страницInstallation Guide 16.6Ngắng Thuyễn100% (1)

- Install AnsysCivilFEM EngДокумент30 страницInstall AnsysCivilFEM EngHectoreRodriguezlОценок пока нет

- How To Install Native Instruments Download Products (PC)Документ2 страницыHow To Install Native Instruments Download Products (PC)Jonathan BatesОценок пока нет

- Install and Configure AsteriskNOW PBXДокумент12 страницInstall and Configure AsteriskNOW PBXJhonAlexanderОценок пока нет

- Aphelion Imaging Suite-Quick Installation GuideДокумент2 страницыAphelion Imaging Suite-Quick Installation Guidekarina19851Оценок пока нет

- Cleverscope Update USB DriverДокумент8 страницCleverscope Update USB DriverFergus GardnerОценок пока нет

- ReadmeДокумент3 страницыReadmesparda94Оценок пока нет

- Tutorial Win XPДокумент6 страницTutorial Win XPtampalbanОценок пока нет

- Simio Installation NotesДокумент4 страницыSimio Installation NotesvsukrishnaОценок пока нет

- KingSCADA User ManualДокумент500 страницKingSCADA User ManualPedro BortotОценок пока нет

- VIDA DICE Installation GuideДокумент9 страницVIDA DICE Installation GuideBobby TaargüsОценок пока нет

- Aironet340 Jornada720Документ6 страницAironet340 Jornada720meolo2002Оценок пока нет

- Article #12120 - The Exchange KnowledgebaseДокумент3 страницыArticle #12120 - The Exchange KnowledgebasepaulinapevОценок пока нет

- Ses-Cdegs 2k - InstallДокумент7 страницSes-Cdegs 2k - InstallGilberto MejiaОценок пока нет

- Installing Cgtech ProductsДокумент120 страницInstalling Cgtech ProductsPACOEDURNEОценок пока нет

- DASH Setup GuideДокумент10 страницDASH Setup GuideGani AnumandlaОценок пока нет

- DL850 Software Upgrade Procedur June 2012AДокумент2 страницыDL850 Software Upgrade Procedur June 2012AParul MehtaОценок пока нет

- DNVS Licence Manager Installation NotesДокумент21 страницаDNVS Licence Manager Installation NotesMahmoud ElsayedОценок пока нет

- Evaluation of Some Android Emulators and Installation of Android OS on Virtualbox and VMwareОт EverandEvaluation of Some Android Emulators and Installation of Android OS on Virtualbox and VMwareОценок пока нет

- Quality Quality Management SystemsДокумент2 страницыQuality Quality Management SystemsFlo87Оценок пока нет

- Xfmea DfmeaДокумент9 страницXfmea DfmeamaxlentiОценок пока нет

- XilinxДокумент150 страницXilinxchetansrinidhiОценок пока нет

- IntroToSpartanFPGABook PDFДокумент130 страницIntroToSpartanFPGABook PDFAnonymous Wu14iV9dqОценок пока нет

- Basys2 SCHДокумент7 страницBasys2 SCHFlo87Оценок пока нет

- Vernier, Dial, and Electronic Digital Calipers: Session 3Документ40 страницVernier, Dial, and Electronic Digital Calipers: Session 3Emman Bosito100% (1)

- A JIT Lot Splitting Model For Supply Chain Management Enhancing Buyer Supplier Linkage 2003 International Journal of Production EconomicsДокумент10 страницA JIT Lot Splitting Model For Supply Chain Management Enhancing Buyer Supplier Linkage 2003 International Journal of Production EconomicsDaniel Renaldo SimanjuntakОценок пока нет

- Variable Frequency Drive Using IR215xДокумент7 страницVariable Frequency Drive Using IR215xartyomОценок пока нет

- Ma-Mscmt-10 J16Документ5 страницMa-Mscmt-10 J16Dilip BhatiОценок пока нет

- Solution 2 AntennaДокумент7 страницSolution 2 Antennaabdulwahab12100% (1)

- BTSДокумент75 страницBTSgyanesh198450% (2)

- Twice As Sharp Operators ManualДокумент34 страницыTwice As Sharp Operators ManualLeonardo CHTZОценок пока нет

- TF Section - MICET 2016Документ21 страницаTF Section - MICET 2016Eddie D SouzaОценок пока нет

- EA 4b ArchiMate Views and Viewpoints PDFДокумент41 страницаEA 4b ArchiMate Views and Viewpoints PDFanon_834023132Оценок пока нет

- Environmental Quality Control of Emission From Diesel Engines Regulations 1996 - P.U.a 429-96Документ22 страницыEnvironmental Quality Control of Emission From Diesel Engines Regulations 1996 - P.U.a 429-96scribdledeeОценок пока нет

- Saes N 004Документ5 страницSaes N 004Mo'tasem SerdanehОценок пока нет

- LB2 UC30 Data Sheet enUS 80218564235Документ5 страницLB2 UC30 Data Sheet enUS 80218564235Ahmed ShawkyОценок пока нет

- BraginskiiДокумент97 страницBraginskiicordella_francescoОценок пока нет

- Control Valve and Steam Line PDFДокумент19 страницControl Valve and Steam Line PDFRofi MuhammadОценок пока нет

- High Voltage Grease Reduces Wear and ArcingДокумент2 страницыHigh Voltage Grease Reduces Wear and ArcingtlnferreiraОценок пока нет

- Calibration of A Pressure GaugeДокумент6 страницCalibration of A Pressure GaugeThapelo100% (2)

- NX Training Syllabus Module IДокумент5 страницNX Training Syllabus Module IDharaiya HardikОценок пока нет

- Electrostatic and Electromagnetic Forces: Electronic Address: Tim - Henley@mail - Utoronto.caДокумент9 страницElectrostatic and Electromagnetic Forces: Electronic Address: Tim - Henley@mail - Utoronto.caTimothy Murray HenleyОценок пока нет

- Android Tutorial - Broadcast ReceiversДокумент15 страницAndroid Tutorial - Broadcast ReceiversTrieu Ngo HuyОценок пока нет

- Agentur H. Willems: Tel.: +49-421-52009-0 List of Manufacturers Fax: +49-421-545858Документ5 страницAgentur H. Willems: Tel.: +49-421-52009-0 List of Manufacturers Fax: +49-421-545858Trần Minh NhậtОценок пока нет

- Udayanandan, Notes On Tensors PDFДокумент56 страницUdayanandan, Notes On Tensors PDFhristos314Оценок пока нет

- Process Level ChartДокумент2 страницыProcess Level ChartzaidinОценок пока нет

- Aviation Week & Space Technology - September 22, 2014 USAДокумент60 страницAviation Week & Space Technology - September 22, 2014 USAJohn David Hoyos MarmolejoОценок пока нет

- Company Profile: How Aristagloves Became a Leader in Personal Protective EquipmentДокумент16 страницCompany Profile: How Aristagloves Became a Leader in Personal Protective EquipmentNissaaОценок пока нет

- Proposed Rule: Domestic Mail Manual: Domestic Mailing Services New StandardsДокумент45 страницProposed Rule: Domestic Mail Manual: Domestic Mailing Services New StandardsJustia.comОценок пока нет

- Final Defence 2078Документ43 страницыFinal Defence 2078XxxОценок пока нет

- Next Gen Ford Ranger Digital BrochureДокумент10 страницNext Gen Ford Ranger Digital BrochureTri BureauОценок пока нет

- PactFocus Report - Sample - LPGДокумент27 страницPactFocus Report - Sample - LPGIqbal HussainОценок пока нет

- Stoichiometry - Determination of Percent by Mass of NaHCO3 in Alka Seltzer TabletsДокумент6 страницStoichiometry - Determination of Percent by Mass of NaHCO3 in Alka Seltzer Tabletsgabbal009Оценок пока нет

- Air Conditioning Fact SheetДокумент6 страницAir Conditioning Fact SheetrjchpОценок пока нет