Академический Документы

Профессиональный Документы

Культура Документы

Register File Description USING VHDL

Загружено:

Sumeet SauravАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Register File Description USING VHDL

Загружено:

Sumeet SauravАвторское право:

Доступные форматы

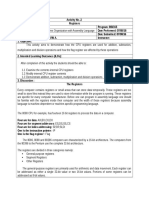

Csc343 LAB Register File

Objective Design a 4*4 register file and test it on VSIM, QUARTUS, and UP3 board. What is a register file A register file is the central storage of a microprocessor. Most operations involve using or modifying data stored in the register file. The register file that will be designed has 4 locations( such as 00,01,10,11). Figure 1 is the suggested block diagram.

figure 1

Our Register File Description If a register file is 4*4, it means we have 4 registers and each register is 4 bits wide. Each cell of the register file, in this case, is constructed by a Dff. Therefore, a register is constructed by 4 DFFs, for example, D1,D2,D3,and D4. Each of the four registers has a clock input (positive edge triggered), a data input, and a data output. This collection of registers is managed by one 2:4 decoder and two4:1 multiplexors. There are two output ports(PortA and PortB) for the register file. Therefore, two registers can be read simultaneously. Each output of the registers is connected to two multiplexors. By changing the Read register number 1 and Read register number 2, 1

we can choose which two registers we want to extract data into the PortA bus and PortB bus. We use clock4(write) combining with and gates to control the register writing. When a clock comes in, a candidate register will be selected to be updated according to which and gates is ON ( on of the input = 1). This is determined by the 2:4 decoder. Compiling and Simulating your register file using VSIM Get the registerfile.vhd file from the Appendix B. You need to input your design of add, dff, and multiplexor into your project and make them as the corresponding names that the registerfile.vhd calls. Design your own test_registerfile.vhd. In your test file designing, first step, generate four clocks and combine the output of the 2:4 decoder(00,01,10,11) to input the data(0000, 1010,0011,1111) into register1, register2, register3, and register4. Then, extract these data from the corresponding registers by giving different values(for example, 00,01,10,11) to read register number 1 and read register number 2. After completing your test file design, according your pervious knowledge of how to run VISM, you should get the wave form as figure 2.

figure 2

Compiling and Simulating your register file using QUARTUSII Open QuartusII and create a new object named LABN. Then do the same procedures except in new project wizard of page 3 select the corresponding parameters for UP3.

In QuartusII, create symbol for registerfile.vhd called registerfile.bdf. Create LABN.bdf file by adding pins to registerfile.bdf. Then do compilation and simulation procedures. Putting your design into UP3 board In order to put your design into the corresponding board, usually, we need to do input preparation and output preparation. Input preparation 1.Using push-button to generate clocks and count the number of clocks using the figure 3s suggestion.

figure 3

The function of de-bounce is to filter the bounces which generated by the push-button and output a clock with a good shape, you can find this function in the disk of the book or you can design it by yourself. The Souncter function counts the number of clocks. You can use the module 4 counter that we already have, or you can use megafunctions by specify the inputs and outputs. The purpose of using Souncter function is to simultaneously select address for the register file. The purpose of using multiplexor here is to simultaneously select the input data to be written into the selected register according to the push-button.

Output preparation LED display ( It is not a case in UP3 but I prefer include it ) For the register file, we have two output buses, PortA and PortB. These ports all output binary numbers. In order to show the corresponding number in LED display, we need to design our own CONNECTOR to convert binaries into the corresponding LED displayer codes. Table 1 shows the relationship. Table 1 Hexadecimal 1 2 3 4 5 6 7 8 9 A B C D E F 0

Binary code 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 0000

LED display code 1100111 0010010 0000110 1001100 0100100 0100000 0001111 0000000 0001100 0001000 1100000 0110000 1000010 0110000 0111000 0000001

CONNECTOR can be designed according to Table 1. Figure 4 is the output preparation design. This design will extract data from these 4 registers according to clock serially. For example, when you first time push the button, it will show the data has the address 01, second, the data of address 10, third, the data of address 11, fourth, the data of address 00.

figure 4.

Appendix A shows the result of VISM according these design ideas. The clocks of the first three lines are generated by three push-buttons. The first clock is for generating addresses(00,01,10,11) and inputting data (0001, 0010, 0011,0100) into registers with these addresses in the register file. The second clock is for reading data from the register file into PortA at the same time converting binary code into LED display code, and the third clock is doing the same thing for PortB.

LCD display Because we have two output ports PortA and PortB and only one LCD display in UPS3 board, you need to add one 2:1 multiplexor for the selection. The LCD display is totally different from the LED. Either you can design your own LCD CONNECTOR or use the book provided Lcd_display.vhd. In both ways, to make LCD working, we need to have an enable, a data bus, a read and write signal, and a read and write memory address. And these signals have strict requirements( details see appendix C) . Figure 5 shows the basic concept design for LCD.

figure 5.

Appendix A: The output after input preparation and output preparation

Appendix B: register file vhdl code

==================registerfile.vhd================================== library ieee; use ieee.std_logic_1164.all; use work.all; entity registerfile is port ( clock4: in std_logic; registerNumber: in std_logic_vector(1 downto 0); Read_registerNumber1: in std_logic_vector(1 downto 0); Read_registerNumber2: in std_logic_vector(1 downto 0); DataIn: in std_logic_vector(3 downto 0); DataOut_A: out std_logic_vector(3 downto 0); DataOut_B: out std_logic_vector(3 downto 0) ); end registerfile; architecture struct of registerfile is component dff is port ( clock: in std_logic; D: in std_logic; Q: out std_logic ); end component; component decoder is port ( I: in std_logic_vector(1 downto 0); O: out std_logic_vector(3 downto 0) ); end component; component AND1 is port ( x: in std_logic; y: in std_logic; F: out std_logic ); end component; component multiplexor4 is port ( I3: in std_logic_vector(3 downto 0); I2: in std_logic_vector(3 downto 0); I1: in std_logic_vector(3 downto 0); I0: in std_logic_vector(3 downto 0); S: in std_logic_vector(1 downto 0); O: out std_logic_vector(3 downto 0) ); end component;

signal signal signal signal

ss1: ss2: ss3: ss4:

std_logic; std_logic; std_logic; std_logic;

signal ss: std_logic_vector(3 downto 0);

signal signal signal signal

DataOut1: DataOut2: DataOut3: DataOut4:

std_logic_vector(3 std_logic_vector(3 std_logic_vector(3 std_logic_vector(3

downto downto downto downto

0); 0); 0); 0);

begin decoder1: decoder port map ( I(0) => registerNumber(0), I(1) => registerNumber(1), O(0)=>ss1, O(1)=>ss2,O(2)=>ss3, O(3)=>ss4); And_1: And_2: And_3: And_4: AND1 AND1 AND1 AND1 port port port port map map map map ( ( ( ( X=>clock4,Y=>ss1,F=>ss(0)); X=>clock4,Y=>ss2,F=>ss(1)); X=>clock4,Y=>ss3,F=>ss(2)); X=>clock4,Y=>ss4,F=>ss(3));

D1: dff port map (clock => ss(0), D =>DataIn(0), Q=>DataOut1(0)); D2: dff port map (clock => ss(0), D=>DataIn(1), Q=>DataOut1(1)); D3: dff port map (clock=>ss(0), D=>DataIn(2), Q=>DataOut1(2)); D4: dff port map (clock=>ss(0), D=>DataIn(3), Q=>DataOut1(3)); D5: dff port map (clock => ss(1), D =>DataIn(0), Q=>DataOut2(0)); D6: dff port map (clock => ss(1), D=>DataIn(1), Q=>DataOut2(1)); D7: dff port map (clock=>ss(1), D=>DataIn(2), Q=>DataOut2(2)); D8: dff port map (clock=>ss(1), D=>DataIn(3), Q=>DataOut2(3)); D9: dff port map (clock => ss(2), D =>DataIn(0), Q=>DataOut3(0)); D10: dff port map (clock => ss(2), D=>DataIn(1), Q=>DataOut3(1)); D11: dff port map (clock=>ss(2), D=>DataIn(2), Q=>DataOut3(2)); D12: dff port map (clock=>ss(2), D=>DataIn(3), Q=>DataOut3(3)); D13: dff port map (clock => ss(3), D =>DataIn(0), Q=>DataOut4(0)); D14: dff port map (clock => ss(3), D=>DataIn(1), Q=>DataOut4(1)); D15: dff port map (clock=>ss(3), D=>DataIn(2), Q=>DataOut4(2)); D16: dff port map (clock=>ss(3), D=>DataIn(3), Q=>DataOut4(3)); mux1: multiplexor4 port map (S(0)=>Read_registerNumber1(0), S(1)=>Read_registerNumber1(1), I0(0)=> DataOut1(0),I0(1)=>DataOut1(1),I0(2)=>DataOut1(2),I0(3)=>DataOut1(3), I1(0)=>DataOut2(0),I1(1)=>DataOut2(1),I1(2)=>DataOut2(2),

I1(3)=>DataOut2(3), I2(0)=>DataOut3(0),I2(1)=>DataOut3(1),I2(2)=>DataOut3(2), I2(3)=>DataOut3(3), I3(0)=>DataOut4(0),I3(1)=>DataOut4(1),I3(2)=>DataOut4(2), I3(3)=>DataOut4(3), O(0)=>DataOut_A(0),O(1)=>DataOut_A(1), O(2)=>DataOut_A(2), O(3)=>DataOut_A(3)); mux2: multiplexor4 port map (S(0)=>Read_registerNumber2(0), S(1)=>Read_registerNumber2(1), I0(0)=> DataOut1(0),I0(1)=>DataOut1(1),I0(2)=>DataOut1(2),I0(3)=>DataOut1(3), I1(0)=>DataOut2(0),I1(1)=>DataOut2(1),I1(2)=>DataOut2(2), I1(3)=>DataOut2(3), I2(0)=>DataOut3(0),I2(1)=>DataOut3(1),I2(2)=>DataOut3(2), I2(3)=>DataOut3(3), I3(0)=>DataOut4(0),I3(1)=>DataOut4(1),I3(2)=>DataOut4(2), I3(3)=>DataOut4(3), O(0)=>DataOut_B(0),O(1)=>DataOut_B(1), O(2)=>DataOut_B(2), O(3)=>DataOut_B(3));

end struct;

Appendix C: time requirement for writing and reading LCD

10

11

Вам также может понравиться

- 9-State Up/Down CounterДокумент10 страниц9-State Up/Down CounterTong AlanОценок пока нет

- Application SSC02 eДокумент4 страницыApplication SSC02 eDragosFlorinLismanОценок пока нет

- Simple 8051 Programming and Digital Design With VHDLДокумент17 страницSimple 8051 Programming and Digital Design With VHDLAlaso Braun-wezОценок пока нет

- Logiccircuitmanual V.3withdesignДокумент46 страницLogiccircuitmanual V.3withdesignAnonymous BjaA0IiYОценок пока нет

- Tutorial ProjectДокумент16 страницTutorial ProjectMuhammadNizarArifansyahОценок пока нет

- Discontinued: Synchronous FIFO 5.0Документ10 страницDiscontinued: Synchronous FIFO 5.0Prathap NsОценок пока нет

- Verilog Present 2Документ25 страницVerilog Present 2markloopОценок пока нет

- Full Chip Level Implementation of Reed Solomon Encoder: Amar Narayan, Sheetal Belaldavar, VenkateshappaДокумент4 страницыFull Chip Level Implementation of Reed Solomon Encoder: Amar Narayan, Sheetal Belaldavar, VenkateshappaSumanth VarmaОценок пока нет

- Evaluative LanguageДокумент7 страницEvaluative LanguageCapuchino HuiNingОценок пока нет

- Sic and SIC/XEДокумент14 страницSic and SIC/XEravneet_mahal198100% (1)

- St.Joseph's College Engineering Dept. CS2304 System SoftwareДокумент49 страницSt.Joseph's College Engineering Dept. CS2304 System Softwaresumathi7975% (16)

- Lab 31Документ13 страницLab 31ansarirahim1Оценок пока нет

- Microprocessors and Assembly Language EC4121: Lecture 1: Introduction By: Mohamed Elnourani 0911471315Документ27 страницMicroprocessors and Assembly Language EC4121: Lecture 1: Introduction By: Mohamed Elnourani 0911471315divine serpentОценок пока нет

- Lab Session # 3 Complex Logic Design (Code Converter) : Figure 1: Multi-Input To Multi-Output CircuitДокумент10 страницLab Session # 3 Complex Logic Design (Code Converter) : Figure 1: Multi-Input To Multi-Output CircuitAhmad M. HammadОценок пока нет

- Chapter 1 Introduction To Microprocessor and MicrocontrollerДокумент21 страницаChapter 1 Introduction To Microprocessor and MicrocontrollernikmatenaОценок пока нет

- CPLD Experiment 8 - Encoders & 7-Segment DisplayДокумент14 страницCPLD Experiment 8 - Encoders & 7-Segment DisplayNicholas ThomasОценок пока нет

- Embed Lab4Документ6 страницEmbed Lab4cointoinОценок пока нет

- Lab 6 - Combinational Logic Modules - DecodersДокумент7 страницLab 6 - Combinational Logic Modules - DecodersSiegrique Ceasar A. JalwinОценок пока нет

- Lab Sequential CircuitsДокумент6 страницLab Sequential CircuitsMu'izz KaharОценок пока нет

- 1.0 The Design of Datapath Decoder: Ece 522/computer OrganizationДокумент36 страниц1.0 The Design of Datapath Decoder: Ece 522/computer OrganizationacapОценок пока нет

- ECE3073 2014 Lab 3Документ5 страницECE3073 2014 Lab 3Andrew WalleyОценок пока нет

- Example Usage: Mov R2, R0 (R2 R0)Документ4 страницыExample Usage: Mov R2, R0 (R2 R0)Divyam ShreevatsalОценок пока нет

- VHDL Data Types Lab - 4 to 1 Mux DesignДокумент3 страницыVHDL Data Types Lab - 4 to 1 Mux DesignMohamd barcaОценок пока нет

- Lab 12: ALU (Arithmetic and Logic Unit) Performed: 9/7, 11/7, 12/7, 16/7/2013 17 July, 2013Документ5 страницLab 12: ALU (Arithmetic and Logic Unit) Performed: 9/7, 11/7, 12/7, 16/7/2013 17 July, 2013Derek ByersОценок пока нет

- 8085 Microprocessor Programming Modes and Instruction SetДокумент16 страниц8085 Microprocessor Programming Modes and Instruction SetUiОценок пока нет

- University Solved Answers Unit 1 SS (System Software Notes)Документ12 страницUniversity Solved Answers Unit 1 SS (System Software Notes)Vaishnavi Rave100% (1)

- B302 BteqДокумент30 страницB302 BteqranusofiОценок пока нет

- EE 222 Assignment No 1Документ17 страницEE 222 Assignment No 1Ahmed Razi UllahОценок пока нет

- Intermediate I/O Programming Using MikroC CompilerДокумент13 страницIntermediate I/O Programming Using MikroC CompilerSalemAbaadОценок пока нет

- Activity No 2 Registers Alejo Aljiven R.Документ19 страницActivity No 2 Registers Alejo Aljiven R.ALJIVEN ALEJOОценок пока нет

- M.Tech ES ARM LABДокумент14 страницM.Tech ES ARM LABdownloadscribdpdfОценок пока нет

- DE2 Media ComputerДокумент44 страницыDE2 Media ComputerTruong Quang ThongОценок пока нет

- SIC MACHINE ARCHITECTURE SUGANYA KEERTHANAДокумент47 страницSIC MACHINE ARCHITECTURE SUGANYA KEERTHANAsivayagОценок пока нет

- Activity 2Документ11 страницActivity 2Lebron Bryant100% (1)

- Lab 4Документ7 страницLab 4Desiree Mae Ibon100% (1)

- CO Lab Manual-MinДокумент40 страницCO Lab Manual-MinMatheen TabidОценок пока нет

- Sheet MicorДокумент42 страницыSheet MicorFiras TaherОценок пока нет

- 7 Segment Display GuideДокумент12 страниц7 Segment Display Guidehieu minh TranОценок пока нет

- Lecture 12: More On Registers, Multiplexers, Decoders, Comparators and Wot-NotsДокумент5 страницLecture 12: More On Registers, Multiplexers, Decoders, Comparators and Wot-NotsTaqi ShahОценок пока нет

- In The Real Mode, Each of These Instructions Fetches A Vector From The Vector Table, and Then Calls The Procedure Stored at The Location Addressed by The VectorДокумент5 страницIn The Real Mode, Each of These Instructions Fetches A Vector From The Vector Table, and Then Calls The Procedure Stored at The Location Addressed by The Vectorsaqib idreesОценок пока нет

- BME 438 Digital Logic Design and Computer Architecture LabДокумент73 страницыBME 438 Digital Logic Design and Computer Architecture LabHafiz Muhammad Ahmad RazaОценок пока нет

- SsДокумент60 страницSsponns100% (1)

- After Completing This Module, You Will Be Able ToДокумент0 страницAfter Completing This Module, You Will Be Able TojayanthskОценок пока нет

- Emb C QB - Unit IiiДокумент15 страницEmb C QB - Unit IiiANANTHI SОценок пока нет

- CaseДокумент25 страницCaseDeepanshu Midha5140Оценок пока нет

- Coa MidДокумент7 страницCoa Midmulugetahiluf995Оценок пока нет

- HDL LAB EXPERIMENTS AND CODESДокумент76 страницHDL LAB EXPERIMENTS AND CODESvijaykannamallaОценок пока нет

- Assignment No:: Subject: Name: Rollno.Документ25 страницAssignment No:: Subject: Name: Rollno.Sharad Patil DholeОценок пока нет

- Digital I/O (Part 2): Keypads, LCDs and EEPROMДокумент4 страницыDigital I/O (Part 2): Keypads, LCDs and EEPROMAmmar AlkindyОценок пока нет

- Fabbc9: Convert Hexadecimal To BinaryДокумент11 страницFabbc9: Convert Hexadecimal To BinaryShan NavasОценок пока нет

- LGLite ATE 93C46Документ10 страницLGLite ATE 93C46Vijayakumar SОценок пока нет

- Debugging of Verilog Hardware Designs On DE2Документ19 страницDebugging of Verilog Hardware Designs On DE2CharismaztexОценок пока нет

- CountersДокумент13 страницCountersmuthubeОценок пока нет

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationОт EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationОценок пока нет

- PIC Projects and Applications using C: A Project-based ApproachОт EverandPIC Projects and Applications using C: A Project-based ApproachРейтинг: 4 из 5 звезд4/5 (2)

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.От EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Оценок пока нет

- Modeling and Simulation of Logistics Flows 3: Discrete and Continuous Flows in 2D/3DОт EverandModeling and Simulation of Logistics Flows 3: Discrete and Continuous Flows in 2D/3DОценок пока нет

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemОт EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemОценок пока нет

- Assembly Programming:Simple, Short, And Straightforward Way Of Learning Assembly LanguageОт EverandAssembly Programming:Simple, Short, And Straightforward Way Of Learning Assembly LanguageРейтинг: 5 из 5 звезд5/5 (1)

- Mathematical Methods Physics Partial Diiferential EquationsДокумент2 страницыMathematical Methods Physics Partial Diiferential EquationsBharavi K SОценок пока нет

- Keynes, John Maynard - The General Theory of Employment, Interest and MoneyДокумент257 страницKeynes, John Maynard - The General Theory of Employment, Interest and Moneyapi-3736392Оценок пока нет

- Shell Middle Distillate Synthesis (SMDS) Process: F. J. M. SchrauwenДокумент16 страницShell Middle Distillate Synthesis (SMDS) Process: F. J. M. SchrauwenBharavi K SОценок пока нет

- FW Delayed-Coking Process: Howard M. Feintuch Kenneth M. NeginДокумент58 страницFW Delayed-Coking Process: Howard M. Feintuch Kenneth M. NeginBharavi K S100% (2)

- Conocophillips S Zorb Diesel Process: Ed Sughrue and John S. ParsonsДокумент6 страницConocophillips S Zorb Diesel Process: Ed Sughrue and John S. ParsonsBharavi K SОценок пока нет

- The Syntroleum Process of Converting Natural Gas Into Ultraclean HydrocarbonsДокумент10 страницThe Syntroleum Process of Converting Natural Gas Into Ultraclean HydrocarbonsBharavi K SОценок пока нет

- Hydrogen Processing: P A R T 1 4Документ68 страницHydrogen Processing: P A R T 1 4Bharavi K SОценок пока нет

- Oxygenates Production Technologies: P A R T 13Документ8 страницOxygenates Production Technologies: P A R T 13Bharavi K SОценок пока нет

- Oxypro Process: Steve Krupa, Larry Richardson, and Jill MeisterДокумент4 страницыOxypro Process: Steve Krupa, Larry Richardson, and Jill MeisterBharavi K SОценок пока нет

- Uop Olefin Isomerization: Steve KrupaДокумент6 страницUop Olefin Isomerization: Steve KrupaBharavi K SОценок пока нет

- Uop Ethermax Process For Mtbe, Etbe, and Tame Production: Steve Krupa, Jill Meister, and Charles LuebkeДокумент4 страницыUop Ethermax Process For Mtbe, Etbe, and Tame Production: Steve Krupa, Jill Meister, and Charles LuebkeBharavi K S100% (1)

- Visbreaking and Coking: P A R T 12Документ32 страницыVisbreaking and Coking: P A R T 12Bharavi K SОценок пока нет

- Uop Molex Process For Production of Normal Paraffins: Stephen W. SohnДокумент4 страницыUop Molex Process For Production of Normal Paraffins: Stephen W. SohnBharavi K SОценок пока нет

- Uop Merox Process: G. A. DziabisДокумент12 страницUop Merox Process: G. A. DziabisBharavi K SОценок пока нет

- Gasoline Desulfurization: Douglas A. Nafis and Edward J. HoudeДокумент22 страницыGasoline Desulfurization: Douglas A. Nafis and Edward J. HoudeBharavi K SОценок пока нет

- Uop Par-Isom Process: Nelson A. CusherДокумент6 страницUop Par-Isom Process: Nelson A. CusherBharavi K S100% (1)

- The S Zorb Sulfur Removal Technology Applied To Gasoline: David Legg and Jason GislasonДокумент8 страницThe S Zorb Sulfur Removal Technology Applied To Gasoline: David Legg and Jason GislasonBharavi K SОценок пока нет

- Belco Edv Wet Scrubbing System: Best Available Control Technology (Bact) For Fccu Emission ControlДокумент16 страницBelco Edv Wet Scrubbing System: Best Available Control Technology (Bact) For Fccu Emission ControlBharavi K S100% (1)

- The Rose Process: Tayseer Abdel-Halim and Raymond FloydДокумент14 страницThe Rose Process: Tayseer Abdel-Halim and Raymond FloydBharavi K SОценок пока нет

- Uop Olex Process For Olefin Recovery: Stephen W. SohnДокумент4 страницыUop Olex Process For Olefin Recovery: Stephen W. SohnBharavi K SОценок пока нет

- Kerosene Isosiv Process For Production of Normal Paraffins: Stephen W. SohnДокумент6 страницKerosene Isosiv Process For Production of Normal Paraffins: Stephen W. SohnBharavi K SОценок пока нет

- Sulfur Compound Extraction and Sweetening: P A R T 11Документ14 страницSulfur Compound Extraction and Sweetening: P A R T 11Bharavi K SОценок пока нет

- Uop Isosiv Process: Nelson A. CusherДокумент6 страницUop Isosiv Process: Nelson A. CusherBharavi K SОценок пока нет

- Separation Processes: P A R T 10Документ14 страницSeparation Processes: P A R T 10Bharavi K SОценок пока нет

- Uop/Fw Usa Solvent Deasphalting Process: Daniel B. GillisДокумент26 страницUop/Fw Usa Solvent Deasphalting Process: Daniel B. GillisBharavi K SОценок пока нет

- Uop Penex Process: Nelson A. CusherДокумент14 страницUop Penex Process: Nelson A. CusherBharavi K SОценок пока нет

- Uop Sorbex Family of Technologies: James A. JohnsonДокумент8 страницUop Sorbex Family of Technologies: James A. JohnsonBharavi K SОценок пока нет

- Uop Butamer Process: Nelson A. CusherДокумент8 страницUop Butamer Process: Nelson A. CusherBharavi K SОценок пока нет

- Uop Tip and Once-Through Zeolitic Isomerization Processes: Nelson A. CusherДокумент12 страницUop Tip and Once-Through Zeolitic Isomerization Processes: Nelson A. CusherBharavi K SОценок пока нет

- Isomerization: P A R T 9Документ6 страницIsomerization: P A R T 9Bharavi K SОценок пока нет

- ch1 v1Документ22 страницыch1 v1LujainОценок пока нет

- Your Statement: Complete AccessДокумент7 страницYour Statement: Complete AccessWeb TreamicsОценок пока нет

- 19CBS1003 - Usability Design of Software Applications - LabДокумент10 страниц19CBS1003 - Usability Design of Software Applications - LabYala yoloОценок пока нет

- Crop Yield Prediction Using Random Forest AlgorithmДокумент11 страницCrop Yield Prediction Using Random Forest AlgorithmVj KumarОценок пока нет

- History of The InternetДокумент3 страницыHistory of The InternetAngelly V Velasco100% (1)

- IN B.E. Degree Electronics & Communication Engineering: Year: I Teaching Schedule Examination Schedule RemarksДокумент161 страницаIN B.E. Degree Electronics & Communication Engineering: Year: I Teaching Schedule Examination Schedule RemarksGorakh Raj JoshiОценок пока нет

- 05 Tabla de Intercambio de Información-V2.1 - (Excel)Документ466 страниц05 Tabla de Intercambio de Información-V2.1 - (Excel)patricioОценок пока нет

- Daikin Inverter Air Cooled Screw ChillerДокумент14 страницDaikin Inverter Air Cooled Screw Chillerfiqrinovel100% (1)

- Alia ARC900 Paperless RecordersДокумент4 страницыAlia ARC900 Paperless RecordersRexCrazyMindОценок пока нет

- Impact of Computer Security System On The Job Performance of The Office TechnologistДокумент10 страницImpact of Computer Security System On The Job Performance of The Office TechnologistIjasini Banga GabrielОценок пока нет

- NLP Project ReporttttДокумент9 страницNLP Project Reporttttteddy demissieОценок пока нет

- Sap Abap CV & Resume for MaheshДокумент4 страницыSap Abap CV & Resume for Maheshsunil tiwaryОценок пока нет

- Introduction to Servo MotorsДокумент13 страницIntroduction to Servo MotorsReda FakihОценок пока нет

- Panasonic KX Tg1100hgДокумент81 страницаPanasonic KX Tg1100hgmirkodeОценок пока нет

- PE MCQ Unit-IIДокумент9 страницPE MCQ Unit-IIKalpesh MahajanОценок пока нет

- Hawk Eye TechnologyДокумент14 страницHawk Eye TechnologyDerrick MillerОценок пока нет

- Freemake Software For YoutubeДокумент5 страницFreemake Software For YoutubeVickfor LucaniОценок пока нет

- Gartner Market Guide DDI 25042014Документ6 страницGartner Market Guide DDI 25042014Mohamed Osama AbosreeОценок пока нет

- Csec It Sba 2022 - SpreadsheetДокумент6 страницCsec It Sba 2022 - SpreadsheetJanicSmith50% (2)

- Histograms Answers MMEДокумент5 страницHistograms Answers MMEEffОценок пока нет

- Open Source Real-Time Temperature MonitoringДокумент39 страницOpen Source Real-Time Temperature MonitoringdhaОценок пока нет

- CCNA Practical Lab 2nd Edition PDFДокумент88 страницCCNA Practical Lab 2nd Edition PDFYACINE NABILОценок пока нет

- Skyscanner Tone of VoiceДокумент32 страницыSkyscanner Tone of VoiceJefferson Bobby OrtegaОценок пока нет

- Document 2005035Документ2 страницыDocument 2005035Joseph LeeОценок пока нет

- CHRMP Generative AI Sept 2023 1Документ19 страницCHRMP Generative AI Sept 2023 1shajmalikОценок пока нет

- ALARM Manual8088Документ36 страницALARM Manual8088k_georgoОценок пока нет

- P0903BSG Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorДокумент5 страницP0903BSG Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorAndika WicaksanaОценок пока нет

- Watson Studio-Student Guide PDFДокумент62 страницыWatson Studio-Student Guide PDFghadaОценок пока нет

- Speed Control of Induction Motors Without Speed SensorsДокумент8 страницSpeed Control of Induction Motors Without Speed Sensorsharibhushan4912Оценок пока нет

- CJV150 - CJV300 - CJV330 - Cutting Adjustment Guide D501067 Ver.2.0Документ16 страницCJV150 - CJV300 - CJV330 - Cutting Adjustment Guide D501067 Ver.2.0BrandonОценок пока нет