Академический Документы

Профессиональный Документы

Культура Документы

Technology: Multi-Channel Audio CODEC

Загружено:

vetchboyИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Technology: Multi-Channel Audio CODEC

Загружено:

vetchboyАвторское право:

Доступные форматы

AVS Technology AV2388

Multi-Channel Audio CODEC

FEATURES 48, 96 and 192KHz. Sampling Rates, 192

fs or 128 fs for 96 KHz Sampling Rates.

• Six Channel 24/20-bit DACs. and 86 fs or 64 fs for 192 KHz. Sampling

- 102 dB SNR Rate.

- 104 dB Dynamic Range. • Automatic input format detection.

- -92 dB THD + N Ratio. • 5-volt Power Supply.

- 32,44.1, 48, 96 and 192KHz. Sampling • 3.3 -volt Digital Interface Friendly.

rates. • I2C Interface for Mode Setting.

- 24, 20, 18 and 16-bit Digital Inputs.

- Containing Digital De-emphasis Filters. Applications

- Independent Digital Volume Control. • Digital Surround Sound For Home Theater

- I2S, Left and Right Justified Digital Input • DVD

Formats. • Car Audio.

- Auto-Mute Control.

- On -chip Reconstruction Filters.

- -96 dB THD + N Ratio. • 28 pin SOP package

- I2S and Left Justified Output Formats.

• System clock: 384 fs or 256 fs for 32, 44.1

SDA I2C Serial

Control Port

AV2388

SCL D/A 40KHz VOR3

SD1 80 D/A VOL3

40KHz

5th Order Σ∆

Digital Volume

De-Emphasis

Over-sampling

Modulators

SD2 80

D/A 40KHz VOR2

96 Times

Filters

Audio I/F

Serial

SD3 77

D/A 40KHz VOL2

D/A 40KHz VOR1

SF 77

D/A 40KHz VOL1

SC 78

Format PLL

Detect'n

15 15

XCK RST VCM

AVS Technology Inc.

4110 Clipper Ct., Fremont CA94538 1-20 January 3, 2002

Tel: (510) 353-0848

Fax: (510) 353-0856

AV2388

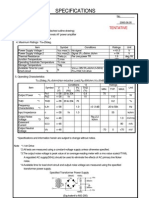

Item PERFORMANCE SPECIFICATIONS Spec.

Audio DAC

1 Audio Output Level 1 Vrms

2 Audio Bandwidth 20Hz - 20 KHz +/- 0.1 dB

3 SNR (A-weight, Muted) >102 dB

4 SNR (A-weight, Not Muted) >96 dB

6 THD + N (A-weight, FFS Output) < -92 dB

7 Dynamic Range 104 dB

8 Channel Separation < -96 dB

9 Nonlinear Distortion < 0.25 dB

10 Channel Gain Error < 0.1 dB

All Measurement were taken with only one channel active.

2-20 January 3, 2002

AV2388

DESCRIPTION

The AV2388 is a mixed signal CMOS monolithic audio CODEC. It consists of six channels sigma delta DACs The

DACs support 24, 20, 18 and 16-bit input data. It also support multiple sampling frequency data. Each DAC has it

own individual volume control.

XCK REQUIREMENT

The AV2388 supports 384 and 256 times sampling clock for 32, 44.1, 48, 96 and 192K audio; 192 or 128 times for

the 96 K audio.; and 96 and 64 times for the 192K audio.

XCK Requirement

Sampling XCK Freq.

Rate PLLcntl=[0 0] PLLcntl=[1 0] PLLcntl=[0 1]

Normal XCK 4 times XCK 2 times XCK

384*fs 256*fs 4*384*fs 4*256*fs 2*384*fs 2*256*fs

32 K 12.288 MHz 8.192 MHz 49.152 MHz 32.768 MHz 24.576 MHz 16.384 MHz

44.1 16.934 Mhz 11.29 Mhz. 67.738 Mhz 45.158 Mhz. 33.869 Mhz 22.579 Mhz.

48 K 18.432 MHz 12.288 Mhz. 73.728 MHz 49.152 Mhz. 36.864 MHz 24.576 Mhz.

96 K 18.432 MHz 12.288 Mhz. 73.728 MHz 49.152 Mhz. 36.864 MHz 24.576 Mhz.

192 K 18.432 Mhz 12.288 Mhz. 73.728 Mhz 49.152 Mhz. 36.864 Mhz 24.576 Mhz.

3-20 January 3, 2002

AV2388

PIN ASSIGNMENT

SD3 1 28 AR1

SD2 2 27 AL1

SD1 3 26 AR2

TSTO 4 25 AL2

SC 5 24 AR3

AV2388

SF 6 23 AL3

DGND 7 22 AGND

DVDD 8 21 VCM

DGND 9 20 AVDD

XCK 10 19 N/C

SCL 11 18 AGND

SDA 12 17 N/C

TST 13 16 N/C

RST 14 15 N/C

PIN DESCRIPTION

Pin Name Pin # Type Description

DIGITAL

SD3 1 I Audio Serial Data Input 3.

SD2 2 I Audio Serial Data Input 2.

SD1 3 I Audio Serial Data Input 1,..

TSTO 4 O Test output pin. This pin should be no be connected.

SC 5 I Audio Serial Data Clock pin.

SF 6 I Left/Right Channel Clock pin. For Left justified or Right justified mode, a high in

SF indicates Left Channel Data, a low in SF indicates Right Channel Data. For

I2S mode, a low in SF indicates Left Channel Data, a high in SF indicates Right

Channel Data.

DGND 7 GND Digital ground

DVDD 8 +5V Digital power supply.

DGND 9 GND Digital ground

XCK 10 I External Master Clock Input.

4-20 January 3, 2002

AV2388

PIN DESCRIPTION (Continued)

Pin Name Pin # Type Description

SCL 11 I I2C clock input.

SDA 12 I/O I2C DATA bus. Open drain output. Externally this pin should tie to a 680 ohm

pull up resistor.

TST 13 O Test fs reference pin. For test vector verification. For normal operation this pin

must be tied to ‘0’.

RST 14 I Active low power down reset. When low, the chip is reset and all programmable

registers are reset to default values.

Analog

AR1 28 O Analog right channel 1 output

AL1 27 O Analog left channel 1 output

AR2 26 O Analog right channel 2 output.

AL2 25 O Analog left channel 2 output.

AR3 24 O Analog right channel 1 output.

AL3 23 O Analog left channel 1 output.

AVSS 22 GND Analog circuits ground

VCM 21 Common voltage output pin for the DAC.

AVDD 20 +5V Analog circuits power supply

N/C 19 No connection. Can be tied to AVSS

AGND 18 GND Analog circuits ground

N/C 17 I No connection. Can be tied to AVSS

N/C 16 I No connection. Can be tied to AVSS

N/C 15 No connection, Can be tied to AVSS

5-20 January 3, 2002

AV2388

DIGITAL AUDIO SERIAL INTERFACE

The digital serial interface consists of 3 serial input pins, SD1, SD2, SD3, and one serial clock input pin, SC, and

one left/right indicator input pin, SF. The data are 2’s complement MSB first numbers. The AV2388 supports four

resolution, which are selected either by setting the FMT[1] and FMT[0] pins or by programming the control register

CREG0[5:4] via the I2C serial control port. Table 1 describes these four resolution.

Table (1): Audio Serial Data Input Format,

Format CREG0[5] CREG0[4] SD1, SD2, and SD3

0 0 0 24-bit

1 0 1 20-bit

2 1 0 18-bit

3 1 1 16-bit

The SD3, SD2 and SD1 can be either 24-bit or 32-bit per frame as well as left justified, right justified or I2S. The

AV2388 counts the number of BCK per frame to determine whether the input is 24 or 32 bits format.

Table (1): Audio Serial Data Input Modes

Mode CREG0[7] 0REG0[6] SD1, SD2, and SD3

0 0 0 Right Justified

1 0 1 I2S

2 1 0 Left Justified

3 1 1 Invalid

6-20 January 3, 2002

AV2388

Figure 1. Audio Serial Input Data Timing Diagram

1/fs

LEFT CHANNEL RIGHT CHANNEL

SF

SC

MSB LSB MSB LSB

SD1,2,3 2 1 0 2 1 0

Right justified, CREG0[7,6]=[0 0]

1/fs

LEFT CHANNEL RIGHT CHANNEL

SF

SC

MSB LSB MSB LSB

SD1,2,3 0 1 0

Left justified, CREG0[7,6]=[1 0]

1/fs

LEFT CHANNEL RIGHT CHANNEL

SF

SC

MSB LSB MSB LSB

SD1,2,3 1 0 1 0

IIS, CREG0[7,6]=[0 1]

Figure 2.

7-20 January 3, 2002

AV2388

Figure 3. Audio Serial Output Data Timing Diagram

1/fs

LEFT CHANNEL RIGHT CHANNEL

SF

SC

MSB LSB MSB LSB

SD1,2,3 23 22 21 2 1 0 23 22 21 2 1 0

Left justified, CREG0[7,6]=[X 0]

1/fs

LEFT CHANNEL RIGHT CHANNEL

SF

SC

MSB LSB MSB LSB

SD1,2,3

23 22 21 2 1 0 23 22 21 2 1 0

IIS, CREG0[7,6]=[0 1]

8-20 January 3, 2002

AV2388

INFINITE ZERO DETECTION

The AV2388 has an Infinite Zero Detection circuit which detects zero in the Audio Serial Port that lasts for

approximately 0.5 sec. By default, the zero detection circuit is on.

Serial Command Port

The user can use the pin to select the chip operation or by programming the internal control registers through the 7

bit address I2C port. The Chip Address for the AV2388 is 31H. The protocol for write operation consists of sending

3 byte data to AV2388, following each byte are the acknowledges generated by AV2388. The first byte is the 7-bit

Chip Address followed by the read/write bit (read is high write is low). The second byte is the control register

address. The third byte is the control register data.

Upon power up, all programmable registers are set to default values. Figure 4 describes the serial command port

timing relationship.

Figure 4. Serial Command Port Timing

I2 C Bus Control Register write example:

Start CA6 CA0 R/W ACK A7 A0 ACK D7 D0 ACK Stop

SDA 1 1 1

SCL

Chip adrress: CA<6:0> = 31H

Register address: A<7:0> = 00H

DATA: D<7:0> = 30H

9-20 January 3, 2002

AV2388

SERIAL PORT CONTROL REGISTER ASSIGNMENT

There are 10 registers dedicated to the AV2388 for chip functional programming,. One register for testing. The

register addresses assignments are

Address Default

Register Register Function

(decimal) Value

0 CREG0[7:0] 80 Data input format, de-emphasis filter selection

1 CREG1[7:0] 80 Input format and PLL output frequency selection

2 VOLREG0[7:0] 80 Volume control for channel 1, left

3 VOLREG1[7:0] 80 Volume control for channel 1, right

4 VOLREG2[7:0] 80 Volume control for channel 2, left

5 VOLREG3[7:0] 80 Volume control for channel 2, right

6 VOLREG4[7:0] 80 Volume control for channel 3, left

7 VOLREG5[7:0] 80 Volume control for channel 3, right

8 MUTE[5:0] 00 Mute control register.

9 TREG1[7:0] 00 Test control

10-20 January 3, 2002

AV2388

CONTROL REGISTERS DESCRIPTION

Control Register 0(ADRS=hex00, default=hex80)

CREG0[7:0]

ADDR[4:0]

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

Hex 00 LT IIS FMT[1:0] AMUTE AMPX2 FIRSL[1:0]

Default Value 1 0 0 0 0 0 0 0

R/W R/W R/W R/W R/W R/W R/W R/W R/W

[LT, IIS] Digital Serial Bus Format Select

00: - Normal or Right Justified Format.

01: - I2S Format.

10: - Left Justified Format. (default)

11: - Not allowed.

FMT[1:0]: - These two bits define the serial audio input resolution

00: - 24-bit resolution. (default)

01: - 20-bit resolution.

10: - 18-bit resolution.

11: - 16-bit resolution.

AMUTE: - Active low auto-mute detection enable.

0: - Auto-mute enabled. (default)

1: - No auto-mute.

AMPX2: - Multiplied the Volume by two.

0: - Normal. (default)

1: - Volume is doubled. Should be used with Pre-De-emphasis track.

DEML: - De-emphasis Control

00: - No De-emphasis. (default)

01: - Select 44.1K De-emphasis filter.

10:- Select 48 K De-emphasis filter.

11: - Select 44.1K and 36K sampling filter: No De-emphasis.

Control Register 1 (ADRS=hex01, default=hex80)

CREG1[7:0]

ADDR[4:0]

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

Hex 01 Autodet zero fs384 px4s px2s zero PLLcntl1 PLLcntl0

Default Value 1 0 0 0 0 0 0

R/W R/W R/W R/W R/W R/W R/W R/W

11-20 January 3, 2002

AV2388

Autodet: Input format auto detection enable

0 - disable input format detection. The user need to program bit[5:3] in order to select the input format

and filters for 96K and 192K sampling.

1 - enable input format detection.

F384: XCK frequency.

0 -XCK is 384 times the bit clock, SCK.

1 - XCK is 256 times the bit clock, SCK.

[Px4s Px2s]: Higher sampling filter selection.

[0 0] - normal sampling.

[0 1] - 2 times over sampling filter enable.

[1 0] - 4 times over sampling filter enable.

[1 1] - invalid.

PLLcntl[1:0]:System clock PLL control.

[ 0 0] - normal sampling XCK input.

[ 0 1] - 2 times XCK input.

[ 1 0] - 4 times XCK input.

[ 1 1] - invalid

Volume Registers for channel 1 to channel 3, (ADRS=hex02 - hex07, default=hex80)

Volume Registers

ADDR[4:0]

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

Hex 02 Channel 1 left volume register, VLREG0L[7:0]

Hex 03 Channel 1 right volume register, VLREG0R[7:0]

Hex 04 Channel 2 left volume register, VLREG1L[7:0]

Hex 05 Channel 2 right volume register, VLREG!1R[7:0]

Hex 06 Channel 3 left volume register, VLREG2L[7:0]

Hex 07 Channel 3 right volume register, VLREG2RL[7:0]

Default Value 1 0 0 0 0 0 0 0

VOLREG:- Control the volume of the 6 DAC’s

80h- corresponds to 0 dB setting. Value should not be programed greater than 80h.

12-20 January 3, 2002

AV2388

Mute Reg (ADRS=hex10, default=hex80)

Mute[5:0]

ADDR[4:0]

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

Hex 01 Mute3R Mute3L Mute2R Mute2L Mute1R Mute1L

Default Value 0 0 0 0 0 0

R/W R/W R/W R/W R/W R/W R/W

13-20 January 3, 2002

AV2388

Application Connection Example:

Digital 4.7 ohm Analog

+5 Volt

22 uF 8 20 22 uF

DVCC AVCC

1

SD3

2 22 uF

SD2 28

Digital Audio 3 AR1

Interface SD1

27 22 uF

5 AL1

SC

6 26 22 uF

SF AR2

10 25 22 uF

Over Sample Clock XCK AL2

24 22 uF

AR3

+5 Volt AV2388 23 22 uF

AL3

680 ohm

21

11

2 VCM

I C Serial SCL 4.7uF

Interface 12

SDA

13

TST

14

Reset RST

DVSS AVSS

7 9 15 18 22

All Unmarked

Capacitors are

0.1 uF

14-20 January 3, 2002

AV2388

TIMING DIAGRAM

Figure 5. Audio Serial Interface Timing Requirement

tsc

tscH tscL

SC

tsd su

SD1-3

tsdout mx tsd hd

SDOUT

tsdout mn

tsf su

SF

tsf hd

Figure 6. Serial Command Port Write Timing Requirement

tBUF tSU;STA

SDA

tHD;STA tSU;DAT

tSU;STO

tHIGH

SCL P S P

Sr

tLOW

tR

tF tHD;DAT

15-20 January 3, 2002

AV2388

Figure 7. Power Down / Reset Timing

trst

PWD

ABSOLUTE MAXIMUM RATINGS

Symbol Characteristics Min Max Units

VDD Power Supply Voltage (Measured to GND) -0.5 +7.0 V

Vi Digital Input Applied Voltage2 GND-0.5 V

Ai Digital Input Forced Current3,4 -100 100 mA

Vo Digital Output Applied Voltage2 GND-0.5 VDD+0.5 V

Ao Digital Output Forced Current3,4 -100 100 mA

TDsc Digital Short Circuit Duration (single output high state to Vss) 1 Sec

TASC Analog Short Circuit Duration (single output to VSS1) infinite Sec

Ta Ambient Operating Temperature Range -25 +125 o C

Tstg Storage Temperature Range -65 +150 o C

Tj Junction Temperature (Plastic Package) -65 +150 o C

Tsol Lead Soldering Temperature (10 sec., 1/4” from pin) 300 o C

Tvsol Vapor Phase Soldering (1 minute) 220 o C

Tstor Storage Temperature -65 +150 o C

Notes:

1. Absolute maximum ratings are limiting values applied individually, while all other parameters are within specified

operating conditions.

2. Applied voltage must be current limited to specified range, and measured with respect to VSS.

3. Forcing voltage must be limited to specified range.

4. Current is specified as conventional current, flowing into the device.

16-20 January 3, 2002

AV2388

RECOMMENDED OPERATING CONDITIONS

Symbol Characteristics Min Typical Max Units

VDD Power supply voltage 4.5 5 5.5 V

VVCM Reference voltage 2.25 2.41 V

RL Analog output load 37.5 70 Ω

Ta Ambient operating temperature range 0 70 o C

ELECTRICAL CHRACTERISTICS

Parameter Characteristics Min Typ Max Units

Supply

IDD Total Power Supply Current, Analog + Digital 135 145 mA

Digital Characteristics

VIH Digital Input Voltage, Logic HIGH, 2.0 VDD V

TTL Compatible Inputs.

VIL Digital Input Voltage, Logic LOW, VSS 0.8 V

TTL Compatible Inputs

IIH Digital Input Current, Logic HIGH, (VIN=4.0V) 10 µA

IIL Digital Input Current, Logic LOW, (VIN=0.4V) -10 µA

CIN Digital Input Capacitance (f=1Mhz, VIN=2.4V) 7 pF

VOH Digital Output Voltage, Logic HIGH, 3.2 3.4 3.5 V

(IOH= -1mA)

VOL Digital Output Voltage, Logic LOW, VSS 0.4 V

(IOL=4.0 mA)

IOZH Hi-Z Leakage Current, HIGH, 10 µA

VDD=Max, VIN=VDD)

IOZL Hi-Z Leakage Current, LOW, -10 µA

VDD=Max, VIN=VSS)

CI Digital Input Capacitance (TA=25oC, f=1Mhz) 8 pF

CO Digital Output Capacitance (TA=25oC, 10 pF

f=1Mhz)

17-20 January 3, 2002

AV2388

Parameter Characteristics Min Typ Max Units

Audio Serial Interface Timing

tsc SC Cycle Time 80 ns

tscH SC Pulse Width, HIGH 30 ns

tscL SC Pulse Width, LOW 30 ns

tsdsu Audio Data Setup Time With Respect To Ris- 10 ns

ing Edge of SC

tsdhd Audio Data Hold Time With Respect to Rising 15 ns

Edge of SC

tsfsu Audio SFSetup Time With Respect To Rising 10 ns

Edge of SC

tsfhd Audio SF Hold Time With Respect To Rising 15 ns

Edge of SC

tsdoutmx SC falling edge to SDOUT Valid 25 ns

tsdoutmn SC falling edge to SDOUT Valid 5 ns

Reset Signal

trst Active low reset time 1 µs

Serial Command Port

fsc SCL Clock Frequency 100 kHz

tsu;sta Start condition set up time 4.7 us

thd;sta Start condition hold time 4.0 us

tsu;sto Stop condition set up time 4.0 us

tLOW SCL Low time 4.7 us

tHIGH SCL High time 4.0 us

tr SCL & SDA rise time 1.0 us

tf SCL & SDA fall time 0.3 us

tsu;DAT Data set-up time 250 ns

thd;DAT Data hold time 0 ns

tvd;DAT SCL LOW to data out valid 3.4 us

tBUF Bus Free time 4.7 us

18-20 January 3, 2002

AV2388

Parameter Characteristics Min Typ Max Units

Audio DAC Characteristics

SNR Signal To Noise Ratio 99 102 dB

THD+N Total Harmonic Distortion + Noise 94 dB

Dynamic Range 102 104 dB

Channel Separation 84 97 dB

Full Scale Output Voltage .96 1 1.02 Vrms

Center Voltage 2.18 2.20 2.25 V

Inter-channel Gain Mismatch 0.1 dB

Analog Output Load Resistance 5 KΩ

Analog Output Load Capacitance 100 pF

19-20 January 3, 2002

AV2388

PACKAGING INFORMATION

Dimensions

Mils Mils

min norm max min norm max

A 93 100 104 E1 291 295 299

A1 4 8 12 E2 394 406 419

b 14 16 19 e 50

C 9 10 12 L 20 30 40

D 691 702 713

28-Pin (SOP)

A1

E2 A

E1

20-20 January 3, 2002

Вам также может понравиться

- Technology: Multi-Channel Audio CODECДокумент19 страницTechnology: Multi-Channel Audio CODECvetchboyОценок пока нет

- 2 Adc, 8 Dac, 96 KHZ, 24-Bit: - CodecДокумент25 страниц2 Adc, 8 Dac, 96 KHZ, 24-Bit: - Codecmusical_cat2Оценок пока нет

- High Feature 96Khz 24bit Dir: Asahi Kasei (Ak4112A)Документ32 страницыHigh Feature 96Khz 24bit Dir: Asahi Kasei (Ak4112A)DavidОценок пока нет

- Pcm3168a q1 PDFДокумент66 страницPcm3168a q1 PDFSATYAM NAIDUОценок пока нет

- Six Channel, 20-Bit Codec: Features DescriptionДокумент36 страницSix Channel, 20-Bit Codec: Features Descriptionalive ElectronicsОценок пока нет

- Pawpaw: Analog ReinventedДокумент64 страницыPawpaw: Analog ReinventedНиколайОценок пока нет

- ES9038Q2M Datasheet v1.4Документ65 страницES9038Q2M Datasheet v1.4Thắng NguyễnОценок пока нет

- pcm1794 PDFДокумент30 страницpcm1794 PDFSunghwan ShinОценок пока нет

- ES9016S Datasheet v1.91Документ33 страницыES9016S Datasheet v1.91Nursapta nugrohoОценок пока нет

- PCM 1796Документ61 страницаPCM 1796joe joeОценок пока нет

- PCM 5102Документ38 страницPCM 5102Володимир ТеліженкоОценок пока нет

- Cs4362a F2Документ50 страницCs4362a F2raiksonОценок пока нет

- Ak4962ecb en ProductbriefДокумент7 страницAk4962ecb en ProductbriefIonut LapusteОценок пока нет

- 98 Ak 4480 EfДокумент44 страницы98 Ak 4480 EfYurii LembergОценок пока нет

- Tda 1309Документ24 страницыTda 1309اديب اسماعيلОценок пока нет

- Analog Reinvented: High Performance USB DAC With Headphone Amplifier, MQA, ADC, PLL, Jack Detect, Mic, and A/D MixingДокумент3 страницыAnalog Reinvented: High Performance USB DAC With Headphone Amplifier, MQA, ADC, PLL, Jack Detect, Mic, and A/D MixingCoreyОценок пока нет

- Analog Reinvented: ES9018K2M 32-Bit Stereo Mobile Audio DACДокумент2 страницыAnalog Reinvented: ES9018K2M 32-Bit Stereo Mobile Audio DACivo radoichevОценок пока нет

- dbx376CutSheetA2 OriginalДокумент2 страницыdbx376CutSheetA2 OriginalCamelia GalateanuОценок пока нет

- DBX PA Cut SheetA2Документ2 страницыDBX PA Cut SheetA2Willy WakkerОценок пока нет

- Ak4113 (Spdif In)Документ49 страницAk4113 (Spdif In)slobodan.jovanovic.jaОценок пока нет

- Key Features: Electronics and ConnectorsДокумент2 страницыKey Features: Electronics and ConnectorsIrvanda ENVIOUSОценок пока нет

- Sonydsp v77 SM 479622 PDFДокумент41 страницаSonydsp v77 SM 479622 PDFmorvetrОценок пока нет

- TLV 320 Aic 3100Документ134 страницыTLV 320 Aic 3100megatornadoОценок пока нет

- Tpa6404 q1Документ12 страницTpa6404 q1siogОценок пока нет

- AK4342ENДокумент43 страницыAK4342ENDamnLostОценок пока нет

- Sigmadsp 28/56-Bit Audio Processor With 2Adc/4Dac Adau1701: Preliminary Technical DataДокумент43 страницыSigmadsp 28/56-Bit Audio Processor With 2Adc/4Dac Adau1701: Preliminary Technical DataNguyễn Quang TrânОценок пока нет

- Panasonic Sa-Ak210e SMДокумент14 страницPanasonic Sa-Ak210e SMmarianОценок пока нет

- BW Broadcast DSPX-FM Datasheet PDFДокумент1 страницаBW Broadcast DSPX-FM Datasheet PDFwendyОценок пока нет

- CFDCD 777 SMK 2Документ68 страницCFDCD 777 SMK 2ketemagetachew69Оценок пока нет

- PCM 1802Документ32 страницыPCM 1802Raiatea MoeataОценок пока нет

- ES8396Документ13 страницES8396Luis PerezОценок пока нет

- PCMuu 4220272 T 2 Yu 2 Beusuagw 7 WF 1 T 1 T 2 T 5252 T 2 TДокумент34 страницыPCMuu 4220272 T 2 Yu 2 Beusuagw 7 WF 1 T 1 T 2 T 5252 T 2 THIGURASHI 86Оценок пока нет

- 114 DB, 192 KHZ, Multi-Bit Audio A/D Converter: Features General DescriptionДокумент25 страниц114 DB, 192 KHZ, Multi-Bit Audio A/D Converter: Features General DescriptionLéo TecladistaОценок пока нет

- CS4398 DS568F4Документ45 страницCS4398 DS568F4vantri27082004Оценок пока нет

- 101 DB, 192 KHZ, Multi-Bit Audio A/D Converter: Features General DescriptionДокумент24 страницы101 DB, 192 KHZ, Multi-Bit Audio A/D Converter: Features General DescriptionGilbertoAdonayGutierrezОценок пока нет

- PCM 5121Документ107 страницPCM 5121Fabio Da Silva Assunçao AssunçaoОценок пока нет

- Hfe Panasonic Sa-Pm54e Eb Eg Service enДокумент115 страницHfe Panasonic Sa-Pm54e Eb Eg Service enMantasPuskoriusОценок пока нет

- Dacmagic.: Service Manual - Ap25144/1Документ15 страницDacmagic.: Service Manual - Ap25144/1Michał TuliszkiewiczОценок пока нет

- C4 Data Sheet: General Description Analog-Controlled DigitalДокумент4 страницыC4 Data Sheet: General Description Analog-Controlled DigitalChristian FloresОценок пока нет

- SMD Chip 89412CNДокумент82 страницыSMD Chip 89412CNdinh vinh nguyenОценок пока нет

- STA308A: Multichannel Digital Audio Processor With DDX™Документ46 страницSTA308A: Multichannel Digital Audio Processor With DDX™Milka RamirezОценок пока нет

- Digital TD Controller: For NEXO PS Series Cabinets and LS SubsДокумент2 страницыDigital TD Controller: For NEXO PS Series Cabinets and LS SubsrummanhzОценок пока нет

- CS42448 Audio DAC ADCДокумент66 страницCS42448 Audio DAC ADCQuinta EspОценок пока нет

- Tda 8425Документ24 страницыTda 8425vali dОценок пока нет

- High-Performance 24-Bit, 216Khz Sampling Stereo Audio Analog-To-Digital ConverterДокумент31 страницаHigh-Performance 24-Bit, 216Khz Sampling Stereo Audio Analog-To-Digital Converterharigopalk12Оценок пока нет

- Pcm175X 24-Bit, 192-Khz Sampling, Enhanced Multilevel, Delta-Sigma, Audio, Digital-To-Analog ConverterДокумент41 страницаPcm175X 24-Bit, 192-Khz Sampling, Enhanced Multilevel, Delta-Sigma, Audio, Digital-To-Analog ConverterSATYAM NAIDUОценок пока нет

- DX2 DatasheetДокумент1 страницаDX2 DatasheetAgin TersakitiОценок пока нет

- HTTPSWWW - Micro Semiconductor - Hudatasheet97 AK4628AVQ PDFДокумент42 страницыHTTPSWWW - Micro Semiconductor - Hudatasheet97 AK4628AVQ PDFPoon Electronic Training CentreОценок пока нет

- G2 ServiceManual PDFДокумент37 страницG2 ServiceManual PDFAntonio Fernandes100% (1)

- Obsolete Product(s) - Obsolete Product(s) : STA308AДокумент63 страницыObsolete Product(s) - Obsolete Product(s) : STA308AJorgeОценок пока нет

- Protea-4 24c PDFДокумент2 страницыProtea-4 24c PDFwahyuОценок пока нет

- VX-4500/4600 Series: VHF/UHF Mobile RadiosДокумент2 страницыVX-4500/4600 Series: VHF/UHF Mobile RadiosLaraОценок пока нет

- Very High Speed 16-Bit, Sampling A/D Converters: in A Space-Saving 46-Pin Hybrid PackageДокумент8 страницVery High Speed 16-Bit, Sampling A/D Converters: in A Space-Saving 46-Pin Hybrid PackageСергей КолосовОценок пока нет

- Features: Crystalclear™ Portable Isa Audio SystemДокумент98 страницFeatures: Crystalclear™ Portable Isa Audio Systemradaki-1Оценок пока нет

- DUO Tech DetailsДокумент3 страницыDUO Tech Detailscagen8684Оценок пока нет

- 02-Maxon SD-670D Series Spec SheetДокумент2 страницы02-Maxon SD-670D Series Spec SheetAlexandre Barbieri FolatreОценок пока нет

- Motorola Mag One VZ 20 Walkie TalkieДокумент2 страницыMotorola Mag One VZ 20 Walkie TalkietoitkitcoОценок пока нет

- Adi2 e ManualДокумент17 страницAdi2 e ManualDanielo ErréОценок пока нет

- 2 X 3 W Dual/Quad Power Amplifier For Car Radio: ProtectionsДокумент10 страниц2 X 3 W Dual/Quad Power Amplifier For Car Radio: ProtectionsJosé VidalОценок пока нет

- Audio Tda8567q Spec enДокумент20 страницAudio Tda8567q Spec envetchboyОценок пока нет

- 4 X 30W Quad Bridge Car Radio Amplifier: Protections: DescriptionДокумент12 страниц4 X 30W Quad Bridge Car Radio Amplifier: Protections: DescriptionvetchboyОценок пока нет

- Audio Tda8567q Spec enДокумент20 страницAudio Tda8567q Spec envetchboyОценок пока нет

- Audio Tda8510j Spec enДокумент16 страницAudio Tda8510j Spec envetchboyОценок пока нет

- Audio Tda8569q Spec enДокумент20 страницAudio Tda8569q Spec envetchboyОценок пока нет

- CD-R/RW Playback Shock Proof CDP Chipset Specification: (Full Digit LCD Model)Документ16 страницCD-R/RW Playback Shock Proof CDP Chipset Specification: (Full Digit LCD Model)vetchboyОценок пока нет

- TDA7384A: 4 X 35W Quad Bridge Car Radio AmplifierДокумент9 страницTDA7384A: 4 X 35W Quad Bridge Car Radio AmplifierGerardo Moreno RenteriaОценок пока нет

- Tda 7313Документ15 страницTda 7313jordachadiОценок пока нет

- Tda 7296Документ14 страницTda 7296Mayra GonzálezОценок пока нет

- 4 X 18W Bridge Car Radio Amplifier: Protections: DescriptionДокумент10 страниц4 X 18W Bridge Car Radio Amplifier: Protections: DescriptionvetchboyОценок пока нет

- Digital Controlled Stereo Audio Processor With Loudness: DescriptionДокумент14 страницDigital Controlled Stereo Audio Processor With Loudness: DescriptionvetchboyОценок пока нет

- Dual Btl/Quad Power Amplifier For Car Radio: ProtectionsДокумент14 страницDual Btl/Quad Power Amplifier For Car Radio: ProtectionsvetchboyОценок пока нет

- 120V - 100W Dmos Audio Amplifier With Mute/St-By: Multipower BCD TechnologyДокумент13 страниц120V - 100W Dmos Audio Amplifier With Mute/St-By: Multipower BCD TechnologyvetchboyОценок пока нет

- Amplificador 20W RMS TDA2003 Con Placa PCBДокумент15 страницAmplificador 20W RMS TDA2003 Con Placa PCBEnya Andrea Ribba Hernandez100% (5)

- Tda7294 PDFДокумент16 страницTda7294 PDFRoger NunesОценок пока нет

- Tda 7265 2 x25 WДокумент12 страницTda 7265 2 x25 WJavier CanaviriОценок пока нет

- 30W Bridge Car Radio Amplifier: DescriptionДокумент10 страниц30W Bridge Car Radio Amplifier: DescriptionvetchboyОценок пока нет

- TDA1554Q 44W Audio AmplifierДокумент11 страницTDA1554Q 44W Audio Amplifiersava7698Оценок пока нет

- Tda 7269aДокумент7 страницTda 7269aAlexa DanОценок пока нет

- TDA 2822M CircuitoДокумент11 страницTDA 2822M CircuitoDATA24Оценок пока нет

- 10W Car Radio Audio Amplifier: DescriptionДокумент11 страниц10W Car Radio Audio Amplifier: DescriptionvetchboyОценок пока нет

- Tda 2004Документ11 страницTda 2004Diana Belen Rodriguez HernandezОценок пока нет

- Audio Tda2002 Spec enДокумент2 страницыAudio Tda2002 Spec envetchboyОценок пока нет

- STK442 110Документ4 страницыSTK442 110Ivan AsimovОценок пока нет

- Description: Angus Electronics Company LimitedДокумент9 страницDescription: Angus Electronics Company LimitedvetchboyОценок пока нет

- TA2041 Four Channel Class-T Digital Audio Amplifier Using Digital Power Processing (DPP) TechnologyДокумент18 страницTA2041 Four Channel Class-T Digital Audio Amplifier Using Digital Power Processing (DPP) TechnologyvetchboyОценок пока нет

- Audio Tas5100a Spec enДокумент15 страницAudio Tas5100a Spec envetchboyОценок пока нет

- Low Power Quad Operational Amplifiers: LM124 LM224 - LM324Документ13 страницLow Power Quad Operational Amplifiers: LM124 LM224 - LM324vetchboyОценок пока нет

- Description: Angus Electronics Company LimitedДокумент13 страницDescription: Angus Electronics Company LimitedvetchboyОценок пока нет

- High Voltage Switchgear Type 8DN8 72,5 KV and Above Current TransformersДокумент3 страницыHigh Voltage Switchgear Type 8DN8 72,5 KV and Above Current Transformersমোঃ মহসিনОценок пока нет

- Product Specifications: W2X-6516DS - VTMДокумент3 страницыProduct Specifications: W2X-6516DS - VTMEvgeny VakhteevОценок пока нет

- Tutorial 2 Chapter 2: Direct CurrentДокумент8 страницTutorial 2 Chapter 2: Direct CurrentSYAFIQAH ISMAILОценок пока нет

- Ada 6.1 & Ampx4: Ada 6.1 Surround Processor & 4 Channel Power Amplifier Operations & Installation ManualДокумент19 страницAda 6.1 & Ampx4: Ada 6.1 Surround Processor & 4 Channel Power Amplifier Operations & Installation ManualCesar Eddy Diaz HernandezОценок пока нет

- Lokozo Battery Mangement System Bms LP 15s60aДокумент2 страницыLokozo Battery Mangement System Bms LP 15s60aPhani ArvapalliОценок пока нет

- Compact NS - 630A - 31790Документ3 страницыCompact NS - 630A - 31790becemОценок пока нет

- Power Calculation Summary and ExamplesДокумент12 страницPower Calculation Summary and ExamplesHernán RodarteОценок пока нет

- Design and Simulation of 2:1 Mux Using Multiple Logic GatesДокумент58 страницDesign and Simulation of 2:1 Mux Using Multiple Logic Gatesdurga manisha100% (1)

- SmpsДокумент11 страницSmpsBhaskar RamОценок пока нет

- Lenovo Server Storage Price List 2019 SingaporeДокумент57 страницLenovo Server Storage Price List 2019 SingaporeAnchor Business & IT SolutionsОценок пока нет

- Unit-4. Programmable Logic ControllerДокумент15 страницUnit-4. Programmable Logic ControllerHaripriya PalemОценок пока нет

- 2 SD 424Документ2 страницы2 SD 424Ruben David Ibañez RetamalОценок пока нет

- Set 1 Linear Integrated Circuits & Applications (15A04503)Документ4 страницыSet 1 Linear Integrated Circuits & Applications (15A04503)N.RAMAKUMARОценок пока нет

- ManDistr SDM1 Standard Eng 1 5Документ12 страницManDistr SDM1 Standard Eng 1 5Emrah AltındişОценок пока нет

- Objective: Design A Practical Integrator Circuit Using Common OP AMP Circuits. TestДокумент10 страницObjective: Design A Practical Integrator Circuit Using Common OP AMP Circuits. TestVinoth KumarОценок пока нет

- Logic Design Styles: Dinesh SharmaДокумент6 страницLogic Design Styles: Dinesh Sharmachandan choudharyОценок пока нет

- DocДокумент36 страницDocjuanОценок пока нет

- Electronic Circuits For Biological Engineering Laboratory: BE154L/A43/4Q1920Документ34 страницыElectronic Circuits For Biological Engineering Laboratory: BE154L/A43/4Q1920Kylle SaligumbaОценок пока нет

- RF Communications Test Set Family HPДокумент56 страницRF Communications Test Set Family HPdanielbs1969Оценок пока нет

- Multi Cycle ProcessorДокумент26 страницMulti Cycle Processorpowergla139556Оценок пока нет

- Chapter 3 - Alternating Current MetersДокумент35 страницChapter 3 - Alternating Current MetersANDREW LEONG CHUN TATT STUDENTОценок пока нет

- AppC PDFДокумент10 страницAppC PDFGuilherme PohlОценок пока нет

- EON515 JBLДокумент3 страницыEON515 JBLalexnder gallegoОценок пока нет

- MESFET Distributed Amplifier Design GuidelinesДокумент8 страницMESFET Distributed Amplifier Design Guidelinessanjeevsoni64Оценок пока нет

- DPS-40 UPBPSPDEL002 Philips PSUДокумент3 страницыDPS-40 UPBPSPDEL002 Philips PSUAndres OrlaynetaОценок пока нет

- Ds Ah 0079344Документ2 страницыDs Ah 0079344Ursu AlexОценок пока нет

- Touch Screen OmronДокумент6 страницTouch Screen OmronCesar VicenteОценок пока нет

- FreeBSD Boot LogДокумент8 страницFreeBSD Boot LogsegamegaОценок пока нет