Академический Документы

Профессиональный Документы

Культура Документы

Chapter 1: Introduction To Asics

Загружено:

Ali AhmadИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Chapter 1: Introduction To Asics

Загружено:

Ali AhmadАвторское право:

Доступные форматы

Introduction to ASIC Design

Chapter 1: Introduction to ASICs

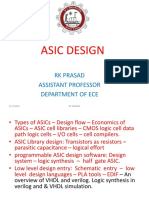

Key concepts: The difference between full-custom and semi custom ASICs The difference between standard-cell, gate-array, and programmable ASICs ASIC design flow Design economics ASIC cell library An ASIC (a-sick) is an application-specific integrated circuit A gate equivalent is a NAND gate F = A B (IBM uses a NOR gate), or four transistors History of integration: small-scale integration ( SSI , ~10 gates per chip, 60s), medium-scale integration ( MSI , ~1001000 gates per chip, 70s), large-scale integration ( LSI , ~100010,000 gates per chip, 80s), very large-scale integration ( VLSI , ~10,000100,000 gates per chip, 90s), ultra large scale integration ( ULSI , ~1M10M gates per chip) History of technology: bipolar technology and transistortransistor logic (TTL) preceded metal-oxide-silicon (MOS) technology because it was difficult to make metal-gate n -channel MOS (nMOS or NMOS); the introduction of complementary MOS (CMOS, never cMOS) greatly reduced power. The feature size is the smallest shape you can make on a chip and is measured in l or lambda Origin of ASICs: the standard parts , initially used to design microelectronic systems , were gradually replaced with a combination of glue logic , custom ICs , dynamic random-access memory ( DRAM ) and static RAM ( SRAM ) History of ASICs: The IEEE Custom Integrated Circuits Conference (CICC) and IEEE International ASIC Conference document the development of ASICs

ali.raza.anjum@gmail.com

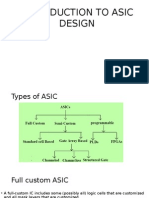

Introduction to ASIC Design Application-specific standard products (ASSPs) are a cross between standard parts and ASICs 1.1 Types of ASICs ICs are made on a wafer. Circuits are built up with successive mask layers . The number of masks used to define the interconnect and other layers is different between full-custom ICs and programmable ASICs Full-Custom ASICs Standard-CellBased ASICs Gate-ArrayBased ASICs Channeled Gate Array Channel less Gate Array Structured Gate Array Programmable Logic Devices Field-Programmable Gate Arrays

1.1.1 Full-Custom ASICs All mask layers are customized in a full-custom ASIC . It only makes sense to design a full-custom IC if there are no libraries available. Full-custom offers the highest performance and lowest part cost (smallest die size) with the disadvantages of increased design time, complexity, design expense, and highest risk. Microprocessors were exclusively full-custom, but designers are increasingly turning to semicustom ASIC techniques in this area too. Other examples of full-custom ICs or ASICs are requirements for high-voltage

ali.raza.anjum@gmail.com

II

Introduction to ASIC Design 1.1.2 Standard-CellBased ASICs A cell-based ASIC (CBIC sea-bick): Standard cells Possibly mega cells , mega functions , full-custom blocks , system-level macros ( SLMs ), fixed blocks , cores , or Functional Standard Blocks ( FSBs ) All mask layers are customizedtransistors and interconnect Custom blocks can be embedded Manufacturing lead time is about eight weeks.

1.1.3 Gate-ArrayBased ASICs A gate array , masked gate array , MGA , or prediffused array uses macros ( books ) to reduce turnaround time and comprises a base array made from a base cell or primitive cell . There are three types:

Channeled gate arrays Channel less gate arrays Structured gate arrays

1.1.4 Channeled Gate Array A channeled gate array: Only the interconnect is customized The interconnect uses predefined spaces between rows of base cells Manufacturing lead time is between two days and two weeks

ali.raza.anjum@gmail.com

III

Introduction to ASIC Design 1.1.5 Channelless Gate Array A channel less gate array (channel-free gate array , sea-of-gates array , or SOG array) Only some (the top few) mask layers are customizedthe interconnect Manufacturing lead time is between two days and and two weeks

1.1.6 Structured Gate Array An embedded gate array or structured gate array ( master slice or master image ) Only the interconnect is customized Custom blocks (the same for each design) can be embedded Manufacturing lead time is between two days and two weeks.

1.1.7 Programmable Logic Devices A programmable logic device ( PLD ) No customized mask layers or logic cells Fast design turnaround A single large block of programmable interconnect ali.raza.anjum@gmail.com IV

Introduction to ASIC Design A matrix of logic macro cells that usually consist of

Examples and types of PLDs: Read-only memory ( ROM ) programmable ROM or PROM electrically programmable ROM , or EPROM An erasable PLD (EPLD) electrically erasable PROM , or EEPROM UV-erasable PROM , or UVPROM mask-programmable ROM

A mask-programmed PLD usually uses bipolar technology Logic arrays may be either a Programmable Array Logic (PAL, a registered trademark of AMD) or a programmable logic array (PLA); both have an AND plane and an OR plane

1.1.8 Field-Programmable Gate Arrays A field-programmable gate array (FPGA) or complex PLD : None of the mask layers are customized A method for programming the basic logic cells and the interconnect The core is a regular array of programmable basic logic cells that can implement combinational as well as sequential logic (flip-flops) A matrix of programmable interconnect surrounds the basic logic cells

ali.raza.anjum@gmail.com

Introduction to ASIC Design Programmable I/O cells surround the core Design turnaround is a few hours

1.2 Design Flow A design flow is a sequence of steps to design an ASIC: 1. Design entry: Using a hardware description language (HDL) or schematic entry. 2. Logic synthesis: Produces a netlist logic cells and their connections. 3. System partitioning: Divide a large system into ASIC-sized pieces. 4. Pre-layout simulation: Check to see if the design functions correctly. 5. Floor-planning: Arrange the blocks of the netlist on the chip. 6. Placement: Decide the locations of cells in a block. 7. Routing: Make the connections between cells and blocks. 8. Extraction: Determine the resistance and capacitance of the inter-connect. 9. Post-layout simulation: Check to see the design still works with the added loads of the inter-connect.

ali.raza.anjum@gmail.com

VI

Introduction to ASIC Design

1.4 Economics of ASICs Well compare the most popular types of ASICs: an FPGA, an MGA, and a CBIC. The figures in the following sections are approximate and used to illustrate the different components of cost. 1.4.1 Comparison between ASIC Technologies 1.4.2 Product Cost 1.4.3 ASIC Fixed Costs 1.4.4 ASIC Variable Costs 1.4.1 Comparison between ASIC Technologies Example of an ASIC part cost: A 0.5 m m, 20 k-gate array might cost 0.01 0.02 cents/gate (for more than 10,000 parts) or $2$4 per part, but an equivalent FPGA might be $20. When does it make sense to use a more expensive part? This is what we shall examine next.

ali.raza.anjum@gmail.com

VII

Introduction to ASIC Design 1.4.2 Product Cost In a product cost there are fixed costs and variable costs (the number of products sold is the sales volume):

total product cost = fixed product cost + variable product cost

products sold

In a product made from parts the total cost for any part is

total part cost = fixed part cost + variable cost per part

volume of parts

For example, suppose we have the following (imaginary) costs:

FPGA: $21,800 (fixed) $39 (variable) MGA: $86,000 (fixed) $10 (variable) CBIC $146,000 (fixed) $8 (variable)

Then we can calculate the following break-even volumes:

FPGA/MGA FPGA/CBIC MGA/CBIC

2000 parts 4000 parts 20,000 part

ali.raza.anjum@gmail.com

VIII

Introduction to ASIC Design 1.4.3 ASIC Fixed Costs

Examples of fixed costs: training cost for a new electronic design automation (EDA) system hardware and software cost productivity production test and design for test programming costs for an FPGA nonrecurring-engineering (NRE) test vectors and test-program development cost pass (turn or spin)

ali.raza.anjum@gmail.com

IX

Introduction to ASIC Design profit model represents the profit flow during the product lifetime product velocity second source

1.4.4 ASIC Variable Costs Factors affecting fixed costs: wafer size wafer cost Moores Law (Gordon Moore of Intel) gate density gate utilization die size die per wafer defect density yield die cost profit margin (depends on fab or fabless ) price per gate part cost

ali.raza.anjum@gmail.com

Introduction to ASIC Design 1.5 ASIC Cell Libraries You can: 1. use a design kit from the ASIC vendor 2. buy an ASIC-vendor library from a library vendor 3. you can build your own cell library (1) is usually a phantom library the cells are empty boxes, or phantoms , you hand off your design to the ASIC vendor and they perform phantom instantiation (Synopsys CBA) (2) Involves a buy-or-build decision. You need a qualified cell library (qualified by the ASIC foundry ) If you own the masks (the tooling ) you have a customerowned tooling ( COT , pronounced see-oh-tee) solution (which is becoming very popular) (3) involves a complex library development process: cell layout behavioral model Verilog/VHDL model timing model test strategy characterization circuit extraction process control monitors ( PCMs ) or drop-ins cell schematic cell icon layout versus schematic ( LVS ) check cell icon logic synthesis retargeting wire-load model routing model phantom

ali.raza.anjum@gmail.com

XI

Introduction to ASIC Design 1.6 Summary

Types of ASIC ASIC type Full-custom Semicustom Family member Analog/digital Cell-based (CBIC) Masked gate array (MGA) Programmable Field-programmable gate array (FPGA) Programmable logic device (PLD) Key concepts:

Custom mask layers All All Some None None

Custom logic cells Some None None None None

We could define an ASIC as a design style that uses a cell library The difference between full-custom and semicustom ASICs The difference between standard-cell, gate-array, and programmable ASICs The ASIC design flow Design economics including part cost, NRE, and breakeven volume The contents and use of an ASIC cell library

ali.raza.anjum@gmail.com

XII

Introduction to ASIC Design 1.7 Problems Suggested homework: 1.4, 1.5, 1.9 (from ASICs... the book)

ali.raza.anjum@gmail.com

XIII

Introduction to ASIC Design 1.8 Bibliography EE Times (ISSN 0192-1541, http://techweb.cmp.com/eet ) EDN (ISSN 0012-7515, http://www.ednmag.com ) EDAC (Electronic Design Automation Companies) (http://www.edac.org ) The Electrical Engineering page on the World Wide Web (E2W3) ( http://www.e2w3.com ) SEMATECH (Semiconductor Manufacturing Technology) (http://www.sematech.org) The MIT Semiconductor Subway ( http://www-mtl.mit.edu ) EDA companies at http://www.yahoo.com under Business_and_Economy in Companies/Computers/Software/Graphics/CAD/IC_Design The MOS Implementation Service (MOSIS) ( http://www.isi.edu ) The Microelectronic Systems Newsletter at http://www-ece.engr.utk.edu/ece NASA ( http://nppp.jpl.nasa.gov/dmg/jpl/loc/asic )

ali.raza.anjum@gmail.com

XIV

Introduction to ASIC Design 1.9 References Glasser, L. A., and D. W. Dobberpuhl. 1985. The Design and Analysis of VLSI Circuits. Reading, MA: Addison-Wesley, 473 p. ISBN 0-201-12580-3. TK7874.G573. Detailed analysis of circuits, but largely nMOS. Mead, C. A., and L. A. Conway. 1980. Introduction to VLSI Systems. Reading, MA: Addison-Wesley, 396 p. ISBN 0-201-04358-0. TK7874.M37. Weste, N. H. E., and K. Eshraghian. 1993. Principles of CMOS VLSI Design: A Systems Perspective. 2nd ed. Reading, MA: Addison-Wesley, 713 p. ISBN 0-20153376-6. TK7874.W46. Concentrates on full-custom design.

ali.raza.anjum@gmail.com

XV

Вам также может понравиться

- Asic PPT CompleteДокумент504 страницыAsic PPT CompleteSwaroop SОценок пока нет

- Asic CH1Документ16 страницAsic CH1Anonymous eWMnRr70qОценок пока нет

- ASic DesignДокумент14 страницASic DesignManpreet SinghОценок пока нет

- Unit I - 1Документ26 страницUnit I - 1Janakiram VОценок пока нет

- Unit 5Документ62 страницыUnit 5bhupendra1977Оценок пока нет

- Introduction To Asic DesignДокумент53 страницыIntroduction To Asic DesignPerumal NamasivayamОценок пока нет

- Fpga ArchitectureДокумент98 страницFpga ArchitectureKavya Vimal100% (1)

- AsicДокумент1 страницаAsicwalternampimadomОценок пока нет

- ASICs The Course BookДокумент506 страницASICs The Course Bookahmadafaq09100% (1)

- EE4S23 - ASIC Technology and Test SystemsДокумент39 страницEE4S23 - ASIC Technology and Test Systemsfahadmas872070Оценок пока нет

- Presentation On AsicsДокумент20 страницPresentation On AsicsShruti ChaudharyОценок пока нет

- WINSEM2019-20 ECE5014 ETH VL2019205005781 Reference Material I 20-Dec-2019 Types of ASICДокумент50 страницWINSEM2019-20 ECE5014 ETH VL2019205005781 Reference Material I 20-Dec-2019 Types of ASICAashishОценок пока нет

- Unit 1Документ50 страницUnit 1mohitОценок пока нет

- Ics Intended For A Specific Application E.G Chip For Toy Bear That Talks - 3 TypesДокумент60 страницIcs Intended For A Specific Application E.G Chip For Toy Bear That Talks - 3 Typeskldfurio111Оценок пока нет

- Unit 1and II - ASIC - Design NewДокумент120 страницUnit 1and II - ASIC - Design New20D076 SHRIN BОценок пока нет

- Asic Design Cadence DR D Gracia Nirmala RaniДокумент291 страницаAsic Design Cadence DR D Gracia Nirmala RaniAdline RiniОценок пока нет

- Introduction To Asics: Ni Logic Pvt. LTD., PuneДокумент84 страницыIntroduction To Asics: Ni Logic Pvt. LTD., PuneankurОценок пока нет

- Introduction To Asics: Ni Logic Pvt. LTD., PuneДокумент25 страницIntroduction To Asics: Ni Logic Pvt. LTD., PuneRAJKUMARОценок пока нет

- Module I-ASIC NBBДокумент49 страницModule I-ASIC NBB20D076 SHRIN BОценок пока нет

- Introduction To AsicsДокумент14 страницIntroduction To AsicsmuralitejasОценок пока нет

- Asic Design FlowДокумент9 страницAsic Design FlowUrs Amarjith SinghОценок пока нет

- Introduction To VLSI Design Custom and Semi Custom Design: Daviet Digital Circuit Logic Design Slide-1Документ77 страницIntroduction To VLSI Design Custom and Semi Custom Design: Daviet Digital Circuit Logic Design Slide-1delkatty1Оценок пока нет

- Introduction To AsicДокумент12 страницIntroduction To AsicSrinivas CherukuОценок пока нет

- Application-Specific Integrated Circuits (ASICs)Документ5 страницApplication-Specific Integrated Circuits (ASICs)ijeteeditor100% (1)

- ASIC Design Classification DetailsДокумент27 страницASIC Design Classification Detailsnaveenchand_a6Оценок пока нет

- Arjun PL Vlsi1Документ97 страницArjun PL Vlsi1Tony StarkОценок пока нет

- UNIT 5 - First HalfДокумент9 страницUNIT 5 - First Halfsvvarsha124Оценок пока нет

- Application Specific Integrated Circuits (ASIC) : Beit Vii UET TaxilaДокумент30 страницApplication Specific Integrated Circuits (ASIC) : Beit Vii UET TaxilaAsif MahmoodОценок пока нет

- Introduction To ASIC TechnologyДокумент6 страницIntroduction To ASIC Technologyrpa projectОценок пока нет

- Application-Specific Integrated Circuits: Dr. K. R. PasupathyДокумент77 страницApplication-Specific Integrated Circuits: Dr. K. R. PasupathyBhavani BhagyasreeОценок пока нет

- Design Abstraction and Validation VLSI MEDC 104Документ90 страницDesign Abstraction and Validation VLSI MEDC 104maheshsamanapally0% (1)

- Different Types of ASICДокумент21 страницаDifferent Types of ASICParth Shah100% (1)

- Rohini 55102868036Документ18 страницRohini 55102868036عليОценок пока нет

- CPLD and FpgaДокумент28 страницCPLD and FpgaUday KumarОценок пока нет

- Application - Specific.IC DesignFlowДокумент8 страницApplication - Specific.IC DesignFlowNandagopal SivakumarОценок пока нет

- VLSI M1 Ktunotes - inДокумент98 страницVLSI M1 Ktunotes - inaslakshmi153Оценок пока нет

- ASIC Cell LibrariesДокумент2 страницыASIC Cell Librariesrpa projectОценок пока нет

- Comparison Between ASIC TechnologyДокумент12 страницComparison Between ASIC Technologyasifpatel1234Оценок пока нет

- Vlsi Design StyleДокумент15 страницVlsi Design StyleSubir MaityОценок пока нет

- Unit I - 2Документ28 страницUnit I - 2Janakiram VОценок пока нет

- ASIC Design: Prabhavathi P Associate Professor Dept. of ECE, BNMITДокумент203 страницыASIC Design: Prabhavathi P Associate Professor Dept. of ECE, BNMITPrabhavathi ParameshwarappaОценок пока нет

- ASIC 1st Module NOTESДокумент29 страницASIC 1st Module NOTESmanjunathanaikv100% (2)

- System-on-Chip Design:: Dr. Syed Azhar Ali Zaidi Assistant ProfessorДокумент37 страницSystem-on-Chip Design:: Dr. Syed Azhar Ali Zaidi Assistant ProfessorBilal Haider TanoliОценок пока нет

- Programmable ASIC Design: Haibo Wang ECE Department Southern Illinois University Carbondale, IL 62901Документ25 страницProgrammable ASIC Design: Haibo Wang ECE Department Southern Illinois University Carbondale, IL 62901Huzur AhmedОценок пока нет

- EEE 313-Chapter-5-ImplimentationApproachДокумент34 страницыEEE 313-Chapter-5-ImplimentationApproachKhairul IslamОценок пока нет

- DEE6113 Topic 6Документ78 страницDEE6113 Topic 6Magesh Waran GanesanОценок пока нет

- Asic & Fpga Design QB For MeДокумент24 страницыAsic & Fpga Design QB For MejebajohannahsamuelОценок пока нет

- 14EC770 ASIC DESIGN K.Kalyani PDFДокумент270 страниц14EC770 ASIC DESIGN K.Kalyani PDFsayooj kОценок пока нет

- Asic Interview QuestionsДокумент2 страницыAsic Interview Questionspritam044Оценок пока нет

- Chapter 5: Asics vs. PldsДокумент13 страницChapter 5: Asics vs. PldsLaxmanaa GajendiranОценок пока нет

- Fpga Based System DesignДокумент30 страницFpga Based System DesignKrishna Kumar100% (1)

- System On Chip SOCДокумент25 страницSystem On Chip SOCHammadAliОценок пока нет

- Standard Cell Libraries: - Presentation by Abhay Dixit Meeta Bhate Kedar RajpathakДокумент18 страницStandard Cell Libraries: - Presentation by Abhay Dixit Meeta Bhate Kedar RajpathakSGSОценок пока нет

- SOC - BasicsДокумент52 страницыSOC - BasicsShanmukha Pulipati100% (2)

- Standard CellДокумент53 страницыStandard CellShwethОценок пока нет

- Asic Design: RK Prasad Assistant Professor Department of EceДокумент107 страницAsic Design: RK Prasad Assistant Professor Department of EceSri JalakamОценок пока нет

- METMEL 43 PP2 MNAI SmolaДокумент32 страницыMETMEL 43 PP2 MNAI SmolaSrinivas CherukuОценок пока нет

- Vlsi Design SlidesДокумент77 страницVlsi Design SlidesmigadОценок пока нет

- Vlsi JyoДокумент77 страницVlsi Jyoapi-3743621Оценок пока нет

- Lectrue # 12 and 13 - 30-04-08Документ26 страницLectrue # 12 and 13 - 30-04-08Ali AhmadОценок пока нет

- Matlab Training - SIMULINKДокумент8 страницMatlab Training - SIMULINKAtta RehmanОценок пока нет

- Lecture 2 - 30-01-08Документ17 страницLecture 2 - 30-01-08Ali AhmadОценок пока нет

- Matlab Training Session Iii Numerical Methods: Solutions To Systems of Linear EquationsДокумент14 страницMatlab Training Session Iii Numerical Methods: Solutions To Systems of Linear EquationsAli AhmadОценок пока нет

- Matlab Training Session Iv Simulating Dynamic Systems: Sampling The Solution EquationДокумент9 страницMatlab Training Session Iv Simulating Dynamic Systems: Sampling The Solution EquationAli AhmadОценок пока нет

- The Purpose of Business Activity: LECTURE # 01 & 02Документ9 страницThe Purpose of Business Activity: LECTURE # 01 & 02Ali AhmadОценок пока нет

- Matlab Training Session Vii Basic Signal Processing: Frequency Domain AnalysisДокумент8 страницMatlab Training Session Vii Basic Signal Processing: Frequency Domain AnalysisAli AhmadОценок пока нет

- Operators: Introduction To ASIC DesignДокумент6 страницOperators: Introduction To ASIC DesignAli AhmadОценок пока нет

- Printing The Model:: SimulinkДокумент8 страницPrinting The Model:: SimulinkAli AhmadОценок пока нет

- Introduction To VHDL: AIR University AU, E-9, IslamabadДокумент29 страницIntroduction To VHDL: AIR University AU, E-9, IslamabadAli AhmadОценок пока нет

- 2-Level Logic ( 0', 1') .: Introduction To ASIC DesignДокумент8 страниц2-Level Logic ( 0', 1') .: Introduction To ASIC DesignAli AhmadОценок пока нет

- Acknowledgement - 2Документ11 страницAcknowledgement - 2Ali AhmadОценок пока нет

- Matlab Training Session Ii Data Presentation: 2-D PlotsДокумент8 страницMatlab Training Session Ii Data Presentation: 2-D PlotsAli AhmadОценок пока нет

- Introduction To: Artificial IntelligenceДокумент31 страницаIntroduction To: Artificial IntelligenceAli AhmadОценок пока нет

- Introduction To Symbian Os: AIR University AU, PAF Complex, E-9, IslamabadДокумент64 страницыIntroduction To Symbian Os: AIR University AU, PAF Complex, E-9, IslamabadAli AhmadОценок пока нет

- Introduction To ASIC Design: Lab Report InstructionsДокумент1 страницаIntroduction To ASIC Design: Lab Report InstructionsAli AhmadОценок пока нет

- Introduction To ASIC Design: Lab Report StandardsДокумент1 страницаIntroduction To ASIC Design: Lab Report StandardsAli AhmadОценок пока нет

- Example 5.1: Multiplexer #1 Using OperatorsДокумент10 страницExample 5.1: Multiplexer #1 Using OperatorsAli AhmadОценок пока нет

- How Chips Are DesignedДокумент46 страницHow Chips Are DesignedAli AhmadОценок пока нет

- Sequential Code in VHDLДокумент42 страницыSequential Code in VHDLAli Ahmad0% (1)

- Second SessionalCourseOutlineДокумент1 страницаSecond SessionalCourseOutlineAli AhmadОценок пока нет

- System On Chips Soc'S & Multiprocessor System On Chips MpsocsДокумент42 страницыSystem On Chips Soc'S & Multiprocessor System On Chips MpsocsAli AhmadОценок пока нет

- Assignment # 3: The EndДокумент1 страницаAssignment # 3: The EndAli AhmadОценок пока нет

- Air University Fall 2005 Faculty of Engineering Department of Electronics Engineering Course InformationДокумент2 страницыAir University Fall 2005 Faculty of Engineering Department of Electronics Engineering Course InformationAli AhmadОценок пока нет

- Assignment 1Документ1 страницаAssignment 1Ali AhmadОценок пока нет

- Assignment#4Документ1 страницаAssignment#4Ali AhmadОценок пока нет

- State Machine Block DiagarmДокумент6 страницState Machine Block DiagarmAli AhmadОценок пока нет

- Digital Filters in VHDL LabДокумент5 страницDigital Filters in VHDL LabAli AhmadОценок пока нет

- Assignment#5Документ1 страницаAssignment#5Ali AhmadОценок пока нет

- A rA r r B A: To find B, and hence the magnetic field H = B/ μ, we take the curl of A. In spherical coordinatesДокумент14 страницA rA r r B A: To find B, and hence the magnetic field H = B/ μ, we take the curl of A. In spherical coordinatesAli AhmadОценок пока нет

- Chapter 1: Introduction: Σημειώσεις από το βιβλίο Operating System ConceptsДокумент11 страницChapter 1: Introduction: Σημειώσεις από το βιβλίο Operating System Conceptsengajmal1371Оценок пока нет

- PPP Feature Config Guide Rev CДокумент29 страницPPP Feature Config Guide Rev CSai Kyaw HtikeОценок пока нет

- Obia Release NotesДокумент40 страницObia Release Notesprakash9565Оценок пока нет

- Chi Square DistributionДокумент4 страницыChi Square DistributionIziОценок пока нет

- NachosДокумент16 страницNachosmkumarshahiОценок пока нет

- Gorm Day2Документ45 страницGorm Day2Ryan SmithОценок пока нет

- Linear ProgrammingДокумент13 страницLinear ProgrammingTan KIm HAn0% (1)

- Coding Decoding Practice Session 1 1Документ47 страницCoding Decoding Practice Session 1 1Aniket LamaОценок пока нет

- Chapter 8. Architecture DesignДокумент32 страницыChapter 8. Architecture DesignAlbert AmadoОценок пока нет

- Iso 10083 2006 en FR PDFДокумент11 страницIso 10083 2006 en FR PDFGiovanni BalderramaОценок пока нет

- Ap30 Data Sheet PDFДокумент6 страницAp30 Data Sheet PDFJuan Miguel Mogollon ParedesОценок пока нет

- Unit 3 - NormalizationДокумент59 страницUnit 3 - NormalizationNimish MakhariaОценок пока нет

- MathsДокумент40 страницMathsKrunal ShahОценок пока нет

- Activity 1Документ4 страницыActivity 1Benedict SungaОценок пока нет

- AWS - Services - and - Customer - Responsibility - Matrix - For - Alignment To CSFДокумент51 страницаAWS - Services - and - Customer - Responsibility - Matrix - For - Alignment To CSFApoorva BadolaОценок пока нет

- Block KlienДокумент4 страницыBlock KlienHeri SatuemcomОценок пока нет

- PreviewpdfДокумент23 страницыPreviewpdfstudio lineОценок пока нет

- Stryker Xenon 6000 Light Source: Troubleshooting GuideДокумент1 страницаStryker Xenon 6000 Light Source: Troubleshooting GuideHealthcare repair and serviceОценок пока нет

- Advanced Algorithms - Cse-CsДокумент2 страницыAdvanced Algorithms - Cse-Csaarthi devОценок пока нет

- Monitor MFL68702414 ManualДокумент192 страницыMonitor MFL68702414 ManualTasos KaratzoglouОценок пока нет

- LW050V2 Manual EngДокумент22 страницыLW050V2 Manual EngbtsorinОценок пока нет

- Under Ground Cable Fault Detection Using IOT-1Документ22 страницыUnder Ground Cable Fault Detection Using IOT-1Sarath V PradheepОценок пока нет

- Lister - HW4Документ3 страницыLister - HW4Jacqueline JensenОценок пока нет

- Crunchit! 2.0 Quick Start Guide: Texas A&M UniversityДокумент26 страницCrunchit! 2.0 Quick Start Guide: Texas A&M UniversityJim KimОценок пока нет

- Chapter 2-ITSA01Документ20 страницChapter 2-ITSA01Augustine Laureta100% (1)

- Update LogsДокумент170 страницUpdate Logsconeinha123Оценок пока нет

- Minh Nguyen ResumeДокумент2 страницыMinh Nguyen Resumeapi-537841053Оценок пока нет

- Worksheet 1Документ2 страницыWorksheet 1Victor FamilienaamОценок пока нет

- Image Search Engine: Resource GuideДокумент16 страницImage Search Engine: Resource Guideprakash_embsysОценок пока нет

- P Median ModelДокумент26 страницP Median ModelLeonardo CetreОценок пока нет