Академический Документы

Профессиональный Документы

Культура Документы

Quasi Resonant Controller: The Future of Analog IC Technology

Загружено:

Juarez GouveiaИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Quasi Resonant Controller: The Future of Analog IC Technology

Загружено:

Juarez GouveiaАвторское право:

Доступные форматы

HFC0100

QUASI RESONANT CONTROLLER

The Future of Analog IC Technology

DESCRIPTION

The HFC0100 is a peak current mode controller with Green Mode Operation. Its high efficiency feature over the entire line and load range meets the stringent world-wide energy efficiency requirements. The HFC0100 integrated with a high voltage current source, its valley detector ensures minimum Drain-Source voltage switching (Quasi-Resonant operation). When the output power falls below a given level, the controller enters the burst mode. The HFC0100 features variable protections like Thermal Shutdown (TSD), Vcc Under voltage Lockout (UVLO), Over Load Protection (OLP), Over Voltage Protection (OVP). The HFC0100 is available in the 8-pin SOIC8 package.

FEATURES

Universal Main Input Voltage (85~265VAC) Quasi-Resonant Operation Valley Switching for high efficiency and EMI Active Burst Mode for low standby power consumption Internal High Voltage Current Source High level of integration, allows a very low number external component count Maximum Frequency Limited Internal Soft Start Internal 250nS Leading Edge Blanking Thermal shutdown (auto restart with hysteresis) Vcc Under Voltage Lockout with Hysteresis (UVLO) Over Voltage Protection Over Load Protection.

APPLICATIONS

Battery charger: cellular phone, digital camera, video camera, electrical shaver, emergency lighting system, etc Standby power supply: CRT-TV, ProjectionTV, LCD-TV, PDP-TV, Desk top PC, Audio system, etc SMPS: Inc jet printer, DVD player/recorder, VCR, CD player, Set top box, Air conditioner, refrigerator, washing machine, dish washer, Adapter for NB, etc

For MPS green status, please visit MPS website under Quality Assurance. MPS and The Future of Analog IC Technology are Registered Trademarks of Monolithic Power Systems, Inc.

HFC0100 Rev. 1.01 www.MonolithicPower.com 9/23/2011 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2011 MPS. All Rights Reserved.

HFC0100QUASI RESONANT CONTROLLER

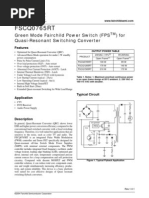

TYPICAL APPLICATION

T1 *

+ +

RTN

* HV N/C VCC VSD

4 3 2 1

5 6 7 8

Drive CS GND FB

HFC0100 Rev. 1.01 www.MonolithicPower.com 9/23/2011 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2011 MPS. All Rights Reserved.

HFC0100QUASI RESONANT CONTROLLER

ORDERING INFORMATION

Part Number* HFC0100HS Package SOIC8 Top Marking HFC100 Free Air Temperature (TA) -40C to +125C

*For Tape & Reel, add suffix Z (e.g. HFC0100HSZ); For RoHS compliant packaging, add suffix LF (e.g. HFC0100HSLFZ)

PACKAGE REFERENCE

TOP VIEW

VSD VCC NC HV 1 2 3 4 8 7 6 5 FB GND CS Drive

ABSOLUTE MAXIMUM RATINGS

(1)

Recommended Operation Conditions

(3)

HV Break Down Voltage .............. -0.7V to 700V Vcc, DRV to GND ...........................-0.3V to 22V FB, CS, VSD to GND ........................-0.3V to 7V (2) Continuous Power Dissipation(TA = +25C) ....1.3W Junction Temperature ...............................150C Thermal Shut Down ..................................150C Thermal Shut Down Hysteresis ..................50C Lead Temperature ....................................260C Storage Temperature .............. -60C to +150C ESD Capability Human Body Model (All Pins except HV) ............................................... 2.0kV ESD Capability Machine Model ................. 200V

Operating Vcc range ...........................8V to 20V Maximum Junction Temp. (TJ) ............. +125C

Thermal Resistance

(4)

SOIC8 .....................................96 ...... 45 ... C/W

Notes: 1) Exceeding these ratings may damage the device. 2) The maximum allowable power dissipation is a function of the maximum junction temperature TJ (MAX), the junction-toambient thermal resistance JA, and the ambient temperature TA. The maximum allowable continuous power dissipation at any ambient temperature is calculated by PD (MAX) = (TJ (MAX)-TA)/JA. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage. 3) The device is not guaranteed to function outside of its operating conditions. 4) Measured on JESD51-7, 4-layer PCB.

JA

JC

HFC0100 Rev. 1.01 www.MonolithicPower.com 9/23/2011 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2011 MPS. All Rights Reserved.

HFC0100QUASI RESONANT CONTROLLER

ELECTRICAL CHARACTERICS

For typical value TJ=25

Parameter Start-up Current Source (Pin HV) Charging current from Pin HV Leakage current from Pin HV Symbol Icharge Ileak Conditions Vcc=6V;VHV=400V With auxiliary supply; VHV=400V, Vcc=13V Min 1.4 -700 10.6 7.2 -Fs=100kHz, Vcc=12V VCC=6V ---------40 -High State; Ipin2=3.0mA Low State; Ipin2=-2.0mA Pull down from 2V to -100mV 7 -0.8 120 6.6 -------Typ 2 20 -11.8 8 5.5 2.0 450 10 4.5 3 2.4 0.5 0.7 3.7 55 10 7.5 -0.65 160 7.8 4.6 3.5 6 24 250 17 7 Max 2.6 --13 8.8 ----------70 -8 V -0.5 200 9 -------nS S S S V k nS Unit mA A V V V V mA A k V -mS V V V mV mV

Break Down Voltage VBR Supply Voltage Management (Pin Vcc) Vcc Upper Level at which the Internal VCCH High Voltage Current Source Stops Vcc Lower Level at which the Internal VCCL High Voltage Current Source Triggers Vcc Re-charge Level at which the Vccp protection occurs Internal IC Consumption, 1nF Load on Icc1 Drive Pin, Internal IC Consumption, Latch off Icc2 phase, Feedback Management (Pin FB) Internal Pull Up Resistor RFB Internal Pull Up Voltage Vup FB Pin to Current Limit Division Ratio Idiv Internal Soft-Start Time Tss FB Decreasing Level at which the VBURL controller enter the Burst Mode FB Increasing Level at which the VBURH controller leave the Burst Mode Over Load Set Point VOLP Valley Switching Management (Pin VSD) Valley Switching Threshold Voltage VVSD Valley Switching Hysteresis Vhys Pin VSD Clamp Voltage Valley Switching Propagation Delay VVSDH VVSDL TVSD

Minimum Off Time Tmin Re-start time After Last Valley detect Trestart Transition OVP Sampling Delay TOVPS Pin VSD OVP reference level VOVP Internal Impedance Rint Current Sampling Management (Pin CS) Leading Edge Blanking TLEB Driving Signal (Pin DRIVE) Sourcing Resistor RH Sinking Resistor RL

HFC0100 Rev. 1.01 www.MonolithicPower.com 9/23/2011 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2011 MPS. All Rights Reserved.

HFC0100QUASI RESONANT CONTROLLER

PIN FUNCTIONS

Pin # 1 2 3 4 5 6 7 8 Name VSD Vcc N/C HV Drive CS GND FB Description Input from the auxiliary flyback signal, it ensures discontinuous operation and valley switching. It also offers a fixed OVP detection. Supply voltage Pin. This pin is connected to an external bulk capacitor of typically 22uf and a ceramic capacitor of typically 0.1uF. This Pin ensures adequate creepage distance. Input for the start up current unit. Output of the driving signal. Input of the current sense. Ground. The Pin sets the peak current limit, by connecting an optocoupler to this Pin. A feedback voltage of 3.7V will trigger an over load protection, and a feedback voltage of 0.5V will trigger a burst mode operation.

HFC0100 Rev. 1.01 www.MonolithicPower.com 9/23/2011 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2011 MPS. All Rights Reserved.

HFC0100QUASI RESONANT CONTROLLER

TYPICAL PERFORMANCE CHARACTERISTICS

TA=25

IC Consumption Vs Vcc (No Output Load)

1100 1000 3400 3000 FS=100kHz FS=60kHz 2600 FS=100kHz

IC Consumption Vs Vcc (1nF Output Load)

3

Charging Current From Pin HV (Vcc=6V, VHV=400V) Vs Temperature

800 700 600 500 400

ICHARGE (mA)

ICC1 (uA)

900

2.5

ICC1 (uA)

2200 1800 1400 1000 10 11 12 13 14 15 16 17 18 VCC (V) FS=60kHz

1.5

10 11 12 13 14 15 16 17 18 VCC (V)

1 -40 -20

0 25 50 85 105 125 TEMPERATURE (oC)

12 11.8

Vcc Upper Level at which the Internal High Voltage Current Source Stops Vs Temperature

8.5 8.3 8.1

Vcc Lower Level at which the Internal High Voltage Current Source Triggers Vs Temperature

Pin FB Internal Pull Up Resistor Vs Temperature

12

11

VCCH (V)

VCCL (V)

11.6 11.4 11.2 11 -40 -20

10 7.9 7.7 7.5 -40 -20 9

25

50

85 105 125

25

50

85 105 125

8 -40 -20

25

50

85 105 125

TEMPERATURE (oC)

TEMPERATURE (oC)

TEMPERATURE (oC)

Over Load Set Point Vs Temperature

4

Valley Switching Threshold Voltage Vs Temperature

80 70

Minimum Off Time Vs Temperature

9

8.5

VVSD (mV)

3.8

VOLP (V)

TMIN (us)

60 50 40

3.6

7.5

3.4 -40 -20

25

50

85 105 125

30 -40 -20

25

50

85 105 125

7 -40 -20

25

50

85 105 125

TEMPERATURE (OC)

TEMPERATURE (OC)

TEMPERATURE (OC)

HFC0100 Rev. 1.01 www.MonolithicPower.com 9/23/2011 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2011 MPS. All Rights Reserved.

HFC0100QUASI RESONANT CONTROLLER

TYPICAL PERFORMANCE CHARACTERISTICS (continues)

TA=25

OVP Sampling Delay Vs Temperature

4 3.8

TSAMPLE (us) VREF (V)

Pin VSD OVP reference level Vs Temperature

6.2

Pin VSD Internal Impedance Vs Temperature

30 28 26

6.1

3.6 3.4 3.2 3 -40 -20 0 25 50 85 105 125 TEMPERATURE (OC)

6 24 5.9 22 20 -40 -20

5.8 -40 -20

0 25 50 85 105 125 TEMPERATURE (OC)

0 25 50 85 105 125 TEMPERATURE (OC)

Sourcing Resistor Vs Temperature

30

Sinking Resistor Vs Temperature

20 600

FB Decreasing Level at which the controller enter the Burst Mode Vs Temperature

25

15

VBURH(mV)

550

20

10

500

15

450

10 -40 -20

25

50

85 105 125

0 -40 -20

25

50

85 105 125

400 -40 -20

25

50

85 105 125

TEMPERATURE (OC)

TEMPERATURE (OC)

TEMPERATURE (OC)

800

FB Increasing Level at which the controller leave the Burst Mode Vs Temperature

750

VBURH(mV)

700

650

600 -40 -20

25

50

85 105 125

TEMPERATURE (OC)

HFC0100 Rev. 1.01 www.MonolithicPower.com 9/23/2011 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2011 MPS. All Rights Reserved.

HFC0100QUASI RESONANT CONTROLLER

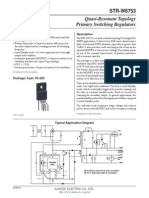

BLOCK DIAGRAME

Vcc(2)

Power Management

Start Up Unit

HV(4)

VSD(1)

Valley Detector

Driving Signal Managment Peak Current Limitation Burst Mode Control

Drive(5)

N.C.(3)

Protection Unit

CS(6)

GND(7)

FB(8)

Figure 1 Block Diagram

HFC0100 Rev. 1.01 www.MonolithicPower.com 9/23/2011 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2011 MPS. All Rights Reserved.

HFC0100QUASI RESONANT CONTROLLER

OPERATION

The HFC0100 incorporates all the necessary features needed to a reliable Switch Mode Power Supply. Its valley detector ensures minimum Drain-Source voltage switching (Quasi-Resonant operation). When the output power falls below a given level, the regulator enters the burst mode. An internal minimum off time limiter prevents the free running frequency to exceed 150kHz. Start-Up Initially, the IC is self supplying from the internal high voltage current source unit which drawn from the HV pin. The IC starts switching and the internal high voltage current source unit is stopped as soon as the voltage on Pin Vcc reaches the threshold VCCH11.8V. Before the supply is taken over by the auxiliary winding of the transformer, the Vcc capacitor supplies HFC0100 to maintain Vcc. Quasi-Resonant Operation The HFC0100 operates in Discontinuous Conduction Mode (DCM). The valley detector ensures minimum Drain-Source voltage switching (Quasi-Resonant operation) As a result, there are virtually no primary switch turn on losses and no secondary diode recovery losses. It ensures the reduction of the EMI noise. Figure2 shows the valley detector unit. When the voltage:

(VDS Vin )x Naux 24k x < 55mV Npri 24k + R VSD

Figure 2Valley Detector

VDS 100V/div

Valley Switching

4us/div

Figure 3Valley Switching To ensure the switching frequency below the EN55022 start limit---150kHz, HFC0100 employs an internal minimum off time limiter---7.8S, shows as figure 4.

VDS Drain Source Voltage of the primary FET VINInput Voltage Naux Auxiliary Winding Turns of the transformer Npri Primary Winding Turns of the transformer The valley detector sends out a valley signal to turn on the primary FET. Figure3 shows a typical drain source voltage waveform with valley switching.

VDS 100V/div

Toff7.8uS

2us/div

Figure 4Minimum Off Time Limit

HFC0100 Rev. 1.01 www.MonolithicPower.com 9/23/2011 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2011 MPS. All Rights Reserved.

HFC0100QUASI RESONANT CONTROLLER

VCC Under-Voltage Lock-out When the Vcc below the UVLO threshold-8V, the HFC0100 stops switching and the internal high voltage current source unit re-starts, the Vcc external bulk capacitor is re-charged by it. Figure 5 shows the typical waveform with Vcc under voltage lock out.

The auxiliary winding take over VCC VCCH=11.8V V CCL=8V ON Internal Current Source OFF

Figure 6OVP Sample Unit To avoid the mis-trigger due to the oscillation of the leakage inductance and the parasitic capacitance, the OVP sampling has a TOVPS blanking, typical 3.5S, shows as Figure 7.

VVSD

Sampling Here

Driving Signal

Figure 5Vcc Under-Voltage Lock Out Over-Voltage Protection (OVP) The positive plateau of auxiliary winding voltage is proportional to the output voltage, the OVP use the auxiliary winding voltage instead of directly monitoring the output voltage. The Figure 6 shows the OVP sample unit. If the voltage:

VO N aux 24k > 6V N SEC 24k + R VSD

0V

TOVPS

Figure 7 Over Load Protection (OLP) The maximum output power is limited by the maximum switching frequency and maximum primary peak current. If the output consumes more than the maximum output power, the output voltage is drawn below the set point, this reduces the current through the optocoupler LED, which also reduces the transistor current, thus increases the FB voltage. By continuously monitoring the Pin FB voltage, when the feedback voltage exceeds the threshold VOLP3.7V, it shuts off the switching cycle. The HFC0100 enters a safe low power operation that prevents from any lethal thermal or stress damage. As soon as the default disappears, the power supply resumes operation. During the start up or load transient, the FB voltage will be high enough temporarily to mistrigger the OLP, to prevent this undesired protection, OLP circuit is designed to be triggered after Vcc is decreased below 8.5V.

VOOutput voltage Naux Auxiliary Winding Turns of the transformer NSECSecondary transformer Winding Turns of the

The OVP circuit is triggered, and the HFC0100 stops the switching cycle and goes into latched fault condition. The controller stays fully latched in this position until the Vcc is decreased down to 3V, e.g. when the user unplugs the power supply from the main supply and re-plugs it.

HFC0100 Rev. 1.01 www.MonolithicPower.com 9/23/2011 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2011 MPS. All Rights Reserved.

10

HFC0100QUASI RESONANT CONTROLLER

Burst Operation To minimize the power dissipation in no load or light load, the HFC0100 enters the burst mode operation. As the load decreases, the FB voltage decreases,, the HFC0100 stops the switching cycle when the FB voltage drops below the threshold VBURL0.5V. And the output voltage starts to drop at a rate dependent on the load. This causes the FB voltage to rise again. Once the FB voltage exceeds the threshold VBURH 0.7V, switching resumes. The FB voltage then falls and rises repeatedly. The burst mode operation alternately enables and disables switching cycle of the MOSFET thereby reducing switching loss in the no load or light load conditions. Figure 8 shows the typical FB and Drive waveform during the burst mode.

VBURH:0.7V

Current Limit Setting The switch current is sensed by the resistor series between the Source of the FET and the ground. And the current limit is determined by the FB signal,

VLimit = VFB VFB = I div 3

. To limit the

maximum output power, the current limit is clamped at 1V when VFB is bigger than 3.3V. Leading Edge Blanking In order to avoid the premature termination of the switching pulse due to the parasitic capacitance, an internal leading edge blanking (LEB) unit is employed between the CS Pin and the current comparator input. During the blanking time, the path, CS Pin to the current comparator input, is blocked. Figure 9 shows the leading edge blanking.

VLimit

TLEB =250nS

VBURL:0.5V

VFB 200mV/div VDrive 5V/div 40us/div

Figure 8Burst Mode Thermal Shutdown (TSD) To prevents from any lethal thermal damage. The HFC0100 shuts down switching cycle when the inner temperature exceeds 150DegC. As soon as the inner temperature drops below 100DegC, the power supply resumes operation. Soft-Start To reduce the stress on primary MOSFET and secondary diode during start up, to smoothly establish the output voltage, the HFC0100 has an internal soft-start circuit that increases the current comparator inverting input voltage, together with the MOSFET current, slowly after it starts up. The pulse width to the power switching device is progressively increased to establish the correct working conditions for transformers, inductors, and capacitors.

t Figure 9Leading Edge Blanking Over Power Compensation

In the case of current sensing, shows as figure 10, the turn off of the FET is delayed due to the propagation delay of the control circuit, the delay time is the inherent characteristic of the control circuit, so Tdelay can be seen fixed. This delay will cause an overshoot of the peak current. I2 is bigger than I1 due to the bigger rising ratio(the higher input voltage, the bigger rising ratio).

HFC0100 Rev. 1.01 www.MonolithicPower.com 9/23/2011 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2011 MPS. All Rights Reserved.

11

HFC0100QUASI RESONANT CONTROLLER

The propagation delay is done by means of the feedforward resistor, shown as Figure 11. Through this method, adding one offset voltage at CS pin (the higher input voltage, the bigger offset voltage.).

ILim it

IL im it2 IL im it1 IL im it I1I2

t

Td elay Td elay T d elayTd elay

Figure 10Propagation delay of the current limit

V_bulk T1

HFC0100

Current Comparator

6

Rfeedforward Q1 R1

CS

V ref

C1

Rsense

Figure 11Over Power Compensation

Figure 12 shows the HFC0100 control flow chart. Figure 13 shows the HFC0100 evolution of the signals in presence of faults

HFC0100 Rev. 1.01 www.MonolithicPower.com 9/23/2011 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2011 MPS. All Rights Reserved.

12

HFC0100QUASI RESONANT CONTROLLER

Start Y Internal High Voltage Current Source ON Shut off the Switching Pulse Vcc Decrease to 5.5V Vcc<3V? N

Y OTP= Logic High?

Shut Down Internal High Voltage Current Source

Vcc>11.8V

Latch off the Switching Pulse N Y OVP= Logic High? N

Vcc<8V Y Soft Start Monitor Vcc

Thermal Monitor Pin VSD Monitor

Monitor VFB Y VFB<0.5V 0.5V<VFB<3.7V VFB>3.7V Vcc<8.5V? and OLP=Logic High Y N Continuous Fault Monitor QR mode Operation OLP=Logic High

Burst Mode Operation

VFB >0.7V

Toff<7.8uS

UVLO, OTP & OLP are auto restart , OVP is latch Release from the latch condition , need to unplug from the main input .

Y Constraint Toff_min7.8uS

Figure 12Control Flow Chart

HFC0100 Rev. 1.01 www.MonolithicPower.com 9/23/2011 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2011 MPS. All Rights Reserved.

13

HFC0100QUASI RESONANT CONTROLLER

Vcc

Start up

Regulation Occurs Here

Over Voltage Occurs Here

Unplug from main input Normal operation

Normal operation

Normal operation

11.8V 8.5V 5.5V

Driver

Driver Pluses

High voltage current source On

Off IFault Flag

Normal operation

OVP Fault Occurs Here

Normal operation

OLP Fault Occurs Here

Normal operation

OTP Fault Occurs Here

Normal operation

Figure 13Evolution of the Signals in Presence of Faults

HFC0100 Rev. 1.01 www.MonolithicPower.com 9/23/2011 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2011 MPS. All Rights Reserved.

14

HFC0100QUASI RESONANT CONTROLLER

PACKAGE INFORMATION

SOIC8

0.189(4.80) 0.197(5.00) 8 5 0.063(1.60) 0.024(0.61) 0.050(1.27)

PIN 1 ID

0.150(3.80) 0.157(4.00)

0.228(5.80) 0.244(6.20)

0.213(5.40)

TOP VIEW

RECOMMENDED LAND PATTERN

0.013(0.33) 0.020(0.51)

0.053(1.35) 0.069(1.75) SEATING PLANE 0.004(0.10) 0.010(0.25) 0.050(1.27) BSC

0.0075(0.19) 0.0098(0.25) SEE DETAIL "A"

FRONT VIEW

SIDE VIEW

0.010(0.25) x 45o 0.020(0.50) GAUGE PLANE 0.010(0.25) BSC

NOTE:

1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS. 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX. 5) DRAWING CONFORMS TO JEDEC MS-012, VARIATION AA. 6) DRAWING IS NOT TO SCALE.

0o-8o

0.016(0.41) 0.050(1.27)

DETAIL "A"

NOTICE: The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

HFC0100 Rev. 1.01 www.MonolithicPower.com 9/23/2011 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2011 MPS. All Rights Reserved.

15

Вам также может понравиться

- IC-ON-LINE - CN dm0365r 44840Документ20 страницIC-ON-LINE - CN dm0365r 44840MoscandoОценок пока нет

- LM5007 High Voltage (80V) Step Down Switching Regulator: FeaturesДокумент17 страницLM5007 High Voltage (80V) Step Down Switching Regulator: FeaturesbhushanchittaragiОценок пока нет

- Ncl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsДокумент10 страницNcl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsKhúc Hành QuânОценок пока нет

- DM0265Документ19 страницDM0265liberthОценок пока нет

- High Efficiency Low-Side N-Channel Controller For Switching RegulatorsДокумент33 страницыHigh Efficiency Low-Side N-Channel Controller For Switching Regulatorssoft4gsmОценок пока нет

- Apl 5336Документ20 страницApl 5336FlavianoSilvaОценок пока нет

- PD Derated at 8.5mW/ For Temperature Above Ta 25 (When Mounted On A PCB 70.0mm×70.0mm×1.6mm)Документ5 страницPD Derated at 8.5mW/ For Temperature Above Ta 25 (When Mounted On A PCB 70.0mm×70.0mm×1.6mm)Osama YaseenОценок пока нет

- Dap006 Dap6a DataДокумент15 страницDap006 Dap6a DataluisfeipezzОценок пока нет

- NCP1203 Advance Information PWM Current-Mode Controller For Universal Off-Line Supplies Featuring Standby and Short Circuit ProtectionДокумент12 страницNCP1203 Advance Information PWM Current-Mode Controller For Universal Off-Line Supplies Featuring Standby and Short Circuit ProtectionthongleОценок пока нет

- P1027P65 (SMPS)Документ30 страницP1027P65 (SMPS)Jesus Silva67% (3)

- FOD3180 2A Output Current, High Speed MOSFET Gate Driver OptocouplerДокумент13 страницFOD3180 2A Output Current, High Speed MOSFET Gate Driver OptocouplergsergwesrОценок пока нет

- DatasheetДокумент13 страницDatasheetadixadrianОценок пока нет

- CQ 0765RTДокумент24 страницыCQ 0765RTsonivitel100% (2)

- HT7 L4815 V 100Документ9 страницHT7 L4815 V 100Enéas BaroneОценок пока нет

- Tps 61183Документ25 страницTps 61183GilvaneSilvaОценок пока нет

- NCP1337 D PDFДокумент15 страницNCP1337 D PDFBoKi PoKiОценок пока нет

- Tps 2051 BДокумент29 страницTps 2051 Bdragon-red0816Оценок пока нет

- Preliminary Data Sheet TDA21101: FeaturesДокумент5 страницPreliminary Data Sheet TDA21101: FeaturesJuan RiosОценок пока нет

- LM25005 42V, 2.5A Step-Down Switching Regulator: Literature Number: SNVS411BДокумент24 страницыLM25005 42V, 2.5A Step-Down Switching Regulator: Literature Number: SNVS411BPravin MevadaОценок пока нет

- NCP 1207Документ18 страницNCP 1207soukehalhamedОценок пока нет

- Ir 1153Документ20 страницIr 1153ytnateОценок пока нет

- DRV 8811Документ22 страницыDRV 8811nelson_loboОценок пока нет

- 8 Pin Ic - FSQ510Документ15 страниц8 Pin Ic - FSQ510Raja Pathamuthu.GОценок пока нет

- Fan 7316Документ21 страницаFan 7316sontuyet82Оценок пока нет

- LCD Bias Power Integrated With WLED Backlight Drivers: FeaturesДокумент31 страницаLCD Bias Power Integrated With WLED Backlight Drivers: FeaturesJoseph BernardОценок пока нет

- 1.5A USB-Friendly Li-Ion Battery Charger and Power-Path Management ICДокумент33 страницы1.5A USB-Friendly Li-Ion Battery Charger and Power-Path Management ICanarchie2008Оценок пока нет

- APW7165Документ20 страницAPW7165Jorge BulacioОценок пока нет

- Boq 4.3.14 .M FinalДокумент16 страницBoq 4.3.14 .M FinalSiam Hasan100% (1)

- 1.5A Power Switching Regulator: DescriptionДокумент16 страниц1.5A Power Switching Regulator: DescriptionPravin MevadaОценок пока нет

- HS-2420RH - Fast Sample and HolДокумент8 страницHS-2420RH - Fast Sample and HolDeepa DevarajОценок пока нет

- HT7L4811 Non-Isolation Buck LED Lighting Driver With Active PFCДокумент12 страницHT7L4811 Non-Isolation Buck LED Lighting Driver With Active PFCEnéas BaroneОценок пока нет

- 1565 RTДокумент24 страницы1565 RTJose Samuel Robelto RОценок пока нет

- NCP1217, NCP1217A Enhanced PWM Current Mode Controller For High Power Universal Off Line SuppliesДокумент18 страницNCP1217, NCP1217A Enhanced PWM Current Mode Controller For High Power Universal Off Line SuppliesalexОценок пока нет

- CCFL Inverter IC OZ960Документ12 страницCCFL Inverter IC OZ960davesworkshopОценок пока нет

- Ir1161lpbf - Infineon Solutions For Transportation 24V To 60VДокумент25 страницIr1161lpbf - Infineon Solutions For Transportation 24V To 60VAnonymous R0s4q9X8Оценок пока нет

- Intelligent CCFL Inverter Controller: FeaturesДокумент12 страницIntelligent CCFL Inverter Controller: FeaturesMirosław DżumakОценок пока нет

- DL 0165 RДокумент20 страницDL 0165 Rledu035Оценок пока нет

- Tda 4601Документ8 страницTda 4601Mirko AleksicОценок пока нет

- Fan 7530Документ20 страницFan 7530aldo_suviОценок пока нет

- NCP1234AD65R2GДокумент33 страницыNCP1234AD65R2GAndré Frota PaivaОценок пока нет

- FSFR1800Документ17 страницFSFR1800sontuyet82Оценок пока нет

- APW7159AДокумент23 страницыAPW7159AVoicu AdrianОценок пока нет

- MC34067 PDFДокумент16 страницMC34067 PDFwj18868908Оценок пока нет

- Very Low Input /very Low Dropout 2 Amp Regulator With EnableДокумент10 страницVery Low Input /very Low Dropout 2 Amp Regulator With EnableCao Ngọc ThànhОценок пока нет

- FAN7602B Green Current-Mode PWM Controller: Features DescriptionДокумент17 страницFAN7602B Green Current-Mode PWM Controller: Features DescriptionNichole RollinsОценок пока нет

- SSC2001S Application NoteДокумент18 страницSSC2001S Application NoteGerardo Mendez CamarilloОценок пока нет

- Uc3842b 3843BДокумент10 страницUc3842b 3843Bbob75Оценок пока нет

- STR W6753 DatasheetДокумент8 страницSTR W6753 DatasheetjgerabmОценок пока нет

- 1207p Smps ControlДокумент18 страниц1207p Smps ControlVijay MistryОценок пока нет

- Fonte PWS-801Документ20 страницFonte PWS-801LuizОценок пока нет

- LD7750 High-Voltage PWM ControllerДокумент20 страницLD7750 High-Voltage PWM ControllerAndres Alegria100% (1)

- FSQ110 Green Mode Fairchild Power Switch (FPS™) : Features DescriptionДокумент12 страницFSQ110 Green Mode Fairchild Power Switch (FPS™) : Features DescriptionJohan BeckersОценок пока нет

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Оценок пока нет

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsОт EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsРейтинг: 3.5 из 5 звезд3.5/5 (6)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Рейтинг: 2.5 из 5 звезд2.5/5 (3)

- Analog Circuit Design Volume Three: Design Note CollectionОт EverandAnalog Circuit Design Volume Three: Design Note CollectionРейтинг: 3 из 5 звезд3/5 (2)

- Office of Building Technology, State and Community Programs Energy Efficiency and Renewable Energy - U.S. Department of EnergyДокумент15 страницOffice of Building Technology, State and Community Programs Energy Efficiency and Renewable Energy - U.S. Department of Energyapi-309082881Оценок пока нет

- Testando TiristorДокумент2 страницыTestando TiristorJuarez GouveiaОценок пока нет

- 2009 11 17 Arduino Basics PDFДокумент36 страниц2009 11 17 Arduino Basics PDFgpt1708Оценок пока нет

- AL-73932-AB Instructions E00200 Error AnalysisДокумент10 страницAL-73932-AB Instructions E00200 Error AnalysisJuarez GouveiaОценок пока нет

- Equivalência de Transistores 2Документ6 страницEquivalência de Transistores 2Fly ModelismoОценок пока нет

- Arc 2Документ2 страницыArc 2chandrabhushan kushwahaОценок пока нет

- Assignment No.2: Topic: OscillaДокумент6 страницAssignment No.2: Topic: OscillaMuhammad Mubashar AwaisiОценок пока нет

- Synchronous Rectification For Forward Converters PDFДокумент41 страницаSynchronous Rectification For Forward Converters PDFtongaiОценок пока нет

- Current, Resistance, and Electromotive Force: Powerpoint Lectures ForДокумент39 страницCurrent, Resistance, and Electromotive Force: Powerpoint Lectures ForZia Aryanti ZeeОценок пока нет

- Voltage Sag Mitigation Using Dynamic Voltage Restorer SystemДокумент5 страницVoltage Sag Mitigation Using Dynamic Voltage Restorer SystemAnonymous xaeuoo4Оценок пока нет

- Ruggedcom Win: Wide Area Private Wireless SystemsДокумент16 страницRuggedcom Win: Wide Area Private Wireless SystemsJorge Orlando Aballe ArvinculaОценок пока нет

- 24CL128 Data SheetДокумент23 страницы24CL128 Data Sheetmsalem73Оценок пока нет

- Centrifuge DSC-203,303SD (Manual) - 2021Документ3 страницыCentrifuge DSC-203,303SD (Manual) - 2021Leah DarinoОценок пока нет

- STEC-NA2 - Operation Edition - EngДокумент155 страницSTEC-NA2 - Operation Edition - EngcristinainoueОценок пока нет

- ElectrostaticsДокумент18 страницElectrostaticsRishi MishraОценок пока нет

- Cross Correlation and Autocorrelation On MatlabДокумент14 страницCross Correlation and Autocorrelation On Matlabmuddassir07100% (7)

- Controller ManualДокумент58 страницController Manualmarcelb64Оценок пока нет

- 8999 3632 00 Diagrams and DrawingsДокумент128 страниц8999 3632 00 Diagrams and DrawingsArtur ArtSpiОценок пока нет

- Ac&Dc CircuitsДокумент142 страницыAc&Dc CircuitsJerry Comia0% (1)

- BS en 9934-3Документ21 страницаBS en 9934-3The Normal HeartОценок пока нет

- SCADAДокумент15 страницSCADARam VBITОценок пока нет

- Embedded System & Microcontroller Application Course Code: 4351102Документ8 страницEmbedded System & Microcontroller Application Course Code: 4351102Raggy TannaОценок пока нет

- Prok ManualДокумент8 страницProk ManualaymaanfkОценок пока нет

- Unit V Design of Controllers For Drives: 3.1transfer Function For DC MotorДокумент12 страницUnit V Design of Controllers For Drives: 3.1transfer Function For DC Motormanoj kumarОценок пока нет

- Direct Memory Access: Direct Memory Access (DMA) Is A Process in Which An External Device TakesДокумент21 страницаDirect Memory Access: Direct Memory Access (DMA) Is A Process in Which An External Device TakesAkheel AhmedОценок пока нет

- Slides Week8 PDFДокумент46 страницSlides Week8 PDFvidhya dsОценок пока нет

- AirbagsДокумент353 страницыAirbagsvixentdОценок пока нет

- ICL7107 Ammeter Design - Circuits4youДокумент5 страницICL7107 Ammeter Design - Circuits4youHuang FerryОценок пока нет

- Wireless MIDI Interface: User Guide Version 2.0Документ11 страницWireless MIDI Interface: User Guide Version 2.0Rene VaughanОценок пока нет

- Datasheet IC 4017Документ8 страницDatasheet IC 4017Tri KusbiantoОценок пока нет

- Ultracapacitors DC-DC Converters in Regenerative Braking SystemДокумент6 страницUltracapacitors DC-DC Converters in Regenerative Braking SystemKaran AroraОценок пока нет

- Series RLC Circuit Voltage and Impedance AnalysisДокумент8 страницSeries RLC Circuit Voltage and Impedance AnalysisJeffrey JimenezОценок пока нет

- Active Crossover - PCR 2213 - v2.1Документ21 страницаActive Crossover - PCR 2213 - v2.1Евгений ЯвищенкоОценок пока нет

- Viper22A-E Viper22Adip-E, Viper22As-E: Low Power Off-Line Smps Primary SwitcherДокумент21 страницаViper22A-E Viper22Adip-E, Viper22As-E: Low Power Off-Line Smps Primary SwitcherAkash KumarОценок пока нет

- Qty. Description CRE 45-2-2 A-F-A-E-HQQE: Company Name: Created By: Phone: DateДокумент2 страницыQty. Description CRE 45-2-2 A-F-A-E-HQQE: Company Name: Created By: Phone: DateVitor AntunesОценок пока нет