Академический Документы

Профессиональный Документы

Культура Документы

ABB ICSTT-SDS-8110 - en Plantguard TMR Processor P8110

Загружено:

salic2013Исходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

ABB ICSTT-SDS-8110 - en Plantguard TMR Processor P8110

Загружено:

salic2013Авторское право:

Доступные форматы

ABB.

ICSTT-SDS-8110

3/$17*8$5' TMR Controller

3ODQWJXDUG TMR Processor-P8110

Dec 2002

FRONT PANEL

DESCRIPTION

3ODQWJXDUG TMR Processors

contain and execute the operating and

application software programs in a

triple redundant, fault tolerant

controller system..

The fault tolerant design contains

six fault containment regions. The

three synchronized processor fault

containment regions each contain a

600 series microprocessor, its

memory, voter, and associated

circuits.

The non-volatile memory is used

to store the configuration and

application programs for the system.

Each processor has an

independent power supply fed from

the dual-redundant 24Vdc power

supply of the 3ODQWJXDUG Controller

chassis backplane. The processor

power supplies provide short circuit

protection and regulated power to the

module electronics.

The processors operate

concurrently to achieve triple

modular redundancy and fault

tolerance. By providing 2-out-of-3

hardware voting on every inter-

processor exchange and memory data

retrieval, uncompromised fault

detection and error-free operation are

assured.

3ODQWJXDUG TMR Processors

communicate with other modules via

a backplane mounted, triplicated

Inter-Module Bus. Additionally,

interface modules are used to support

communication with I/O sub-systems

and other equipment.

Module faults are automatically

detected, time-stamped, and stored

for historical review. Transient

faults, once they are recorded, are

cleared automatically without

nuisance alarming. Permanent faults

in a processor are annunciated on the

front panel of the module, without

disturbing on-going processing in the

two remaining processors.

When a failed 3ODQWJXDUG TMR

Processor is replaced, the

replacement module is automatically

initialized without external loaders or

other equipment.

Application programs are developed

using the full suite of IEC 1131-3

languages. The user can load, run,

stop, single-step or delete the

application program. A front panel

maintenance enable keyswitch allows

the download of application

programs.

FEATURES

Triple modular redundant, Iault

tolerant 3-2-0 operation

Two-out-oI-three voting on

internal operations

Automatic Iault handling

without nuisance alarming

3ODQWJXDUG Operating System

kernel (IEC 61508 SIL3)

Time-stamped Iault historian

Module replacement without

program down-loading

Non-volatile memory Ior

program storage

Full suite oI IEC 1131-3

languages

Multiple process program

execution

TV certiIied Ior saIety, SIL3

ABB.ICSTT-SDS-8110

3/$17*8$5' TMR Controller

3ODQWJXDUG TRM Processor-P8110

ABB

Technical data sheets are intended for

information and guidance. ABB has a policy of

continual product development and

improvement. Specifications are subject to

change without notice.

BLOCK DIAGRAM

ELECTRICAL SPECIFICATION

Voltage Range 20 to 32V dc

Maximum Load 75W

Heat Dissipation 70W

Use With Chassis T8100

Processor Clock 50MHz

Memory Type And Size

DRAM

EPROM

FLASH

NVRAM

8MB/16MB/32MB/64MB EDO 60ns

512kB

2MB/4MB

128kB

I/O InterIace Triple redundant Inter-Module Bus

MECHANICAL

SPECIFICATION

Dimensions (HxWxD):

241mm x 90mm x 300mm

(9.5ins x 3.6ins x 11.8ins)

Weight:

2.71kg (5.95lbs)

ENVIROMENTAL

Operating Temperature:

-5C to 60C

(23F to 140F)

Operating Humidity:

5 to 95%, non-condensing

Vibration:

10 to 57Hz 0.075mm

57 to 150Hz 1.0g

Shock:

15g, sine wave, 11ms

EMI (IEC 801):

ESD

Air discharge to 15kV

Contact discharge to 8kV

Radiated Fields

10V/m, 27MHz to

500MHz

Transients and Bursts

2kV, 2.5kHz for

t=60 seconds

Вам также может понравиться

- 2949 HSE Risk Register - 2013-06-16 RevD1-VB FreeДокумент3 страницы2949 HSE Risk Register - 2013-06-16 RevD1-VB Freesalic201388% (8)

- Volkswagen RNS 510 Pin AssignmentsДокумент4 страницыVolkswagen RNS 510 Pin Assignmentssalic2013Оценок пока нет

- Flyer - PCS-9691E Overcurrent Relay PDFДокумент2 страницыFlyer - PCS-9691E Overcurrent Relay PDFscottsaw50% (2)

- Assessing The Sukhoi PAKДокумент46 страницAssessing The Sukhoi PAKsalic2013Оценок пока нет

- 05 4 ServomotorsДокумент118 страниц05 4 ServomotorsJosé Carlos Macavilca RománОценок пока нет

- Valeo Passenger Cars & LCV Security Systems 2012 2013 Catalogue 956216Документ40 страницValeo Passenger Cars & LCV Security Systems 2012 2013 Catalogue 956216salic2013Оценок пока нет

- 111-D-1005 Feed Surge Drum: NotesДокумент1 страница111-D-1005 Feed Surge Drum: Notessalic2013Оценок пока нет

- ESD System OperationДокумент53 страницыESD System Operationsalic2013100% (1)

- Saes Z 003Документ10 страницSaes Z 003salic2013Оценок пока нет

- Volkswagen RCD 510 Pin AssignmentsДокумент4 страницыVolkswagen RCD 510 Pin Assignmentssalic2013100% (1)

- PMP50 Using This ManualДокумент5 страницPMP50 Using This Manualsalic2013Оценок пока нет

- Active Disturbance Rejection Control for Nonlinear Systems: An IntroductionОт EverandActive Disturbance Rejection Control for Nonlinear Systems: An IntroductionОценок пока нет

- TutorialsДокумент17 страницTutorialsnandini chinthalaОценок пока нет

- Chapter 1: Introduction To HCS12/MC9S12 The HCS12 Microcontroller Han-Way Huang Minnesota State University, Mankato September 2009Документ31 страницаChapter 1: Introduction To HCS12/MC9S12 The HCS12 Microcontroller Han-Way Huang Minnesota State University, Mankato September 2009Omar LopezОценок пока нет

- Pir Sensor Based Energy SaverДокумент76 страницPir Sensor Based Energy Saverk.aparna100% (1)

- Anti Theft System For Valuable Items Using LDRДокумент6 страницAnti Theft System For Valuable Items Using LDRKethavath Sakrunaik KОценок пока нет

- Course Title Microprocessor SystemДокумент20 страницCourse Title Microprocessor SystemElmustafa Sayed Ali AhmedОценок пока нет

- 0506 PCX-2 V0106 enДокумент127 страниц0506 PCX-2 V0106 enspale82Оценок пока нет

- VCD-D ManualДокумент13 страницVCD-D ManualnimmuhkОценок пока нет

- Mcs 014 Systeem Design PDFДокумент10 страницMcs 014 Systeem Design PDFMuthukrishnan NОценок пока нет

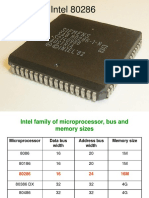

- Intel 80286Документ24 страницыIntel 80286Rajesh PatelОценок пока нет

- Lab 1 - OLED, GPIO, InterruptДокумент6 страницLab 1 - OLED, GPIO, Interruptprakash_shrОценок пока нет

- Analysis of A High-Potential Business: Sqreen: Application Security Management PlatformДокумент13 страницAnalysis of A High-Potential Business: Sqreen: Application Security Management Platformhinaya khanОценок пока нет

- 1769-If4I Analog Input ModuleДокумент24 страницы1769-If4I Analog Input ModuleHilder Ramirez PuellesОценок пока нет

- Lecture 6Документ10 страницLecture 6Elmustafa Sayed Ali AhmedОценок пока нет

- Two-Wire Peripheral Expansion For The AT89C2051 MicrocontrollerДокумент9 страницTwo-Wire Peripheral Expansion For The AT89C2051 MicrocontrollerVlaovic GoranОценок пока нет

- 80286Документ28 страниц80286Kavitha SubramaniamОценок пока нет

- Manual SMC Dialog Plus Controller. Allen BradleyДокумент189 страницManual SMC Dialog Plus Controller. Allen BradleygreenlinexОценок пока нет

- Masibus 8208 ManualДокумент36 страницMasibus 8208 ManualCraig Godfrey100% (1)

- GT30 ManualДокумент83 страницыGT30 ManualJerry ReddenОценок пока нет

- 65 KVA Perkins Diesel Generator Set - Non EPA - 50Hz TP-P65-T1-50Документ5 страниц65 KVA Perkins Diesel Generator Set - Non EPA - 50Hz TP-P65-T1-50AbdaljaleelAlqazeeОценок пока нет

- P211 en M A31Документ64 страницыP211 en M A31Koustav DasguptaОценок пока нет

- Max DemandДокумент11 страницMax DemanddwarakeshОценок пока нет

- EMBEDDED BASED Automatic AUDITORIUM CONTROLLER 0TH REVДокумент36 страницEMBEDDED BASED Automatic AUDITORIUM CONTROLLER 0TH REVspringsource100% (1)

- Romana T-3805-EДокумент19 страницRomana T-3805-EjorgeОценок пока нет

- 80286Документ74 страницы80286Arannya MonzurОценок пока нет

- Basic ComputerДокумент22 страницыBasic ComputerKashyap Sompura100% (1)

- Intel 80286 Programmer ModelДокумент276 страницIntel 80286 Programmer ModelsreepadaravikumarОценок пока нет

- #Ped Lab 03Документ24 страницы#Ped Lab 03akilaОценок пока нет

- ES Series Hardware Manual170413Документ64 страницыES Series Hardware Manual170413Oscar MontañezОценок пока нет

- 8085 Microproceesor - PPTДокумент59 страниц8085 Microproceesor - PPTShanagonda Manoj KumarОценок пока нет

- EPM Manual Model 42iДокумент347 страницEPM Manual Model 42ichaling3Оценок пока нет

- Mge Upsilon Sts - BrochureДокумент4 страницыMge Upsilon Sts - BrochureMetalloyОценок пока нет

- Renesas Flash Programmer Sample Circuit For Programming PC Serial PDFДокумент5 страницRenesas Flash Programmer Sample Circuit For Programming PC Serial PDFAjay J VermaОценок пока нет

- R01an0239ej sh7125Документ35 страницR01an0239ej sh7125ArmanОценок пока нет

- DsPIC30F4011 - Robotics 3Документ33 страницыDsPIC30F4011 - Robotics 3Senthil Kumar100% (1)

- Debugger Hc12Документ52 страницыDebugger Hc12carver_uaОценок пока нет

- 9619 Philips 32PFL3605 42PFL3605 Chassis RAM1 0A LA Televisor LCD Manual de Servicio PDFДокумент66 страниц9619 Philips 32PFL3605 42PFL3605 Chassis RAM1 0A LA Televisor LCD Manual de Servicio PDFMaya Tes100% (1)

- D2-250-1 Key Features: DL250-1 CPUДокумент3 страницыD2-250-1 Key Features: DL250-1 CPUVladimir Aliro Quezada CidОценок пока нет

- The VLSI Ruby II Advanced Communication ProcessorДокумент1 страницаThe VLSI Ruby II Advanced Communication ProcessorvlkumashankardeekshithОценок пока нет

- LPKF ProtoMat S103Документ2 страницыLPKF ProtoMat S103jhonny639Оценок пока нет

- Auto ShiftДокумент56 страницAuto Shiftshaikintiyazsultana0% (1)

- 84.vehicle Superintending System With Voice Feedback DocuДокумент88 страниц84.vehicle Superintending System With Voice Feedback DocuMoluguri KirankumarОценок пока нет

- RC5 Protocol Decoding With 8051 Microcontroller (Embedded C) - ProEmbSys TechnologiesДокумент4 страницыRC5 Protocol Decoding With 8051 Microcontroller (Embedded C) - ProEmbSys TechnologieskhhoaОценок пока нет

- Micro Controller and Embedded Systems (Revised)Документ2 страницыMicro Controller and Embedded Systems (Revised)Ashok ShahОценок пока нет

- C40 Trace Manual EnglishДокумент24 страницыC40 Trace Manual EnglishBertОценок пока нет

- General Gps Vehicle Tracker Wetrack2 User ManualДокумент20 страницGeneral Gps Vehicle Tracker Wetrack2 User ManualDanang Irawan0% (1)

- Ec2304 LP III EceДокумент5 страницEc2304 LP III EcesunvenkatОценок пока нет

- k120s K7MDR14UE ManualДокумент11 страницk120s K7MDR14UE ManualAhmed Hebeshe100% (1)

- 23 Rapiscan Mvxr5000 CBTДокумент2 страницы23 Rapiscan Mvxr5000 CBTAnonymous abOKZAaОценок пока нет

- 78K0-KB2 Sample ProgramДокумент58 страниц78K0-KB2 Sample ProgramAnonymous pu1L9ZОценок пока нет

- Multiple Transformers Oil Temperature Monitoring With Automatic CircuitДокумент25 страницMultiple Transformers Oil Temperature Monitoring With Automatic CircuitPrem Narayan Singh100% (1)

- 99.automatic Auditorium ControllingДокумент3 страницы99.automatic Auditorium ControllingDinesh DspОценок пока нет

- Seminar ReportДокумент26 страницSeminar Reportharishk03Оценок пока нет

- ABB ICSTT-SDS-8151 - en Plantguard Communications Interface P8151Документ2 страницыABB ICSTT-SDS-8151 - en Plantguard Communications Interface P8151salic2013Оценок пока нет

- Td02600004e Emr-4000Документ20 страницTd02600004e Emr-4000CristhJuliang100% (1)

- Efm32G890 Datasheet: EFM32G890 Microcontrollers Are Suited For All Battery Operated ApplicationsДокумент71 страницаEfm32G890 Datasheet: EFM32G890 Microcontrollers Are Suited For All Battery Operated ApplicationsamerosperosОценок пока нет

- ATxmega 128 A3 UДокумент141 страницаATxmega 128 A3 UsanapashokОценок пока нет

- 3bnp004720r101.PDF - en Triguard 2 TMR Safety ProductsДокумент20 страниц3bnp004720r101.PDF - en Triguard 2 TMR Safety ProductsluispedrojrОценок пока нет

- ABB ICSTT-SDS-8100 - en Plantguard Controller Chassis P8100Документ2 страницыABB ICSTT-SDS-8100 - en Plantguard Controller Chassis P8100salic2013Оценок пока нет

- PCS 7 APACS OS Symbols and Faceplates V6.1Документ66 страницPCS 7 APACS OS Symbols and Faceplates V6.1salic2013Оценок пока нет

- Connection: 4xwire +12V GND CAN High Can Low Gateway TPMS ControllerДокумент2 страницыConnection: 4xwire +12V GND CAN High Can Low Gateway TPMS Controllersalic2013Оценок пока нет

- CAP Short PresentationДокумент12 страницCAP Short Presentationsalic2013Оценок пока нет

- Ieh - Chapter 6-9 - Partial-Stroke Testing of Block ValvesДокумент24 страницыIeh - Chapter 6-9 - Partial-Stroke Testing of Block ValvesKareem RasmyОценок пока нет

- HV Induction Motors Technical IEC Catalog FINAL en 092011 LowresДокумент152 страницыHV Induction Motors Technical IEC Catalog FINAL en 092011 LowresSangeet BhandariОценок пока нет

- INSTRUCALCДокумент1 страницаINSTRUCALCsalic2013Оценок пока нет

- Proforma Invoice: 1) Time of Delivery: 30 Days After Receiving Your Payment 2) Packing: Standard Export CartonДокумент1 страницаProforma Invoice: 1) Time of Delivery: 30 Days After Receiving Your Payment 2) Packing: Standard Export Cartonsalic2013Оценок пока нет

- 10 Things Deploying Desktops From ImagesДокумент4 страницы10 Things Deploying Desktops From Imagessalic2013100% (1)

- Baggage X RayДокумент4 страницыBaggage X RayShaaban HassanОценок пока нет

- Saxby KatalogДокумент163 страницыSaxby KatalogjaОценок пока нет

- SynchronizationДокумент114 страницSynchronizationSudha PatelОценок пока нет

- Pioneer PLX 500kДокумент15 страницPioneer PLX 500kFabiОценок пока нет

- Technical Specification: ConfigurationДокумент7 страницTechnical Specification: ConfigurationAhmedRamadanОценок пока нет

- GCC 5241PДокумент16 страницGCC 5241Pboating1997Оценок пока нет

- InstallДокумент6 страницInstallDebangshu KumarОценок пока нет

- Define Field SelectionДокумент3 страницыDefine Field SelectionSenthil NayagamОценок пока нет

- GIS SPDSS FinalДокумент11 страницGIS SPDSS FinalsrverngpОценок пока нет

- Rate Monotonic Scheduling: Group - 12Документ19 страницRate Monotonic Scheduling: Group - 12Brajmohan kr SinghОценок пока нет

- Mobile Phones Read The Following Text:: Source: Newsweek, May 1999Документ3 страницыMobile Phones Read The Following Text:: Source: Newsweek, May 1999Stiven Giraldo VillegasОценок пока нет

- Multicast Routing Protocols in Wireless Sensor Networks (WSNS)Документ9 страницMulticast Routing Protocols in Wireless Sensor Networks (WSNS)Journal of Computing100% (1)

- Printed in FranceДокумент4 страницыPrinted in FranceYusron AzharyОценок пока нет

- Brilla SpaДокумент16 страницBrilla SpaRaman SainiОценок пока нет

- PI Calliope SQN3223 3 20160205 Web PDFДокумент2 страницыPI Calliope SQN3223 3 20160205 Web PDFrqueirosОценок пока нет

- 1250Документ1 страница1250Mijin28Оценок пока нет

- HE - FOS - GR7-9 - Q1 - MODULE-2 For TeacherДокумент27 страницHE - FOS - GR7-9 - Q1 - MODULE-2 For TeacherVicente VicenteОценок пока нет

- Denon Avr-1613 Owners ManualДокумент131 страницаDenon Avr-1613 Owners ManuallerondotОценок пока нет

- 92.railway Track Pedestrain Crossing Without Using StaircaseДокумент3 страницы92.railway Track Pedestrain Crossing Without Using StaircaseMaragoni MukeshОценок пока нет

- 05a1 E70 Central Locking PDFДокумент19 страниц05a1 E70 Central Locking PDFMozes SimataaОценок пока нет

- AOC LCD MonitorДокумент60 страницAOC LCD MonitorRoger Martínez BermúdezОценок пока нет

- Book IELTS Test Online Booking WizardДокумент4 страницыBook IELTS Test Online Booking WizardNilza BackesОценок пока нет

- Bartender BrochureДокумент13 страницBartender Brochuren_santhoshuОценок пока нет

- Optima User GuideДокумент158 страницOptima User GuideVikasОценок пока нет

- Biomedical 7-8Документ20 страницBiomedical 7-8முத்துலிங்கம். பால்ராஜ்Оценок пока нет

- Programming NortelДокумент11 страницProgramming NortelNeelakanteswar AslapuramОценок пока нет

- ITC-3 Technical Description - 2020 PDFДокумент24 страницыITC-3 Technical Description - 2020 PDFAndres Mtz CotaОценок пока нет

- Final Mangonel Group ProjectДокумент7 страницFinal Mangonel Group ProjectAarohan Verma100% (2)

- 6WG1 TanıtımДокумент17 страниц6WG1 TanıtımHalil KaraОценок пока нет