Академический Документы

Профессиональный Документы

Культура Документы

Do Practice CO

Загружено:

Sudeep SharmaАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Do Practice CO

Загружено:

Sudeep SharmaАвторское право:

Доступные форматы

i. The common bus architecture system for 30 processor registers.

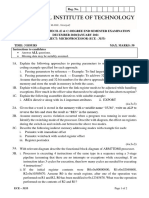

How many selection lines are required for each multiplexer for the destination decoder. (1) ii. How subroutine call is different from branching? iii. Define the term selective set with example. iv. What are the four basic types of operations that need to be supported by an instruction set? v. The memory unit of a computer has 256 K words of 32 bits each. The computer has an instruction format with four fields: an operation code field, a mode field to specify one of seven addressing modes, a memory address. Specify the instruction format and the number of bits in each field if the instruction is in one memory word. vi. Why is transfer of control instructions needed? vii. Name and explain the types of control organizations? viii. Discuss the race round condition in J-K flip flop. ix. What is the benefit of using multiple bus architecture compared to single bus architecture? x. Explain the steps of an instruction cycle.

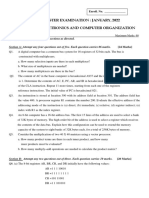

Q1. a) Draw the logic diagram of a full subtractor using hallf subtractor and required gates. b) Show the block diagram that executes the statement xT3 : A B, B A c) Draw the logic diagram of a bit encoder circuit with four input lines, exactly one of which is high at any instant and two output lines whose 2-bit binary value tells which input is high. d) It is stated that both an arithmetic left shift and a logical left shift corresponds to a multiplication by 2 when there is no overflow, and if overflow occurs, arithmetic and logical left shift operations produce different results, but the arithmetic left shift retains the sign of the number. Demonstrate that these statements are true/false for 5-bit twos complement integers. Q2. a) Show how a shift register with parallel load can be used to convert serial input to parallel output and parallel output and parallel input to serial output b) Draw a timing diagram assuming that SC is cleared to 0 at time T3 if control signal C7 is active C7T3 SC 0 C7 is activated with the positive clock transition associated with T1. c) Design an arithmetic circuit with one selection variable S and two n-bit data inputs A and B the circuit generates the following four arithmetic operations in conjunction with the input carry Cin . Draw the logic diagram for the first two stages. S Cin=0 Cin=1 1 D=A-1 D=A+B+1 0 D=A+B D=A+1 Q3.a) A digital system has 16 registers, each with 32 bits it is necessary to provide parallel data transfer from each register to every other register. i) How many lines are needed for transfer along 4 common bus? ii) How many lines are needed for direct parallel transfer?

iii) List the sequence of micro operations for a transfer of contents R6 to R13. b) Consider a hypothetical microprocessor generating 64 bit instructions composed of two fields: first two bytes contain opcode and remainder the immediate operand or an operand address a. What is the maximum directly addressable memory capacity (in bytes)? b. Discuss the impact on the system speed if the microprocessor bus has i. A 64 bit local address bus and a 32 bit local data bus or ii. A 32 bit local address bus and a 32 bit local data bus c. How many bits are needed for the program counter and the instruction register? Q4. a) Consider a computer system that contains an I/O module controlling as simple keyboard/printer teletype. The following registers are contained in the processor and connected directly to the system bus: INPR : Input Register, 8 bits OUTR : Output Register, 8 bits FGI : Input Flag, 1 bit FGO : Output Flags, 1 bit IEN : Interrupt Enable, 1 bit Keystroke input from the teletype and printer output to the teletype are controlled by the I/O module. The teletype is able to encode an alphanumeric symbol to an 8-bit word and decode an 8-bit word into an alphanumeric symbol. a) Describe how the processor, using the first four register listed in this problem can achieve I/O with the teletype. b) Describe how the function can be performed more efficiently by also employing IEN b) Consider a hypothetical computer with an instruction set of only two n-bit instructions. The first bit specifies the opcode, and the remaining bits specify one of the 2n-1 n-bit words of main memory. The two instructions are follows: SUBS X Subtract the contents of location X from the accumulator and store the result in location x and the accumulator JUMPX Place address X in the program counter A word in main memory may contain either an instruction or a binary number in twos complement notation. Demonstrate that this instruction repertoire is reasonably complete by specifying how operations can be programmed. a. Data transfer: Location X to accumulator, accumulator to location X b. addition: add content of location X to accumulator c. Conditional branch d. Logical OR e. I/O operations

Вам также может понравиться

- E6995ca TutДокумент14 страницE6995ca Tutrabinoss0% (1)

- Shivalik College of Engineering Question Bank Computer Organization B.Tech II Year (IV Semester)Документ5 страницShivalik College of Engineering Question Bank Computer Organization B.Tech II Year (IV Semester)Paras TilaraОценок пока нет

- COA Assignment: This Assignment Consists of 10 Questions. Each Question Is of 5 MarksДокумент3 страницыCOA Assignment: This Assignment Consists of 10 Questions. Each Question Is of 5 Marksprakhar agrawalОценок пока нет

- Computer Organization and Architecture (01CE0402) Lab ManualДокумент4 страницыComputer Organization and Architecture (01CE0402) Lab ManualrockyОценок пока нет

- 2629acomputer ArchitectureДокумент15 страниц2629acomputer ArchitectureSiddhant Jain SethОценок пока нет

- Co QBДокумент6 страницCo QBHarris ChikunyaОценок пока нет

- BSC (H) CSHT II 204 Mid2012 Ddu Assignment IДокумент2 страницыBSC (H) CSHT II 204 Mid2012 Ddu Assignment IRavi RanjanОценок пока нет

- COA Assignment - 3Документ2 страницыCOA Assignment - 3KomalОценок пока нет

- Computer Applications and ManagementДокумент11 страницComputer Applications and ManagementParag PaliwalОценок пока нет

- CA Assignment IIДокумент9 страницCA Assignment IISomesh ThakurОценок пока нет

- COA QuestionBank - 1Документ3 страницыCOA QuestionBank - 1itzzsandeshОценок пока нет

- QbankДокумент3 страницыQbankAnanthi RajkumarОценок пока нет

- Final Exam of COAДокумент3 страницыFinal Exam of COATigabu Yaya100% (1)

- Computer Organization - List of Assignments.Документ7 страницComputer Organization - List of Assignments.arnab_bhattacharj_26Оценок пока нет

- Question Bank For DecoДокумент2 страницыQuestion Bank For Decotheamg7272Оценок пока нет

- COA WorksheetДокумент1 страницаCOA WorksheetAngesom DestaОценок пока нет

- Microprocessor (ECE-3153)Документ2 страницыMicroprocessor (ECE-3153)RAHUL RTRОценок пока нет

- Caassgnsem 1Документ12 страницCaassgnsem 1Sunil GawaskerОценок пока нет

- DDCO UPDATED QUESTION BANKttttДокумент4 страницыDDCO UPDATED QUESTION BANKttttbrahmareddy.22iseОценок пока нет

- Unit - IДокумент2 страницыUnit - IPranathi NimmuОценок пока нет

- Computer Architecture and Organization Assignment IIДокумент2 страницыComputer Architecture and Organization Assignment IIDEMEKE BEYENEОценок пока нет

- Solution To Assignments For BScCSIT 3rd Semester (2069)Документ8 страницSolution To Assignments For BScCSIT 3rd Semester (2069)Bijay MishraОценок пока нет

- (WWW - Entrance-Exam - Net) - PTU MCA 3rd Semester Sample Paper 4Документ2 страницы(WWW - Entrance-Exam - Net) - PTU MCA 3rd Semester Sample Paper 4Mangesh MalvankarОценок пока нет

- CAO 2021 Assignment QuestionДокумент9 страницCAO 2021 Assignment Questiondawit tadewoseОценок пока нет

- Computer Organization Unit 4 AssignmentДокумент4 страницыComputer Organization Unit 4 Assignmentsaiteja1234Оценок пока нет

- End Semester Examination: January, 2022 Digital Electronics and Computer OrganizationДокумент3 страницыEnd Semester Examination: January, 2022 Digital Electronics and Computer OrganizationFFFОценок пока нет

- Network Basics CollectionДокумент11 страницNetwork Basics Collectionrocks66aryanОценок пока нет

- DSP Unit 1 To 5 QBДокумент12 страницDSP Unit 1 To 5 QBSamuel WhiteОценок пока нет

- Te Oct 2014Документ149 страницTe Oct 2014contrasterОценок пока нет

- In Computers, Subtraction Is Generally Carried Out byДокумент2 страницыIn Computers, Subtraction Is Generally Carried Out byatul211988Оценок пока нет

- Module 2 - Collaborative LearningДокумент3 страницыModule 2 - Collaborative LearningSuzanne GeorgeОценок пока нет

- Computer Organisation and ArchitectureДокумент2 страницыComputer Organisation and ArchitectureSelin DandpatОценок пока нет

- CSC 204 - Final Study GuideДокумент12 страницCSC 204 - Final Study GuideFVCproductionsОценок пока нет

- 8051 MCQДокумент25 страниц8051 MCQRohan Bachhav100% (1)

- MCS-012 - Computer Organisation and AssemblyДокумент4 страницыMCS-012 - Computer Organisation and AssemblyLataPuthranОценок пока нет

- 134ak - Computer OrganizationДокумент2 страницы134ak - Computer Organizationsameeksha chiguruОценок пока нет

- MCS 012Документ4 страницыMCS 012rajatkumar.codingОценок пока нет

- Question Bank - M5 To M7Документ2 страницыQuestion Bank - M5 To M7Pieter MarkerОценок пока нет

- Digital Principles and System DesignДокумент76 страницDigital Principles and System Designraja rОценок пока нет

- Question BankДокумент4 страницыQuestion BankChetan GowdaОценок пока нет

- Question Bank of Unit-III COAДокумент4 страницыQuestion Bank of Unit-III COAYamini BishtОценок пока нет

- Unit 1: MPI (CST-282, ITT-282) SUBMISSION DATE: 14.02.2020Документ9 страницUnit 1: MPI (CST-282, ITT-282) SUBMISSION DATE: 14.02.2020Shruti SinghОценок пока нет

- ContdДокумент2 страницыContdchandra sekharОценок пока нет

- Microprocessor and Architecture Solution PDFДокумент23 страницыMicroprocessor and Architecture Solution PDFKarmaveer Bhaurao Patil CollegeОценок пока нет

- CA-Assignment 2 - FinalДокумент2 страницыCA-Assignment 2 - Finaljixxy jaxОценок пока нет

- Assignment COA ETCS-204Документ3 страницыAssignment COA ETCS-204YuvrajОценок пока нет

- Assignment 1Документ1 страницаAssignment 1PULKIT KUMAR 21SCSE1420057Оценок пока нет

- DLDM Question BankДокумент8 страницDLDM Question BankMayur PatilОценок пока нет

- Assignment 1 CSAДокумент4 страницыAssignment 1 CSAPrashant RawatОценок пока нет

- Assignments CSE211Документ4 страницыAssignments CSE211Raghav JhanjeeОценок пока нет

- Assignments For BScCSIT 3rd Semester (2069)Документ2 страницыAssignments For BScCSIT 3rd Semester (2069)jijibishamishraОценок пока нет

- Cs6201-Digital Principles and System DesignДокумент6 страницCs6201-Digital Principles and System DesignAnonymous L4iu94ZIlwОценок пока нет

- Coa Imp Questions - 32543434 - 2024 - 03 - 19 - 23 - 14Документ6 страницCoa Imp Questions - 32543434 - 2024 - 03 - 19 - 23 - 14cofasi3281Оценок пока нет

- Individual Assignment QuestionsДокумент3 страницыIndividual Assignment QuestionsGemechisОценок пока нет

- Computer Organization Jun 2010Документ2 страницыComputer Organization Jun 2010Prasad C MОценок пока нет

- 21CS34 SIMP Questions - 21SCHEME: Module-1 (Study Any 5 Questions)Документ4 страницы21CS34 SIMP Questions - 21SCHEME: Module-1 (Study Any 5 Questions)Rohan RОценок пока нет

- Rr310401-Digital Ic ApplicationsДокумент2 страницыRr310401-Digital Ic ApplicationsSRINIVASA RAO GANTAОценок пока нет

- Department of Eee: Special Course Exam Iot Based AutomationДокумент6 страницDepartment of Eee: Special Course Exam Iot Based AutomationsathyatnОценок пока нет

- Software Testing Mini Project ReportДокумент61 страницаSoftware Testing Mini Project ReportSudeep SharmaОценок пока нет

- New SS - OS Lab ManualДокумент31 страницаNew SS - OS Lab ManualSudeep SharmaОценок пока нет

- AnswersДокумент3 страницыAnswersSudeep SharmaОценок пока нет

- Institute of Computer Applications & Management: Bharati Vidyapeeth'SДокумент3 страницыInstitute of Computer Applications & Management: Bharati Vidyapeeth'SSudeep SharmaОценок пока нет

- DBMS Lab Manual PDFДокумент40 страницDBMS Lab Manual PDFKarthikeyan Ramajayam80% (10)

- Fourth Sem Solved Lab ManualДокумент48 страницFourth Sem Solved Lab ManualSudeep SharmaОценок пока нет

- Assignment 2 0Документ2 страницыAssignment 2 0Sudeep SharmaОценок пока нет

- DBMSLabManual SureshДокумент34 страницыDBMSLabManual SureshSudeep SharmaОценок пока нет

- Data MiningДокумент4 страницыData MiningSudeep SharmaОценок пока нет

- DBMSLabManual SureshДокумент34 страницыDBMSLabManual SureshSudeep SharmaОценок пока нет

- Dbms Lab ManualДокумент95 страницDbms Lab ManualSudeep SharmaОценок пока нет

- Rdbms Lab Manual New SchemeДокумент24 страницыRdbms Lab Manual New SchemeSudeep SharmaОценок пока нет

- Indow TO Iewport Ransformation: Presented By: Mohammed Hisham 042Документ11 страницIndow TO Iewport Ransformation: Presented By: Mohammed Hisham 042Sudeep SharmaОценок пока нет

- All Pairs Shortest Path: Presented By: Sudeep SharmaДокумент13 страницAll Pairs Shortest Path: Presented By: Sudeep SharmaSudeep SharmaОценок пока нет

- Fresher Test - 23 July 2011 (Offcampus-1)Документ4 страницыFresher Test - 23 July 2011 (Offcampus-1)Sudeep SharmaОценок пока нет

- DWDMДокумент2 страницыDWDMSudeep SharmaОценок пока нет

- Chapter 06Документ19 страницChapter 06Sudeep SharmaОценок пока нет

- Curve Modelling-B SplineДокумент60 страницCurve Modelling-B SplineSudeep SharmaОценок пока нет

- Computer Graphics: Curves and Surfaces IIДокумент33 страницыComputer Graphics: Curves and Surfaces IISudeep SharmaОценок пока нет

- Internal 1 2011 14 - 0Документ2 страницыInternal 1 2011 14 - 0Sudeep SharmaОценок пока нет

- Javaindex 1Документ7 страницJavaindex 1Sudeep Sharma100% (2)

- ASPДокумент13 страницASPkitchaaОценок пока нет

- Important Questions!!Документ21 страницаImportant Questions!!Sudeep SharmaОценок пока нет

- LINQДокумент82 страницыLINQSudeep SharmaОценок пока нет

- Abstract V InterfaceДокумент1 страницаAbstract V Interfacechetanraj07Оценок пока нет

- javaINDEX 2Документ1 страницаjavaINDEX 2Sudeep SharmaОценок пока нет

- "Sun" "Mon" "Tues" "Wed" "Thurs" "Fri" "Sat": //indexer Example Class StringДокумент2 страницы"Sun" "Mon" "Tues" "Wed" "Thurs" "Fri" "Sat": //indexer Example Class StringSudeep SharmaОценок пока нет

- Csharp Interview Questions PDFДокумент9 страницCsharp Interview Questions PDFsugupremОценок пока нет

- Bouncing BallДокумент8 страницBouncing BallSudeep SharmaОценок пока нет

- A JDBC TutorialДокумент8 страницA JDBC TutorialSudeep SharmaОценок пока нет

- Introduction To Computer OrganizationДокумент207 страницIntroduction To Computer Organizationhemanth ramireddyОценок пока нет

- Exam2 ReviewДокумент54 страницыExam2 ReviewSurbhie Kalia ChebaОценок пока нет

- Shift and Rotate Instructions: GroupДокумент20 страницShift and Rotate Instructions: GroupOsama Mk ShakarjiОценок пока нет

- Cse 211 NotesДокумент41 страницаCse 211 NotesVamsi Krishna100% (1)

- Shift Micro OperationsДокумент14 страницShift Micro Operationsanand_gsoft3603Оценок пока нет

- Register Transfer and MicrooperationsДокумент45 страницRegister Transfer and MicrooperationsSalma SaleemОценок пока нет

- Register Transfer and MicrooperationsДокумент58 страницRegister Transfer and Microoperationsnskprasad89Оценок пока нет

- Logic Microoperations - NotesДокумент22 страницыLogic Microoperations - NotesRitesh KumarОценок пока нет

- CSI - 03b - OperationsДокумент36 страницCSI - 03b - OperationsKhanh HungОценок пока нет

- Register Transfer & - OperationsДокумент45 страницRegister Transfer & - Operationshassan halaikaОценок пока нет

- Veilog HDL Module 3Документ62 страницыVeilog HDL Module 3Mallik KglОценок пока нет

- Lec11 Register Transfer and Micro Operations Part2Документ22 страницыLec11 Register Transfer and Micro Operations Part2Diptee KalolaОценок пока нет

- Lecture 4 - Chapter 4 - REGISTER TRANSFER AND MICROOPERATIONSДокумент11 страницLecture 4 - Chapter 4 - REGISTER TRANSFER AND MICROOPERATIONSsaifsunnyОценок пока нет

- Mpal 8Документ48 страницMpal 8ifrah shujaОценок пока нет

- Shift and RotateДокумент27 страницShift and RotateAdrian RamosОценок пока нет

- Register Transfer Language Register Transfer Bus and Memory Transfers Arithmetic Micro-Operations Logic Micro-Operations Shift Micro-Operations Arithmetic Logic Shift UnitДокумент16 страницRegister Transfer Language Register Transfer Bus and Memory Transfers Arithmetic Micro-Operations Logic Micro-Operations Shift Micro-Operations Arithmetic Logic Shift UnitYash Gupta MauryaОценок пока нет

- Do Practice COДокумент2 страницыDo Practice COSudeep SharmaОценок пока нет

- Register Transfer and MicrooperationsДокумент35 страницRegister Transfer and MicrooperationsPerfectamente EstupendoОценок пока нет

- Register Transfer and Micro OperationsДокумент49 страницRegister Transfer and Micro OperationsabhishekОценок пока нет

- CSEN 402: Computer Org. & Sys. Programming: Slides Prepared By: Dr. Ihab Amer Lecturer: Dr. Cherif SalamaДокумент17 страницCSEN 402: Computer Org. & Sys. Programming: Slides Prepared By: Dr. Ihab Amer Lecturer: Dr. Cherif SalamaMichael HannaОценок пока нет

- Activity No 6Документ6 страницActivity No 6Anonymous RO0RYTAIZpОценок пока нет

- Shift Micro-OperationsДокумент8 страницShift Micro-Operationsoureducation.in100% (4)

- Lab 09Документ7 страницLab 0915obaid.rehman20041Оценок пока нет

- Instruction Set 21Документ200 страницInstruction Set 21Raj shahОценок пока нет

- Co Unit 2.1Документ45 страницCo Unit 2.1Prasanth ReddyОценок пока нет

- Lecture 6Документ37 страницLecture 6Ritesh KumarОценок пока нет

- Register Transfer and MicrooperationsДокумент47 страницRegister Transfer and MicrooperationsDhruv PanditОценок пока нет

- Activity No 6 Bit ManipulationДокумент6 страницActivity No 6 Bit ManipulationMark Daniel RuizОценок пока нет

- ALU and MAC NotesДокумент36 страницALU and MAC NotesMajerry Pierre-AntoineОценок пока нет

- Bitwise OperationДокумент8 страницBitwise Operationsmith_5Оценок пока нет