Академический Документы

Профессиональный Документы

Культура Документы

Architecture of 8086 Microcontroller

Загружено:

Shubhan SinghОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Architecture of 8086 Microcontroller

Загружено:

Shubhan SinghАвторское право:

Доступные форматы

Architecture of 8086 Unlike microcontrollers, microprocessors do not have inbuilt memory.

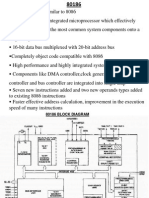

Mostly Princeton architecture is used for microprocessors where data and program memory are combined in a single memory interface. Since a microprocessor does not have any inbuilt peripheral, the circuit is purely digital and the clock speed can be anywhere from a few MHZ to a few hundred MHZ or even GHZ. This increased clock speed facilitates intensive computation that a microprocessor is supposed to do. We will discuss the basic architecture of Intel 8086 before discussing more advanced microprocessor architectures. Internal architecture of Intel 8086: Intel 8086 is a 16 bit integer processor. It has 16-bit data bus and 20-bit address bus. The lower 16-bit address lines and 16-bit data lines are multiplexed (AD0-AD15). Since 20-bit address lines are available, 8086 can access up to 2 20 or 1 Mega byte of physical memory. The basic architecture of 8086 is shown below.

Fig 29.1 Basic Architecture of 8086 Microprocessor The internal architecture of Intel 8086 is divided into two units, viz., Bus Interface Unit (BIU) and Execution Unit (EU). Bus Interface Unit (BIU ) The Bus Interface Unit (BIU) generates the 20-bit physical memory address and provides the interface with external memory (ROM/RAM). As mentioned earlier, 8086 has a single memory interface. To speed up the execution, 6-bytes of instruction are fetched in advance and kept in a 6-byte Instruction Queue while other instructions are being executed in the Execution Unit (EU). Hence after the execution of an instruction, the next instruction is directly fetched from the instruction queue without having to wait for the external memory to send the instruction. This is called pipe-

lining and is helpful for speeding up the overall execution process. 8086's BIU produces the 20-bit physical memory address by combining a 16-bit segment address with a 16-bit offset address. There are four 16-bit segment registers, viz., the code segment (CS), the stack segment (SS), the extra segment (ES), and the data segment (DS). These segment registers hold the corresponding 16bit segment addresses. A segment address is the upper 16-bits of the starting address of that segment. The lower 4-bits of the starting address of a segment is always zero. The offset address is held by another 16-bit register. The physical 20-bit address is calculated by shifting the segment address 4-bit left and then adding that to the offset address. For Example: Code segment Register CS holds the segment address which is 4569 H Instruction pointer IP holds the offset address which is 10A0 H The physical 20-bit address is calculated as follows. Segment address : 45690 H Offset address :+ 10A0 H Physical address : 46730 H

Вам также может понравиться

- Internal Architecture 8086Документ3 страницыInternal Architecture 8086firoz83% (6)

- Manoj Gupta 26301620016 Microprocessor & MicrocontrollerДокумент12 страницManoj Gupta 26301620016 Microprocessor & MicrocontrollerAbhijit Misra AbhiОценок пока нет

- I Am Intel 8086Документ8 страницI Am Intel 8086AB ESPORTSОценок пока нет

- 8086Документ8 страниц8086MOHAMMED ASLAM CОценок пока нет

- Memory Segmentation in 8086 Microprocessor ExplainedДокумент7 страницMemory Segmentation in 8086 Microprocessor Explainedshahid aliОценок пока нет

- 8086 MicroprocessorДокумент48 страниц8086 MicroprocessorBlackk SpydoОценок пока нет

- Unit-I (Architecture of 8086)Документ23 страницыUnit-I (Architecture of 8086)Gouse MaahiОценок пока нет

- Architecture of 8086Документ4 страницыArchitecture of 8086sree ramyaОценок пока нет

- 8086 Microprocessor Cheatsheet GuideДокумент17 страниц8086 Microprocessor Cheatsheet Guidedz15dzОценок пока нет

- Organization of Intel 8086Документ10 страницOrganization of Intel 8086Ashok ChakriОценок пока нет

- Unit-1,2,3 MP&MC NotesДокумент25 страницUnit-1,2,3 MP&MC NotesHyma Prasad GelliОценок пока нет

- 8086 Memory Organization PDFДокумент6 страниц8086 Memory Organization PDFAshok ChakriОценок пока нет

- 8086 Memory OrganizationДокумент6 страниц8086 Memory OrganizationManohar_3020Оценок пока нет

- Chapter 3 (Part III) - The 8086 MicroprocessorДокумент34 страницыChapter 3 (Part III) - The 8086 MicroprocessorKirubel EsayasОценок пока нет

- Architecture of 8086 MicroprocessorДокумент15 страницArchitecture of 8086 MicroprocessorAnwar Ali KhanОценок пока нет

- 8086 Microprocessor ArchitectureДокумент5 страниц8086 Microprocessor ArchitectureSanjay SharmaОценок пока нет

- Intel 8086 CPU Assembly LanguageДокумент4 страницыIntel 8086 CPU Assembly LanguageAparnaaОценок пока нет

- 8086 Memory OrganizationДокумент6 страниц8086 Memory OrganizationTarun KumarОценок пока нет

- Arche of 8086Документ9 страницArche of 8086MOHAMMED ASLAM CОценок пока нет

- 8086 Memory Organization in 40 CharactersДокумент6 страниц8086 Memory Organization in 40 CharactersRajiv Kumar100% (1)

- Microprocessor SystemsДокумент26 страницMicroprocessor SystemsHaseeb shaikhОценок пока нет

- Chapter 3: Intel 8086Документ135 страницChapter 3: Intel 8086singhrps8483% (6)

- Microprocesser AssignmentДокумент15 страницMicroprocesser AssignmentMukul RanaОценок пока нет

- Amp Module 1Документ14 страницAmp Module 1fasnamditОценок пока нет

- Introduction to the 8086 MicroprocessorДокумент11 страницIntroduction to the 8086 MicroprocessorYogesh KuteОценок пока нет

- Chapter 2 Basic Architecture of The 8088 and 8086 MicroprocessorsДокумент6 страницChapter 2 Basic Architecture of The 8088 and 8086 MicroprocessorsNugusa AberaОценок пока нет

- Unit 1&3Документ18 страницUnit 1&3Sreekanth PagadapalliОценок пока нет

- 8086 Notes NITW2020Документ76 страниц8086 Notes NITW2020ka21ecb0f27Оценок пока нет

- CS18303 Microprocessor and Microcontroller Lecture NotesДокумент160 страницCS18303 Microprocessor and Microcontroller Lecture NotesDeepak SrinivasОценок пока нет

- Chapter 5Документ168 страницChapter 5salitemhiretОценок пока нет

- Introduction To Microprocessors and Processor Organization: 1. 8086 Microprocessor FeaturesДокумент41 страницаIntroduction To Microprocessors and Processor Organization: 1. 8086 Microprocessor FeaturesYash DagaОценок пока нет

- Microprocessor Unit-1 PART AДокумент12 страницMicroprocessor Unit-1 PART ASasi BhushanОценок пока нет

- 8086 Third Term TopicsДокумент46 страниц8086 Third Term TopicsgandharvsikriОценок пока нет

- Chapter - Two of Microprocessor29Документ45 страницChapter - Two of Microprocessor29Sã MïОценок пока нет

- 2nd Lecture - Block Diagram of 8086Документ37 страниц2nd Lecture - Block Diagram of 8086shreypachauri3Оценок пока нет

- Intel 8086 Microprocessor Architecture and Features NoteДокумент12 страницIntel 8086 Microprocessor Architecture and Features NotehilmegnawОценок пока нет

- Architecture of 8086 MicroprocessorДокумент17 страницArchitecture of 8086 MicroprocessorsreenimolОценок пока нет

- EC 8691-MICROPROCESSORS AND MICROCONTROLLERSДокумент39 страницEC 8691-MICROPROCESSORS AND MICROCONTROLLERSbeaulajenishОценок пока нет

- 8086 ArchДокумент19 страниц8086 Archapi-3848496100% (1)

- Microprocessor LAB IIДокумент26 страницMicroprocessor LAB IISomnath DeyОценок пока нет

- Microprocessor NotesДокумент140 страницMicroprocessor NotesSaquibh ShaikhОценок пока нет

- SYNAPSE Techno Design Innovation PVT LTDДокумент47 страницSYNAPSE Techno Design Innovation PVT LTDcobalt_1223Оценок пока нет

- UNIT-1 Assembly Language ProgrammingДокумент30 страницUNIT-1 Assembly Language ProgrammingIshan Tiwari100% (1)

- Microprocessor and Peripherals Interfacing-ECC501Документ48 страницMicroprocessor and Peripherals Interfacing-ECC501Mohil KhareОценок пока нет

- Microprocessor ArchitectureДокумент83 страницыMicroprocessor Architectureसुनील ढिल्लोОценок пока нет

- 8086 Architecture AnswerДокумент4 страницы8086 Architecture Answerndtvv tvОценок пока нет

- 8086 Architecture Addressing ModesДокумент10 страниц8086 Architecture Addressing ModesKumaran GОценок пока нет

- Chapter-2 (Week 3 and 4)Документ20 страницChapter-2 (Week 3 and 4)getnet gizachewОценок пока нет

- 8086/8088 Architecture, Addressing Modes and Instruction SetДокумент29 страниц8086/8088 Architecture, Addressing Modes and Instruction SetAnimesh PalОценок пока нет

- L2 Architecture and InterfaceДокумент28 страницL2 Architecture and InterfaceLawal Ahmed ShehuОценок пока нет

- Mpi Unit 1Документ22 страницыMpi Unit 1sree ramyaОценок пока нет

- MPMC Unit 1Документ75 страницMPMC Unit 1Bhure VedikaОценок пока нет

- Advanced Microprocessor Presentation 4Документ21 страницаAdvanced Microprocessor Presentation 4Ubaid SaudagarОценок пока нет

- 3851.lecture1 and 2Документ12 страниц3851.lecture1 and 2Aditya GautamОценок пока нет

- Intel 8086Документ4 страницыIntel 8086Shishir YalburgiОценок пока нет

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960От EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Оценок пока нет

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationОт EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationОценок пока нет

- Mega Drive Architecture: Architecture of Consoles: A Practical Analysis, #3От EverandMega Drive Architecture: Architecture of Consoles: A Practical Analysis, #3Оценок пока нет

- PlayStation Architecture: Architecture of Consoles: A Practical Analysis, #6От EverandPlayStation Architecture: Architecture of Consoles: A Practical Analysis, #6Оценок пока нет

- PlayStation 2 Architecture: Architecture of Consoles: A Practical Analysis, #12От EverandPlayStation 2 Architecture: Architecture of Consoles: A Practical Analysis, #12Оценок пока нет

- Mahindra SUV NuvoSports - Task-B - 1Документ1 страницаMahindra SUV NuvoSports - Task-B - 1Shubhan SinghОценок пока нет

- MMD User's Guide En-UsДокумент93 страницыMMD User's Guide En-UsMekaTronОценок пока нет

- Complete FDDI Admission 2018 stepsДокумент1 страницаComplete FDDI Admission 2018 stepsShubhan SinghОценок пока нет

- Admissions 2019-20 Handbook: Master of Design (M.Des.)Документ22 страницыAdmissions 2019-20 Handbook: Master of Design (M.Des.)Shubhan SinghОценок пока нет

- UI Guidelines BlackBerry 10 PDFДокумент156 страницUI Guidelines BlackBerry 10 PDFShubhan SinghОценок пока нет

- Qualitative Research Methods and ToolsДокумент2 страницыQualitative Research Methods and ToolsShubhan SinghОценок пока нет

- AddictionДокумент2 страницыAddictionShubhan SinghОценок пока нет

- Jio-Fi Activity-B 1Документ1 страницаJio-Fi Activity-B 1Shubhan SinghОценок пока нет

- Activity-A 1Документ1 страницаActivity-A 1Shubhan SinghОценок пока нет

- TRF Abstract Shubhan SinghДокумент2 страницыTRF Abstract Shubhan SinghShubhan SinghОценок пока нет

- Activity-A 1Документ1 страницаActivity-A 1Shubhan SinghОценок пока нет

- CNC NotesДокумент21 страницаCNC NotesradhiostrokesОценок пока нет

- Interior Motives Spring 2017 PDFДокумент80 страницInterior Motives Spring 2017 PDFShubhan SinghОценок пока нет

- MadhushalaДокумент39 страницMadhushalaShailendra100% (7)

- Siemens PLM Mitsubishi Pencil Cs Z6Документ4 страницыSiemens PLM Mitsubishi Pencil Cs Z6Shubhan SinghОценок пока нет

- Robot Deal With ObjectsДокумент14 страницRobot Deal With ObjectsShubhan SinghОценок пока нет

- Summer Training PresentationДокумент13 страницSummer Training PresentationShubhan SinghОценок пока нет

- Improved Vapour Compression Refrigeration Cycles - Literature ReviДокумент9 страницImproved Vapour Compression Refrigeration Cycles - Literature ReviShubhan SinghОценок пока нет

- Cough and Cold RemedyДокумент1 страницаCough and Cold RemedyShubhan SinghОценок пока нет

- Solid Works Training ReportДокумент48 страницSolid Works Training ReportShubhan Singh63% (24)

- Unit 3-32Документ23 страницыUnit 3-32Ahmad Fahmi HidayatullahОценок пока нет

- R&AC Lecture 1Документ19 страницR&AC Lecture 1jojovaliaveetilОценок пока нет

- Material Handling Equipment...Документ41 страницаMaterial Handling Equipment...Shubhan Singh100% (2)

- MSME Centre Six Sigma CertificationДокумент9 страницMSME Centre Six Sigma CertificationShubhan SinghОценок пока нет

- TQM Library ServicesДокумент18 страницTQM Library ServicesShubhan SinghОценок пока нет

- MATLAB IntroductionДокумент10 страницMATLAB IntroductionShubhan SinghОценок пока нет

- Phantom D72Документ54 страницыPhantom D72gimmyhead_69Оценок пока нет

- Perkin Elmer Manual Operacion Series 200 VacuumDegasser PDFДокумент43 страницыPerkin Elmer Manual Operacion Series 200 VacuumDegasser PDFRuben Martinez Reyna100% (3)

- Lecture 2Документ26 страницLecture 2alessio8Оценок пока нет

- Euro III BH117L UBC Chiron Bus Body Service Manual PDFДокумент297 страницEuro III BH117L UBC Chiron Bus Body Service Manual PDFismael100% (1)

- Electrochemical Machining Nov16th2010Документ47 страницElectrochemical Machining Nov16th2010rajdrklОценок пока нет

- Panasonic Txl42etf62Документ0 страницPanasonic Txl42etf62Doru DariusОценок пока нет

- Gammu Phone DatabaseДокумент3 страницыGammu Phone DatabaseIsa MahfudiОценок пока нет

- Setting Crossovers in An AVR - Pre-Pro With Dirac Live 2 Room CorrectionДокумент5 страницSetting Crossovers in An AVR - Pre-Pro With Dirac Live 2 Room CorrectionstudskirbyОценок пока нет

- @@@ Fluid SensorsДокумент243 страницы@@@ Fluid SensorsNicuVisanОценок пока нет

- Chem Exam 3 Fall 06Документ2 страницыChem Exam 3 Fall 06juliasun8883Оценок пока нет

- MSR500EX (Mini123EX) Portable Magnetic Stripe Card Reader PDFДокумент2 страницыMSR500EX (Mini123EX) Portable Magnetic Stripe Card Reader PDFMiguel Angel Samaniego0% (1)

- COOLER MASTER - Silencio S600Документ2 страницыCOOLER MASTER - Silencio S600casogerardoОценок пока нет

- Sps0650en Poka YokeДокумент8 страницSps0650en Poka Yokepatima_sv4875Оценок пока нет

- Semester Basic Electronics 11thДокумент12 страницSemester Basic Electronics 11thSunil ShekharОценок пока нет

- Broad Band Bow Tie AntennaДокумент101 страницаBroad Band Bow Tie Antennafreon1999Оценок пока нет

- PASS - 245 - KV - 9AKK108467A803 - EN - A23Документ2 страницыPASS - 245 - KV - 9AKK108467A803 - EN - A23ManuelОценок пока нет

- Compensated Semiconductro PDFДокумент7 страницCompensated Semiconductro PDFabhinavruhelaОценок пока нет

- 1-DOF Forced Vibration Frequency ResponseДокумент95 страниц1-DOF Forced Vibration Frequency ResponseTaher Abu SeirОценок пока нет

- J5200Документ5 страницJ5200Yan TyОценок пока нет

- Department of Electrical Engineering (New Campus) : LAB 5: JFET and MOSFET (DC Biasing Review)Документ10 страницDepartment of Electrical Engineering (New Campus) : LAB 5: JFET and MOSFET (DC Biasing Review)syed furqan javedОценок пока нет

- k-300 PDVSA INSTRUMENTATION INTRODUCTIONДокумент10 страницk-300 PDVSA INSTRUMENTATION INTRODUCTIONrodolforfОценок пока нет

- Cpnversor DC - DC MAX17113Документ30 страницCpnversor DC - DC MAX17113Antonio ChavezОценок пока нет

- Vn-541pc Basic Manual MultiДокумент136 страницVn-541pc Basic Manual MultiRD MediaОценок пока нет

- Standart Operation Procedure Panel Soft StarterДокумент2 страницыStandart Operation Procedure Panel Soft Starterela elsatriaОценок пока нет

- Formula of 2 Wire RTD, 3 Wire RTD & 4 Wire RTD.Документ3 страницыFormula of 2 Wire RTD, 3 Wire RTD & 4 Wire RTD.kali bangonОценок пока нет

- TR-808 Snare DIY perfboard layout <40Документ12 страницTR-808 Snare DIY perfboard layout <40dse666Оценок пока нет

- Yokogawa Flow Meter GS01R04B04-00E-EДокумент32 страницыYokogawa Flow Meter GS01R04B04-00E-Edhanu_lagwankarОценок пока нет

- Battery discharge equation describes cell potentialДокумент8 страницBattery discharge equation describes cell potentialAnonymous q9c7KY1vОценок пока нет

- Isa S84.01 SisДокумент110 страницIsa S84.01 SisAlejandro EspinosaОценок пока нет

- 3 Introduction To Digital Communications - Line Coding, Bandpass Modulation PDFДокумент29 страниц3 Introduction To Digital Communications - Line Coding, Bandpass Modulation PDFdragoОценок пока нет