Академический Документы

Профессиональный Документы

Культура Документы

Tutorial 3 Solutions

Загружено:

Crack110011Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Tutorial 3 Solutions

Загружено:

Crack110011Авторское право:

Доступные форматы

Tutorial 3 Solutions

1. (Reference: Pages 1-11, 1-28, 1-29 of 8085 datasheet) Mnemonic code: MOV A, B ADD C MOV D, A Sequence of operations: Read register B: Contents of register B are placed on the data bus Write accumulator: Contents on the data bus are written on the accumulator Read register C: Contents of register C are placed on the data bus Write temporary register: Contents of data bus are written on the temporary register Addition of accumulator and temporary register using ALU and result is stored in accumulator Read accumulator: The stored result in accumulator A is read and placed on the data bus Write register D: The result on the data bus is written to register D

2. The two requirements of the PWM signal are: 1) Frequency of 125kHz: To obtain a clock frequency of 125kHz, it is necessary to reduce bus clock frequency by a factor of 16. Frequency reduction takes place in two stages: first in the prescaler, where the bus clock is stepped down to source clocks (A or B). This is done by writing the PWMPRCLK register (refer page 738). Further, the source clock frequency is stepped down to PWM output channel frequency. This is done by writing the PWMPERx register (refer page 753). 2) Duty cycle of 25%: Duty cycle = [(PWMPERx PWMDTYx)/PWMPERx]*100%. Therefore, for 25% duty cycle, we need, PWMPERx PWMDTYx = 0.25PWMPERx Therefore, PWMDTYx = 0.75PWMPERx To achieve 25% duty cycle, we will need PWMPERx = 4 and PWMDTYx = 3. Thus, clock A is scaled by 4 times to channel 0 (say). Therefore, a prescaling factor of 4 is needed. This can be adjusted setting PWMPRCLK = 0000 0010

Thus, the instruction set becomes, PWME = 0000 0001 % set channel 0 enabled PWMCLK = 0000 0000 % clock A is source of PWM channel 0 PWMPOL = 0000 0000 % polarity 0: pwm pulse start with level low and then goes hi PWMPRCLK = 0000 0010 % Combination of this and PWMPR0 would set pwm freq % here reduction by factor of 4 is achieved PWMCAE = 0000 0000 % left aligned output mode for channel 0 (actually all) PWMPER0 = 0000 0100 % Value 4 to have period reduction by another factor 4 and at % the same time achieve the duty cycle as mentioned above PWMDTY0 = 0000 0011 % To achieve 50% duty cycle Notes: 1) The actual denotation may change depending on the compiler software you choose. The values to be written to the registers, however, remain the same. 2) In actual implementation, all registers will have standard values of 0000 0000. These are, however, specified here only since the values are required in the respective formulae. 3) Note that not all registers specified in the datasheet are used. This is because, some registers, like those concerning clocks SA and SB are not required.

3. (Reference: Pages 1-28, 1-29 of 8085 datasheet) The program proceeds in a loop executing the following steps Value of register pair DE is decremented by 1 Contents of register D are moved to the accumulator (higher order byte of pair DE) The value stored in the accumulator is incremented (D+1) Value stored in the accumulator A is OR-ed with register E bitwise and result is stored in A In short, the program executes A= (D+1) OR E, in an infinite loop every time decreasing value of the pair DE by 1. (NOTE : This program does not do anything useful/meaningful for any applications but is meant just to understand how things would work)

4. Microinstruction required to be executed and the various stages are as follows 1) (MA) (PC) 2) (IR) M[MA]; (PC) (PC) + 1

3) (MA) (PC) 4) (T) M[MA]; 5) (MA) (PC) 6) (W) M[MA]; 7) (AL) (W) 8) (B) (T) + (AL); 9) (MA) (B) 10) (AL) M[MA]

(PC) (PC) + 1 (PC) (PC) + 1

1,2 are instruction fetch operation to fetch instruction from memory in register IR. 3,4 read the second byte (immediately after the instruction) from memory and store it in register T. 5,6 read the third byte from memory and store it in register W. contents of W are moved to AL (Note: we could have directly had the contents of memory moved to AL as well. State definitions would change accordingly). 8 moves the addition of T and AL (carried out by ALU) to register B. Finally B is set as memory address MA and contents of Memory at this address are transferred to register AL in 10. Note: THIS IS NOT THE UNIQUE SOLUTION. YOU CAN HAVE YOUR OWN SEQUENCE AND THE NEW STATES DEFINED SO AS TO FINALLY ACHIEVE THE OPERATION WITH ARCHITECTURE GIVEN (EXCEPT FOR THE CHANGE IN STATES)

5. (Reference: Pages 1-28, 1-29 of 8085 datasheet) Mnemonic code: MOV D, M MOV B, M MOV C, M MOV A, D ANA B ANA C MOV E, A MOV A, D XRA B XRA C ORA E Assembly code: 01010110 01000110 01001110

//Move value of variable A in memory to register D //Move value of variable B in memory to register B //Move value of variable C in memory to register C //Move variable A to accumulator //AND accumulator with B to get A.B in accumulator //AND accumulator with B to get A.B.C in accumulator //Store A.B.C in accumulator to register E //Move variable A to accumulator //XOR accumulator with B to get A B in accumulator //XOR accumulator with C to get A B C in accumulator //OR accumulator with E = A.B.C to get Y in accumulator

01111010 10100000 10100001 01011111 01111010 10101000 10101001 10110011 NOTE: YOU MAY SIMPLIFY EXPRESSION (OR MAKE IT MORE COMPLEX) AND IMPLEMENT IT IN A DIFFERENT WAY AS WELL.

Вам также может понравиться

- MAC Tutorial-1 SolutionsДокумент8 страницMAC Tutorial-1 SolutionsCrack110011Оценок пока нет

- ME 401 Microprocessors & Automatic Control Tutorial QuestionsДокумент2 страницыME 401 Microprocessors & Automatic Control Tutorial QuestionsCrack110011Оценок пока нет

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (890)

- Tutorial 4Документ4 страницыTutorial 4Crack110011Оценок пока нет

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- ME 401: Microprocessors and Automatic Control: Tutorial 5 - Oct 14, 2010 in ClassДокумент2 страницыME 401: Microprocessors and Automatic Control: Tutorial 5 - Oct 14, 2010 in ClassCrack110011Оценок пока нет

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (399)

- ME 401: Microprocessors and Automatic Control: Tutorial 5 - Oct 14, 2010 in ClassДокумент2 страницыME 401: Microprocessors and Automatic Control: Tutorial 5 - Oct 14, 2010 in ClassCrack110011Оценок пока нет

- ME 401 Microprocessors & Automatic Control Tutorial QuestionsДокумент2 страницыME 401 Microprocessors & Automatic Control Tutorial QuestionsCrack110011Оценок пока нет

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- ME 401 Microprocessors & Automatic Control Tutorial QuestionsДокумент2 страницыME 401 Microprocessors & Automatic Control Tutorial QuestionsCrack110011Оценок пока нет

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Tutorial 3Документ2 страницыTutorial 3Crack110011Оценок пока нет

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- ME401 Microprocessors Tutorial - Demultiplexers, Flip-Flops, CountersДокумент3 страницыME401 Microprocessors Tutorial - Demultiplexers, Flip-Flops, CountersCrack110011Оценок пока нет

- Midsem SolutionДокумент9 страницMidsem SolutionCrack110011Оценок пока нет

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Stake Codigo FonteДокумент40 страницStake Codigo FonteionОценок пока нет

- Edyza Sensors For Indoor FarmingДокумент35 страницEdyza Sensors For Indoor FarmingranabasheerОценок пока нет

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- CV Agung PriatmodjoДокумент2 страницыCV Agung PriatmodjoAgung PriatmodjoОценок пока нет

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- Nadia Natasya: Working Experiences About MeДокумент1 страницаNadia Natasya: Working Experiences About MeNurul SyafiqahОценок пока нет

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2219)

- Setting up SSH and SCP securelyДокумент2 страницыSetting up SSH and SCP securelya17fanОценок пока нет

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- Mainframe230 Blogspot inДокумент4 страницыMainframe230 Blogspot inArunachalam NarayananОценок пока нет

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- HCI Lec 1 Handout PDFДокумент5 страницHCI Lec 1 Handout PDFBryan PazОценок пока нет

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (265)

- MS2020 Stratos Series Installation and User's Guide: Metrologic Instruments, IncДокумент112 страницMS2020 Stratos Series Installation and User's Guide: Metrologic Instruments, IncnoflodaОценок пока нет

- 824 WT-2Документ42 страницы824 WT-2Michael BОценок пока нет

- CSD Sierra & Sierra ToolsДокумент2 страницыCSD Sierra & Sierra ToolsKonrad ŻabaОценок пока нет

- Audio and Network LoggingДокумент2 800 страницAudio and Network LoggingSNEYDER ZABALAОценок пока нет

- Understanding the Language of ComputersДокумент94 страницыUnderstanding the Language of Computerskrishnagovind33Оценок пока нет

- Aiwa HT-DV50 DVD Home Cinema System SMДокумент12 страницAiwa HT-DV50 DVD Home Cinema System SMRogelioMartinezОценок пока нет

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- Mr. Salamudeen Alhassan Department of Computer Sc. UDS, Navrongo, GhanaДокумент15 страницMr. Salamudeen Alhassan Department of Computer Sc. UDS, Navrongo, GhanaAziz RahimОценок пока нет

- Order 7870856 Post SIEM Implementation FinalДокумент19 страницOrder 7870856 Post SIEM Implementation FinalQuinter WandiaОценок пока нет

- OMNet 4.0 ManualДокумент361 страницаOMNet 4.0 ManualHari KrishnaОценок пока нет

- How To Connect To MySQL Using PHPДокумент3 страницыHow To Connect To MySQL Using PHPSsekabira DavidОценок пока нет

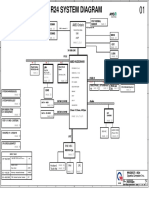

- R24 System Diagram: AMD OntarioДокумент36 страницR24 System Diagram: AMD OntarioRicardo SilvaОценок пока нет

- WDIP - API Specifications - Release 2.1 - v0.2 - FinalДокумент1 138 страницWDIP - API Specifications - Release 2.1 - v0.2 - FinalAnonymous QwwZmjОценок пока нет

- Technical Information Modbus SC2XXXДокумент44 страницыTechnical Information Modbus SC2XXXNicolas Silva BrionesОценок пока нет

- Programa de Impresion SmartformsДокумент2 страницыPrograma de Impresion Smartformsotracuentaaux5Оценок пока нет

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (119)

- A Framework To Effectively Develop Insider Threat Controls: Randy Trzeciak Dan CostaДокумент35 страницA Framework To Effectively Develop Insider Threat Controls: Randy Trzeciak Dan CostaJeya Shree Arunjunai RajОценок пока нет

- Language ProcessingДокумент29 страницLanguage ProcessingBhumika Dave50% (8)

- Mcq4 Questions on Spring Boot, Spring MVC, Microservices and REST APIsДокумент40 страницMcq4 Questions on Spring Boot, Spring MVC, Microservices and REST APIsAbcdОценок пока нет

- Developing Enterprise ArchitectsДокумент12 страницDeveloping Enterprise ArchitectskikinjoОценок пока нет

- Question 1:-Answer True or False For The Following StatementsДокумент5 страницQuestion 1:-Answer True or False For The Following StatementsMony JosephОценок пока нет

- Uniden User GuidesДокумент1 059 страницUniden User GuidesSensameaОценок пока нет

- Keys TopazДокумент6 страницKeys TopazMKОценок пока нет

- Total Station and Its ApplicationsДокумент4 страницыTotal Station and Its ApplicationsBrahmaji KommojuОценок пока нет

- DM 0903 Data Stage Slowly Changing PDFДокумент32 страницыDM 0903 Data Stage Slowly Changing PDFsirishdahagamОценок пока нет