Академический Документы

Профессиональный Документы

Культура Документы

40 V High Voltage Arbitrary Waveform Pulse Generator at Automatic Parametric Tester

Загружено:

wqefwer23erqИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

40 V High Voltage Arbitrary Waveform Pulse Generator at Automatic Parametric Tester

Загружено:

wqefwer23erqАвторское право:

Доступные форматы

40 V High Voltage arbitrary waveform Pulse Generator at Automatic Parametric Tester

Yang Pana, James Yub, Jay Kima, and Peter Griffithsa

a

Semiconductor Business, Keithley Instruments, Inc., USA, ypan@keithley.com, b Keithley Instruments, Inc., Korea

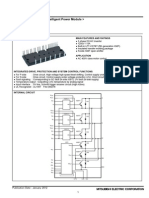

This paper introduces the development work of high voltage pulse capability of Keithley Automatic Parametric Tester (APT). To meet the market demand for high voltage (40V) function/arbitrary waveform pulse generator, Keithley Instruments developed new pulse generator that implements both features of high voltage and function/arbitrary pulse waveform within single instrument. Integrated this new pulse generator into APT, provides flash memory manufacturer a powerful tool to measure flash memory device in both Fab and Lab environment more easily and quickly than ever before. Flash memories are penetrating a wide variety of markets and products. Application examples are memory cards, MP3 audio players, cell phones, and digital cameras. This development work is driven by the demand of flash memory tests, more specifically, multilevel-flash-memories tests. Takes same area size of memory cell and same process steps, a multilevel-flashmemory cell can store 2-bit-per-cell data in 4 levels of threshold voltage (Vth), or 4-bitper-cell data in 16 levels of Vth. In comparison with 1-bit-per-cell flash memory cell that stores 1-bit data in 2 levels of Vth, the data storage density is doubled for 2-bit-per-cell memory, or is two folded for 4-bit-per-cell memory [1] [2]. Therefore, the cost of per bit is reduced significantly in multilevel-flash-memory. In order to distinguish multilevel of Vth practically and easily in memory manufacturing, a higher Vth of the largest one is required and necessary, as shown in Fig. 1. This is where the high voltage comes in. To program (write) each cell to the target Vth, program-then-verify approach is widely used. Takes 2-bit-per-cell as example, at beginning, an initial program operation sets each cell of a page of flash memory to one of level in the 3-step waveform pulse signal (Fig. 2). Then, a sequence of pulse is applied, each followed by a read operation for Vth verification. It is essential to control each level of Vth in a tight range to avoid adjacent Vth overlap one another. Since the manufacturing deviation, the numbers of program pulse needed over a whole page of flash memory is spread widely, for example, the fastest cell needs 5 pulses to program to the target Vth, but the slowest cell needs 10 pulses. The slowest cell lags program speed. It is found that ramp-T (increase pulse width) method reduces the numbers of verification steps [3], furthermore, ramp-V (increase pulse amplitude) narrows the pulse width [4]. Put both of them together, the requirement of staircase waveform pulse signal (Fig. 3) comes out. Figure 4 illustrates the hardware configuration of pulse generator in APT system. The pulse generator (4205-PG2 card) is installed in the chassis of Keithley 4200-SCS, 4200-SCS is mounted in the cabinet of Keithley S600 APT. Pulse signals are routed through test head to probe card, and send to wafer finally. Software command set are coded to facilitate users to write their own algorithm easily and to migrate old algorithms easily. The commands are p_init, p_config1, p_config2, p_config3, p_configS, and p_trig. The commands start initialization and trig, defines waveform of pulse level 1, 2, 3 and staircase accordingly.

ISDRS 2007, December 12-14, 2007, College Park, MD, USA

Wafers from different manufacturers were tested using new tool, test results are well correlated to those that is from previous tool. Test speed improvement dramatically. In summary, high voltage (40V) function/arbitrary waveform pulse generator is integrated in APT tester for multilevel flash memory measurement. The reasons why high voltage arbitrary waveform pulse generator is important are addressed. Hardware and software structure are described. Test result shows satisfied correlation and faster throughput than old tool.

4-bit-per-cell

Number of cell tested

erase 1111 1110 1101 1100 1011 1010 1001 1000 0111 0110 0101 0100 0011 0010 0001 0000

program

40 V

Vth

Number of cell tested

2-bit-per-cell program erase 11 10 01 00 Vth

1 S

Fig. 1 Profile of multilevel-flash-memory gate threshold voltage Vth distribution

Fig. 2 A 3-step waveform signal in one burst of pulse. It is defined by single command of p_config3.

Keithley S600 APT

40 V

Keithley 4200-SCS PG2 Pulse generator

50 connectors

Test head

Probe card Wafer

DC

s ble ca

Monitor

4 S Fig. 3 A 10-levels staircase waveform signal in one burst of pulse. It is defined by single command of p_configS. References

Sun Workstation

p_init p_configS p_trig

Automatic prober

Fig. 4 Hardware configuration of high voltage arbitrary waveform pulse generator in Keithley S600 Automatic Parametric Test (APT) system

[1] Marco Grossi, M. Lanzoni, and B. Ricco, "A Novel Algorithm for High-Throughput Programming of Multilevel Flash Memories," IEEE Trans. Electron Devices, Vol. 50, No. 5, pp. 1290-1296, May 2003. (Journal Article) [2] Shuka Zernovizky and Rochelle Singer, "4-Bit/Cell NAND Usage Impossible? Possible!," White Paper, msytems, SanDisk, 01-WP-0406-00, Rev 1.0, May 2006. [3] Toshihiro Tanaka, M. Kato, T. Adachi, K. Ogura, K Kimura and H. Kume, "High-Speed Programming and Program-Verify Methods Suitable for Low-Voltage Flash Memories," 1994 Symposium on VLSI Circuits Digest Technical Papers, pp. 61-62, June 1994. [4] Kang-Deog Suh, B. Suh, Y. Lim, J. Kim, Y. Choi, Y. Koh, S. Lee, S. Kwon, B. Choi, J. Yum, J. Choi, J. Kim, and H. Lim, "A 3.3V 32Mb NAND Flash Memory with Incremental Step Pulse Programming Scheme," 1995 IEEE Internal Solid State Circuits Conference, Digest of Technical papers, 42nd ISSCC, section 7, pp. 128-129, Feb. 1995. ISDRS 2007 http://www.ece.umd.edu/ISDRS

Вам также может понравиться

- Zive MP2Документ12 страницZive MP2Sandhya JakkuОценок пока нет

- Pulse / Pulsefit: Software For Electrophysiological Research, Data Acquisition, Review and Online AnalysisДокумент8 страницPulse / Pulsefit: Software For Electrophysiological Research, Data Acquisition, Review and Online AnalysisHRCОценок пока нет

- Ultrasonic Nondestructive Testing - Advanced Concepts and ApplicationsДокумент7 страницUltrasonic Nondestructive Testing - Advanced Concepts and ApplicationsDhanasekaran RОценок пока нет

- Eca Lab IntroductionДокумент7 страницEca Lab IntroductionbharathjreddyОценок пока нет

- 39ICRASE130513Документ4 страницы39ICRASE130513Kanaga VaratharajanОценок пока нет

- 2007 - Mixdes07Документ5 страниц2007 - Mixdes07Animesh GhoshОценок пока нет

- SDT LabmanualДокумент15 страницSDT LabmanualstenalyОценок пока нет

- AMP Lab ManualДокумент22 страницыAMP Lab ManualSatish PawarОценок пока нет

- 1KW-61454-1 1ns Pulsing Technical Brief 020619 PDFДокумент13 страниц1KW-61454-1 1ns Pulsing Technical Brief 020619 PDFGindra WinaldiОценок пока нет

- Automated Measurement of Frequency Response of Electrical Networks Filters and AmplifiersДокумент7 страницAutomated Measurement of Frequency Response of Electrical Networks Filters and AmplifiersDiscrete ComponentОценок пока нет

- Linear Circuit Analysis Lab Manual BeeeДокумент60 страницLinear Circuit Analysis Lab Manual BeeeAbdulQuddusОценок пока нет

- General Purpose Equipment: Me 4053 Mechanical Systems LaboratoryДокумент8 страницGeneral Purpose Equipment: Me 4053 Mechanical Systems Laboratorybill obrienОценок пока нет

- Cpu DB: Recording Microprocessor HistoryДокумент9 страницCpu DB: Recording Microprocessor Historylifelong1985Оценок пока нет

- Design of Low Power TPG With LP-LFSR: AbstractДокумент5 страницDesign of Low Power TPG With LP-LFSR: AbstractijcertОценок пока нет

- 07 Practicals STAN 7-8-9-10Документ12 страниц07 Practicals STAN 7-8-9-10Saïd Ben AbdallahОценок пока нет

- Operational Transconductance Amplifier Research PaperДокумент6 страницOperational Transconductance Amplifier Research PaperafeawjjwpОценок пока нет

- HFNSДокумент16 страницHFNSrashmi sОценок пока нет

- ,calculation: Transactions NOДокумент9 страниц,calculation: Transactions NOsirisiri100Оценок пока нет

- In The Blink of An Eye: There Goes Your AES KeyДокумент7 страницIn The Blink of An Eye: There Goes Your AES Keyserga333Оценок пока нет

- A Jitter Injection Signal Generation and ExtractioДокумент14 страницA Jitter Injection Signal Generation and Extractioيبسسي سيسيسيОценок пока нет

- AMP ManualДокумент22 страницыAMP ManualRagini SundarramanОценок пока нет

- Talking Volt MeterДокумент9 страницTalking Volt Meterudita10Оценок пока нет

- Development of A Fully Implantable Recording System For Ecog SignalsДокумент6 страницDevelopment of A Fully Implantable Recording System For Ecog SignalsGeneration GenerationОценок пока нет

- ++ 437-1692-1-PBДокумент9 страниц++ 437-1692-1-PBAli TarkashvandОценок пока нет

- Qex 1982-02Документ18 страницQex 1982-02Tihomir MitrovicОценок пока нет

- HPДокумент4 страницыHPHKVMVPVPV021511Оценок пока нет

- Low Power VLSI Unit 3Документ8 страницLow Power VLSI Unit 3Vamsi Krishna KuppalaОценок пока нет

- A Programmable Neural Interface For Investigating Arbitrary Stimulation StrategiesДокумент3 страницыA Programmable Neural Interface For Investigating Arbitrary Stimulation StrategiesTharindu DissanayakeОценок пока нет

- Performance of Various Sense Amplifier Topologies in Sub100nm Planar MOSFET TechnologyДокумент8 страницPerformance of Various Sense Amplifier Topologies in Sub100nm Planar MOSFET TechnologyInternational Journal of Application or Innovation in Engineering & ManagementОценок пока нет

- Concurrent TST RFДокумент10 страницConcurrent TST RFDeibendeile CarinuyОценок пока нет

- Microcontroller Ethernet Interfacing Purpose: MAE 285 Laboratory #5Документ11 страницMicrocontroller Ethernet Interfacing Purpose: MAE 285 Laboratory #5Avik SarkarОценок пока нет

- Data Collection System of EEG Based On USB InterfaceДокумент4 страницыData Collection System of EEG Based On USB InterfaceAdonis LealОценок пока нет

- 2 Canada-Us Cansmart Workshop: 10 - 11 October 2002, Montreal, Quebec, CanadaДокумент7 страниц2 Canada-Us Cansmart Workshop: 10 - 11 October 2002, Montreal, Quebec, CanadaBhuvaneshwar PatilОценок пока нет

- TX4400 Manual v0.94Документ39 страницTX4400 Manual v0.94ahmedalishОценок пока нет

- Ultrasonic Pulse Analyzer ControlsДокумент5 страницUltrasonic Pulse Analyzer ControlsDessvi ConsultoresОценок пока нет

- Debug and Testability Features For Multi-Protocol 10G SerdesДокумент5 страницDebug and Testability Features For Multi-Protocol 10G SerdesvelusnОценок пока нет

- Introduction To Lab Hardware: ObjectiveДокумент5 страницIntroduction To Lab Hardware: ObjectiveSoumyadeep NagОценок пока нет

- Prometer RДокумент8 страницPrometer RBitacora InternautaОценок пока нет

- Cse466 Lab 2 - Assembly and Pulse-Width Modulation: ObjectivesДокумент3 страницыCse466 Lab 2 - Assembly and Pulse-Width Modulation: ObjectivesSurya Pratap SinghОценок пока нет

- 77 PubДокумент6 страниц77 PubMojtaba JabbariОценок пока нет

- 36Документ74 страницы36Sanoop MkОценок пока нет

- FH CP12438IRC-IECinteroperability 76Документ14 страницFH CP12438IRC-IECinteroperability 76kosicenetflixОценок пока нет

- EEC 581 Computer Architecture: ProjectДокумент8 страницEEC 581 Computer Architecture: Projectjenil7042Оценок пока нет

- Prof P.N.V.M Sastry, Prof - Dr.D.N.Rao, Prof Dr.S.Vathsal: KeywordsДокумент21 страницаProf P.N.V.M Sastry, Prof - Dr.D.N.Rao, Prof Dr.S.Vathsal: KeywordstheijesОценок пока нет

- Thesis On LFSRДокумент104 страницыThesis On LFSRKaran RoyОценок пока нет

- 333 - Lab - 6 - 2017 Clarified 4 - 8 - 17Документ8 страниц333 - Lab - 6 - 2017 Clarified 4 - 8 - 17abdul nurudeenОценок пока нет

- Internal Peripherals of Avr McusДокумент2 страницыInternal Peripherals of Avr McusKuldeep JashanОценок пока нет

- Zpev 2Документ19 страницZpev 2vissie01Оценок пока нет

- Shuttle - HOT557 v.1.32 (Motherboard) - User's ManualДокумент35 страницShuttle - HOT557 v.1.32 (Motherboard) - User's Manuala.diedrichsОценок пока нет

- R01an0767eu sh7216Документ13 страницR01an0767eu sh7216mamathaursОценок пока нет

- PC Based Spectrum Analuzer With MC1496Документ7 страницPC Based Spectrum Analuzer With MC1496SzyОценок пока нет

- Power Systems Analytical Software ToolsДокумент20 страницPower Systems Analytical Software ToolsdskymaximusОценок пока нет

- MPC5xxx Programming The eTPUДокумент14 страницMPC5xxx Programming The eTPUSAABОценок пока нет

- ECNG3016 Practical 4Документ7 страницECNG3016 Practical 4Marlon BoucaudОценок пока нет

- Barrel Shifter System For Event Reconstruction For Upto3 Signal TrainsДокумент3 страницыBarrel Shifter System For Event Reconstruction For Upto3 Signal TrainsSai KrishnaОценок пока нет

- Demo Abstract: Assert - Advanced Wireless Environment Research TestbedДокумент2 страницыDemo Abstract: Assert - Advanced Wireless Environment Research TestbedMuhammad Taufik NelasОценок пока нет

- Gain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipОт EverandGain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipОценок пока нет

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsОт EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsОценок пока нет

- Ps22a74 eДокумент11 страницPs22a74 ewqefwer23erqОценок пока нет

- Duke University Dissertation Template2010Документ33 страницыDuke University Dissertation Template2010omogenikkyОценок пока нет

- TOP Business-Controller Rev 01Документ1 страницаTOP Business-Controller Rev 01wqefwer23erqОценок пока нет

- Allbuildingrules 4p LetterДокумент4 страницыAllbuildingrules 4p Letterwqefwer23erqОценок пока нет

- Energies: Analysis of Peak-to-Peak Current Ripple Amplitude in Seven-Phase PWM Voltage Source InvertersДокумент1 страницаEnergies: Analysis of Peak-to-Peak Current Ripple Amplitude in Seven-Phase PWM Voltage Source Inverterswqefwer23erqОценок пока нет

- Energies: Analysis of Peak-to-Peak Current Ripple Amplitude in Seven-Phase PWM Voltage Source InvertersДокумент1 страницаEnergies: Analysis of Peak-to-Peak Current Ripple Amplitude in Seven-Phase PWM Voltage Source Inverterswqefwer23erqОценок пока нет

- 7 Wonders StrategyДокумент33 страницы7 Wonders Strategywqefwer23erqОценок пока нет

- Shalina Healthcare JD - Business AnalyticsДокумент2 страницыShalina Healthcare JD - Business AnalyticsMeow bunОценок пока нет

- Desktop Window Manager: DWM Overviews DWM Reference DWM Sample CodeДокумент3 страницыDesktop Window Manager: DWM Overviews DWM Reference DWM Sample Codekris_onlineОценок пока нет

- IBEC BPL System ArchitectureДокумент2 страницыIBEC BPL System ArchitectureAleksandar ConevОценок пока нет

- Pas 16 - Property Plant and EquipmentДокумент4 страницыPas 16 - Property Plant and EquipmentJessie ForpublicuseОценок пока нет

- 1.doosan D1146Документ1 страница1.doosan D1146Md. ShohelОценок пока нет

- Guidelines in Research Proposal WritingДокумент19 страницGuidelines in Research Proposal WritingMark RelloresОценок пока нет

- Donor's Tax Post QuizДокумент12 страницDonor's Tax Post QuizMichael Aquino0% (1)

- CANVASS FORM MerchandiseДокумент1 страницаCANVASS FORM MerchandiseJuan VicenteОценок пока нет

- Union of India v. Mohit Minerals Pvt. LTD.-GST Validity AnalysisДокумент4 страницыUnion of India v. Mohit Minerals Pvt. LTD.-GST Validity Analysissandhya parimalaОценок пока нет

- Create or Generate QR Code in ASPДокумент5 страницCreate or Generate QR Code in ASPmtkkumaranОценок пока нет

- US Navy Course NAVEDTRA 14342 - Air Traffic ControllerДокумент594 страницыUS Navy Course NAVEDTRA 14342 - Air Traffic ControllerGeorges100% (4)

- Assignment 1: Unit 3 - Week 1Документ80 страницAssignment 1: Unit 3 - Week 1sathiyan gsОценок пока нет

- Calculation of Work IndexДокумент5 страницCalculation of Work IndexEnryan Oreski RiyadiОценок пока нет

- NISE3600EДокумент2 страницыNISE3600ENgo CuongОценок пока нет

- 213-Article Text-620-1-10-20201118Документ6 страниц213-Article Text-620-1-10-20201118Arlin FebriantiОценок пока нет

- QuickTransit SSLI Release Notes 1.1Документ12 страницQuickTransit SSLI Release Notes 1.1subhrajitm47Оценок пока нет

- Research and Practice in HRM - Sept 8Документ9 страницResearch and Practice in HRM - Sept 8drankitamayekarОценок пока нет

- Mass Effect 5e - The HomebreweryДокумент253 страницыMass Effect 5e - The HomebreweryRony Do CarmoОценок пока нет

- Hach Company v. In-SituДокумент8 страницHach Company v. In-SituPatent LitigationОценок пока нет

- Yosys+Nextpnr: An Open Source Framework From Verilog To Bitstream For Commercial FpgasДокумент4 страницыYosys+Nextpnr: An Open Source Framework From Verilog To Bitstream For Commercial FpgasFutsal AlcoletgeОценок пока нет

- Islm ModelДокумент7 страницIslm ModelPrastuti SachanОценок пока нет

- QuaverEd Lesson Plan 6-7Документ10 страницQuaverEd Lesson Plan 6-7zgyleopardОценок пока нет

- Degree 21-22 INTERNSHIPДокумент4 страницыDegree 21-22 INTERNSHIPkoushik royalОценок пока нет

- Oil & Grease CatalogДокумент4 страницыOil & Grease Catalogmanoj983@gmail.comОценок пока нет

- Tutorial MailchimpДокумент334 страницыTutorial MailchimpLeandroSabado100% (1)

- Universal Declaration of Human RightsДокумент36 страницUniversal Declaration of Human RightsJanine Regalado100% (4)

- 1a. Create Your Yosemite Zone USB DriveДокумент9 страниц1a. Create Your Yosemite Zone USB DriveSimon MeierОценок пока нет

- Analog and Digital Electronics (Ade) Lab Manual by Prof. Kavya M. P. (SGBIT, BELAGAVI)Документ74 страницыAnalog and Digital Electronics (Ade) Lab Manual by Prof. Kavya M. P. (SGBIT, BELAGAVI)Veena B Mindolli71% (7)

- Performance Online - Classic Car Parts CatalogДокумент168 страницPerformance Online - Classic Car Parts CatalogPerformance OnlineОценок пока нет