Академический Документы

Профессиональный Документы

Культура Документы

Guia 4 Final de Ctos

Загружено:

Brian Montes CollanaАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Guia 4 Final de Ctos

Загружено:

Brian Montes CollanaАвторское право:

Доступные форматы

UNIVERS SIDAD PARTI ICULAR CAT TLICA DE SANTA S MAR A DE AREQUIPA

PROG GRAMA PRO OFESIONA AL DE INGEN NIERA MEC CANICA, ME ECANICA ELECTRICA E Y MEC CATRONICA A

CDIGO O: ASIGNAT TURA: 4E0 06035 CIRC CUITOS ELEC CTRONICOS II G GUA DE LABO ORATORIO NRO O 04 Do ocente(s): In ng. Ronald p. Coaguila C Gmez z In ng. Sergio Mest tas Ramos. Fe echa: 2012.10.2 22.

SEGUNDA A FASE: CIR RCUITOS SEC CUENCIALES S

CIRCUITOS ARITMETIC A COS Y SEC CUENCIALE ES

EXPERIENCIA 4: 4 CIRCUITOS AR RITMETIC COS Y SE ECUENCI IALES

I. OBJE ETIVO:

Com mprobar las s funciones lgicas ma atemticas mediante los l circuitos s digitales aritmticos a s. Ver rificar exper rimentalme ente la oper racin de lo os latchs. Ver rificar exper rimentalme ente la oper racin de lo os flip-flops s.

II. MAR RCO TEO ORICO:

2.1 SUMADOR ctrnica un n sumador r es un ci ircuito lgico que ca alcula la o operacin suma. s En los En elec comput tadores mo odernos se encuentra en lo que se denomina Unidad aritmtico lgica (ALU). Generalmente rea alizan las operaciones aritmticas en cdigo binario d decimal o BCD B exceso o 3, gla general los sumad dores emple ean el siste ema binario o. En los c casos en los que se est por reg empleando un co omplement to a dos para repre esentar n meros neg gativos el sumador se tir en un sumador-su s ubstractor ( (Adder-subtracter). convert Las entradas son A,B,Cin A que e son la en tradas de bits b A y B, y Cin es la entrada de e acarreo. Por P da es S y Cout es la sa alida de aca arreo. otra parte, la salid bla muestra a los resulta ados de est te circuito. En la siguiente tab Entra da A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C0 0 1 0 1 0 1 0 1 Salida a C1 0 0 0 1 0 1 1 1 S 0 1 1 0 1 0 0 1

ma de las fu unciones para el acarre eo y la sum ma respectiv vamente so on: La form S = a'b b'C0 + a'bC C0' + ab'C0 0' + abC0 C1 = ab a + bC0 + aC0 Tambin se puede e poner la salida s S en funcin de C1: S = C0 0C1' + bC1' ' + aC1' + abC1

Laborato orio de Circuit tos Electrnic cos II - PPIMM EYM

Sexto S Semestre UCSM M

2012

Adems s, como lo o nico que se hace para inclu uir el acar rreo en la suma es aadirlo a la operacin, este mismo circuito se pued e formar anidando do os semisum madores, de e manera que, da S del primer se emisumado or se cone ecte a una de las entradas del segun ndo la salid semisum mador, la entrada e C0 0 se conect te con la otra o entrada del semi sumador, las salidas de acarreo o se conectan a un or para propo orcionar la salida del acarreo tot uma (C1) y la tal de la su salida S del segun ndo semisum mador se q queda como o resultado total de la operacin. .

2.2 SUMADOR BI INARIO 74 4183

2.3 LAT TCH El latch h (cerrojo) es un tip po de disp positivo de e almacena amiento tem dos mporal de dos estad (biestab bles), que se suele e agrupar en una categora c diferente a la de los flip-flops. Bsicam mente, los latches son n similares a los flip-f flops, ya qu ue son tam mbin dispos sitivos de dos d estados s que pued den perman necer en cu ualquier de e sus dos estados e gra acias a su capacidad de realime entacion, lo que consis ste en cone ectar (realimentar) ca ada una de e las salidas s a la entra ada opuesta a. La difere encia prinicpal entre a ambos tipos s de dispos sitivos est en el mto odo emplea ado para cambiar de estado e

Ing. Ronald C Coaguila G./In ng. Sergio Mes stas R.

Arequ uipa

2012

Laborato orio de Circuit tos Electrnic cos II - PPIMM EYM

Sexto S Semestre UCSM M

2012

2.4 CIR RCUITOS DE D RELOJ Los circ cuitos de re eloj genera an una se al que se alterna a ent tre los valo ores lgicos s 0 y 1 en un periodo o regular, esta seal es usada pa ara coordina ar las acciones de dos s o ms circ cuitos. al de reloj j oscila ent tre estado alto o bajo o, y grficamente tom ma la forma a de una on nda Una se cuadrad da. Los circ cuitos que utilizan u la s seal de reloj para la sincronizac cin pueden n activarse en el flanco ascenden nte, flanco descenden te o en am mbos, por ejemplo, las s memorias s DDR SDR RAM a flanc cos. son activadas en ambos yora de los s circuitos integrados s complejos s utilizan una seal d de reloj para sincronizar La may sus dife erentes par rtes y conta ar los tiemp pos de prop pagacin.

2.5 FLI IP-FLOP Los flip-flops son s circuito os capaces de perma anecer en uno de do os estados estables. Su ionamiento o es similar al de un la atch con gatillo. funci Un p pulso de en ntrada selecciona uno o de los est tados del flip-flop, el cual puede e permanecer por t tiempo inde efinido. El siguiente s p pulso de entrada lleva al flip-flop p al estado opuesto, que q tamb bin es esta able. Los d dos estado os opuestos s se consid deran estab bles porque e es necesa r un pulso de ario aplicar entra ada para ca ambiar el nivel de la s salida. Por consiguiente, un flip-flop es u n dispositivo biestab ble, similar en su op peracin a un uito multivib brador bies stable. La a breviatura para el flip p-flop es FF F. circu Los flip-flops son s import tantes en circuitos lgicos por rque prese entan caractersticas de moria. mem Para cada pulso de entrada el circu uito mantiene las cond diciones de e salida hasta la llega ada siguiente pulso p de en ntrada. Deb e que las compuertas c s lgicas no tienen esta del s be notarse capa acidad de memoria. m -flop J-K FlipEste flip-flop J-K se cons sidera como o el FF un niversal. Su u smbolo l lgico se muestra m en n la ra. figur

dos entrada as para dat tos etiquet tadas como o J y K as como otra a para el pulso p de re eloj Tiene d (CK). T Tambin tie ene dos sa alidas: Q y Q. La fl lecha (> ) en la ent trada CK indica que es disparado por fla anco ascendente; el crculo seala que el e disparo se hace con c el flan nco

Ing. Ronald C Coaguila G./In ng. Sergio Mes stas R.

Arequ uipa

2012

Laborato orio de Circuit tos Electrnic cos II - PPIMM EYM

Sexto S Semestre UCSM M

2012

descend dente, lo cu ual significa a que los d datos se tra ansfieren de esde las en ntradas has sta la salida aQ cuando el pulso de e reloj efecta una tra ansicin desde ALTO hasta h BAJO . -flop JK pre esenta cuatro modos de d operaci n tiles: El funcionamiento de un flipde retencin (hold) ). Este mo odo corresp ponde al estado de m memoria. Los L pulsos de Modo d reloj en n la entrada a CK no tien nen efecto alguno sob bre las salid das. Modo r reinicializa a (reset). La salida Q se lleva a a 0 cuand do J = 0, K=1 y el pulso p de re eloj cambia de ALTO a BAJO. inicializa (set) ( . La sa alida Q se l lleva a 1 cu uando J = 1, K = 0 y el pulso de e reloj cambia Modo i O a BAJO. de ALTO Modo d de cambio o de estado o de con nmutacin (toggle). ( En n este mod do, el estad do de la salida Q se ca ambia de manera m alter rna (de 1 a 0, de 0 a 1 y as sucesivamente e) cada vez z que llega un pulso de reloj. Se dice entonces que el FF J-K est en modo de transici n cuando la entrada J y odo de oper racin es muy m til. K permanecen en 1. Este mo op D Flip-flo Este flip p-flop slo tiene una entrada pa ara datos y otra para el pulso de e reloj CK. Sin embarg go, tiene do os salida Q y Q, como o todos los flip-flops.

bre flip-flop p D significa a flip-flop d de dato. En n algunas ocasiones ta ambin recibe el nomb bre El nomb de flip-f flop de reta ardo debido o a que se suele emp plear para retrasar, r en n un lapso equivalente e a un ciclo o de reloj, la aparici n del dato o en la salid da Q. Este retardo, d de pocos nanosegundos, puede s ser muy importante en aplicacion nes donde interviene muchos cir rcuitos. cha (> ) que est inm mediatamente despus s de la entr rada de relo oj en la figu ura La cabeza de flec ado por flan nco. En est te caso, el flip-flop D es un FF disparado d p por , indica que el FF es dispara ascendente e, trmino que q signific ca que el dato se tran nsfiere desd de la entrada D hasta a la flanco a salida Q cuando el e pulso de reloj efect ta una tra ansicin des sde el esta ado BAJO hasta el ALT TO. Se utiliz za un pequeo crculo o para indic car que el FF F se dispar ra cuando la n del pulso de a transicin reloj se e lleva a cab bo en direccin opues ta; es decir, desde AL LTO hasta B BAJO. op T Flip-flo En este e caso, el flip-flop f alterna si T= 1 cuando el reloj hac ce una tran o y nsicin de alto a bajo conserv va su estado actual si T=0 cuand do el flip-flo op est controlado por r el reloj. ente del flip p-flop T co n reloj, es slo un flip p-flop JK co on entradas s J=K=T, y su El circuito equivale a C es contr rolada por la seal de el reloj. La ecuacin e ca aracterstica a del flip-flop T con re eloj entrada se pued de deducir r de la ecu uacin del flip-flop JK, sustituy yendo T po or J y K de d la mane era siguient te:

Ing. Ronald C Coaguila G./In ng. Sergio Mes stas R.

Arequ uipa

2012

Laborato orio de Circuit tos Electrnic cos II - PPIMM EYM

Sexto S Semestre UCSM M

2012

III. INFO ORME PRE EVIO:

1. Analizar y sealar s las s caracter rsticas el ctricas y electrnic cas de los CI TT TL: 74LS83, 74L LS82, 74LS S86, en ba ase a las hojas h de da atos. 2. Exp plicar cm mo trabajan n los TTLs Full Ader y Half Ade er 3. Sealar y explicar los l tipos de TTL que se usan pa ra las fu unciones de mu ultiplicacin y divisi n, sus pr rincipales aplicacione a es. 4. Sim mular los circuitos c en un softw ware simul lador. Ano otar y pega ar graficas s obtenidas. 5. Cules son la as semejanzas y dif ferencias entre e un la atch y un f flip-flop. 6. Que es un circuito antirebote y c como se construye. c 7. Dis see y exp plique el ci ircuito que e realice la a multiplicacin de 2 nmeros s de 2 bits. un 8. Que es un ci ircuito de reloj, cua les son su us caractersticas y c como se construye c cuito de re eloj. circ (lo ms im 9. Ob btenga el datasheet d mportante) ) de los circuitos int tegrados a utilizar. Int terprete la as variable es de estas s hojas de datos.

IV. MA ATERIAL LES Y EQU UIPOS

Fue entes de Alimentaci A n Mu ultmetro 1 CI 7482 1 CI 7483 3 CI 7486 2 CI 7400 NAND Cables de co onexin 4D Dip switch de 4 y 8 contactos c Res sistencias (por lo menos m cua atro V. PRO OCEDIMIE ENTO CIRCU UITOS AR RTIMETICOS 1. Real lizar la su uma de de e dos nm meros de 4 bits cada uno a partir de e sumador res completos com mo el mostrado en l a figura. Anotar A el resultado r Protoboard Circ cuitos inte egrados 2 CI 7402 NOR 2 CI 7473 Flip Flop JK J 2 CI 7474 Flip Flop D 1 CI 74194 4 Reg. Uni iversal cada tipo): 220, 33 30, 560, Koh hm, Led ds de color res variado os

Ing. Ronald C Coaguila G./In ng. Sergio Mes stas R.

Arequ uipa

2012

Laborato orio de Circuit tos Electrnic cos II - PPIMM EYM

Sexto S Semestre UCSM M

2012

2. Dise ear y re ealizar un n sumado or rest tador de 4 bits s segn las s siguient tes instr rucciones. a) La a resta debe de real lizarse en C1 (comp plemento 1). 1 b) Ex xiste una entrada e P que deter rmina si se e realiza una u resta o una sum ma c) P= =0 suma P=1 P resta d) Pa ara el cir rcuito de la figura a , utiliza ar fu uncionamie ento coloc car una co omn a 5 V (resta) y tierra (s suma) el 74 482 y el 7483.Par aun mej jor XOR (748 86) en ser rie con la s entradas b, la pa ata

3. Implementar el e siguient te circuito y observa ar el comp portamient to, anotar resultados:

4. Implementar

y comprobar e l funciona amiento del circui ito del punto p 4 del d

cues stionario previo. p

LATC CH

5. Implemente el e siguiente e circuito.

Ing. Ronald C Coaguila G./In ng. Sergio Mes stas R.

Arequ uipa

2012

Laborato orio de Circuit tos Electrnic cos II - PPIMM EYM

Sexto S Semestre UCSM M

2012

6. Com mpruebe su u funcionamiento y a antelo en n una tabla a S R Q

7. Cam mbie el Latch del pun nto 1 con u uno construido con puertas N AND. antelo en 8. Com mpruebe su u funcionamiento y a n una tabla a. S R Q

9. Implemente el e latch con gatillo que s muestra m a continuac cin y compruebe su func cionamient to mediant te una tab bla.

10.Ree emplace la as puerta as NOR p por puerta as NAND y verifiqu ue el fun ncionamien nto anot tando en una u tabla. 11.Imp plemente el e circuito antirebote e del punt to 2 del previo. 12.Com mpruebe su s funciona amiento re egistrndo olo en una tabla.

Ing. Ronald C Coaguila G./In ng. Sergio Mes stas R.

Arequ uipa

2012

Laborato orio de Circuit tos Electrnic cos II - PPIMM EYM

Sexto S Semestre UCSM M

2012

FLIP-FLOP

13.Arm mar el circu uito para probar p el f flip flop tip po D

14.Apli ique los niveles n y pulsos p de reloj necesarios (c circuito an ntirebote) y anote sus s resu ultados en una tabla. 15.Cu l es la fun ncin del Set S y del R Reset 16.Gra afique el Diagrama de d Estados s de dicho flip flop. 17. Arm mar el circ cuito para probar el flip flop tipo JK

18.En base a los s flip flops tipo JK im mplemente e un flip flo op tipo T 19.Apli ique los ni iveles y pu ulsos nece esarios y anote sus resultados r s en una ta abla. 20.Gra afique el Diagrama de d Estados s de dicho flip flop. VI. CUES STIONARI IO FINAL L: 1. Fund damente como c funciona el cir rcuito del punto p 2 y 3 de la pr rctica. 2. Redisee el circuito c del d punto tres del procedim miento con nsiderand do entrad das

a nivel alto en e A4, A3, B1 y B2 2 del segu undo y tercer 74LS S83

3. Indic car en que e aplicacio ones prcti icas se usa an los circ cuitos sum madores y restadores s. 4. Cul l es la imp portancia de d los flip-flops. 5. Cul l es la func cin de las s patillas P Preset, Reset clear. 6. Cuan ndo emple ear latchs y cuando filp-flops. 7. Com mo almacen nar mas de un bit d e informacin. VII. CON NCLUSION NES Y OB BSERVACI IONES Form mule por lo o menos cinco conclu usiones re eferidas al desarrollo o de la pr ctica. VIII. BIB BLIOGRA AFIA: Indiq que la bibliografa co onsultada en la elab boracin de e su inform me.

TIEMPO: : 2 sesiones s de laborat torio

Ing. Ronald C Coaguila G./In ng. Sergio Mes stas R. Arequ uipa

2012

2012

Вам также может понравиться

- Guia Practica 4 PDFДокумент8 страницGuia Practica 4 PDFJuanAldairRiveraDueñas0% (1)

- Lab1 Grupo5 VilchezhuamanДокумент12 страницLab1 Grupo5 VilchezhuamanNinguna PersonaОценок пока нет

- Flip Flop ColladoДокумент10 страницFlip Flop Colladomcals1Оценок пока нет

- Electronica SecuencialДокумент33 страницыElectronica SecuencialDanielAlvarezDelValleОценок пока нет

- Flip-Flops RS JK DДокумент10 страницFlip-Flops RS JK DEduardo FajardoОценок пока нет

- cd2 Final1Документ8 страницcd2 Final1Eleazar CastilloОценок пока нет

- Final 4Документ15 страницFinal 4Jose ArmandoОценок пока нет

- Lab - Flip FlopДокумент7 страницLab - Flip Flopomar0sandoval0timanaОценок пока нет

- Universidad Nacional de PiuraДокумент7 страницUniversidad Nacional de PiurasergioabelramirezzapОценок пока нет

- Flip FlopДокумент6 страницFlip FlopJulian Andres EcheverryОценок пока нет

- Flip FlopДокумент23 страницыFlip FlopRenzoОценок пока нет

- Contadores digitales: divisores de frecuencia y circuitos integradosДокумент17 страницContadores digitales: divisores de frecuencia y circuitos integradosmadura123Оценок пока нет

- Practica 07 - Secuenciales1Документ4 страницыPractica 07 - Secuenciales1Karito HernandezОценок пока нет

- Informe Final 1 UtrillaДокумент10 страницInforme Final 1 UtrillaCaptain Underoos0% (1)

- Practika 4 - LaboratorioДокумент20 страницPractika 4 - LaboratorioAnthony Cardenas Castillo100% (2)

- Sistemas Digitales - Casemiro - UnmsmДокумент29 страницSistemas Digitales - Casemiro - UnmsmPaulОценок пока нет

- Introducción a los contadores digitales síncronos y asíncronosДокумент14 страницIntroducción a los contadores digitales síncronos y asíncronosAlee AlejandroОценок пока нет

- Flip Flops D, J-K, y T.Документ14 страницFlip Flops D, J-K, y T.AnaKarenHsОценок пока нет

- Análisis de CI 74LS74 y 74LS75Документ7 страницAnálisis de CI 74LS74 y 74LS75Gustavo PajueloОценок пока нет

- Electrónica Industrial - P8 - 1Документ10 страницElectrónica Industrial - P8 - 1ROCIO DE LOS ANGELES JUAREZ GARCIAОценок пока нет

- Lab 2-Circuitos Latch y Flip FlopДокумент3 страницыLab 2-Circuitos Latch y Flip Flopjuanjo20_11Оценок пока нет

- Cuestionario Previo 10 PDFДокумент8 страницCuestionario Previo 10 PDFROBERTO GASPAR ESCOBEDO CONTRERASОценок пока нет

- Unidad 1, 2, 3Документ30 страницUnidad 1, 2, 3Roberto Ruiz AlcántaraОценок пока нет

- Labort Sistemas DigitalesДокумент25 страницLabort Sistemas DigitalesJuan FieeОценок пока нет

- MARCO TEORICO CONTADOR ASINCRONO Imprimir y BorrarДокумент11 страницMARCO TEORICO CONTADOR ASINCRONO Imprimir y BorrarMartin CarbajalОценок пока нет

- Circuitos Latch y Flip FlopДокумент25 страницCircuitos Latch y Flip FlopJunior Solis MiñanoОценок пока нет

- Práctica 8 Latches y Flip FlopsДокумент4 страницыPráctica 8 Latches y Flip FlopsRay GzzОценок пока нет

- Entrega 2 Sistemas Digitales y EnsambladoresДокумент3 страницыEntrega 2 Sistemas Digitales y EnsambladoresErledy 711Оценок пока нет

- Informe Final 6 LABEL IIIДокумент10 страницInforme Final 6 LABEL IIIElvisHpОценок пока нет

- Informe Previo 2Документ13 страницInforme Previo 2CarlosVillavicencioGОценок пока нет

- Circuitos SecuencialesДокумент9 страницCircuitos SecuencialesjorihuelaОценок пока нет

- Flip Flop Informe 4 Circuitos Electrónicos IIДокумент13 страницFlip Flop Informe 4 Circuitos Electrónicos IIDavid IturriagaОценок пока нет

- Contador asincrónico UP/DOWN módulo 16Документ5 страницContador asincrónico UP/DOWN módulo 16Amy WatsonОценок пока нет

- Flip Flop InformeДокумент14 страницFlip Flop InformeLouis Charles100% (3)

- Trabajo Practico Flip-Flops y Circuitos Secuenciales PDFДокумент10 страницTrabajo Practico Flip-Flops y Circuitos Secuenciales PDFDonaldo Leonel Vargas AnguloОценок пока нет

- LABORATORIO 06 ORTIZ- PALOMINO- LOPEZДокумент31 страницаLABORATORIO 06 ORTIZ- PALOMINO- LOPEZJefferson ViaОценок пока нет

- Introducción A Circuitos de DisparoДокумент6 страницIntroducción A Circuitos de DisparoLuis LagunaОценок пока нет

- Informe RelojДокумент6 страницInforme RelojJuan Esteban Lopez BedoyaОценок пока нет

- 1er Informe de Digitales IiДокумент16 страниц1er Informe de Digitales IiSamirОценок пока нет

- Practica de LabДокумент13 страницPractica de LabAlexis EspinosaОценок пока нет

- FrecuencimetroДокумент13 страницFrecuencimetrojacho16Оценок пока нет

- Circuitos SecuencialesДокумент9 страницCircuitos SecuencialesVitore MorleoneОценок пока нет

- 2corte Laboratorio 1 PDFДокумент3 страницы2corte Laboratorio 1 PDFVlade RamirezОценок пока нет

- Practica SecuencialesДокумент23 страницыPractica SecuencialesJimmy MartinezОценок пока нет

- Circuitos ContadoresДокумент11 страницCircuitos Contadoresdark_0Оценок пока нет

- Implementación y análisis de circuitos biestables y monoestables en laboratorio de circuitos digitales IIДокумент11 страницImplementación y análisis de circuitos biestables y monoestables en laboratorio de circuitos digitales IIErick VillanuevaОценок пока нет

- Unidad 2. Actividad 1. EntregableДокумент3 страницыUnidad 2. Actividad 1. EntregableRicardo QuirozОценок пока нет

- Final 2 Sistemas DigitalesДокумент31 страницаFinal 2 Sistemas DigitalesMario Ccoyori100% (1)

- Sistemas Final 2Документ29 страницSistemas Final 2yuriОценок пока нет

- Circuito 555 temporizadorДокумент10 страницCircuito 555 temporizadorManuel RiegaОценок пока нет

- Contador Asincrono AscendeneДокумент13 страницContador Asincrono AscendeneAndiie RiveraОценок пока нет

- Informe FINAL 3 DigiДокумент15 страницInforme FINAL 3 DigiYean Guere LavadoОценок пока нет

- Experiencias sobre circuitos eléctricos en serie operados por corriente directaОт EverandExperiencias sobre circuitos eléctricos en serie operados por corriente directaОценок пока нет

- Curso moderno de máquinas eléctricas rotativas: Las máquinas eléctricas en régimen dinámicoОт EverandCurso moderno de máquinas eléctricas rotativas: Las máquinas eléctricas en régimen dinámicoОценок пока нет

- 100 circuitos de shields para arduino (español)От Everand100 circuitos de shields para arduino (español)Рейтинг: 3.5 из 5 звезд3.5/5 (3)

- Lab3 2013Документ3 страницыLab3 2013Brian Montes CollanaОценок пока нет

- Mejoramiento Y Tecnificación de Extrusora para La ElaboraciónДокумент97 страницMejoramiento Y Tecnificación de Extrusora para La ElaboraciónJ Andres Daza0% (1)

- Lab3 2013Документ3 страницыLab3 2013Brian Montes CollanaОценок пока нет

- LadrillosДокумент17 страницLadrillosAlexis Paredes BendezúОценок пока нет

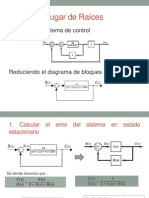

- Lugar de RaicesДокумент26 страницLugar de RaicesBrian Montes CollanaОценок пока нет

- GUIA 4 Circuitos Electricos2Документ4 страницыGUIA 4 Circuitos Electricos2Erik Leon ChañiОценок пока нет

- MS 2Документ31 страницаMS 2Brian Montes CollanaОценок пока нет

- MISSI 01 ResumenДокумент19 страницMISSI 01 ResumenSeba GiuliettiОценок пока нет

- IT Essential Resumen Capítulo 6Документ85 страницIT Essential Resumen Capítulo 6Ignacio JiménezОценок пока нет

- Analítica Web PDFДокумент48 страницAnalítica Web PDFAusberto AguilarОценок пока нет

- Medición Del Trabajo Teoria BasicaДокумент20 страницMedición Del Trabajo Teoria BasicaxОценок пока нет

- Plataforma de aprendizaje virtual SENAДокумент1 страницаPlataforma de aprendizaje virtual SENApaula andrea avila duarteОценок пока нет

- Norma para La Autorización de Levantamientos Aéreos y Exploraciones Geográficas en El Territorio NacionalДокумент5 страницNorma para La Autorización de Levantamientos Aéreos y Exploraciones Geográficas en El Territorio NacionalAdanely Bernardino GonzálezОценок пока нет

- Infraestructura FortinetДокумент1 страницаInfraestructura Fortinetedgf504Оценок пока нет

- Regulador de Voltaje Con Diodo ZenerДокумент2 страницыRegulador de Voltaje Con Diodo ZenerMaximiliano Nava CandiaОценок пока нет

- Hidroenergia Trabajo FinalДокумент13 страницHidroenergia Trabajo FinalLeysi PasacheОценок пока нет

- Practica 4 DiodoДокумент9 страницPractica 4 DiodoDaniel TacuriОценок пока нет

- PRACTICA 8 El Motor de Arranque Por CapacitorДокумент8 страницPRACTICA 8 El Motor de Arranque Por Capacitorgerahunterz96Оценок пока нет

- Estudio de Métodos y Cómo Se Hace en 8 EtapasДокумент8 страницEstudio de Métodos y Cómo Se Hace en 8 EtapasDaniel BarrenoОценок пока нет

- 7 Control FeedForwarddДокумент26 страниц7 Control FeedForwarddrolando jesus100% (1)

- Nom - 002 - Riesgos de Incendio y ExplosiónДокумент19 страницNom - 002 - Riesgos de Incendio y ExplosiónSERVICIOS ZIELKEОценок пока нет

- Guia de Aprendizaje #09Документ2 страницыGuia de Aprendizaje #09Lenin SalinasОценок пока нет

- Catedra Minuto de DiosДокумент3 страницыCatedra Minuto de DiosLiizth GonzäLëzОценок пока нет

- Tutorial: Registro de La Solicitud de Examen de RezagadosДокумент4 страницыTutorial: Registro de La Solicitud de Examen de RezagadosivanОценок пока нет

- KCSD U3 A2 RRR5Документ4 страницыKCSD U3 A2 RRR5CELОценок пока нет

- Reproductor Mp5 2 Din para Coche: EspecificaciónДокумент8 страницReproductor Mp5 2 Din para Coche: Especificaciónvictor david echeverria gonzalezОценок пока нет

- CMLB Operación 930e-5Документ254 страницыCMLB Operación 930e-5Gerardo Esteban Lagos Rojas100% (2)

- Técnica grupal el CongresoДокумент8 страницTécnica grupal el Congresoeiner perezОценок пока нет

- PRODUCTO - ACADÉMICO3 Curso ComputaciónДокумент3 страницыPRODUCTO - ACADÉMICO3 Curso ComputaciónBeykerCc ContrerasОценок пока нет

- 17.8.1 Lab Diseñe y Construya Una Red PequeñaДокумент2 страницы17.8.1 Lab Diseñe y Construya Una Red Pequeñaiam rootОценок пока нет

- Eje 1 - La Ingeniería en Colombia y Sus AplicacionesДокумент4 страницыEje 1 - La Ingeniería en Colombia y Sus AplicacionesLuisa Fernanda Pulgarin HoyosОценок пока нет

- Plan de desarrollo curricular bimestral de Física en tercer año de secundariaДокумент8 страницPlan de desarrollo curricular bimestral de Física en tercer año de secundariaLEONARDO VIVANCOSОценок пока нет

- U1 Medios de Transporte Urbano PDFДокумент40 страницU1 Medios de Transporte Urbano PDFJustina Saharaim Vargas AcostaОценок пока нет

- Tarea 2 - Griselda MéndezДокумент2 страницыTarea 2 - Griselda MéndezAmelia Cardozo YnsembranteОценок пока нет

- Guía 3primero BásicoДокумент2 страницыGuía 3primero BásicoNery BojОценок пока нет

- Memoria Sanitarias Amancio Jesus Moreno ChurampiДокумент4 страницыMemoria Sanitarias Amancio Jesus Moreno ChurampijorgeОценок пока нет

- INTRODUCCIÓN A LOS Proceso-ProductivosДокумент26 страницINTRODUCCIÓN A LOS Proceso-ProductivosJohairaОценок пока нет