Академический Документы

Профессиональный Документы

Культура Документы

Chapter 2

Загружено:

Nabilah AzizАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Chapter 2

Загружено:

Nabilah AzizАвторское право:

Доступные форматы

CHAPTER 2 THE TRAINING PROGRAMME

2.1 Module for Guided Industrial Training Module A.1 : Process And Device Characterization (Semiconductor Fabrication Process & Device Charaterization for CMOS Technology using SILVACO TCAD tools) No 1 Assignment A1001A Introduction to Semiconductor Fabrication Process 2 A1002A Semiconductor Fabrication Process And Device Characterization for CMOS 3 A1002B Semiconductor Fabrication Process And Device Characterization for CMOS Technology Table 4 : Assignment for Module A.1 Module A.2: Digital IC Design (semiconductor physics and characterisation of PMOS, NMOS, CMOS Inverter circuits using SILVACO EDA tools) No 1 2 3 4 Assignment A2001A MOSFET Characterization A2001B MOSFET Characterization A2002A CMOS Inverter Design (Preliminary) A2002B CMOS Inverter Design Deadline 26 JUNE 2013 2 JULY 2013 4 JULY 2013 12JULY2013 16 AUGUST 2013 25 JULY 2013 Deadline 17 JULY 2013

Table 5 : Assignment for Module A.2 Module A.3 : Digital IC Design (Design and layout of combinational digital logic Arithmetic circuits using SILVACO EDA tools.

No 1 2

Assignment A3001A CMOS Adder Design (Preliminary) A3001B CMOS Adder Deisgn

Deadline 20 AUGUST2013 30 AUGUST 2013

Table 6 : Assignment for Module A.3 2.2 Summary Of Works During the 10 weeks of industrial training, there were two types of task that need to be completed which were Module (70%) and Functional (30%). Table below summarized the works done within the ten weeks of industrial training.

WEEKS Week 1

SUMMARY OF WORK DONE Report in ICMIC at 8.30AM Briefing by Internship Coordinator for ICMIC, Cik Che'e Azliza binti Mohd Radzi Sorted into group F94 and being placed at ICD3 Daily Briefing Session (DBS) Briefing by En. A.Rahman regarding Module A2 Module A2001A : Preliminary Assignment about MOSFET

characterization Learning and understand the usage of Gateway and Expert software by referring on its manual Week 2 Module A2001B: MOSFET characterization Daily Briefing Session (DBS) Module A2001B : MOSFET Characterization

Module A2002A : CMOS Inverter (Preliminary) Meeting with functional supervisor Divided the task on HTML Basic assignment Week 3 Module A2002B : CMOS Inverter Design Functional project assignment on HTML5 Week 4 Module A1001A : Introduction to Semiconductor Fabrication Process Functional project assignment on Javascript

Week 5

Module A1002A: Semiconductor Fabrication Process And Device Characterization for CMOS

Week 6

Functional Project Assignment on JQuery Ajax Learning and understand the Athena and Atlas software by referring

Table 7 : Summarization of work done 2.3 Module A1: Fabrication Process and Device Characterization using Technology Computer Aided Design (TCAD) tools.

2.3.1 Introduction CMOS technology has become more popular mainly due to the lower power dissipation, practicality and lower cost of fabrication. The possibility of placing both analog and digital circuits on the same chip so as to improve the overall performance also has made CMOS technology more attractive. There are many step in fabrication process which is oxidation, threshold voltage implant, deposition, etching, doping, spacer oxide, ion implantation, annealing and others. 2.3.2 ATHENA Athena is a SILVACO Incs Version of SUPREM and is normally used in conjunction with virtual wafer fab interactive tools which include DECKBUILD, TONY PLOT, DEVEDIT, MASKVIEWS and OPTIMIZER. DECKBUILD provides an interactive run time environment. TONYPLOT supplies scientific visualization capabilities. DEVEDIT is an interactive tool for structure and mesh, MASKLVIEWS is an IC Layout Editor. The OPTIMIZER supports black box optimizations across multiple simulators. ATHENA is frequently used in conjunction with ATLAS device simulator. ATHENA predicts the physical structure that result from processing. These physical structures are used as input by ATLAS, which then predicts the electrical characteristics associated with specified bias conditions. 2.3.3 ATLAS ATLAS can be defined as device simulation tool. To run ATLAS it must fully

integrated with ATHENA process simulation software. ATLAS is a modular framework for one, two and three dimensional semiconductor device simulation. ATLAS enables from the coding stated to simulate the electrical, optical, and thermal behavior of semiconductor devices. ATLAS provides a physics-based, easy to use, modular, and extensible platform to analyze DC, AC, and time domain responses for all semiconductor based technologies in 2 and 3 dimensions. Result and process variation problems for optimal combination of speed, power, density, breakdown, leakage, luminosity, or reliability. 2.3.4 IC Fabrication Process

a) Oxidation In the process of oxidation, a protective layer of silicon dioxide is grown on the surface of the silicon wafer. Oxidation is required throughout the entire IC fabrication process. Silicon dioxide has several uses which is to act as a mask against implant or diffusion of dopant into silicon; to provide surface passivation so that wafers do not degrade when exposed to air to isolate one devices from another and to serve as a component in MOS structures. The ability to grow such a layer makes silicon one of the most used semiconductor materials. Techniques for producing silicon dioxide include thermal oxidation, wet anodization, chemical vapour deposition and plasma anodization or oxidation, the most common of which is thermal oxidation. Thermal oxidation takes place in an oxidation furnace. It is a batch operation where several lots are processed simultaneously. Wafers are exposed to an atmosphere of O2 or water vapor at temperature in the 9001300oC range. Oxidation is preceeded by a cleaning operation design to remove any impurites that may be present on the wafer surface. After cleaning, the wafers are dried and placed on a holder to be loaded on the furnace, the thickness of the oxide grown on the wafer surface is proportional to the furnace temperature and the length of exposure. b) Threshold voltage implant

adjust and maintain close control of threshold voltage, Vt by using ion implantation technique. c) Deposition The wafer is defined a thin layer of material must be grown or deposited on the wafer surface to provide conducting regions within the device, protection from the environment, and electrical insulation between metals. The most common techniques for deposition are atmopheric pressure. chemical vapor deposition (CVD), low pressure chemical vapor deposition (LPCVD), and a plasma assisted chemical vapor deposition (PCVD). In chemical vapor deposition, the wafer and gaseous compounds react thermally in a reaction chamber, producing a thin layer of a desired stable compound on the surface of the wafer, this is usually a batch operation with several lots processed in parallel. The most commonly deposited materials include polycrystalline silicon, silicon dioxide (doped and undoped) and silicon nitride. Epitaxial deposition is a special form of CVD, its special characteristic being that a thin crystalline film is deposited on the wafer surface. Several techniques have been developed for epitaxial deposition, including vapor growth,hydrogen reduction of silicon tetrachloride, and pyrolysis of silane. The deposition process begins by cleaning the wafer surface, the wafers are loaded on the epitaxial system with great care so as not to contaminate their surfaces. The epitaxial system is heated up to the proper temperature and a thin region of damaged silicon is removed from the surface of the wafer by means of an HCL etch. In the deposition step the layer is actually grown and doped. Finally the system is cooled down and the wafers are unloaded

Figure 5 : Deposition Process d) Etching Etching is the process of using strong acid or etchant to cut into the unprotected parts of a metal surface to create a design. It is used in microfabrication to chemically remove layers from the surface of a wafer during manufacturing. It is also a critically important process module, and every wafer undergoes many etching steps before it is complete. For many etch steps, part of the wafer is protected from the etchant by a "masking" material which resists etching. the masking material is a photoresist which has been patterned using photolithography Two main methods of etching: i. Wet etching Use of chemicals where a batch of wafers is dipped into a highly concentrated pool of acid and the exposed areas of the wafer are etched away. Wet etching is good and fairly cheap and capable of processing many wafers quickly.The disadvantage is that wet etching does not allow the smaller critical geometries that are needed for today chips ii. Dry etching

Dry etching refers to any of the methods of etching that use gas instead of chemical etchants. Dry etching is capable of producing critical geometries that are very small. Example of dry etching are Plasma Etching, Reactive Ion Etching in 80s, Electron Cyclotron Resonance (ECR) and Inductively Coupled Plasmas (ICP) in 90s.

Table 8 : Comparison between Wet and Dry etching e) Doping Doping is a process of chemical dopants are introduced into a silicon substrate to form the electronic structures that make integrated circuits useful. It is used to form bases, emitters, and resistors in bipolar devices, as well as drains and sources in MOS devices. It is also used to dope polysilicon layers. There are two types of doping: i) Diffusion / Thermal diffusion The movement of a chemical species from an area of high concentration to an area of lower concentration. ii) Ion implant

Process of depositing a chemical species into a substrate by direct bombardment of the substrate with high energy ions of the chemical for deposition.

Figure 6 : Doping Process f) Spacer Oxide Spacer oxide is one of a step of silicidation where spacer oxide is created on the edges of the polysilicon gate so that the deposition of the silicide will not short the gate to the source and drain.

Figure 7: Spacer Oxide Process g) Ion Implantation Impurity atoms are vaporized and accelerated toward the silicon substrate. Ion implantation forms the source or drain regions of NMOS transistors and n-well ties. The implant also dopes the polysilicon layer of the NMOS transistors, reducing its sheet

resistance.

Figure 8: Ion Implantation Process h) Annealing Annealing is the process of heating the silicon up to where the lattice structure begins to weaken, about 1000degC. Its left there for 1530minutes. The heat vibrates the atoms and if done correctly, the bonds in the crystalline structure realign themselves in their most stable form. It is needed to repair the lattice damage and put dopant atoms in substitutional sites where they can be electrically active again. 2.3.5 Parameter That Affect The Gate Oxide Thickness The parameters that affect the gate oxide thickness are the temperature, partial pressure, time and HCL. By using ATHENA software I able to prove it. i) Varying the parameter temperature with constant variable Time : 11minutes HCL : 3% Partial Pressure : 1.0atm

Figure 9: Structure of an oxide thickness for Temperature : 950c

Figure 10: Structure of an oxide thickness for Temperature : 1050c

Figure 11: Structure of an oxide thickness for Temperature : 1100c ii) Varying the parameter time with constant : Temperature : 950oc HCL : 3% Partial Pressure : 1.0atm

Figure 12: Structure of an oxide thickness for Time :11minutes

Figure 13: Structure of an oxide thickness for Time :15minutes

Figure 14: Structure of an oxide thickness for Time: 18minutes iii) Varying the parameter HCL with constant variable Time : 11minutes Temperature : 950oc Partial Pressure : 1.0atm

Figure 15: Structure of an oxide thickness for HCL :3%

Figure 16: Structure of an oxide thickness for HCL: 5%

Figure 17: Structure of an oxide thickness for HCL: 8% iv) Varying the parameter Partial pressure with contant variables: Time : 11minutes Temperature : 950oc HCL :3%

Figure 18: Structure of an oxide thickness for Pressure : 1atm

Figure 19: Structure of an oxide thickness for Pressure : 3atm

Figure 20: Structure of an oxide thickness for Pressure : 6atm Threshold voltage is ideally independent of drain voltage. The Id-Vg graph at different drain voltages level between 0 to 3.3 is plotted and the different logfiles to visually compare the operation at different voltages level is overlayed. The code to plot the graph is as below: solve vdrain=0.0 outfile=solve_1 solve vdrain=1.1 outfile=solve_2 solve vdrain=2.2 outfile=solve_3 solve vdrain=3.3 outfile=solve_4 # load infile=solve_1 log outf=nmos2_0.log

solve name=gate vgate=0 vfinal=3.3 vstep=0.3 # load infile=solve_2 log outf=nmos3_0.log solve name=gate vgate=0 vfinal=3.3 vstep=0.3 # load infile=solve_3 log outf=nmos4_0.log solve name=gate vgate=0 vfinal=3.3 vstep=0.3 # load infile=solve_4 log outf=nmos5_0.log solve name=gate vgate=0 vfinal=3.3 vstep=0.3 tonyplot -overlay nmos2_0.log nmos3_0.log nmos4_0.log -set nmos.set quit

Figure 21 : Id-VG Graph 2.3.6 MOSFET Design By using Athena, I design the NMOS and PMOS transistors with the following specifications. i. Gate length: 0.6um

ii. Abs. Threshold voltage: 0.4 V < VTH < 0.5 V iii.Abs. Leakage current: < 0.1 nA iv. NMOS Drain current, ID > 1 mA at VGS = 3.3 V and VDS = 3.3 V v. PMOS Drain Current, ID < 0.5 mA at VGS = -3.3V and VDS = -3.3 V

Figure 22: NMOS Code

Figure 23 : NMOS Output Structure

Figure 24: I-V Curve The I-V curve above shows the ID when VDS and VGS are equal 3.3 V. The value of ID is larger than 1mA as in the specifications. (ID=1.014 mA). 2.4 Module A.2: Digital IC Design (semiconductor physics and characterisation of PMOS, NMOS, CMOS Inverter circuits using SILVACO EDA tools) 2.4.1 Introduction CMOS technology has become more popular mainly due to the lower power dissipation, practicality and lower cost of fabrication. The possibility of placing both analog

and digital circuits on the same chip so as to improve the overall performance also has made CMOS technology more attractive. 2.4.2 Three Main MOS Operating Region i) Cutoff Vgs>Vt, Vgd=Vgs and Vds=0 -The sources and body is connected then it is grounded -Gate to source voltage (Vgs) is less than threshold voltage (Vt) *Source and drain have free electrons while body has free holes but no free electrons -The junction is in zero biased or reversed biased, so it have little or no current flows *No channel exist and the transistor is said to be OFF and the operation is called cutoff region

ii) Linear -Vgs>Vt,Vgs>Vgd>Vt,0<Vds<Vgs-Vt -The channel reaches the drain -Since Vds>0, there is electric field to push current from drain to source *Current flows from drain to source -Drain-to-source current, Ids increases with Vds -Linear mode of operation is also known as resistive and nonsaturated or unsaturated

iii)

Saturation -Vgs>Vt,Vds>Vgs-Vt -The channel is pinched off close to then drain (since Vgd<Vt) -There is still conduction due to drifting motion of the electron -Ids independent of Vds and depends on Vgs only -Current saturates as current does not change much (similar to current source)

2.4.3 CMOS Inverter Inverter is the most common digital gate used in the digital logic. It is used to implement logical negation. In other words, the inverter inverts the logic value of the input signal. The CMOS inverter consists of P-MOS transistor as the pull-up device and N-MOS transistor as the pull-down device. The inverter can be characterized using the voltage transfer characteristic (VTC) curve and the performance is measured by parameters such as the noise margin and the speed of the circuit.

Figure 35 : CMOS Basic Inverter Circuit

Figure 36 : Voltage Transfer Characteristic with Input Signal Region I : The PMOS device is forward biased (VSG > -VTP) and therefore on.This MOSFET is in the linear region(VSD<=VSG+VTP=VDD-Vo+VTP). The NMOS device is cut off since the input voltage isbelow VTN (Vi=VGS<VTN). The power dissipation is zero Region II: The PMOS device is in the linear region (VSD<=VSG+VTP). The NMOS device is in the saturation region (Vi=VDS>=VGS-VTN=Vo-VTN). Current now flows through both devices. Power dissipation is no longer zero. Region III: The PMOS device is in the saturation region (VSD>=VSG+VTP=VDD-Vo+VTP). The NMOS device is in the saturation region (VDS>=VGS-VTN=Vo-VTN). Power dissipation reaches a peak in this region, namely at where VM=Vi=Vo. Region IV: The PMOS device is in the saturation region (VSD>=VSG+VTP=VDD-Vo+VTP). The NMOS device is forward biased (Vi=VGS > VTN) and therefore on. This MOSFET is in the linear region (Vi=VDS<=VGS-VTN=Vo-VTN).

Region V: The PMOS device is cut off when the input is at VDD (VSG=0 V). The NMOS device is forward biased (Vi=VGS > VTN) and therefore on. This MOSFET is in the linear region (Vi=VDS<=VGS-VTN). The total power dissipation is zero just as in region I.

Figure 37 : Cmos Inverter Layout 2.4.4 CMOS Characterization A schematic is setup as shown below. The width, W = 10 m, length, L = 1 m is set, the gate to source voltage, Vgs = 1V and the drain to source voltage, Vds = VDS. The .PARAM symbol is used to introduce the DC parameter in the schematic. This part uses an ideal SPICE transistors model. The Control File is setup accordingly.

Figure 38 : NMOS Schematic Setup

Figure 39: Control File Setup

Figure 40: NMOS (Ids VS Vds)

Figure 41 : NMOS (Ids vs Vds for Vgs 1-5V) The Ids vs. Vds characteristics for the N-MOS device using the sizes below is plotted: i) W = 80 m, L = 4 m, ii) W = 20 m, L = 1 m, iii) W = 40 m, L = 20 m, iv) W= 200 m, L = 10 m, The Vds voltage from 0 V to 3 V, Vgs = 1 V is sweep

Figure 42: Control File

Figure 43: NMOS graph based on different sizes

2.4.5 Channel Length Modulation (Non-Ideal) The Control File is set to use the given process transistor model. The library files is sured are at the same location with the schematic.

Figure 44: Non-Ideal Library The Ids vs. Vds characteristics for the N-MOS device for the sizing below is plotted and the Vds voltage from 0 V to 5 V is sweeped, Vgs = 1 V.:

Table 9: Transistors Sizing for NMOS Non-Ideal and Ideal

Figure 45: NMOS NON IDEAL GRAPH

Figure 46: NMOS NON IDEAL GRAPH 2.4.6 CMOS Inverter Design I need to design and simulate the operation of CMOS inverter using the given reference datasheet. The datasheet (74HC04) is high speed Inverter IC product which contains six identical inverters with each inverter is designed with three buffer stages. A CMOS inverter chain according to the specifications (74HC04 at Temp = 25C) for the typical condition. The transistor model is used as provided by the process. For VIH

& VIL simulations, the loading capacitance CL = 15 pF at the output of the inverter is connected.

Figure 47: Schematic for CMOS Inverter Chain with Capacitor

Figure 48: Setup Control File

Figure 49: Output Graph for VIL And VIH

Table 10 : Comparison between the specification and the measured value The design met the specifications since all the measured value are in range between the needed specifications for VIH and VIL For VOH & VOL simulations, the following is set: i. ii. Connect a current source at the output of the inverter. Measure the VOH and compare the measured results to the specifications. Does the design meet the specifications? To simulate the VOH, the current source is set so that it sources the current out from the inverter. i.e the current is negative value. I. Finding the VOH by using the test condition in the data sheet

Figure 50 : CMOS Inverter Circuit for VOH

Table 11: Test Condition for VOH Simulations

Figure 51 : Output VOH For Io=5.2mA

Figure 52: Test Condition for Io=20uA

Figure 53: Test Condition for Io=4.0mA By using the test condition in the datasheet, I found that all the three test condition measured value meets it specification by referring the datasheet. The difference between this three test condition is based on current source and Vcc. Thats why there is difference in output graph as seen above,. After that, I need to find VOL by using the test conditions in the data sheet. Difference from VOH, to find VOL we place the current by connecting one end of it to VDD and the other one to Vout .

Figure 54: Schematic Setup For VOL

Table 12: Test Condition for VOL Simulations

Figure 55: Test Condition for Io=5.2mA

Figure 56: Test Condition for Io=20uA

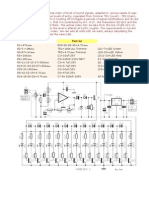

Based on the graph and the measured value, I had prove that this design had meet its specification. After all the test had been proved, I proceed to designing the CMOS Hex Incverter layout and attach the DRC and LVS report. DRC report can be seen in appendix section.

Figure 57: CMOS HEX Inverter Layout Design

Figure 58: LVS Report

2.5 Module A3 : Digital IC Design (Design and layout of combinational digital logic Arithmetic circuits using SILVACO EDA tools. In digital design, an adder or summer is a digital circuit that performs addition of numbers. In modern computers adders reside in the arithmetic logic unit (ALU) where other operations are performed. Generally, there are two types of adder, which are half adder and full adder. Adder circuit can be implemented in many ways and the most general way is by using digital gates. For example, the half adder circuit can be implemented using XOR and AND gates. Multiplier can be designed by using multiple adders. In this module three I start with basic knowledge such as binary calculation, the schematic and the truth table for half adder and full adder circuit. Next, I proceed to the design and simulate the operation of CMOS adder design. To design a full adder circuit, I need to design it by using the transistor model as provided by the process (model library:A2-002-M2-Fab2-Process1.lib)

Figure 59: 1 Bit Full Adder Circuit

Figure 60 : AND schematic used in Full Adder

Figure 61 : X-OR schematic used in the Full Adder

Figure 62 : OR schematic used in the Full Adder

To test it, I need an appropriate signals for inputs A,B and CIN. The appropriate signals can be seen as below. After that, I setup the control file and compare the result output and the truth table of the full adder.

Figure 63 :Full Adder Signal

Figure 64 : Control File

Table 13: Truth Table for Full Adder

Figure 65 : Output Simulation for Full Adder Lastly, in module A3, we are required to design a 4 bit CMOS Adder circuit. To design a 4 bit, I will design 1 bit and then copy and paste it until it have 4 bit and connected each of it. To design a 4 bit, I need to design one by one logic circuit required in 1 bit full adder which is x-or, and, or and inverter layout then after test the LVS, I will connected all of it.

Figure 66: 4 Bit Full Adder Circuit

Figure 67 : 1 Bit Full Adder

Figure 68 : 4 Bit Full Adder

Figure 69: LVS Report

Вам также может понравиться

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- Keigo Iizuka Elements of Photonics. Vol 2Документ645 страницKeigo Iizuka Elements of Photonics. Vol 2Santi Martinez CОценок пока нет

- Gas LasersДокумент53 страницыGas LasersDheeraj100% (1)

- Long Report DsДокумент21 страницаLong Report DsNabilah AzizОценок пока нет

- Silvaco ATHENA Description 4Документ21 страницаSilvaco ATHENA Description 4Nabilah AzizОценок пока нет

- A3-001-B Cmos Adder Design: Module AssignmentДокумент16 страницA3-001-B Cmos Adder Design: Module AssignmentNabilah AzizОценок пока нет

- Chapter 1Документ6 страницChapter 1Nabilah AzizОценок пока нет

- 2 4 Integrated Circuit Fabrication Process Doping StudentДокумент11 страниц2 4 Integrated Circuit Fabrication Process Doping StudentNabilah AzizОценок пока нет

- Junction LeakageДокумент3 страницыJunction LeakageNabilah AzizОценок пока нет

- MS Thesis ZhinengZhuДокумент81 страницаMS Thesis ZhinengZhuRajesh GawandeОценок пока нет

- Chapter4 OscillatorsДокумент36 страницChapter4 OscillatorsNabilah AzizОценок пока нет

- Global WarmingДокумент1 страницаGlobal WarmingNabilah AzizОценок пока нет

- Bent 3113 CHP 1 - IntroДокумент30 страницBent 3113 CHP 1 - IntroNabilah AzizОценок пока нет

- Start OrgДокумент1 страницаStart OrgNabilah AzizОценок пока нет

- Unit 2: Architecture of MicroprocessorДокумент50 страницUnit 2: Architecture of MicroprocessorNabilah AzizОценок пока нет

- Mtl7000 Series: Ultra-Slim Safety Barriers That Can Be Used Like TerminalsДокумент13 страницMtl7000 Series: Ultra-Slim Safety Barriers That Can Be Used Like TerminalsDharmilОценок пока нет

- Passive Radio Sensor Systems: HabilitationsschriftДокумент120 страницPassive Radio Sensor Systems: HabilitationsschriftoctaviantudoraОценок пока нет

- Proceedings of Spie: A Novel Spice Model of Photodetector For OEIC DesignДокумент9 страницProceedings of Spie: A Novel Spice Model of Photodetector For OEIC Design陳傳中Оценок пока нет

- Automatic NiCd Battery Charger CircuitДокумент2 страницыAutomatic NiCd Battery Charger CircuitdewasuryantoОценок пока нет

- Color TV Vertical Deflection Output Circuit: 3075-SIP7HДокумент3 страницыColor TV Vertical Deflection Output Circuit: 3075-SIP7HKiril Petranov- PetranoffОценок пока нет

- Shanghai Prisemi Elec PSC5415A - C110741Документ33 страницыShanghai Prisemi Elec PSC5415A - C110741alephzeroОценок пока нет

- Inductive Couple Plasma Reactive Ion Etching Characteristics of TiO2Документ8 страницInductive Couple Plasma Reactive Ion Etching Characteristics of TiO2Rudy FalcaoОценок пока нет

- An Activity Based Costing-Based A Case S-DikonversiДокумент12 страницAn Activity Based Costing-Based A Case S-DikonversiMuhammad Reza RizaldyОценок пока нет

- Spice Mosfet Model IntroДокумент58 страницSpice Mosfet Model IntrodeancjenningsОценок пока нет

- Voice Integrated Speed and Direction Control For DC MotorДокумент6 страницVoice Integrated Speed and Direction Control For DC MotorRahul Kumar SinghОценок пока нет

- MQ303AДокумент2 страницыMQ303APVPPPОценок пока нет

- PLC SchematicsДокумент7 страницPLC SchematicsJorge Luis Castro Vivar100% (1)

- LithographyДокумент34 страницыLithographysona007Оценок пока нет

- HCPL 314JДокумент14 страницHCPL 314JonafetsОценок пока нет

- Interface L298N DC Motor Driver Module With ArduinoДокумент16 страницInterface L298N DC Motor Driver Module With ArduinoIhot HarianjaОценок пока нет

- All Sub CO & CLO IMPДокумент48 страницAll Sub CO & CLO IMPanil1216kumarОценок пока нет

- Basic Idea of Counters Asynchronous (Ripple) Counter Using Flip-FlopsДокумент16 страницBasic Idea of Counters Asynchronous (Ripple) Counter Using Flip-FlopsSelvasundar KumarОценок пока нет

- Maharashtra State Board of Technical Education Mumbai. (M.S.)Документ9 страницMaharashtra State Board of Technical Education Mumbai. (M.S.)ythОценок пока нет

- DMC TZ1Документ63 страницыDMC TZ1Brayan Stiven ArevaloОценок пока нет

- Using Only The PVC, Move The Soda Can, But You Cannot Touch The Can With The PVC or Blow On The Can. Explain How You Did ItДокумент37 страницUsing Only The PVC, Move The Soda Can, But You Cannot Touch The Can With The PVC or Blow On The Can. Explain How You Did Itnazia zulfiqarОценок пока нет

- Circuit of Optical Index of Level of Sound SignalsДокумент1 страницаCircuit of Optical Index of Level of Sound Signalsionioni2000Оценок пока нет

- btb24600bw PDFДокумент9 страницbtb24600bw PDFAleksandar MateskiОценок пока нет

- Vector D ModelsДокумент20 страницVector D ModelsJose BurritoОценок пока нет

- Intel Advertisements Critical AnalysisДокумент7 страницIntel Advertisements Critical AnalysisSudeep D'SouzaОценок пока нет

- Alexandria University Faculty of Engineering: Electromechanical Engineering Sheet 1 (Synchronous Machine)Документ5 страницAlexandria University Faculty of Engineering: Electromechanical Engineering Sheet 1 (Synchronous Machine)Mahmoud EltawabОценок пока нет

- SigmaTel STIr4200 Datasheet 315577 1Документ22 страницыSigmaTel STIr4200 Datasheet 315577 1alpha2003rolОценок пока нет

- SFH 309 Fa - enДокумент14 страницSFH 309 Fa - enJairo FernandezОценок пока нет

- THAT 4301 DatasheetДокумент12 страницTHAT 4301 DatasheetSaverioCorОценок пока нет