Академический Документы

Профессиональный Документы

Культура Документы

27 C 512

Загружено:

Shirly KoorayИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

27 C 512

Загружено:

Shirly KoorayАвторское право:

Доступные форматы

27C512A

512K (64K x 8) CMOS EPROM

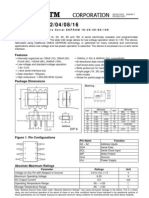

FEATURES PACKAGE TYPES

TSOP

• High speed performance

OE/VPP 1 28 A10

• CMOS Technology for low power consumption A11 2 27 CE

A9 3 26 D7

- 25 mA Active current A8 4 25 D6

- 30 µA Standby current A13

A14

5

6

24

23

D5

D4

VCC 7 22 D3

• Factory programming available 27C512A

A15 8 21 VSS

• Auto-insertion-compatible plastic packages A12 9 20 D2

A7 10 19 D1

• Auto ID aids automated programming A6 11 18 D0

A5 12 17 A0

• High speed express programming algorithm A4 13 16 A1

A3 14 15 A2

• Organized 64K x 8: JEDEC standard pinouts

- 28-pin Dual-in-line package PLCC

A12

A15

A14

A13

Vcc

NU

A7

- 32-pin PLCC Package

32

31

30

A6 5 29 A8

- 28-pin SOIC package A5 6 28 A9

- 28-pin TSOP package A4 7 27 A11

27C512A

A3 8 26 NC

- 28-pin VSOP package A2 9 25 OE/VPP

A1 10 24 A10

- Tape and reel A0 11 23 CE

NC 12 22 O7

• Data Retention > 200 years O0 13 21 O6

• Available for the following temperature ranges

14

15

16

17

18

19

20

O1

O2

NU

O3

O4

O5

VSS

- Commercial: 0˚C to +70˚C

- Industrial: -40˚C to +85˚C DIP/SOIC

- Automotive: -40˚C to +125˚C A15 1 28 VCC

A12 2 27 A14

DESCRIPTION A7

A6

3

4

26

25

A13

A8

A5 5 24 A9

The Microchip Technology Inc. 27C512A is a CMOS

27C512A

A4 6 23 A11

512K bit electrically Programmable Read Only Memory A3 7 22 OE/VPP

(EPROM). The device is organized into 64K words by A2 8 21 A10

A1 9 20 CE

8 bits (64K bytes). Accessing individual bytes from an A0 10 19 O7

address transition or from power-up (chip enable pin O0 11 18 O6

going low) is accomplished in less than 90 ns. This O1 12 17 O5

O2 13 16 O4

very high speed device allows the most sophisticated VSS 14 15 O3

microprocessors to run at full speed without the need

for WAIT states. CMOS design and processing enables

this part to be used in systems where reduced power

consumption and high reliability are requirements. VSOP

A complete family of packages is offered to provide the

OE/VPP 22 21 A10

most flexibility in applications. For surface mount appli- A11 23 20 CE

cations, PLCC, VSOP, TSOP or SOIC packaging is A9 24 19 O7

A8 25 18 O6

available. Tape or reel packaging is also available for A13 26 17 O5

PLCC or SOIC packages. A14 27 16 O4

15 O3

VCC

A15

28

1

27C512A 14 VSS

A12 2 13 O2

A7 3 12 O1

A6 4 11 O0

A5 5 10 A0

A4 6 9 A1

A3 7 8 A2

1996 Microchip Technology Inc. DS11173E-page 1

This document was created with FrameMaker 4 0 4

27C512A

1.0 ELECTRICAL CHARACTERISTICS TABLE 1-1: PIN FUNCTION TABLE

1.1 Maximum Ratings* Name Function

VCC and input voltages w.r.t. VSS ........ -0.6V to +7.25V A0-A15 Address Inputs

VPP voltage w.r.t. VSS during CE Chip Enable

programming ......................................... -0.6V to +14V

OE/VPP Output Enable/Programming Voltage

Voltage on A9 w.r.t. VSS ...................... -0.6V to +13.5V

Output voltage w.r.t. VSS ............... -0.6V to VCC +1.0V O0 - O7 Data Output

Storage temperature .......................... -65˚C to +150˚C VCC +5V Power Supply

Ambient temp. with power applied ..... -65˚C to +125˚C VSS Ground

*Notice: Stresses above those listed under “Maximum Ratings” NC No Connection; No Internal Connec-

may cause permanent damage to the device. This is a stress rat-

tion

ing only and functional operation of the device at those or any

other conditions above those indicated in the operation listings of NU Not Used; No External Connection is

this specification is not implied. Exposure to maximum rating con-

Allowed

ditions for extended periods may affect device reliability.

TABLE 1-2: READ OPERATION DC CHARACTERISTICS

VCC = +5V ±10%

Commercial: Tamb = 0˚C to +70˚C

Industrial: Tamb = -40˚C to +85˚C

Extended (Automotive): Tamb = -40˚C to +125˚C

Parameter Part* Status Symbol Min Max Units Conditions

Input Voltages all Logic "1" VIH 2.0 VCC+1 V

Logic "0" VIL -0.5 0.8 V

Input Leakage all ILI -10 10 µA VIN = 0 to VCC

Output Voltages all Logic "1" VOH 2.4 V IOH = - 400 µA

Logic "0" VOL 0.45 V IOL = 2.1 mA

Output Leakage all — ILO -10 10 µA VOUT = 0V to VCC

Input Capacitance all — CIN — 6 pF VIN = 0V; Tamb = 25°C;

f = 1 MHz

Output Capacitance all — COUT — 12 pF VOUT = 0V; Tamb = 25°C;

f = 1 MHz

Power Supply Current, C TTL input ICC — 25 mA VCC = 5.5V

Active I, E TTL input ICC — 35 mA f = 1 MHz;

OE/VPP = CE = VIL;

IOUT = 0 mA;

VIL = -0.1 to 0.8V;

VIH = 2.0 to VCC;

Note 1

Power Supply Current, C TTL input ICC(S)TLL — 1 mA

Standby I, E TTL input ICC(S)TLL — 2 mA

all CMOS input ICC(S)CMOS — 30 µA CE = Vcc±0.2V

* Parts: C=Commercial Temperature Range; I, E=Industrial and Extended Temperature Ranges

Note 1: Typical active current increases .75 mA per MHz up to operating frequency for all temperature ranges.

DS11173E-page 2 1996 Microchip Technology Inc.

27C512A

TABLE 1-3: READ OPERATION AC CHARACTERISTICS

AC Testing Waveform: VIH = 2.4V and VIL = .45V; VOH = 2.0V and VOL = 0.8V

Output Load: 1 TTL Load + 100 pF

Input Rise and Fall Times: 10 ns

Ambient Temperature: Commercial: Tamb = 0˚C to +70˚C

Industrial: Tamb = -40˚C to +85˚C

Extended (Automotive): Tamb = -40˚C to +125˚C

27C512-90* 27C512-10* 27C512-12 27C512-15

Parameter Sym Units Conditions

Min Max Min Max Min Max Min Max

Address to Output tACC — 90 — 100 — 120 — 150 ns CE = OE/

Delay VPP = VIL

CE to Output Delay tCE — 90 — 100 — 120 — 150 ns OE/VPP =

VIL

OE to Output Delay tOE — 40 — 40 — 50 — 60 ns CE = VIL

OE to Output High tOFF 0 35 0 35 0 40 0 45 ns

Impedance

Output Hold from tOH 0 — 0 — 0 — 0 — ns

Address, CE or OE/

VPP, whichever

occurred first

*90/10 AC Testing Waveforms: VIH = 3.0V and VIL = 0V; VOH = 1.5V and VOL = 1.5V

Output Load: 1 TTL Load + 30 pF

FIGURE 1-1: READ WAVEFORMS

VIH

Address Address Valid

VIL

VIH

CE

VIL

t CE(2)

VIH

OE

VIL t OFF(1,3)

t OE(2)

t OH

VOH

Outputs High Z High Z

O0 - O7 Valid Output

VOL

t ACC

Notes: (1) tOFF is specified for OE or CE, whichever occurs first

(2) OE may be delayed up to t CE - t OE after the falling edge of CE without impact on tCE

(3) This parameter is sampled and is not 100% tested.

1996 Microchip Technology Inc. DS11173E-page 3

27C512A

TABLE 1-4: PROGRAMMING DC CHARACTERISTICS

Ambient Temperature: Tamb = 25°C ± 5°C

VCC = 6.5V ± 0.25V, OE/VPP = VH = 13.0V ± 0.25V

Parameter Status Symbol Min. Max. Units Conditions (See Note 1)

Input Voltages Logic “1” VIH 2.0 VCC+1 V

Logic “0” VIL -0.1 0.8 V

Input Leakage — ILI -10 10 µA VIN = 0V to VCC

Output Voltages Logic “1” VOH 2.4 V IOH = -400 µA

Logic “0” VOL — 0.45 V IOL = 2.1 mA

VCC Current, program & verify — ICC2 — 35 mA CE = VIL

OE/VPP Current, program — IPP2 — 25 mA

A9 Product Identification — VID 11.5 12.5 V

Note 1: VCC must be applied simultaneously or before VPP voltage on OE/VPP and removed simultaneously or after

the VPP voltage on OE/VPP.

TABLE 1-5: PROGRAMMING AC CHARACTERISTICS

for Program, Program Verify AC Testing Waveform: VIH=2.4V and VIL=0.45V; VOH=2.0V; VOL=0.8V

and Program Inhibit Modes Ambient Temperature: 25°C ±5°C

VCC = 6.5V ± 0.25V, OE/VPP = VH = 13.0V ± 0.25 V

Parameter Symbol Min. Max. Units Remarks

Address Set-Up Time tAS 2 — µs

Data Set-Up Time tDS 2 — µs

Data Hold Time tDH 2 — µs

Address Hold Time tAH 0 — µs

Float Delay (2) tDF 0 130 ns

VCC Set-Up Time tVCS 2 — µs

Program Pulse Width (1) tPW 95 105 µs 100 µs typical

CE Set-Up Time tCES 2 — µs

OE Set-Up Time tOES 2 — µs

OE Hold Time tOEH 2 — µs

OE Recovery Time tOR 2 — µs

OE /VPP Rise Time During Programming tPRT 50 — ns

Note 1: For express algorithm, initial programming width tolerance is 100 µs ±5%.

2: This parameter is only sampled and not 100% teted. Output float is defined as the point where data is no

longer driven (see timing diagram).

DS11173E-page 4 1996 Microchip Technology Inc.

27C512A

FIGURE 1-2: PROGRAMMING WAVEFORMS (1)

Program Verify

VIH

Address Stable

Address VIL

VIH t AS t AH

Data VIL Data In Stable Data Out Valid

t DF

t DS t DH (2)

6.5 V (3)

VCC 5.0V t CE

t VCS (2)

VIH t PW

CE VIL

t CES t OES t OEH

t OR

13.0 V (3)

OE/V PP t OPW

VIL

t PRT

Notes: (1) The input timing reference level is 0.8V for VIL and 2.0V for VIH.

(2) t DF and tOE are characteristics of the device but must be accommodated by the programmer.

(3) VCC = 6.5V ±0.25V, V PP = VH = 13.0V ±0.5V for express programming algorithm.

TABLE 1-6: MODES

Operation Mode CE OE/VPP A9 O0 - O7

Read VIL VIL X DOUT

Program VIL VH X DIN

Program Verify VIL VIL X DOUT

Program Inhibit VIH VH X High Z

Standby VIH X X High Z

Output Disable VIL VIH X High Z

Identity VIL VIL VH Identity Code

X = Don’t Care

1.2 Read Mode For Read operations, if the addresses are stable, the

address access time (tACC) is equal to the delay from

(See Timing Diagrams and AC Characteristics) CE to output (tCE). Data is transferred to the output

Read Mode is accessed when after a delay (tOE) from the falling edge of OE/VPP.

a) the CE pin is low to power up (enable) the chip

b) the OE/VPP pin is low to gate the data to the

output pins

1996 Microchip Technology Inc. DS11173E-page 5

27C512A

1.3 Standby Mode Since the erased state is “1” in the array, programming

of “0” is required. The address to be programmed is set

The standby mode is entered when the CE pin is high, via pins A0 - A15 and the data to be programmed is pre-

and the program mode is not identified. sented to pins O0 - O7. When data and address are

When this conditions are met, the supply current will stable, a low going pulse on the CE line programs that

drop from 25 mA to 30 µA. location.

1.4 Output Enable OE/VPP 1.7 Verify

This multifunction pin eliminates bus connection in mul- After the array has been programmed it must be verified

tiple bus microprocessor systems and the outputs go to to ensure all the bits have been correctly programmed.

high impedance when: This mode is entered when all the following conditions

are met:

• the OE/VPP pin is high (VIH).

a) VCC is at the proper level,

When a VH input is applied to this pin, it supplies the

programming voltage (VPP) to the device. b) the OE/VPP pin is low, and

c) the CE line is low.

1.5 Erase Mode (UV Windowed Versions)

1.8 Inhibit

Windowed products offer the ability to erase the mem-

ory array. The memory matrix is erased to the all “1's” When programming multiple devices in parallel with dif-

state as a result of being exposed to ultraviolet light. To ferent data, only CE needs to be under separate control

ensure complete erasure, a dose of 15 watt-second/ to each device. By pulsing the CE line low on a partic-

cm2 is required. This means that the device window ular device, that device will be programmed; all other

must be placed within one inch and directly underneath devices with CE held high will not be programmed with

an ultraviolet lamp with a wavelength of 2537 Ang- the data (although address and data will be available on

stroms, intensity of 12,000 mW/cm2 for approximately their input pins).

40 minutes.

1.9 Identity Mode

1.6 Programming Mode

In this mode specific data is output which identifies the

The Express algorithm must be used for best results. It manufacturer as Microchip Technology Inc. and the

has been developed to improve programming yields device type. This mode is entered when Pin A9 is taken

and throughput times in a production environment. Up to VH (11.5V to 12.5V). The CE and OE/VPP lines must

to 10 100-microsecond pulses are applied until the byte be at VIL. A0 is used to access any of the two non-eras-

is verified. A flowchart of the Express algorithm is able bytes whose data appears on O0 through O7.

shown in Figure 1-3.

Programming takes place when:

Pin Input Output

a) VCC is brought to the proper voltage,

b) OE/VPP is brought to the proper VH level, and H

Identity 0 O O O O O O O

c) CE line is low. A0 e

7 6 5 4 3 2 1 0

x

Manufacturer VIL 0 0 1 0 1 0 0 1 29

Device Type* VIH 1 0 0 0 1 1 0 0 0D

* Code subject to change

DS11173E-page 6 1996 Microchip Technology Inc.

27C512A

FIGURE 1-3: PROGRAMMING EXPRESS ALGORITHM

Conditions:

Start

Tamb = 25˚C ±5˚C

VCC = 6.5 ±0.25V

VPP = 13.0 ±0.25V ADDR = First Location

VCC = 6.5V

VPP = 13.0V

X=0

Program one 100 µs pulse

Increment X

Verify Pass

Byte

Fail

No Yes Device

X = 10 ? Failed

Last Yes

Address?

No

Increment Address

VCC = VPP = 4.5V, 5.5V

All

Device Yes bytes No Device

Passed = original Failed

data?

1996 Microchip Technology Inc. DS11173E-page 7

27C512A

27C512A Product Identification System

To order or to obtain information (e.g., on pricing or delivery),, please use listed part numbers, and refer to factory or listed sales offices.

27C512A – 70 I /P

Package: L = Plastic Leaded Chip Carrier

P = Plastic DIP (600 Mil)

SO = Plastic SOIC (300 Mil)

TS = Thin Small Outline Package(TSOP) 8x20mm

VS = Very Small Outline Package(VSOP) 8x13.4mm

Temperature Blank = 0˚C to +70˚C

Range: I = -40˚C to +85˚C

E = -40˚C to +125˚C

Access 90 = 90 ns

Time: 10 = 100 ns

12 = 120 ns

15 = 150 ns

Device: 27C512A 512K (64K x 8) CMOS EPROM

1996 Microchip Technology Inc. DS11173E-page 11

Вам также может понравиться

- Memoria Eprom 27256 CRTL PQ SolДокумент12 страницMemoria Eprom 27256 CRTL PQ SolWinderson MacauranОценок пока нет

- 64K (8K X 8) Cmos Eprom: Features Package TypesДокумент13 страниц64K (8K X 8) Cmos Eprom: Features Package TypesIngrid XytrasОценок пока нет

- EEPROMДокумент16 страницEEPROMTutankhalmoxeОценок пока нет

- W27E257 Eprom PDFДокумент15 страницW27E257 Eprom PDFAvi Ramirez CervantesОценок пока нет

- 27C512Документ12 страниц27C512technicalavrОценок пока нет

- 27C020Документ11 страниц27C020technicalavrОценок пока нет

- 27C040Документ12 страниц27C040technicalavrОценок пока нет

- 256K (32K X 8) CMOS EPROM: Features Package TypesДокумент26 страниц256K (32K X 8) CMOS EPROM: Features Package TypesFer PerúОценок пока нет

- 27c512 PLCC 32Документ13 страниц27c512 PLCC 32redtop_68Оценок пока нет

- EEPROM 24LC512 - 21754eДокумент26 страницEEPROM 24LC512 - 21754eMarcelo Azevedo BragaОценок пока нет

- 24LC512Документ26 страниц24LC512tecpowerОценок пока нет

- 28 C 16Документ10 страниц28 C 16Omar Santiago AvalosОценок пока нет

- W 27 e 512Документ16 страницW 27 e 512MassimoОценок пока нет

- Datasheet CY62146DV30LДокумент11 страницDatasheet CY62146DV30LedgarlibanioОценок пока нет

- D27128AДокумент10 страницD27128Asantia6768Оценок пока нет

- Atmel 8568 SEEPROM AT24C256C Datasheet PDFДокумент21 страницаAtmel 8568 SEEPROM AT24C256C Datasheet PDFhanifОценок пока нет

- 74 LV 00Документ10 страниц74 LV 00Brzata PticaОценок пока нет

- CAT24C256 256 KB I C CMOS Serial Eeprom: DescriptionДокумент18 страницCAT24C256 256 KB I C CMOS Serial Eeprom: Descriptionjagadees21Оценок пока нет

- DS1220Y 16k Nonvolatile SRAM: Features Pin AssignmentДокумент8 страницDS1220Y 16k Nonvolatile SRAM: Features Pin AssignmentChico SouzaОценок пока нет

- DS1270W 3.3V 16Mb Nonvolatile SRAM: Features Pin AssignmentДокумент8 страницDS1270W 3.3V 16Mb Nonvolatile SRAM: Features Pin AssignmentAndré CastroОценок пока нет

- Memoria CAT24M01-D-91485Документ15 страницMemoria CAT24M01-D-91485Feer Rusk EdgarОценок пока нет

- S 24 Cs 08Документ34 страницыS 24 Cs 08mj15015100% (1)

- CMOS Static RAM 256K (32K X 8-Bit) IDT71256S IDT71256L: Features DescriptionДокумент10 страницCMOS Static RAM 256K (32K X 8-Bit) IDT71256S IDT71256L: Features DescriptionantoninoxxxОценок пока нет

- 25LC1024Документ32 страницы25LC1024nevdullОценок пока нет

- Nmos 128K (16K X 8) Uv Eprom: Figure 1. Logic Diagram DescriptionДокумент11 страницNmos 128K (16K X 8) Uv Eprom: Figure 1. Logic Diagram DescriptionJosepe Franco GerentОценок пока нет

- 25LC160Документ21 страница25LC160João JoséОценок пока нет

- Two-Wire Serial EEPROM 2K: Wuhan Eshine Technology Co., LTDДокумент20 страницTwo-Wire Serial EEPROM 2K: Wuhan Eshine Technology Co., LTDgrufОценок пока нет

- Dual D-Type Flip-Flop: Integrated CircuitsДокумент8 страницDual D-Type Flip-Flop: Integrated CircuitsRakesh Kumar DОценок пока нет

- 27C1001 PDFДокумент17 страниц27C1001 PDFHamter YoОценок пока нет

- 4M (512K X 8) Static Ram: Cy62148V MoblДокумент9 страниц4M (512K X 8) Static Ram: Cy62148V MoblAurelian ZaharescuОценок пока нет

- Cypress SRAM CY62256Документ11 страницCypress SRAM CY62256MicroemissionОценок пока нет

- 24 LC 2561Документ12 страниц24 LC 2561ricardo_MassisОценок пока нет

- Datasheet Search Site - WWW - AlldatasheetДокумент15 страницDatasheet Search Site - WWW - AlldatasheetPanagiotis PanagosОценок пока нет

- NM27C256 262,144-Bit (32K X 8) High Performance CMOS EPROM: General DescriptionДокумент12 страницNM27C256 262,144-Bit (32K X 8) High Performance CMOS EPROM: General DescriptiondimkaleidoscopeОценок пока нет

- IS61LV25616AL: 256K X 16 High Speed Asynchronous Cmos Static Ram With 3.3V SupplyДокумент17 страницIS61LV25616AL: 256K X 16 High Speed Asynchronous Cmos Static Ram With 3.3V SupplywarekinОценок пока нет

- 74LVC00A: 1. General DescriptionДокумент14 страниц74LVC00A: 1. General DescriptionVlad Cristia-AvramОценок пока нет

- CY27C256Документ12 страницCY27C256Mike EmpeyОценок пока нет

- Datasheet EEPROMДокумент9 страницDatasheet EEPROMIram Loya ValladaresОценок пока нет

- 93lc56 DatasheetДокумент36 страниц93lc56 DatasheetJose Angel Camara SantosОценок пока нет

- NM27C010 1,048,576-Bit (128K X 8) High Performance CMOS EPROMДокумент13 страницNM27C010 1,048,576-Bit (128K X 8) High Performance CMOS EPROMJohn MaxinОценок пока нет

- Memoria Ram 6264Документ14 страницMemoria Ram 6264DOMINGOS ALADIRОценок пока нет

- 27 C 128Документ12 страниц27 C 128andrewОценок пока нет

- 512 Kbit (64Kb x8) UV EPROM and OTP EPROM: DescriptionДокумент15 страниц512 Kbit (64Kb x8) UV EPROM and OTP EPROM: DescriptionNduwti NestaОценок пока нет

- 24 LC 128Документ26 страниц24 LC 128Santiago DiosdadoОценок пока нет

- Programming Amd'S Cmos EpromsДокумент11 страницProgramming Amd'S Cmos EpromsrwpaulaОценок пока нет

- 24 LC 64Документ12 страниц24 LC 64achuthkumarОценок пока нет

- Document Title: GM76C256CДокумент11 страницDocument Title: GM76C256CFrenk EndyОценок пока нет

- 25AA02E48 Spi Bus Serial EEPROMДокумент26 страниц25AA02E48 Spi Bus Serial EEPROMpiyushpandeyОценок пока нет

- Dmf5005n Coe DDN Eng 3Документ16 страницDmf5005n Coe DDN Eng 3roozbehxoxОценок пока нет

- DatasheetДокумент8 страницDatasheetMaizatul Hanisah RoziОценок пока нет

- Cmos Sram K6T1008C2E Family: Document TitleДокумент11 страницCmos Sram K6T1008C2E Family: Document TitleOmar LeonОценок пока нет

- Octal 3-State Noninverting D Flip-Flop: KK74HC574AДокумент6 страницOctal 3-State Noninverting D Flip-Flop: KK74HC574Ajksb100Оценок пока нет

- HCTS245MS: Radiation Hardened Octal Bus Transceiver, Three-State, Non-InvertingДокумент9 страницHCTS245MS: Radiation Hardened Octal Bus Transceiver, Three-State, Non-InvertingDeepa DevarajОценок пока нет

- NM27C512 524,288-Bit (64K X 8) High Performance CMOS EPROM: General DescriptionДокумент10 страницNM27C512 524,288-Bit (64K X 8) High Performance CMOS EPROM: General Descriptioncarlos amayaОценок пока нет

- 3-Wire Serial Eeproms: FeaturesДокумент20 страниц3-Wire Serial Eeproms: FeaturesRaghul RamasamyОценок пока нет

- 000 0 Hy628100bllg 70Документ9 страниц000 0 Hy628100bllg 70Deepa DevarajОценок пока нет

- 7Z08Документ7 страниц7Z08André Frota PaivaОценок пока нет

- 1 N 52 XXBДокумент2 страницы1 N 52 XXB81968Оценок пока нет

- DTC 162021bДокумент5 страницDTC 162021b81968Оценок пока нет

- Llave PDFДокумент1 страницаLlave PDF81968Оценок пока нет

- T315hw07v8led PDFДокумент1 страницаT315hw07v8led PDF81968Оценок пока нет

- 5800 P24QB WP20 C PDFДокумент1 страница5800 P24QB WP20 C PDF81968Оценок пока нет

- 150 Parking Assist 2017Документ7 страниц150 Parking Assist 201781968Оценок пока нет

- Audi A4 Abs EspДокумент1 страницаAudi A4 Abs Esp81968Оценок пока нет

- La76931 76933 Datasheet-2 PDFДокумент6 страницLa76931 76933 Datasheet-2 PDF81968Оценок пока нет

- Components (LWN) (3 of 6)Документ1 страницаComponents (LWN) (3 of 6)81968Оценок пока нет

- PinoutДокумент5 страницPinout819680% (1)

- t315hw07 v8 Led Driver BD 31t14-d06 198 PDFДокумент1 страницаt315hw07 v8 Led Driver BD 31t14-d06 198 PDF8196833% (3)

- t315hw07 v8 Led Driver BD 31t14-d06 198 PDFДокумент1 страницаt315hw07 v8 Led Driver BD 31t14-d06 198 PDF81968100% (3)

- A8M19BДокумент9 страницA8M19B81968100% (1)

- t315hw07 v8 Led Driver BD 31t14-d06 198 PDFДокумент1 страницаt315hw07 v8 Led Driver BD 31t14-d06 198 PDF81968100% (1)

- LM2926/LM2927 Low Dropout Regulator With Delayed Reset: General DescriptionДокумент12 страницLM2926/LM2927 Low Dropout Regulator With Delayed Reset: General Description81968Оценок пока нет

- t315hw07 v8 Led Driver BD 31t14-d06 198Документ1 страницаt315hw07 v8 Led Driver BD 31t14-d06 19881968100% (9)

- ZXMP4A57E6: 40V P-Channel Enhancement Mode MosfetДокумент9 страницZXMP4A57E6: 40V P-Channel Enhancement Mode Mosfet81968Оценок пока нет

- 9623 BIT3251 DatasheetДокумент7 страниц9623 BIT3251 Datasheet81968Оценок пока нет

- 3GBP082470 BSK 3gbp082470 BSKДокумент3 страницы3GBP082470 BSK 3gbp082470 BSKramy alfonsОценок пока нет

- PDF UM 335 02-en-0-tecDocPdfResource PDFДокумент98 страницPDF UM 335 02-en-0-tecDocPdfResource PDFAsif Javed100% (1)

- Lube Oil System - Alco & HHP - 2Документ43 страницыLube Oil System - Alco & HHP - 2kiran kumarОценок пока нет

- Epson C4-Series Robot Manual (r16)Документ256 страницEpson C4-Series Robot Manual (r16)Produccion TAMОценок пока нет

- XRT1500 ManualДокумент60 страницXRT1500 Manualold.smogОценок пока нет

- Service Manual: For Seca 777Документ28 страницService Manual: For Seca 777Natalia VelasquezОценок пока нет

- Elecrtic Motors Universal Protection Device: Service ManualДокумент31 страницаElecrtic Motors Universal Protection Device: Service ManualIgor MândruОценок пока нет

- OptiClean Air HandlerДокумент2 страницыOptiClean Air Handlercarrier indiaОценок пока нет

- Alpha Cxps 48 1.8 I, 48v Pos GNDДокумент52 страницыAlpha Cxps 48 1.8 I, 48v Pos GNDtdzeienОценок пока нет

- The Ratio of Voltage and Electric Current in A Closed CircuitДокумент12 страницThe Ratio of Voltage and Electric Current in A Closed Circuitzunaira123478% (9)

- Gua Conduit Outlet BoxesДокумент4 страницыGua Conduit Outlet BoxesPipitlyОценок пока нет

- Facemaster 2.3 Yedek ParçaДокумент545 страницFacemaster 2.3 Yedek Parçaonur tezmanОценок пока нет

- Foxcom H77MXV-D-HW-SchematicДокумент46 страницFoxcom H77MXV-D-HW-SchematicMai HomОценок пока нет

- Reviewer For Grade 8Документ2 страницыReviewer For Grade 8Nero GuilalasОценок пока нет

- Hydropump 6570269 CRM 3-86 PDFДокумент190 страницHydropump 6570269 CRM 3-86 PDFjulianmataОценок пока нет

- The Shaping MachineДокумент104 страницыThe Shaping MachineJohn Smith90% (10)

- HP Laptop 15-Bs0xxДокумент124 страницыHP Laptop 15-Bs0xxmanoj14febОценок пока нет

- Adam-4068 DS20110819093727Документ1 страницаAdam-4068 DS20110819093727Paun AlОценок пока нет

- Lab 3.1.9c Straight-Through Cable ConstructionДокумент3 страницыLab 3.1.9c Straight-Through Cable ConstructionDennis OonОценок пока нет

- NEC Art 314 314.16 Number of Conductors in Boxes and Conduit BodiesДокумент7 страницNEC Art 314 314.16 Number of Conductors in Boxes and Conduit BodiesroyvindasОценок пока нет

- SST39SF020 - Flash BiosДокумент23 страницыSST39SF020 - Flash BiosFélix NicolauОценок пока нет

- Ac Motor Coupled With DC GeneratorДокумент1 страницаAc Motor Coupled With DC GeneratorVirender RanaОценок пока нет

- Pre Test: Accomplishment Report June 2, 2020Документ4 страницыPre Test: Accomplishment Report June 2, 2020JeffreyОценок пока нет

- CyberPower DS OLS6000-10000ERT6U (XL3U) en v2Документ2 страницыCyberPower DS OLS6000-10000ERT6U (XL3U) en v2Feby AndyОценок пока нет

- Hih 060216Документ337 страницHih 060216Asif IqbalОценок пока нет

- Manual Placa Baza ASUS X99 DELUXEДокумент146 страницManual Placa Baza ASUS X99 DELUXELiviu Gabriel Mares100% (1)

- Metalworking ToolsДокумент6 страницMetalworking ToolsHoai nam100% (1)

- Screenshot 2023-04-05 at 2.49.56 AMДокумент89 страницScreenshot 2023-04-05 at 2.49.56 AMAshrakat Khaled BadawyОценок пока нет

- Totem-Pole Output StageДокумент18 страницTotem-Pole Output StageSlanky BirOe PulauОценок пока нет