Академический Документы

Профессиональный Документы

Культура Документы

Cxa1585q - RGB Decoder

Загружено:

Vehid ParićИсходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Cxa1585q - RGB Decoder

Загружено:

Vehid ParićАвторское право:

Доступные форматы

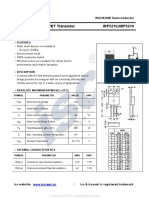

CXA1585Q

RGB Decoder

Description The CXA1585Q is an IC which converts composite video signals into RGB signals, and can be used with both NTSC and PAL systems. Features Filter for sharpness APL circuit Low carrier leak (3.58MHz components, 5mVp-p or less typ.) Compatible with both NTSC and PAL systems Low power consumption (120mV, VCC = 5V) Applications General-purpose RGB decoders, color liquid crystal viewnders, liquid crystal TVs, etc.

32 pin QFP (Plastic)

Structure Bipolar silicon monolithic IC Absolute Maximum Ratings (Ta = +25C) Supply voltage Vcc 7 V Operating temperature Topr 20 to +75 C Storage temperature Tstg 65 to +150 C 500 mW Allowable power dissipation PD Recommended Operating Conditions Supply voltage 4.6 to 5.25 (typ. 5V)

Block Diagram

SYNC TC Y CLPTC

17 APL AMP SIG AMP

24

23

22

21

20

19 APL DET

Vcc1 GND1 SHP CTL SHP F0 TP ADJ C ADJ ACC TC C IN

SHARPNESS 25

CLP SYNC SEP

SYNC SLICE PULSE GEN

APL CTL

18

SYNC IN

CLP TC

APL TC

VREG

Y IN

16

BF SYNC DLA BIAS ACK TC C OUT DLA IN R OUT G OUT

26

15 14

27

BLK

ACK ACK DET CHROMA AMP FF ADD/SUB SW R-Y 0 DEM B-Y

Y CLP 13

28

BURST GATE

PAL ID

29

12 DL AMP

30 ACC DET ACC

11

31

INV 90

10

32

HUE

PS

Y/C MIX

APC 1 2 3

VXO 4 5 6 7 8

APC TC

VXO2

VXO1

SC OUT

GND2

Vcc2

Sony reserves the right to change products and specications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

HUE ADJ

B OUT

E92515B46-TE

CXA1585Q

Pin Descriptions

Pin Number Symbol Pin Voltage Equivalent Circuit Description

HUE ADJ

2.0V

30k 47k 1 1k 1k 5k

Hue adjustment. The hue can be adjusted by 10 or more by applying a voltage ranging from 0.5 to 3.5V to this pin.

5k 100A 20k

3784 02

APC TC

34V

APC (color sync) time constant and free-running frequency adjustment. The VXO free-running frequency can be adjusted by varying the DC voltage applied to this pin for no signal.

2 100k

1k

1k 3.4V 100A

VXO2

3.1 V

Crystal oscillator.

10k 3

100A

100A

3784 04

VXO1

3.2V

Crystal oscillator.

300A

CXA1585Q

Pin Number

Symbol

Pin Voltage

Equivalent Circuit

Description

SC OUT

1.6V

4k

Subcarrier output.

600mVP-P (typ.) 5

200A

3784 06

GND2

0V

GND for chroma.

Vcc2

5V

Vcc for chroma.

B OUT

2.0V

B output.

* With 75% color bar reference level input.

0.75VP-P 200

G OUT

4k 10k 8 9 10 0.5p 364A 92A

G output.

0.75VP-P

10

R OUT

R output.

0.75VP-P

11

DLA IN

0V (NTSC) 2.3V (PAL)

129 11 5k 5k

Delay line amplier input. Connects to GND for NTSC mode; connects the 1H delay line output for PAL mode.

Approx. 10mVP-P 4k 12A

3784 12

4k

CXA1585Q

Pin Number

Symbol

Pin Voltage

Equivalent Circuit

Description

12

C OUT

3.15V

Chroma output for PAL. Connects to Vcc for NTSC mode; connects to the 1H delay line input for PAL mode.

12 Approx. 45mVP-P

364A

13

ACK TC

3.1V

4k

4k

ACK (automatic color killer) time constant.

13 100k

400A

3784 16

14

DLA BIAS

0V (NTSC) 2.3V (PAL)

14

30A

10k 5k 5k

NTSC/PAL mode switching and delay line amplier gain control. NTSC mode: V14 0.8V PAL mode: 2.0V V14 2.6V Variable range: 2dB or more

4k

4k

30A

3784 17

15

SYNC

H 4V or more L 0.5V or less

Composite sync output. This polarity is positive (typ.).

32k 2k 15 1k 1H 5k 4.7s (typ.)

CXA1585Q

Pin Number

Symbol

Pin Voltage

Equivalent Circuit

Description

16

BF

H 4V or more L 0.5V or less

Burst ag output. This polarity is negative (typ.).

32k 2k 16 1k 1H 2.6s (typ.)

5k

3784 20

17

Y CLP TC

3.1V

1k 1k

Pedestal clamp time constant.

17

60k 100A 60A

3784 22

18

APL CTL

3.0V

8k 129 18

APL sensitivity control. The control range is 3 to 5V. When APL control is not performed, connects this pin to GND.

8k

8k

3784 23

19

APL TC

2.5V

2k 19

Time constant for detecting APL (average picture level) of luminance signal. APL 0% V19 = 2.0V (typ.) APL 100% V19 = 3.2V (typ.)

256mV=100% white

164A

50A

3784 24

CXA1585Q

Pin Number

Symbol

Pin Voltage

Equivalent Circuit

Description

20

SYNC TC

3.1V

Sync tip clamp time constant for sync separation.

20 3.4V

60k

100A

60A

3784 26

21

CLP TC

3.1V

Pedestal clamp time constant.

21 3.4V

60k

100A

60A

3784 27

22

VREG

4.2V

22

4.2V regulator output. Decoupling capacitance is provided. It cannot be used as an external power supply.

3784 28

23

SYNC IN

2.5V

129 23 50k

Signal input pin for sync separation. Standard sync level is 103mVp-p. Normally shorted with Y IN (Pin 24) for use.

103mVP-P 2.5V 60A 1H

CXA1585Q

Pin Number

Symbol

Pin Voltage

Equivalent Circuit

Description

24

Y IN

2.5V

46A 129 24 50k 2.5V

3784 31

Y signal input. Standard input level. SYNC = 103mVp-p 100% white = 256mVp-p Do not supply the burst signal.

256mVP-P 103mVP-P

25

Vcc1

5V

Vcc for Y.

26

GND 1

0V

GND for Y.

27

SHP CTL

2.5V

46A 32k 27 3k 2.5V

3784 33

Sharpness gain control. Variable range: 4.5dB to +4.5dB (1.5V V27 3.5V) Adjusts the sharpness level by the voltage supplied to this pin.

28

SHP F0

2.1V

Sharpness lter frequency adjustment. Adjusts the lter f0 by varying the current took out from this pin.

129 28 4k 4k 5p 4k 2.1V 46A

3784 34

CXA1585Q

Pin Number

Symbol

Pin Voltage

Equivalent Circuit

Description

29

TPADJ

1.23V

10k 2.5k 129 29

Sets the timing of the pulses used in the IC. Connects a 27kW resistor between this pin and GND.

* Use a metal lm resistor with an accuracy of 1%.

3784 35

30

C ADJ

2.5V

10k 25k

Chroma amplier gain adjustment. Adjusts the gain of chroma amplier by the voltage (1.5 to 3V) supplied to this pin. Gain variable range: 20 to +8dB

30 20k 2k 2k 25k 60A

3784 36

10k

31

ACC TC

2.2V

220

ACC (automatic color control) time constant.

31

97A

3784 37

32

C IN

2.3V

129 32 8k 2.5k 2.5k 8k

Chroma signal input. The standard input level is 143mVp-p of burst amplitude.

2.3V

100

100 10A

2.3V

143mVP-P

3784 38

CXA1585Q

Electrical Characteristics

(Ta = +25C, VCC = 5V Refer to the Electrical Characteristics Test Circuit)

Input Signals Test Y IN C IN Point 24 pin 32 pin (pin) Min. Typ. Max. Unit SIG1 SIG2 7, 25 17.0 24.0 32.0 mA 8 10.0 11.5 13.0 dB

Item Power consumption Gain for Y

Symbol ICC1 VO

Conditions Sum of currents owing to VCC1 and VCC2 F = 300kHz, VA = 160mVp-p, VL = 160mV Measure gain between input (= VL) and output F = 3.5MHz, VA = 160mVp-p, VL = 160mV Gain difference between 300kHz and 3.5MHz F = 1.5MHz, VA = 50mVp-p, VL = 160mV Ratio of 300kHz and 1.5MHz when SHP CTL (Pin 27) is 3.5V F = 1.5MHz, VA = 160mVp-p, VL = 160mV Ratio of 300kHz and 1.5MHz when SHP CTL (Pin 27) is 1.5V F = 300kHz, VA = 160mVp-p, VL = 256mV Measures gain between input (= VL) and output F = 300kHz, VA = 160mVp-p, VL = 128mV APL CTL (18 pin) = 3.0V Measures gain between input (= VL) and output F = 300kHz, VA = 160mVp-p, VL = 90mV APL CTL (18 pin) = 3.0V Measures gain between input (= VL) and output VL = 256mV Measures DC voltage at APL TC (Pin 19) VL = 0mV Measures DC voltage at APL TC (Pin 19) Measures pedestal voltage at Pins 8, 9 and 10 Inputs fsc + 250Hz sine wave and conrms that it is locked with SC OUT (Pin 5) Inputs fsc 250Hz sine wave and conrms that it is locked with SC OUT (Pin 5) ACC1 = C OUT (6dB: VA = 286mVp-p) C OUT (0dB: VA = 143mVp-p)

Cut-off frequency for Y

VFC

SIG2

3.0

dB

Sharpness characteristics max.

VSHP (max.)

SIG2

4.5

dB

Sharpness characteristics min.

VSHP (min.)

SIG2

4.5 dB

AGC characteristics APL 100%

VAGC1

SIG2

3.6

4.9

6.2

dB

AGC characteristics APL 50%

VAGC2

SIG2

3.9

5.5

7.0

dB

AGC characteristics APL 35%

VAGC3

SIG2

6.3

8.0

9.7

dB

AGC OUT APL 100% AGC OUT APL 0% RGB output pedestal level APC pull-in upper range APC pull-in lower range ACC cover upper range

VAGC4

SIG3

19

3.0

3.2

3.5

VAGC5

SIG3

19

1.9

2.0

2.2

VDC

SIG1

8 9 10 5

1.4

2.0

2.4

Fpu

SIG1

SIG5 /SIG8 SIG5 /SIG8 SIG4 /SIG7

250

Hz

Fpd

SIG1

250 Hz

ACC1

SIG1

12

0.5

3.0

dB

CXA1585Q

Item ACC cover lower range Output D range

Symbol ACC2 VDL ACC2 =

Conditions C OUT (14dB: VA = 286mVp-p) C OUT (0dB: VA = 143mVp-p)

Input Signals Test Y IN C IN Point 24 pin 32 pin (pin) Min. Typ. Max. Unit SIG 1 SIG4 /SIG7 SIG1 SIG6 /SIG9

Measures B OUT level

12 8

3 0 1.5 1.0

dB V

C ADJ (30 pin) 3.0V

Carrier leak

CL

Input signal: SYNC only Measures 3.58MHz component of output With VA = 143mVp-p as 0dB, measures input level (VA) when C OUT chroma signal is no longer output, and calculates the ratio of this to when the level is 143mVp-p

SIG1

20

mV

NTSC ACK operation

ACK

SIG1 SIG4 /SIG7

12

50

30

dB

C.SYNC High level C.SYNC Low level Burst ag High level Burst ag Low level Subcarrier output voltage

VOH VOL VOH VOH VO(SC) Amplitude when frequency at Pin 5 is adjusted to 3.579545MHz 20Hz

SIG1 SIG1 SIG1 SIG1 SIG1

15 15 16 16 5

4.0 0.5 4.0 0.5 500 600

V V V V mV

NOTE: VCC1 = 5V, VCC2 = 5V, Ta = +25C. * Default conditions for pin settings SHP F0 = 39k, SHP CTL = 2.5V, APL CTL = 0V.

10

CXA1585Q

Input Signals (Electrical Characteristic Input Signals)

Y input SIG1

103mV

4.7s 1H = 63.5s

SIG2

VL

4.7s

103mV

Level VA Frequency F

SIG3

VL

4.7s

103mV

11

CXA1585Q

C input

SIG4 Level = VA

3.579545MHz

SIG5

Level = 143mVP-P

3.579545MHz 250Hz

||

fsc

SIG6

Level = 143mVP-P

180deg

180deg

90deg

0deg Level = VA

270deg

SIG7

4.433619MHz

SIG8

Level = 143mVP-P

4.433619MHz 250Hz

||

fsc

Level = 143mVP-P SIG9

135deg 180deg

90deg 0deg

270deg 225deg

180deg 0deg 270deg 90deg

12

Y IN 0.047 C13 V19 C14 V6 0V 0.047 C15 4.7 C5 + 22 R7 510k + 1 0.047 C9 C12

24 APL DET SHARPNESS 25 SYNC SEP 15

SW

23 APL AMP

22

21

20

19

18

17

CLP 16

V16 R8 3.6k V15

SYNC SLICE SIG AMP PULSE GEN

Electrical Characteristics Test Circuit

26 14 BLK ACK ACK DET 13 CHROMA AMP FF ADD/SUB SW INV 90 32 HUE PS 0 DEM B-Y R-Y Y/C MIX 12 Y CLP

C18 + 4.7 SW

V2

27

R9 2k C20 0.01 R11

V7 2.3V

2.5V

R3

28 BURST GATE PAL ID

8.2H

1HDL

DAT

39k

L1

390

V12

R2

29

13

30 ACC DL AMP 31 ACC DET APC VXO 3 4 5

1.5k

27k

C19 0.01

R10

390

C1 0.01

11

SW

V1 2.5V

R1

C3 0.47

10

V10

C IN

180k

C2

V9

0.47

1

C7 1 470 C4 V3 R5 0.01 R4 2V C5 100k V4 0.1 3.4V SW C8 10p

7 A

NTSC mode PAL mode

+

C11 3.579545 MHz 30p C10 SW 30p 4.433619 MHz

V5 R6 5V

C16 0.01

C17 4.7

3784 43

CXA1585Q

V8

V8

CXA1585Q

Description of Operation (1) Luminance signal regeneration system <1> Sharpness lter The video (luminance and sync) signals input from Pin 24 (VIDEO IN) are boosted near 1.5MHz by the sharpness lter. The 1.5MHz component can be varied from 4.5 to +4.5dB (as compared to the 300kHz) according to the voltage of Pin 27 (SHP CTL). Approximately 0dB (as compared to the 300kHz) when Pin 27 (SHP CTL) is 2.5 V. Keep Pin 27 open when sharpness is not operated. Since the DC bias in the IC is 2.5V, the frequency response characteristics are almost the same as the characteristics applied 2.5V to Pin 27 externally. <2> APL circuit The Y AMP gain is controlled by the APL (average picture level) function, and the gain is reduced as the APL increases. The APL circuit is operated when the voltage at Pin 18 (APL CTL) is between 3.0V and 5.0V. It is OFF when APL CTL is 0V. (2) Chrominance signal regeneration system <1> ACC circuit The chroma signal input from Pin 32 (C IN) is controlled so that the burst signal is detected by ACC DET, feedback is applied to ACC AMP in accordance with the detective output, and the burst level is controlled to be constant. The chroma signal level (Pin 12) is approximately 45mVp-p for ACC operations. <2> APC circuit Only the burst signal among the signals whose level has been made constant by ACC AMP enters the APC circuit at the burst gate circuit. 0, +90 and +180 signals are generated in the phase circuit for the VXO Output, and their Composite waves (+90 carrier) enter the APC Circuit passing through the hue circuit. Here their phase is compared with that of the burst signal and feedback is applied to VXO to obtain a phase difference of +90. The 0 and +90 carriers created in this way are supplied to B-Y, R-Y and DEM. This means

that the demodulation axis can be changed by rotating the phase of the composite waves by the DC voltage at Pin 1 (HUE ADJ). <3> DEM circuit (NTSC) The chroma signal whose level has been made constant by ACC AMP is amplified by CHROMA AMP, demodulated by B-Y DEM and R-Y DEM, applied to the Y/C MIX circuit with G-Y created by the resistance rnatrix, mixed with the luminance signal and then output as the R, G, and B primary colors. <4> DEM circuit (PAL) The processing is the same as for NTSC until CHROMA AMP. The chroma signal output to Pin 12 (C OUT) enters DL AMP from Pin 11 (DLA IN) via 1HDL (1H delay line), its level is controlled, and the signal is applied to the ADD/SUB circuit. The original signal is added or subtracted in this circuit: the addition signal is applied to B-Y DEM and the subtraction signal to R-Y DEM, and they are demodulated by the +90 carrier whose phase is inverted every 1 H and the 0 carrier. The signals are then mixed with the luminance signal and output as the R, G, and B primary colors. <5> PAL ID In PAL mode, the phase of the +90 carrier is inverted in synchronization with H.SYNC. Sync detection is conducted to establish whether this matches the input burst. When there is an error, it is corrected by applying feedback to FF (ip-op). (3) Sync separation system The sync tip of the video signals input from Pin 23 (SYNC IN) is clamped and the sync signals are separated. On the basis of the SYNC pulse created here, BF (burst ag), BLK pulse and other timing pulses are generated and supplied to the circuits. The SYNC and BF (burst flag) pulses are output to Pins 15 and 16 via a buffer.

14

Y IN C12

R31

0.047

C5 C9 C11 50k 0.047 R21 4.7 0.047 510k C13 C14 + 1 103mV + 22

Note) Match the phases of Y and C box input.

24 APL DET SHARPNESS 25 SYNC SEP 15 14 BLK ACK DET CHROMA AMP FF ADD/SUB SW INV 90 32 HUE PS 0 DEM B-Y R-Y Y/C MIX ACK YCLP 13

C17 + 4.7

23 APL AMP SIG AMP 16

R22 3.6k

Application Circuit NTSC Mode

22

21

20

19

18

17

CLP PULSE GEN

SYNC SLICE

BF OUT

26

R8 50k

SYNC OUT

27

R10

28

39k R9*

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party and other rights due to same.

BURST GATE PAL ID

15

29

27k

12

C OUT

C1 0.01

30 ACC

R4

R6 R11

DL AMP

11

10k

50k 9.1k C3 R7 0.47

31

ACC DET

10

R OUT

180k

C2

G OUT

C IN

0.47

APC 1

C7 1 R17 R30 R15 6k 1k C4 C6 0.01 R14 100k 0.1 C8 R18

VXO 3 4 5 6 7 8

Standard special parts Crystal HC-49/U by KINSEKI, LIMITED * Metal film resistor with an accuracy of 1%

143mVp-p 1.8k R19 1.5k R20 R16 3k

C10

V1 30p 3.579545 MHz 10p SC OUT 5V 470 3.9k

C15 0.01

C16 4.7

CXA1585Q

B OUT

Y IN

0.047 C12

50k

C5 + 22

C9 C11 0.047 4.7 0.047 R21 510k C13 C14 R31 + 1

103mV

Note) Match the phases of Y and C box input.

24 APL DET SHARPNESS 25 SYNC SEP 15

R23 R24 6k 2k

23 APL AMP

Application Circuit PAL Mode

22

21

20

19

18

17

CLP 16

BF OUT

SYNC SLICE SIG AMP

R22 3.6k

SYNC OUT R25

26 14 BLK ACK ACK DET 13

4.7 C17 +

PULSE GEN

R8

50k

2k C19 0.01 L1 390 R27

27 YCLP

R10

28 BURST GATE CHROMA AMP 12 FF ADD/SUB SW INV 90 R-Y 0 DEM B-Y 32 HUE PS Y/C MIX 11 PAL ID

8.2H

1HDL

DAT

39k

R9*

29

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party and other rights due to same.

C19 0.01 R26 390

DAT: Delay Adjusting Transformer

16

30 ACC DL AMP 31 ACC DET 10 9 APC VXO 3 4 5 6 7 8 1

C7 1 1.8k R19 R17 R30 R15 6k C4 C6 0.01 R14 1k 0.1 R19 100k C8 C10

27k

C1 0.01

R4

R6 R11

10k

50k 9.1k C3 R7 0.47

R OUT

180k

C2

G OUT

0.47

Standard special parts 1HDL ADL-CS346-A02 by Asahi Glass Co., Ltd. DAT BTK ANS-18267DTY by TOKO INC. Crystal HC-49/U by KINSEKI, LIMITED * Metal film resistor with an accuracy of 1%

143mVp-p 1.5k R16 3k

470 3.9k

10p

30p 4.433619 MHz SC OUT

R20

V1 5V

C15 0.01

C16 4.7

B OUT

CXA1585Q

CXA1585Q

Adjustment Procedure NTSC mode Input signal: 75% color bar 1) Free-running f0 adjustment Adjust (R30) the DC voltage at Pin 2 (APC TC) so that the oscillation frequency (subcarrier) f SC = 3.579545MHz at Pin 5 (SC OUT) is within 20Hz under inputting sync condition. 2) Input level adjustment Adjust (R13) the input level so that the white peak (75% white) is set to 0.75Vp-p at the B output. Connect Pin 18 (APL CTL) to GND at this time.

3) HUE ADJ, C ADJ adjustment Adjust (R15, R6) HUE ADJ (Pin 1) and C ADJ (Pin 30) so that the colors (A, B, C and D in the figure below) of the B output amplitude are set to the same amplitude.

SYNC OUT

B OUT 0.75VP-P A B C D

PAL mode Input signal: 75% color bar 1) Free-running f0 adjustment Adjust (R30) the DC voltage at Pin 2 (APC TC) so that the oscillation frequency (subcarrier) fSC = 4.433619MHz at Pin 5 (SC OUT) is within 20Hz under inputting sync condition. 2) Input level adjustment (same as for NTSC).

3) DL AMP and DAT (delay adjusting transformer) adjustment Adjust (R24, DAT) Pin 14 (DLA BIAS) and DAT alternately so that the R output amplitudes (A1 and A2) are equal for the H periods before and after. 4) C ADJ adjustment Adjust (R6) C ADJ so that the colors of the R output amplitude are set to 0.75Vp-p.

SYNC OUT

A1 B OUT

A2

3784 47

17

CXA1585Q

Applications 1) The input dynamic range is 0.36Vp-p (max.). The breakdown is given as follows: Y IN (Pin 24) Sync signal: 0.103Vp-p Luminance signal: 0.256Vp-p (100% white) Burst signal: 0.143Vp-p

5) The amount of delay for luminance and chroma signals in the IC is the same. 6) Demodulation axis and detective output ratio The standard values are given below as referenced in the B-Y axis. 7) Notes on Operation

Demodulation Axis +88 +235 Detective Output Ratio 0.57 0.37

C IN (Pin 32)

Note that when the input signal exceeds the value of 0.36Vp-p from sync tip to white peak, the output may be clipped and attened. This applies the case for the APL circuit OFF (Pin 18 APL CTL = 0V). 2) The center frequency for the sharpness varies according to the resistor connected to Pin 28. The variation is 40kHz/kW, and the standard value is approximately 1.5MHz for 39kW. 3) The voltage of Pin 19 (APL TC) has the following values according to the APL (average picture level): APL 0% (all black): 2.0V APL 100% (all white): 3.2V 4) Pin 23 (SYNC IN) is normally connected to Pin 24 (Y IN) for use. To cope with weak electric elds, however, its level can be increased or a low-pass lter inserted to provide a separate input.

R-Y axis G-Y axis

Be sure to wire X-tal (crystal oscillator) as close to the IC in as short a distance as possible since F0 varies depending on floating capacitance and other factors. Also, take particular care with the routing of the VCC and GND leads. Use a decoupling capacitor for VCC and others with superior performance, and attach it as close to the IC as possible.

18

CXA1585Q

(dB) 2 C OUT (output) (assumed to be 0dB output level for burst level 143mV is input)

ACC Characteristics

(dB) 40 30

Hue Control Characteristics

0 20 PHASE 10 (dB) 2 10 0 10 6 20 8 40 30 10 0 INPUT (Burst level 143mVP-P = 0dB) 20 30 0 1 2 3 HUE ADJ (1 pin) 4 5 (V)

(MHz) 3.5804 3.5802 SC OUT Output (5 pin)

Free-running Frequency

(dB) 15 10 GAIN (assumed to be 0dB OUT level for C ADJ is 2.0V) 5 0 5 10 15 20

CHROMA Control Characteristics

3.5800 3.5798 3.5796 3.5794 3.5792 3.5790 3.5788 3.30 3.35 3.40 APC TC (2 pin) 3.45 3.50 (V)

25 1.0

1.5

2.0

2.5

3.0

C ADJ (30 pin)

3.5 (V)

(dB) 10 9 Gain for Y (B OUT) 8

APL Characteristics

APL CTL voltage (18 pin voltage) 1.5V 3.5V 4.0V

(dB) 8 6 4 B OUT 2 0 -2

Sharpness Control Characteristics

Sharpness Control voltage (27 pin voltage) 1.5V 2.5V 3.5V

7 6

-4 5 4 -6 -8 20 30 60 70 80 90 100 (%) APL (Assumed to be 100% when input Y level is 256mVP-P (100% white) 40 50 10k 100k Frequency 1M 10M (Hz)

19

CXA1585Q

Package Outline

Unit: mm 32 pin QFP (Plastic)

9.0 0.2 7.0 +0.3 0.1

24 17

1.5 +0.35 0.15

0.15

25

16

32

0.1 +0.2 0.1

0.3 0.8

+0.15 0.10

0.12

0.127 +0.1 0.05 0 to 10

PACKAGE STRUCTURE

SONY CODE EIAJ CODE JEDEC CODE QFP-32P-L01 *QFP032-P-0707-A PACKAGE MATERIAL LEAD TREATMENT LEAD MATERIAL PACKAGE WEIGHT EPOXY RESIN SOLDER PLATING 42ALLOY 0.2g

20

0.50

(8.0)

Вам также может понравиться

- Uc284xa Uc384xaДокумент16 страницUc284xa Uc384xayusufwpОценок пока нет

- Colour TV Set: ModelsДокумент19 страницColour TV Set: ModelsLefter TironОценок пока нет

- SG3524 SMPS Control Circuit: Description Pin ConfigurationДокумент5 страницSG3524 SMPS Control Circuit: Description Pin ConfigurationNiko OlnicasaОценок пока нет

- Datasheet Uc3810nДокумент15 страницDatasheet Uc3810nCarlos IbaОценок пока нет

- Cxa1191 110666Документ7 страницCxa1191 110666Anura MaddumageОценок пока нет

- Ta 8252 HДокумент14 страницTa 8252 HNiraj Suroopjeet0% (1)

- CA3160Документ19 страницCA3160Brzata PticaОценок пока нет

- An7316 Idjo3Документ5 страницAn7316 Idjo3Andy Luis Morales GuerraОценок пока нет

- IC CXA2581N DatasheetДокумент23 страницыIC CXA2581N Datasheetnaupas007Оценок пока нет

- Description Features: LTC3861 Dual, Multiphase Step-Down Voltage Mode DC/DC Controller With Accurate Current SharingДокумент36 страницDescription Features: LTC3861 Dual, Multiphase Step-Down Voltage Mode DC/DC Controller With Accurate Current SharingrotenolabsОценок пока нет

- TA8251AH: Max Power 30W BTL × 4ch Audio Power ICДокумент13 страницTA8251AH: Max Power 30W BTL × 4ch Audio Power ICРамиль Невмянов100% (1)

- NCP 3063Документ20 страницNCP 3063Roozbeh BahmanyarОценок пока нет

- STK400 040Документ10 страницSTK400 040Carlos Milton Martinez GaleanoОценок пока нет

- Energy Metering Ic With Pulse Output: DescriptionДокумент7 страницEnergy Metering Ic With Pulse Output: DescriptionvungocduongОценок пока нет

- CXA1779PДокумент10 страницCXA1779PCristian Camilo Lara MonteroОценок пока нет

- 14 + 1 Channel Buffers For TFT-LCD Panels: FeaturesДокумент17 страниц14 + 1 Channel Buffers For TFT-LCD Panels: Featuresroto44Оценок пока нет

- Precision Phase-Locked Loop: ... The Analog Plus CompanyДокумент21 страницаPrecision Phase-Locked Loop: ... The Analog Plus Companykao08Оценок пока нет

- AN8806SB: Three-Beam Method Head Amplifier IC For CD PlayerДокумент10 страницAN8806SB: Three-Beam Method Head Amplifier IC For CD PlayeraldoОценок пока нет

- Ca3140, Ca3140A: 4.5Mhz, Bimos Operational Amplifier With Mosfet Input/Bipolar Output FeaturesДокумент19 страницCa3140, Ca3140A: 4.5Mhz, Bimos Operational Amplifier With Mosfet Input/Bipolar Output FeaturesRicardo Teixeira de AbreuОценок пока нет

- UC2842B/3B/4B/5B UC3842B/3B/4B/5B: High Performance Current Mode PWM ControllerДокумент15 страницUC2842B/3B/4B/5B UC3842B/3B/4B/5B: High Performance Current Mode PWM ControllertoajuiceОценок пока нет

- DatasheetДокумент10 страницDatasheetJose SalgueroОценок пока нет

- Data SheetДокумент5 страницData Sheetpartgio100% (1)

- AS15 Tsl1014if - As15-G - Hx8915a PDFДокумент15 страницAS15 Tsl1014if - As15-G - Hx8915a PDFPedro Alarcon100% (2)

- LTC 1625Документ24 страницыLTC 1625Sakura KunОценок пока нет

- 1.5-A Peak Boost/Buck/Inverting Switching Regulators: FeaturesДокумент23 страницы1.5-A Peak Boost/Buck/Inverting Switching Regulators: FeaturesReinaldo VergaraОценок пока нет

- Datasheet NECДокумент20 страницDatasheet NECPham Trung KienОценок пока нет

- STK4132IIДокумент8 страницSTK4132IIAttila SzelelkiОценок пока нет

- TA8225HДокумент16 страницTA8225HJohn Keneth VasquezОценок пока нет

- Low Power Dual Operational Amplifiers: Order CodesДокумент13 страницLow Power Dual Operational Amplifiers: Order CodesGyeTaeBaeОценок пока нет

- LT1618 DatasheetДокумент16 страницLT1618 DatasheetkurabyqldОценок пока нет

- XR-215 PLLДокумент32 страницыXR-215 PLLJ Jesús Villanueva GarcíaОценок пока нет

- Uc 3872 DWДокумент8 страницUc 3872 DWCarlos CuebasОценок пока нет

- CA3140Документ20 страницCA3140Brzata PticaОценок пока нет

- Fuji Fa5331mДокумент13 страницFuji Fa5331mVenkatesh SubramanyaОценок пока нет

- Datasheet AN5829S - Sound Multiplex Decoder IC For The U.S. Televisions - Panasonic SemiconductorДокумент17 страницDatasheet AN5829S - Sound Multiplex Decoder IC For The U.S. Televisions - Panasonic Semiconductorfernandog251186Оценок пока нет

- Datasheet Fairchild UC3843Документ7 страницDatasheet Fairchild UC3843Tina JohnsonОценок пока нет

- Uc3844 DДокумент16 страницUc3844 DFaisalMalikОценок пока нет

- VCO Produces Positive and Negative Output Frequencies PDFДокумент4 страницыVCO Produces Positive and Negative Output Frequencies PDFagmnm1962100% (1)

- Specifications: 1. Picture Tube 4. Power SupplyДокумент49 страницSpecifications: 1. Picture Tube 4. Power Supplyfvb_spamОценок пока нет

- Cd4538 Pin DiagramДокумент8 страницCd4538 Pin DiagramPrateek NailwalОценок пока нет

- Cxa1645 TV EncoderДокумент14 страницCxa1645 TV EncoderkorrekaminosОценок пока нет

- Linear - 16-Bit, Ultra Precise, Fast Settling VOUT DACДокумент16 страницLinear - 16-Bit, Ultra Precise, Fast Settling VOUT DACAtakan OzturKОценок пока нет

- SN 761672 AДокумент18 страницSN 761672 AAda CsabaОценок пока нет

- Uc3844 DДокумент16 страницUc3844 DankurmalviyaОценок пока нет

- 74 Alvc 164245Документ13 страниц74 Alvc 164245roozbehxoxОценок пока нет

- FДокумент20 страницFfaithfully_fatihОценок пока нет

- Linear Technology LTC3728EG28400Документ37 страницLinear Technology LTC3728EG28400Rickz2k8Оценок пока нет

- LTC1799 DatasheetДокумент13 страницLTC1799 Datasheetkonan_heriОценок пока нет

- Ha 13563Документ18 страницHa 13563Danh ProОценок пока нет

- Akira y Silver Point Om8377 y Om8370Документ20 страницAkira y Silver Point Om8377 y Om8370Rocko RattОценок пока нет

- AKAI - 21CT06FS - Chassis - PX20019 PDFДокумент19 страницAKAI - 21CT06FS - Chassis - PX20019 PDFsertecelecОценок пока нет

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1От EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Рейтинг: 4.5 из 5 звезд4.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Оценок пока нет

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Рейтинг: 2.5 из 5 звезд2.5/5 (3)

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsОт EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsОценок пока нет

- Audio IC Circuits Manual: Newnes Circuits Manual SeriesОт EverandAudio IC Circuits Manual: Newnes Circuits Manual SeriesРейтинг: 5 из 5 звезд5/5 (1)

- PWR221T-30 Series Power Resistor: Features ApplicationsДокумент4 страницыPWR221T-30 Series Power Resistor: Features ApplicationsVehid ParićОценок пока нет

- Isc P-Channel MOSFET Transistor IRF5210, IIRF5210: INCHANGE SemiconductorДокумент2 страницыIsc P-Channel MOSFET Transistor IRF5210, IIRF5210: INCHANGE SemiconductorVehid ParićОценок пока нет

- Tranzistori - ZameneДокумент9 страницTranzistori - ZameneMiodrag Kolakovic100% (1)

- Map 8800Документ2 страницыMap 8800Vehid Parić100% (4)

- Quanta Bl5s R1a SchematicsДокумент38 страницQuanta Bl5s R1a SchematicsVehid ParićОценок пока нет

- Power Supply LW6.194Документ1 страницаPower Supply LW6.194Vehid ParićОценок пока нет

- t60 Schematics PDFДокумент92 страницыt60 Schematics PDFVehid ParićОценок пока нет

- Si4634dy PDFДокумент10 страницSi4634dy PDFVehid ParićОценок пока нет

- TDA1005 - Stereo Decoder PDFДокумент19 страницTDA1005 - Stereo Decoder PDFVehid ParićОценок пока нет

- Haxorware ManualДокумент23 страницыHaxorware ManualVivianandEnrique Garibay100% (1)

- 2085 Micro800 Datasheet PDFДокумент12 страниц2085 Micro800 Datasheet PDFAaron Ibarra San DiegoОценок пока нет

- Comparison DCS&SCADAДокумент34 страницыComparison DCS&SCADALinh Vo TanОценок пока нет

- PLC Simulation ReportДокумент62 страницыPLC Simulation ReportAsraful Goni NirabОценок пока нет

- Fisa Tehnica 500WДокумент2 страницыFisa Tehnica 500WFrancisco Antonio Martínez RayaОценок пока нет

- DM397 Manual PDFДокумент15 страницDM397 Manual PDFAngel RomeroОценок пока нет

- Lab 6 - Potentiometer & Servo MotorДокумент7 страницLab 6 - Potentiometer & Servo MotorChristy CheriyanОценок пока нет

- VduДокумент1 страницаVduZain BazОценок пока нет

- 74 Ls 138Документ1 страница74 Ls 138Ricardo EspañaОценок пока нет

- Modifications On v2:: F405 / 32K Gyro Loop / 5VBEC / 8VBEC / Hall Current Sensor / Camera Control / 5x UART / PDBДокумент3 страницыModifications On v2:: F405 / 32K Gyro Loop / 5VBEC / 8VBEC / Hall Current Sensor / Camera Control / 5x UART / PDBdaniОценок пока нет

- Ixar Academy Laptop Repair Syllabus PDFДокумент3 страницыIxar Academy Laptop Repair Syllabus PDFBlessing MagwereОценок пока нет

- Tutorial4 SolutionsДокумент9 страницTutorial4 SolutionsAditya JabadeОценок пока нет

- L7581 DataSheet PDFДокумент2 страницыL7581 DataSheet PDFRohmad FauziОценок пока нет

- Sy8089aaac - C78988 OriginalДокумент10 страницSy8089aaac - C78988 Originaljonathan hernandezОценок пока нет

- Design of RC Snubbers For PCT Applications - ABBДокумент9 страницDesign of RC Snubbers For PCT Applications - ABBBruno LambertОценок пока нет

- (Catalog) Brochure PDFДокумент13 страниц(Catalog) Brochure PDFrehanОценок пока нет

- Data Sheet APAQ-HCF ENДокумент2 страницыData Sheet APAQ-HCF ENRockoОценок пока нет

- Hyundai d467mnДокумент2 страницыHyundai d467mnManuОценок пока нет

- Phison Flash IdДокумент2 страницыPhison Flash Idclaudi branОценок пока нет

- Imb.e Service Manual-EnДокумент180 страницImb.e Service Manual-EnKonikaHossainОценок пока нет

- How To Use Interrupts With Python On The Raspberry Pi and RPiДокумент12 страницHow To Use Interrupts With Python On The Raspberry Pi and RPiMatthew Vinodh RajОценок пока нет

- Minor Project ReportДокумент16 страницMinor Project ReportGagneet KaurОценок пока нет

- Sandeepani PDC VLSIДокумент2 страницыSandeepani PDC VLSIAvinash BaldiОценок пока нет

- Semiconductor DiodeДокумент74 страницыSemiconductor DiodeOnie EstrellaОценок пока нет

- Manual Urc7540 EnglishДокумент34 страницыManual Urc7540 EnglishAubrey PleinОценок пока нет

- PSRR and Measurement of PSRR in Class-D Audio Amplifiers and LDOs - An-135Документ7 страницPSRR and Measurement of PSRR in Class-D Audio Amplifiers and LDOs - An-135absalomlootОценок пока нет

- BD9215AFVДокумент5 страницBD9215AFVYusuf Agustaf SatrianiОценок пока нет

- Kamath Pole ZeroДокумент6 страницKamath Pole ZeroVenkatesh TatikondaОценок пока нет

- CodanДокумент2 страницыCodaninsinyurОценок пока нет

- PD Interview Questions - Compressed PDFДокумент4 страницыPD Interview Questions - Compressed PDFBhadresh VariyaОценок пока нет