Академический Документы

Профессиональный Документы

Культура Документы

ATtiny13, ATtiny2313, Instruction Set

Загружено:

Mihai PaunИсходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

ATtiny13, ATtiny2313, Instruction Set

Загружено:

Mihai PaunАвторское право:

Доступные форматы

ADD - Add without Carry

Description:

Adds two registers without the C flag and places the result in the destination register Rd. Operation: Rd <- Rd + Rr Syntax: Operands: am Counter: ADD Rd,Rr 0 d 31, 0 r 31 PC + 1 16-bit Opcode: 0000 11rd dddd rrrr

Status Register (SREG) and Boolean Formulae:

Progr PC <-

ITH S V N Z C - - <> <> <> <> <> <> H:Rd3 Rr3+Rr3 R3 + R3 Rd3 Set if there was a carry from bit 3; cleared otherwise S: N [+] V, For signed tests. V:Rd7 Rr7 R7 + Rd7 Rr7 R7 operation; cleared otherwise. Set if two's complement overflow resulted from the

N:R7 Set if MSB of the result is set; cleared otherwise. Z: R7 R6 R5 R4 R3 R2 R1 R0 Set if the result is $00; cleared otherwise. C:Rd7 Rr7 +Rr7 R7 + R7 Rd7 Set if there was carry from the MSB of the result; cleared otherwise. R (Result) equals Rd after the operation. Example: add r1,r2 ; Add r2 to r1 (r1=r1+r2) add r28, r28 ; Add r28 to itself (r28=r28+r28)

Words: 1 (2 bytes) Cycles: 1

ADC - Add with Carry

Description: Adds two registers and the contents of the C flag and places the result in the destination register Rd. Operation: (i)Rd Rd + Rr + C Syntax: Operands: Program Counter: (i)ADC Rd, Rr0 d 31, 0 r 31 PC <- PC + 1 16-bit Opcode: 0001 11rd dddd rrrr Status Register (SREG) Boolean Formulae: ITH S V N Z C - - <> <> <> <> <> <> H:Rd3 Rr3+Rr3 R3 + R3 Rd3 Set if there was a carry from bit 3; cleared otherwise S: N [+] V For signed tests. V:Rd7 Rr7 R7 + Rd7 Rr7 R7 Set if two's complement overflow resulted from the operation; cleared otherwise. N:R7 Set if MSB of the result is set; cleared otherwise. Z: R7 R6 R5 R4 R3 R2 R1 R0 Set if the result is $00; cleared otherwise. C:Rd7 Rr7 + Rr7 R7 + R7 Rd7 Set if there was carry from the MSB of the result; cleared otherwise. R (Result) equals Rd after the operation. Example: ; Add R1:R0 to R3:R2 add r2,r0 ; Add low byte adc r3,r1 ; Add with carry high byte Words: 1 (2 bytes) Cycles: 1

ADIW - Add Immediate to Word

Description: Adds an immediate value (0-63) to a register pair and places the result in the register pair. This instruction operates on the upper four register pairs, and is well suited for operations on the pointer registers. This instruction is not available in all devices. Refer to the device specific instruction set summary. Operation: (i)Rd+1:Rd <- Rd+1:Rd + K Syntax: Operands: Program Counter: (i)ADIW Rd+1:Rd,K d E {24,26,28,30}, 0 <= K <= 63 PC <- PC + 1 16-bit Opcode: 1001 0110 KKdd KKKK Status Register (SREG) and Boolean Formulae: ITHS V N Z C - - - <> <> <> <> <> S: N [+] V, For signed tests. V:Rdh7 R15

Set if two's complement overflow resulted from the operation; cleared otherwise. N:R15 Set if MSB of the result is set; cleared otherwise. Z: R15 R14 R13 R12 R11 R10 R9 R8 R7 R6 R5 R4 R3 R2 R1 R0 Set if the result is $0000; cleared otherwise. C: R15 Rdh7 Set if there was carry from the MSB of the result; cleared otherwise. R (Result) equals Rdh:Rdl after the operation (Rdh7-Rdh0 = R15-R8, Rdl7-Rdl0=R7-R0). Example: adiw r25:24,1 ; Add 1 to r25:r24 adiw ZH:ZL,63 ; Add 63 to the Z pointer(r31:r30) Words: 1 (2 bytes) Cycles: 2

SUB - Subtract without Carry

Description:

Subtracts two registers and places the result in the destination register Rd. Operation: (i)Rd Rd - Rr Syntax: (i)SUB Rd,Rr 16-bit Opcode: 0001 10rd dddd rrrr

Status Register and Boolean Formula:

Operands: 0 d 31, 0 r 31

Program Counter: PC PC + 1

ITH S V N Z C - - <> <> <> <> <> <> H: Rd3 Rr3 +Rr3 R3 +R3 Rd3 Set if there was a borrow from bit 3; cleared otherwise S: N V, For signed tests. V:Rd7 Rr7 R7 + Rd7 Rr7 R7 Set if two's complement overflow resulted from the operation; cleared otherwise. N:R7 Set if MSB of the result is set; cleared otherwise. Z: R7 R6 R5 R4 R3 R2 R1 R0 Set if the result is $00; cleared otherwise. C: Rd7 Rr7 +Rr7 R7 +R7 Rd7

Set if the absolute value of the contents of Rr is larger than the absolute value of Rd; cleared otherwise. R (Result) equals Rd after the operation. Example: sub brne ... noteq: r13,r12 noteq nop ; Subtract r12 from r13 ; Branch if r12<>r13 ; Branch destination (do nothing)

Words: 1 (2 bytes) Cycles: 1

SUBI - Subtract Immediate

Description:

Subtracts a register and a constant and places the result in the destination register Rd. This instruction is working on Register R16 to R31 and is very well suited for operations on the X, Y and Z pointers. Operation: (i)Rd Rd - K Syntax: (i)SUBI Rd,K Operands: 16 d 31, 0 K 255 Program Counter: PC PC + 1

16-bit Opcode: 0101 KKKK dddd KKKK

Status Register and Boolean Formula:

ITH S V N Z C - - <> <> <> <> <> <> H: Rd3 K3+K3 R3 +R3 Rd3 Set if there was a borrow from bit 3; cleared otherwise S: N [+] V, For signed tests. V:Rd7 K7 R7 + Rd7 K7 R7 Set if two's complement overflow resulted from the operation; cleared otherwise. N:R7 Set if MSB of the result is set; cleared otherwise. Z: R7 R6 R5 R4 R3 R2 R1 R0 Set if the result is $00; cleared otherwise. C: Rd7 K7 +K7 R7 +R7 Rd7 Set if the absolute value of K is larger than the absolute value of Rd; cleared otherwise. R (Result) equals Rd after the operation.

Example: subi brne ... noteq:

r22,$11 noteq nop

; Subtract $11 from r22 ; Branch if r22<>$11 ; Branch destination (do nothing)

Words: 1 (2 bytes) Cycles: 1

SBC - Subtract with Carry

Description:

Subtracts two registers and subtracts with the C flag and places the result in the destination register Rd. Operation: (i) Rd Rd - Rr - C Syntax: (i) SBC Rd,Rr 16-bit Opcode: 0000 10rd dddd rrrr

Status Register and Boolean Formula:

Operands: 0 d 31, 0 r 31

Program Counter: PC PC + 1

ITH S V N Z C - - <> <> <> <> <> <> H: Rd3 Rr3 + Rr3 R3 + R3 Rd3 Set if there was a borrow from bit 3; cleared otherwise S: N [+] V, For signed tests. V:Rd7 Rr7 R7 + Rd7 Rr7 R7 Set if two's complement overflow resulted from the operation; cleared otherwise. N:R7 Set if MSB of the result is set; cleared otherwise. Z: R7 R6 R5 R4 R3 R2 R1 R0 Z Previous value remains unchanged when the result is zero; cleared otherwise. C: Rd7 Rr7+ Rr7 R7 +R7 Rd7 Set if the absolute value of the contents of Rr plus previous carry is larger than the absolute value of the Rd; cleared otherwise. R (Result) equals Rd after the operation. Example: sub r2,r0 sbc r3,r1 ; Subtract r1:r0 from r3:r2 ; Subtract low byte ; Subtract with carry high byte

Words: 1 (2 bytes) Cycles: 1

SBCI - Subtract Immediate with Carry

Description:

Subtracts a constant from a register and subtracts with the C flag and places the result in the destination register Rd. Operation: (i)Rd Rd - K - C Syntax: (i) SBCI Rd,K Operands: 16 d 31, 0 K 255 Program Counter: PC PC + 1

16-bit Opcode: 0100 KKKK dddd KKKK

Status Register and Boolean Formula:

ITH S V N Z C - - <> <> <> <> <> <> H: Rd3 K3 + K3 R3 + R3 Rd3 Set if there was a borrow from bit 3; cleared otherwise S: N [+] V, For signed tests. V:Rd7 K7 R7 + Rd7 K7 R7 Set if two's complement overflow resulted from the operation; cleared otherwise. N:R7 Set if MSB of the result is set; cleared otherwise. Z: R7 R6 R5 R4 R3 R2 R1 R0 Z Previous value remains unchanged when the result is zero; cleared otherwise. C: Rd7 K7+ K7 R7 +R7 Rd7 Set if the absolute value of the constant plus previous carry is larger than the absolute value of Rd; cleared otherwise. R (Result) equals Rd after the operation. Example: ; Subtract $4F23 from r17:r16 subi r16,$23 ; Subtract low byte sbci r17,$4F ; Subtract with carry high byte Words: 1 (2 bytes) Cycles: 1

AND - Logical AND

Description: Performs the logical AND between the contents of register Rd and register Rr and places the result in the destination register Rd. Operation: (i)Rd Rd Rr Syntax: Operands: Program Counter: (i)AND Rd,Rr 0 d 31, 0 r 31 PC PC + 1 16-bit Opcode: 0010 00rd dddd rrrr Status Register (SREG) and Boolean Formulae: ITHS VN Z C - - - <> 0 <> <> S: N [+] V, For signed tests. V:0 Cleared N: R7 Set if MSB of the result is set; cleared otherwise. Z: R7 R6 R5 R4 R3 R2 R1 R0 Set if the result is $00; cleared otherwise. R (Result) equals Rd after the operation. Example: and r2,r3 ; Bitwise and r2 and r3, result in r2 ldi r16,1 ; Set bitmask 0000 0001 in r16 and r2, r16 ; Isolate bit 0 in r2 Words: 1 (2 bytes) Cycles: 1

ANDI - Logical AND with Immediate

Description: Performs the logical AND between the contents of register Rd and a constant and places the result in the destination register Rd. Operation: (i)Rd Rd K Syntax: (i)ANDI Rd,K 16-bit Opcode: 0111 KKKK dddd KKKK Status Register (SREG) and Boolean Formulae: Operands: 16 d 31, 0 K 255 Program Counter: PC PC + 1

ITHS VN Z C - - - <> 0 <> <> S: N [+] V, For signed tests. V:0 Cleared N:R7 Set if MSB of the result is set; cleared otherwise. Z: R7 R6 R5 R4 R3 R2 R1 R0 Set if the result is $00; cleared otherwise. R (Result) equals Rd after the operation. Example: andi r17,$0F ; Clear upper nibble of r17 andi r18,$10 ; Isolate bit 4 in r18 andi r19,$AA ; Clear odd bits of r19 Words: 1 (2 bytes) Cycles: 1

OR - Logical OR

Description:

Performs the logical OR between the contents of register Rd and register Rr and places the result in the destination register Rd. Operation: (i)Rd Rd v Rr Syntax:Operands:Program Counter: (i)OR Rd,Rr0 d 31, 0 r 31PC PC + 1 16-bit Opcode: 0010 10rd dddd rrrr

Status Register (SREG) and Boolean Formula:

ITHS VN Z C - - - <> 0 <> <> S: N [+] V, For signed tests. V:0 Cleared N:R7 Set if MSB of the result is set; cleared otherwise. Z: R7 R6 R5 R4 R3 R2 R1 R0 Set if the result is $00; cleared otherwise. R (Result) equals Rd after the operation. Example: or r15,r16 bst r15,6 brts ok ... ; Do bitwise or between registers ; Store bit 6 of r15 in T flag ; Branch if T flag set

ok:

nop

; Branch destination (do nothing)

Words: 1 (2 bytes) Cycles: 1

ORI - Logical OR with Immediate

Description:

Performs the logical OR between the contents of register Rd and a constant and places the result in the destination register Rd. Operation: (i)Rd Rd v K Syntax: Operands: (i)ORI Rd,K 16 d 31, 0 K 255 16-bit Opcode: 0110 KKKK dddd KKKK

Status Register (SREG) and Boolean Formula:

Program Counter: PC PC + 1

ITHS VN Z C - - - <> 0 <> <> S: N [+] V, For signed tests. V:0 Cleared N:R7 Set if MSB of the result is set; cleared otherwise. Z: R7 R6 R5 R4 R3 R2 R1 R0 Set if the result is $00; cleared otherwise. R (Result) equals Rd after the operation. Example: ori r16,$F0 ori r17,1 Words: 1 (2 bytes) Cycles: 1 ; Set high nibble of r16 ; Set bit 0 of r17

EOR - Exclusive OR

Description:

Performs the logical EOR between the contents of register Rd and register Rr and places the result in the destination register Rd. Operation: Rd <- Rd [+] Rr Syntax: Operands: Program Counter:

EOR Rd,Rr 16-bit Opcode: 0010 01rd dddd rrrr

0 d 31, 0 r 31

PC <- PC + 1

Status Register (SREG) and Boolean Formula:

ITHS VN Z C - - - <> 0 <> <> S: N [+] V, For signed tests. V:0 Cleared N:R7 Set if MSB of the result is set; cleared otherwise. Z: R7 R6 R5 R4 R3 R2 R1 R0 Set if the result is $00; cleared otherwise. R (Result) equals Rd after the operation. Example: eor r4,r4 ; Clear r4 eor r0,r22 ; Bitwise exclusive or between r0 and r22 Words: 1 (2 bytes) Cycles: 1

COM - One's Complement

Description:

This instruction performs a one's complement of register Rd. Operation: Rd <- $FF - Rd Syntax: COM Rd 16-bit Opcode:

1001 010d dddd 0000 Status Register (SREG) and Boolean Formulae:

Operands: 0 d 31

Program Counter: PC <- PC + 1

ITHS VN Z C - - - <> 0 <> <> 1 S:N [+] V For signed tests. V:0 Cleared. N:R7 Set if MSB of the result is set; cleared otherwise. Z: R7 R6 R5 R4 R3 R2 R1 R0 Set if the result is $00; Cleared otherwise. C:1 Set. R (Result) equals Rd after the operation. Example: com r4 ; Take one's complement of r4 breq zero ; Branch if zero ... zero: nop ; Branch destination (do nothing) Words: 1 (2 bytes) Cycles: 1

NEG - Two's Complement

Description:

Replaces the contents of register Rd with its two's complement; the value $80 is left unchanged. Operation: (i)Rd $00 - Rd Syntax: Operands: (i) NEG Rd 0 d 31 16-bit Opcode: 1001 010d dddd 0001

Status Register (SREG) and Boolean Formula:

Program Counter: PC PC + 1

ITH S V N Z C - - <> <> <> <> <> <> H:R3 + Rd3 Set if there was a borrow from bit 3; cleared otherwise S:N [+] V For signed tests. V:R7 R6 R5 R4 R3 R2 R1 R0 Set if there is a two's complement overflow from the implied subtraction from zero; cleared otherwise. A two's complement overflow will occur if and only if the contents of the Register after operation (Result) is $80. N:R7 Set if MSB of the result is set; cleared otherwise. Z: R7 R6 R5 R4 R3 R2 R1 R0 Set if the result is $00; Cleared otherwise. C:R7 + R6 + R5 + R4 + R3 + R2 + R1 + R0 Set if there is a borrow in the implied subtraction from zero; cleared otherwise. The C flag will be set in all cases except when the contents of Register after operation is $00. R (Result) equals Rd after the operation. Example: sub r11,r0 ; Subtract r0 from r11 brpl positive ; Branch if result positive neg r11 ; Take two's complement of r11 positive: nop ; Branch destination (do nothing) Words: 1 (2 bytes) Cycles: 1

SBR - Set Bits in Register

Description:

Sets specified bits in register Rd. Performs the logical ORI between the contents of register Rd and constant mask K and places the result in the destination register Rd. Operation: (i)Rd <- Rd v K Syntax: (i)SBR Rd,K 16-bit Opcode: 0110 KKKK dddd KKKK

Status Register (SREG) and Boolean Formula:

Operands: 16<=d<=31, 0<=K<=255

Program Counter: PC PC + 1

ITHS VN Z C - - - <> 0 <> <> S: N V, For signed tests. V:0 Cleared N:R7 Set if MSB of the result is set; cleared otherwise. Z: 'R7 'R6 'R5 'R4 'R3 'R2 'R1 'R0 R (Result) equals Rd after the operation. Example: sbr r16,3 ; Set bits 0 and 1 in r16 sbr r17,$F0 ; Set 4 MSB in r17 Words: 1 (2 bytes) Cycles: 1

CBR - Clear Bits in Register

Description: Clears the specified bits in register Rd. Performs the logical AND between the contents of register Rd and the complement of the constant mask K. The result will be placed in register Rd. Operation: Rd <- Rd ($FF - K) Syntax: Operands: Program Counter: CBR Rd,K 16 d 31, 0 K 255 PC <- PC + 1 16-bit Opcode: (see ANDI with K complemented) Status Register (SREG) and Boolean Formula: ITHS VN Z C - - - <> 0 <> <> S: N V, For signed tests.

V:0 Cleared N:R7 Set if MSB of the result is set; cleared otherwise. Z: R7 R6 R5 R4 R3 R2 R1 R0 Set if the result is $00; cleared otherwise. R (Result) equals Rd after the operation. Example: cbr r16, $F0 ; Clear upper nibble of r16 cbr r18, 1 ; Clear bit 0 in r18 Words: 1 (2 bytes) Cycles: 1

INC - Increment

Description:

Adds one -1- to the contents of register Rd and places the result in the destination register Rd. The C flag in SREG is not affected by the operation, thus allowing the INC instruction to be used on a loop counter in multiple-precision computations. When operating on unsigned numbers, only BREQ and BRNE branches can be expected to perform consistently. When operating on two's complement values, all signed branches are available. Operation: (i) Rd <- Rd + 1 Syntax: (i) INC Rd 16-bit Opcode: 1001 010d dddd 0011

Status Register and Boolean Formula:

Operands: 0 d 31

Program Counter: PC <- PC + 1

ITHS V N Z C - - - <> <> <> <> S:N [+] V For signed tests. V:R7 R6 R5 R4 R3 R2 R1 R0 Set if two's complement overflow resulted from the operation; cleared otherwise. Two's complement overflow occurs if and only if Rd was $7F before the operation. N:R7 Set if MSB of the result is set; cleared otherwise. Z: R7 R6 R5 R4 R3 R2 R1 R0 Set if the result is $00; Cleared otherwise. R (Result) equals Rd after the operation. Example: clr r22 loop: inc r22 ...

; clear r22 ; increment r22

cpi r22,$4F brne loop nop Words: 1 (2 bytes) Cycles: 1

; Compare r22 to $4f ; Branch if not equal ; Continue (do nothing)

DEC - Decrement

Description:

Subtracts one -1- from the contents of register Rd and places the result in the destination register Rd. The C flag in SREG is not affected by the operation, thus allowing the DEC instruction to be used on a loop counter in multiple-precision computations. When operating on unsigned values, only BREQ and BRNE branches can be expected to perform consistently. When operating on two's complement values, all signed branches are available. Operation: Rd <- Rd - 1 Syntax: DEC Rd 16-bit Opcode: 1001 010d dddd 1010

Status Register and Boolean Formula:

Operands: 0 d 31

Program Counter: PC <- PC + 1

ITHS V N Z C - - - <> <> <> <> S:N [+] V For signed tests. V: R7 R6 R5 R4 R3 R2 R1 R0 Set if two's complement overflow resulted from the operation; cleared otherwise. Two's complement overflow occurs if and only if Rd was $80 before the operation. N:R7 Set if MSB of the result is set; cleared otherwise. Z: R7 R6 R5 R4 R3 R2 R1 R0 Set if the result is $00; Cleared otherwise. R (Result) equals Rd after the operation. Example: ldi r17, $10 ; Load constant in r17 loop: add r1, r2 ; Add r2 to r1 dec r17 ; Decrement r17 brne loop ; Branch if r17<>0 nop; Continue (do nothing) Words: 1 (2 bytes) Cycles: 1

TST - Test for Zero or Minus

Description:

Tests if a register is zero or negative. Performs a logical AND between a register and itself. The register will remain unchanged. Operation: (i)Rd Rd Rd Syntax: Operands: (i)TST Rd 0 d 31 16-bit Opcode: (see AND Rd, Rd) 0010 00dd dddd dddd

Status Register and Boolean Formula:

Program Counter: PC PC + 1

ITHS VN Z C - - - <> 0 <> <> S: N [+] V, For signed tests. V:0 Cleared N:R7 Set if MSB of the result is set; cleared otherwise. Z: R7 R6 R5 R4 R3 R2 R1 R0 Set if the result is $00; cleared otherwise. R (Result) equals Rd. Example: tst r0 breq zero ... zero: ; Test r0 ; Branch if r0=0 nop ; Branch destination (do nothing)

Words: 1 (2 bytes) Cycles: 1

CLR - Clear Register

Description:

Clears a register. This instruction performs an Exclusive OR between a register and itself. This will clear all bits in the register. Operation: Rd <- Rd [+] Rd Syntax: CLR Rd Operands: 0 d 31 Program Counter: PC <- PC + 1

16-bit Opcode: (see EOR Rd,Rd) 0010 01dd dddd dddd

Status Register (SREG) and Boolean Formula:

ITHSVNZC -- - 00 0 1 S: 0 Cleared V:0 Cleared N:0 Cleared Z:1 Set R (Result) equals Rd after the operation. Example: clr r18 ; clear r18 loop: inc r18 ; increase r18 ... cpi r18, $50 ; Compare r18 to $50 brne loop Words: 1 (2 bytes) Cycles: 1

SER - Set all bits in Register

Description:

Loads $FF directly to register Rd. Operation: (i) Rd $FF Syntax: (i) SER Rd 16-bit Opcode: 1110 1111 dddd 1111 Operands: 16 d 31 Program Counter: PC PC + 1

Status Register (SREG) and Boolean Formula:

ITHSVNZC -- - - - - - Example: clr r16

; Clear r16

ser r17 out $18,r16 nop out $18,r17 Words: 1 (2 bytes) Cycles: 1

; ; ; ;

Set r17 Write zeros to Port B Delay (do nothing) Write ones to Port B

SBIW - Subtract Immediate from Word

Description:

Subtracts an immediate value (0-63) from a register pair and places the result in the register pair. This instruction operates on the upper four register pairs, and is well suited for operations on the pointer registers. This instruction is not available in all devices. Refer to the device specific instruction set summary. Operation: (i)Rd+1:Rd Rd+1:Rd - K Syntax: (i)SBIW Rd+1:Rd,K 16-bit Opcode: 1001 0111 KKdd KKKK

Status Register (SREG) and Boolean Formula:

Operands: d E {24,26,28,30}, 0 K 63

Program Counter: PC PC + 1

ITHS V N Z C -- - S: N V, For signed tests. V:Rdh7 R15 Set if two's complement overflow resulted from the operation; cleared otherwise. N:R15 Set if MSB of the result is set; cleared otherwise. Z: R15 R14 R13 R12 R11 R10 R9 R8 R7 R6 R5 R4 R3 R2 R1 R0 Set if the result is $0000; cleared otherwise. C:R15 Rdh7 Set if the absolute value of K is larger than the absolute value of Rd; cleared otherwise. R (Result) equals Rdh:Rdl after the operation (Rdh7-Rdh0 = R15-R8, Rdl7-Rdl0=R7-R0). Example: sbiw r25:r24,1 ; Subtract 1 from r25:r24 sbiw YH:YL,63 ; Subtract 63 from the Y pointer(r29:r28) Words: 1 (2 bytes) Cycles: 2

Adresa : http://avr.8b.cz/asmhelp/Html/ATtiny13_Instruction_Set.htm#b

Вам также может понравиться

- Code AsemblyДокумент87 страницCode AsemblyHieu Vo QuocОценок пока нет

- Arithmetic InstructionsДокумент100 страницArithmetic InstructionsdhapraОценок пока нет

- ARM Instruction SetДокумент75 страницARM Instruction SetEragon ShadeSlayerОценок пока нет

- 02 - Data Processing InstructionsДокумент42 страницы02 - Data Processing InstructionsRiver AbodОценок пока нет

- Instr Set PDFДокумент150 страницInstr Set PDFvannybowoooОценок пока нет

- MES Module 2Документ13 страницMES Module 2Radha Krishna - with youОценок пока нет

- Lecture 2 - ARM Instruction SetДокумент42 страницыLecture 2 - ARM Instruction SetSuhaib AbugderaОценок пока нет

- 3.2 Arm Addressing Mode and Instruction SetДокумент32 страницы3.2 Arm Addressing Mode and Instruction Set727721eumt082Оценок пока нет

- Arm NotesДокумент52 страницыArm NotesSanjana GaneshОценок пока нет

- Lect25 26 1pp PDFДокумент58 страницLect25 26 1pp PDFFengxing ZhuОценок пока нет

- Lec08 ARMisa 4upДокумент24 страницыLec08 ARMisa 4upMuthu LinganОценок пока нет

- Lecture6-Bit AddressabilityДокумент27 страницLecture6-Bit AddressabilityJawad shah SayedОценок пока нет

- Chapter 3: Arm Instruction Set: (Architecture Version: Armv4T)Документ32 страницыChapter 3: Arm Instruction Set: (Architecture Version: Armv4T)sunilbhimuОценок пока нет

- AQA Assembly Language Questions and MSДокумент9 страницAQA Assembly Language Questions and MSBen DaffadaОценок пока нет

- Q1 C Code: WhileДокумент2 страницыQ1 C Code: WhileJyothi B.R.Оценок пока нет

- Instruction Set of ARMДокумент82 страницыInstruction Set of ARMwizard01.2022Оценок пока нет

- QRC0001H RVCT v2.1 ThumbДокумент4 страницыQRC0001H RVCT v2.1 ThumbhisriharibabuОценок пока нет

- Unit 2 Mcu PDFДокумент12 страницUnit 2 Mcu PDFatulОценок пока нет

- Experiment No.: 3: PC With Atmel StudioДокумент11 страницExperiment No.: 3: PC With Atmel StudioDhrumil ManiyarОценок пока нет

- Week 04Документ68 страницWeek 04aroosa naheedОценок пока нет

- AVR Instruction SetДокумент150 страницAVR Instruction SetHugo LoureiroОценок пока нет

- Department of Computer Science & Engineering Subject: Microcontroller & Embedded Systems Semester: 4Документ14 страницDepartment of Computer Science & Engineering Subject: Microcontroller & Embedded Systems Semester: 4Azeem TopОценок пока нет

- Arm Instruction 2 - 001Документ26 страницArm Instruction 2 - 001Ankit SanghviОценок пока нет

- Module IIIДокумент58 страницModule IIIprathyusha maddalaОценок пока нет

- SNUVM2 Reference ManualДокумент9 страницSNUVM2 Reference ManualJeongho NahОценок пока нет

- Sum Evenodd of ArrayДокумент1 страницаSum Evenodd of ArrayTr Ần NghĩaОценок пока нет

- Microcontroller Lab Software MANUALДокумент17 страницMicrocontroller Lab Software MANUALshivakeshichoupiriОценок пока нет

- Lecture 7: ARM Arithmetic and Bitwise InstructionsДокумент34 страницыLecture 7: ARM Arithmetic and Bitwise InstructionsfmsarwarОценок пока нет

- AppendixD Assembly ArmДокумент53 страницыAppendixD Assembly ArmBilelAmerОценок пока нет

- Topic 3 ARM Instruction Set Part - 1Документ47 страницTopic 3 ARM Instruction Set Part - 1Dev PatelОценок пока нет

- 18s Cpe221 Test1 SolutionДокумент4 страницы18s Cpe221 Test1 SolutionKyra LathonОценок пока нет

- ARM Slides Part3Документ33 страницыARM Slides Part3Asmitha G ee22b030Оценок пока нет

- Lab ProposalДокумент7 страницLab ProposalMuhammad IshaqОценок пока нет

- Part A - 1 - 2 - 3 - 4 - 5Документ15 страницPart A - 1 - 2 - 3 - 4 - 5Dr. Anoop B KОценок пока нет

- Lab 1 Using Visual Emulator: Download The Emulator Answer To Questions (Q)Документ13 страницLab 1 Using Visual Emulator: Download The Emulator Answer To Questions (Q)Alejandro Sanchez LopezОценок пока нет

- 6803 Instruction Set (68HC11 Subset)Документ93 страницы6803 Instruction Set (68HC11 Subset)Saukani HalimОценок пока нет

- ARM7 CodesДокумент24 страницыARM7 CodesKen AdamsОценок пока нет

- MIPS32 Instruction Set Quick Reference: L B - F O J A B (N: O D S)Документ2 страницыMIPS32 Instruction Set Quick Reference: L B - F O J A B (N: O D S)JayОценок пока нет

- The University of Alabama in Huntsville: r2 r1 Not r1, r2Документ5 страницThe University of Alabama in Huntsville: r2 r1 Not r1, r2Kyra LathonОценок пока нет

- ARM Instruction SetДокумент32 страницыARM Instruction SetLordwin MichealОценок пока нет

- 16 32 r0 RTN Program Counter or PC: CPE 221 Test 1 Solution Spring 2019Документ4 страницы16 32 r0 RTN Program Counter or PC: CPE 221 Test 1 Solution Spring 2019Kyra LathonОценок пока нет

- 18f Cpe221 Test1 SolutionДокумент4 страницы18f Cpe221 Test1 SolutionKyra LathonОценок пока нет

- ARM Instruction Set - Data Processing - IIДокумент13 страницARM Instruction Set - Data Processing - IIAniket SubudhiОценок пока нет

- 18CS44 Module2Документ110 страниц18CS44 Module2SharanKumarHuliОценок пока нет

- Arm Instruction PrgorammingДокумент48 страницArm Instruction PrgorammingkpraneethkОценок пока нет

- 03 Bagian 1 Arsitektur AVRДокумент22 страницы03 Bagian 1 Arsitektur AVRTito Adi NugrohoОценок пока нет

- LECTURE 8 - ECE521 Instruction SETS - Branching N LoopingДокумент49 страницLECTURE 8 - ECE521 Instruction SETS - Branching N LoopingAmar MursyidОценок пока нет

- Appendix I Specification of The CPUДокумент5 страницAppendix I Specification of The CPUAamir AnisОценок пока нет

- COMP10031 ARM Instruction Set SummaryДокумент2 страницыCOMP10031 ARM Instruction Set SummaryADRISTAОценок пока нет

- AVR Instructions 1Документ133 страницыAVR Instructions 1Mlondo Khanyisani EmmanuelОценок пока нет

- ch2 Arm 1Документ32 страницыch2 Arm 1Amit Singh GaurОценок пока нет

- Cao Unit-3Документ14 страницCao Unit-3Hemanth ZОценок пока нет

- AVR Instruction Set SummaryДокумент4 страницыAVR Instruction Set SummarySinan PravadaliogluОценок пока нет

- PPC Assembly IntroДокумент36 страницPPC Assembly IntroMohammad Gulam AhamadОценок пока нет

- List of programs-CHE S6 and CES6-Revision 2015Документ18 страницList of programs-CHE S6 and CES6-Revision 2015Anna JoseОценок пока нет

- Projects With Microcontrollers And PICCОт EverandProjects With Microcontrollers And PICCРейтинг: 5 из 5 звезд5/5 (1)

- 8 Bibliogr PDFДокумент2 страницы8 Bibliogr PDFMihai PaunОценок пока нет

- DCII ManualДокумент70 страницDCII ManualHerberth CatalinОценок пока нет

- Erratico2 PDFДокумент23 страницыErratico2 PDFMihai PaunОценок пока нет

- Sms Controler ATtiny2313 MicrocontrollersДокумент6 страницSms Controler ATtiny2313 MicrocontrollersMihai PaunОценок пока нет

- Sms Controller PROJECTДокумент5 страницSms Controller PROJECTMihai PaunОценок пока нет

- Interactive LED Circuit Lm324Документ1 страницаInteractive LED Circuit Lm324Mihai PaunОценок пока нет

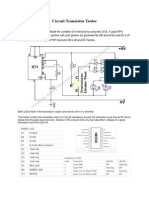

- Circuit Transistor TesterДокумент1 страницаCircuit Transistor TesterMihai PaunОценок пока нет

- TV & FM Jammer - SchematicДокумент9 страницTV & FM Jammer - SchematicRolando DaclanОценок пока нет

- Digital Circuits-I LAB: Jadavpur UniversityДокумент15 страницDigital Circuits-I LAB: Jadavpur UniversityIron PatriotОценок пока нет

- CT HandoutДокумент44 страницыCT HandoutAbdex100% (1)

- 2018 April CS301-B - Ktu QbankДокумент2 страницы2018 April CS301-B - Ktu QbanketgegrgrgesОценок пока нет

- 1 - Bit ALUДокумент13 страниц1 - Bit ALUSouvik BasuОценок пока нет

- Binary and Decimal NumbersДокумент22 страницыBinary and Decimal NumbersAlejandro AguilarОценок пока нет

- CMSC 451: Reductions & NP-completeness: Slides By: Carl KingsfordДокумент22 страницыCMSC 451: Reductions & NP-completeness: Slides By: Carl KingsfordBEKAN FAYERAОценок пока нет

- Thompson NfaДокумент14 страницThompson NfaRebeca LopezОценок пока нет

- 06 MultiplyDivideДокумент34 страницы06 MultiplyDivideMahdi AbbadiОценок пока нет

- Sem 5 Syllabus Vtu Computer ScienceДокумент20 страницSem 5 Syllabus Vtu Computer Sciencepavan kapoorОценок пока нет

- BCD To BinaryДокумент1 страницаBCD To BinaryfaisalОценок пока нет

- CS8501 - THEORY OF COMPUTATION - by LearnEngineering - inДокумент162 страницыCS8501 - THEORY OF COMPUTATION - by LearnEngineering - inKrisHnA 2kОценок пока нет

- Digital Electronics: UNIT-4 Digital Fundamentals & Logic GatesДокумент37 страницDigital Electronics: UNIT-4 Digital Fundamentals & Logic GatesvishnuОценок пока нет

- Theory of Computation Question BankДокумент17 страницTheory of Computation Question BankAnand SharmaОценок пока нет

- Cheat Sheet Data Type OracleДокумент1 страницаCheat Sheet Data Type OracledaemiОценок пока нет

- Number SystemsДокумент36 страницNumber SystemsIsrael EliasОценок пока нет

- GATE OverflowДокумент485 страницGATE Overflowlokenders801Оценок пока нет

- CS402 Grand Quiz Mega File Made by Ans Mughal - Files Preparation GroupДокумент71 страницаCS402 Grand Quiz Mega File Made by Ans Mughal - Files Preparation GroupZee50% (2)

- CENG280 Info PDFДокумент2 страницыCENG280 Info PDFBerk GulerОценок пока нет

- Encoder and DecoderДокумент17 страницEncoder and Decoderjiremy noriegaОценок пока нет

- It Solution 1-7Документ13 страницIt Solution 1-7Asi Cas JavОценок пока нет

- Shah Rayhan: Aa VQ: 4Документ2 страницыShah Rayhan: Aa VQ: 4api-287685452Оценок пока нет

- Unit 2 TOC - CSE - 1595997221Документ18 страницUnit 2 TOC - CSE - 1595997221Yadu PatidarОценок пока нет

- MicroprocessorLab OmNagpurey ENT256Документ20 страницMicroprocessorLab OmNagpurey ENT256Tanmay TalekarОценок пока нет

- The Status of The P Versus NP ProblemДокумент8 страницThe Status of The P Versus NP ProblemJessОценок пока нет

- Optimization ProblemДокумент13 страницOptimization ProblemArie TrisnaОценок пока нет

- Myhill Nerode TheoremДокумент3 страницыMyhill Nerode TheoremAbdurrehman M.IbrahimОценок пока нет

- Chapter Two: Finite Automata: Theoretical Computer Science Abstract Machines MathematicalДокумент32 страницыChapter Two: Finite Automata: Theoretical Computer Science Abstract Machines MathematicalFizza IrfanОценок пока нет

- Introduction To Automata TheoryДокумент14 страницIntroduction To Automata TheoryApoorva NaikОценок пока нет

- Automata Theory NfaДокумент33 страницыAutomata Theory NfaJoseph Neil TacataniОценок пока нет

- Flat Unit-4Документ24 страницыFlat Unit-4chak24339Оценок пока нет